**Delft University of Technology**

# A Self-Calibrated Hybrid Thermal-Diffusivity/Resistor-Based Temperature Sensor

Pan, Sining; Angevare, Jan A.; Makinwa, Kofi A.A.

DOI 10.1109/JSSC.2021.3094166

Publication date 2021 **Document Version** Accepted author manuscript

Published in IEEE Journal of Solid-State Circuits

# Citation (APA)

Pan, S., Angevare, J. A., & Makinwa, K. A. A. (2021). A Self-Calibrated Hybrid Thermal-Diffusivity/Resistor-Based Temperature Sensor. *IEEE Journal of Solid-State Circuits*, *56*(12), 3551 - 3559. https://doi.org/10.1109/JSSC.2021.3094166

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A Self-Calibrated Hybrid Thermal-Diffusivity/Resistor-Based Temperature Sensor

Sining Pan<sup>®</sup>, *Graduate Student Member, IEEE*, Jan A. Angevare<sup>®</sup>, *Graduate Student Member, IEEE*, and Kofi A. A. Makinwa<sup>®</sup>, *Fellow, IEEE*

Abstract—This article describes a hybrid temperature sensor in which an accurate, but energy-inefficient, thermal diffusivity (TD) sensor is used to calibrate an inaccurate, but efficient, resistor-based sensor. The latter is based on silicided polysilicon resistors embedded in a Wien-bridge (WB) filter, while the former is based on an electrothermal filter (ETF) made from a p-diffusion/metal thermopile and an n-diffusion heater. The use of an on-chip sensor for calibration obviates the need for an external temperature reference and a temperature-stabilized environment, thus reducing the cost. To mitigate the area overhead of the TD sensor, it reuses the WB filter's readout circuitry. Realized in a 180-nm CMOS technology, the hybrid sensor occupies 0.2 mm<sup>2</sup>. After calibration at room temperature (~25 °C) and at an elevated temperature (~85 °C), it achieves an inaccuracy of 0.25 °C  $(3\sigma)$  from -55 °C to 125 °C. The WB sensor dissipates 66  $\mu$ W from a 1.8-V supply and achieves a resolution of 450  $\mu K_{rms}$ in a 10-ms conversion time, which corresponds to a resolution figure-of-merit (FoM) of 0.13 pJ·K<sup>2</sup>. The sensor also achieves a sub-10-mHz 1/f noise corner, which is comparable to that of bipolar junction transistor (BJT)-based temperature sensors.

Index Terms—Calibration, hybrid sensor, phase-domain delta–sigma modulator (PD $\Delta\Sigma$ M), resistor-based sensor, temperature sensor, thermal diffusivity (TD).

#### I. INTRODUCTION

**I**NTEGRATED temperature sensors are widely used in many measurement and control systems. For such applications, two sensor specifications are critical: accuracy and energy efficiency. Accuracy defines the error of the resulting system, while energy efficiency defines the amount of energy needed to achieve a given resolution and is especially important in the case of battery-powered systems.

To combat process spread, integrated temperature sensors usually need calibration. This is typically done by comparing the sensor's output with that of an external reference sensor, for example, a Pt-100 thermistor. To minimize calibration error, the two sensors must reach a stable thermal equilibrium.

Manuscript received April 15, 2021; revised June 7, 2021; accepted June 25, 2021. This article was approved by Associate Editor Man-Kay Law. (*Corresponding author: Sining Pan.*)

Sining Pan and Kofi A. A. Makinwa are with the Electronic Instrumentation Laboratory, Microelectronics Department, Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS), Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: s.pan@tudelft.nl).

Jan A. Angevare is with SiTime, 2612 PA Delft, The Netherlands.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2021.3094166.

Digital Object Identifier 10.1109/JSSC.2021.3094166

The extra infrastructure (e.g., oil baths and ovens) and settling time needed to do this significantly increases the manufacturing cost, especially when multiple calibration temperatures are required. As a result, there is a direct tradeoff between cost and accuracy.

Most temperature sensors are based on bipolar junction transistors (BJTs) and the temperature dependency of their base-emitter voltages. With well-designed readout electronics, such sensors only require a one-point calibration to achieve inaccuracies below 0.2 °C (3 $\sigma$ ) over a 180 °C temperature range [1]–[4]. This can be done either by temperature [1], [2] or by voltage [3], [4] calibration. The latter exploits the fact that when two BJTs are biased at a stable current density ratio, the difference in their base-emitter voltages ( $\Delta V_{BE}$ ) is an accurate measure of temperature. By comparing  $\Delta V_{\rm BE}$  with an external voltage reference, the die temperature can be determined with an inaccuracy of better than 0.2 °C ( $3\sigma$ ) [4]–[6]. The use of voltage calibration obviates the need for external reference sensors and a temperature-stabilized environment, thus reducing the calibration cost. Heater-assisted voltage calibration has also been proposed [5], [6]. Here, an on-chip heater is used to elevate the die temperature above ambient, thus facilitating a rapid two-point voltage calibration, which, in turn, results in high accuracy over a wide temperature range or in the presence of the mechanical stress caused by plastic packaging.

Recently, temperature sensors based on on-chip resistors, especially silicided resistors, have been proposed [8], [9]. The latter have a large and linear temperature coefficient (TC), small 1/f noise, and a stable resistance. Sensors based on such resistors are typically one or two orders of magnitude more energy-efficient than BJT-based sensors [14]. However, since both the nominal resistance and TC of such resistors spread significantly, the resulting sensors require a two-point calibration to obtain BJT-like accuracy [8]–[10]. This is a significant drawback, limiting their use to applications where multi-point calibration is required anyway, such as in the frequency compensation of frequency references [7]–[10].

Thermal diffusivity (TD) sensors are another class of CMOS-compatible temperature sensors. They exploit the TD of bulk silicon, which is a well-defined function of temperature [15]. Such sensors can achieve 0.2 °C ( $3\sigma$ ) inaccuracy over a 180 °C temperature range without individual calibration [16]. However, despite their excellent accuracy,

0018-9200 © 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

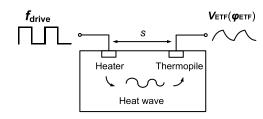

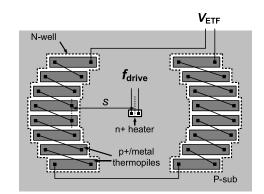

Fig. 1. TD sensor principle.

TD sensors are quite energy-inefficient, since their operation requires the injection of milliwatt-level heat pulses into the substrate.

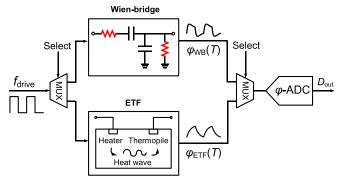

In this article, an extended version of [18], a hybrid TD/resistor-based temperature sensor is proposed. It uses an inherently accurate TD sensor to calibrate an inaccurate, but energy-efficient, resistor-based sensor. The latter is based on silicided polysilicon resistors embedded in a Wien-bridge (WB) filter, while the former is based on an electrothermal filter (ETF) made from a p-diffusion/metal thermopile and an n-diffusion heater. When driven by an external frequency reference, both the sensors generate a temperature-dependent phase shift. As a result, their readout circuit can be shared, thus reducing the chip area and complexity.

The rest of this article is organized as follows. The sensor principles and the basic structure are described in Section II. Section III discusses the design of the resistor-based sensor based on a WB filter, as well as its readout circuits. Section IV focuses on the TD sensor design and its integration with the resistor-based sensor. The measurement results are presented in Section V, and the sensor's performance is compared with the state-of-the-art. Finally, conclusion is drawn in Section VI.

#### II. SENSOR PRINCIPLES AND BASIC STRUCTURE

### A. TD Sensor

As shown in Fig. 1, the heart of a TD sensor is an ETF [15]. This consists of a heater and a relative temperature sensor (thermopile) realized in the substrate of a chip. When driven by a square-wave, the heater generates heat pulses, which propagate through the silicon substrate and cause temperature variations that are detected by the thermopile. Due to the finite and temperature-dependent TD of silicon  $D_{Si}$ , an ETF behaves like a low-pass filter [15]. In the case of a point heater and a point sensor, this phase shift is given by

$$\varphi_{\rm ETF}(\omega) = -s \sqrt{\frac{\omega}{2D_{\rm Si}}} \tag{1}$$

where  $D_{\text{Si}}$  is the TD of bulk silicon (proportional to  $T^{-1.8}$ ) and *s* is the distance between the heater and the sensor. Since  $D_{\text{Si}}$  is a material property of the highly pure substrate, and *s* is defined by lithography,  $\varphi_{\text{ETF}}$  is a well-defined function of temperature and driving frequency. With a sufficiently large *s* (24  $\mu$ m), a 3 $\sigma$  accuracy of 0.2 °C (3 $\sigma$ ) over the military temperature range (-55 °C to 125 °C) can be achieved [16].

#### B. Resistor-Based Sensor

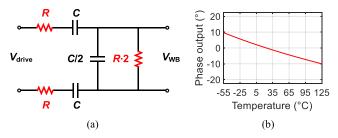

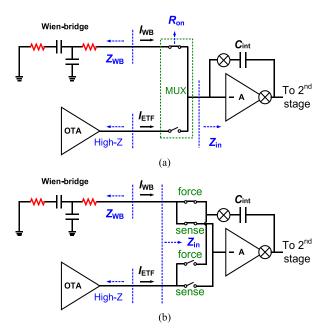

As shown in Fig. 2(a), the resistive sensor used in this design is a WB filter. It is a second-order bandpass filter, whose phase

Fig. 2. (a) WB front-end. (b) Calculated phase response over temperature.

Fig. 3. Simplified structure of the hybrid sensor.

shift can be expressed as

$$\varphi_{\rm WB}(\omega) = -\tan^{-1} \left( \frac{R^2 C^2 \omega^2 - 1}{3RC\omega} \right). \tag{2}$$

When realized from silicided polysilicon resistors (TC ~ 0.3%/°C) and metal–insulator–metal capacitors (MIM, TC ~ 50 ppm/°C), and driven at a constant  $f_{drive}$ , the filter's phase shift will vary by ~20° over the military temperature range, as shown in Fig. 2(b). This phase shift can then be digitized by a phase ADC, resulting in inaccuracies of less than 0.1 °C over a 220 °C temperature range [9], after a two-point calibration.

#### C. Hybrid Sensor

Since the outputs of both the TD and the WB sensors are in the phase domain, a single-phase ADC can be multiplexed between them, as shown in Fig. 3, thus saving area. Since the die temperature can be assumed to be quite homogeneous, the accurate TD sensor can be used to calibrate the energy-efficient WB sensor, as will be discussed in Section V-C. After calibration, the TD sensor can be turned off to save power.

#### III. WB SENSOR

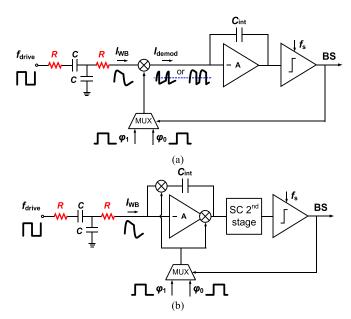

#### A. Phase-Domain Delta-Sigma Modulator

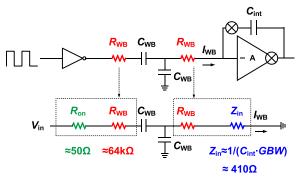

As in [9], the WB sensor is read out by a phase ADC built around a phase-domain delta-sigma modulator (PD $\Delta \Sigma M$ ). As shown in Fig. 4(a), the WB is driven by a square wave, and its phase shift is embedded in the output current  $I_{WB}$  injected into the integrator's virtual ground. The phase demodulator is realized by chopping  $I_{WB}$  with bitstream-dependent reference phases  $\phi_1$  and  $\phi_0$ . Depending on the selected phase, the demodulated current ( $I_{demod}$ ) will have a positive or negative average value. The  $\Delta \Sigma M$  will force the loop filter's average dc

Fig. 4. (a) Simplified single-ended circuit diagram of the WB readout by a PD $\Delta\Sigma$ M. (b) Circuit diagram after chopper merging and adding an SC second stage.

Fig. 5. Resistive error sources of the WB sensor.

input to zero, and thus the bitstream average will be a digital representation of the WB filter's phase shift.

To achieve high resolution within a short conversion time  $(t_{\text{conv}})$ , a feedforward compensated second-order  $\Delta \Sigma M$  is adopted. As shown in Fig. 4(b), it uses a continuous-time first stage and a discrete-time second stage for area efficiency [9]. The amplifier used in the first stage is chopped to suppress its 1/f noise. The required input chopper can be merged with the phase demodulator [8], thus simplifying the required control logic and minimizing errors due to charge injection mismatch.

The WB filter used in this design is inherited from [9], with  $R = 64 \text{ k}\Omega$ , C = 5 pF, and  $f_{\text{drive}} = 500 \text{ kHz}$ . To accommodate *RC* spread over temperature and corners, a reference phase difference of  $45^{\circ} (\phi_1 - \phi_0)$  is chosen.

#### B. First-Stage Amplifier and Biasing Circuit

As shown in Fig. 5, both the ON-resistance  $R_{\rm on}$  of the driving inverters and the input impedance of the integrator  $Z_{\rm in} \propto 1/(C_{\rm int} \cdot \text{GBW})$  are in series with the WB and may thus limit its accuracy. In [9], the first-stage amplifier is a two-stage Miller-compensated opamp based on current-reuse stages. To maximize output swing, its output stage is realized with high-Vt transistors. It is optimized for energy efficiency and

Fig. 6. (a) Loading capacitors of the first-stage amplifier with/without a buffer. (b) Two-stage amplifier and source-follower-based buffers.

achieves a GBW of ~17 MHz. With  $C_{\text{int}} = 23$  pF, this results in  $Z_{\text{in}} \sim 410 \Omega$ , which is much larger than  $R_{\text{on}}$  (~50  $\Omega$ ). As a result, the variations in the opamp's GBW, for example, due to bias current spread, will limit the sensor's accuracy.

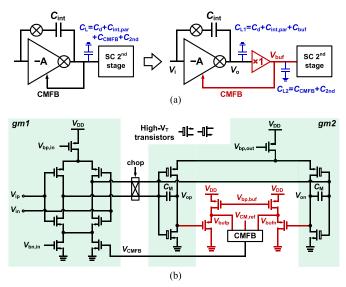

To reduce  $Z_{in}$  without increasing  $C_{int}$  (area), the GBW of the first-stage opamp should be increased. However, this should be done in a power-efficient manner. In [9], a two-stage Miller-compensated opamp is used. Its GBW is then limited by the secondary pole formed by the transconductance of its output stage (gm<sub>2</sub>) and its load capacitor ( $C_L$ ). For sufficient phase margin, the frequency of this pole (gm<sub>2</sub>/ $C_L$ ) should be  $3 \times$  larger than that of the dominant pole (~GBW), that is, gm<sub>2</sub>/ $C_L > 3 \cdot$  GBW. As shown in Fig. 6(a),  $C_L$  consists of the parasitic capacitance of the integration capacitor ( $C_{int,par}$ ), the drain capacitance of the output stage ( $C_d$ ), the input capacitance seen from the common-mode feedback (CMFB) circuit ( $C_{CMFB}$ ), and that of the SC-based second stage ( $C_{2nd}$ ).

The first two parasitic capacitances are hard to reduce. However, the loading effect of  $C_{\text{CMFB}}$  and  $C_{2nd}$  can be removed by introducing a low-power buffer realized with PMOS source followers, as shown in Fig. 6(b). Since the second stage of the PD $\Delta \Sigma M$  only processes a dc signal, the speed of the buffer is not important. It only adds ~1.1  $\mu A$  to the 16- $\mu A$  supply current of the opamp in [11], as well as negligible loading capacitance. Due to the reduced capacitive load, the opamp's GBW can be doubled by adjusting the Miller capacitances.

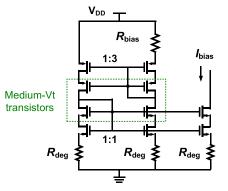

Apart from degrading the sensor's accuracy, the presence of  $Z_{in}$  also degrades the sensor's 1/f noise performance. This is because  $Z_{in}$  will be modulated by the 1/f noise present in the opamp's bias current. To minimize this, the current mirrors of its constant-Gm biasing circuit were realized with degenerated NMOS transistors, as shown in Fig. 7. These are self-cascoded by medium-Vt devices to achieve good power supply sensitivity without using an auxiliary amplifier, as in [11].

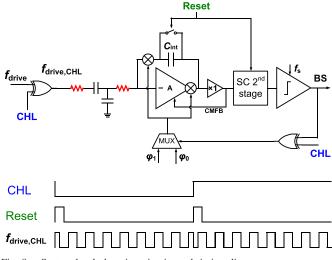

#### C. System-Level Chopping

To further suppress 1/f noise, system-level chopping is applied to the entire sensor readout. XOR-gates are used to

Fig. 7. Biasing generation circuit.

Fig. 8. System-level chopping circuits and timing diagram.

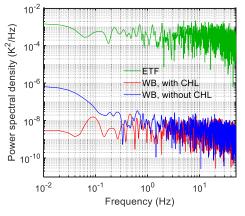

periodically invert the polarity of  $f_{\rm drive}$  at 100 Hz (CHL). To minimize settling errors, switching is done in the middle of each half period, as shown in Fig. 8. To avoid quantization noise folding, the PD $\Delta \Sigma M$  is reset at the start of each phase of system-level chopping. From simulations, the sensor's residual 1/f is ~10 mHz and is mainly limited by the biasing circuit.

#### IV. TD SENSOR AND INTEGRATION

#### A. Noise-Optimized Layout

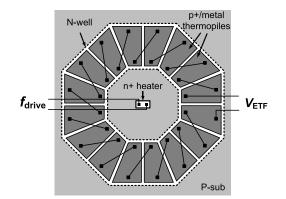

Despite achieving excellent untrimmed accuracy (0.2 °C over the military range), the TD sensor in [16] requires a relatively long conversion time (~6 s) to achieve commensurate resolution (~30 mK<sub>rms</sub>), which is too long for low-cost calibration. The sensor's resolution is mainly limited by the SNR at the output of its thermopiles, whose layout is shown in Fig. 9. In this work, a polygonal thermopile layout is used, Fig. 10 [17], resulting in 5× lower thermopile resistance (~4 k $\Omega$ ), and thus less noise. Furthermore, the sensor's heater power (4.2 mW) is nearly double that of [16], which proportionally increases the thermopile output (~500  $\mu$ V). Together, these measures result in higher resolution (~10 mK) in a much shorter (1 s) conversion time.

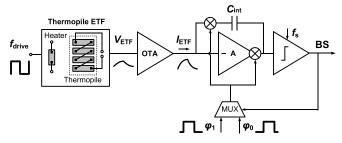

#### B. AZed GM Stage

As shown in Fig. 11, an operational transconductance amplifier (OTA) is used to convert the output of the ETF into a

Fig. 9. ETF with a phase-contour thermopile layout [16].

Fig. 10. ETF with an octagonal thermopile layout [17].

Fig. 11. Simplified single-ended circuit diagram of the ETF readout. System-level chopping and the SC second stage are not shown.

current that is subsequently applied to the first integrator of a PD $\Delta \Sigma M$ . In contrast to [16], the phase demodulation is now done after the OTA, as this allows the same PD $\Delta \Sigma M$  to be used for both the WB and TD sensors. As a result, the OTA now needs to be fast enough to avoid adding significant phase errors to the ETF's output phase.

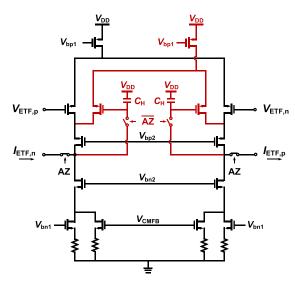

In this work, a telescopic OTA is used (Fig. 12). Compared with the folded-cascode OTA used in [16], it is faster and more power-efficient. It uses PMOS input transistors and resistor-degenerated NMOS current sources to ensure that its 1/f noise corner is lower than the intended ETF driving frequency  $f_{\text{drive}}$  (~30 kHz). Also, it has a large gm (~0.9 mS) and bandwidth (~600 MHz from simulation), which ensures that its thermal noise floor is lower than that of the ETF, and its phase delay contributes negligible phase error.

The offset of the OTA needs to be suppressed, since it will be up-modulated by the phase demodulator in the PD $\Delta \Sigma M$ and the resulting ripple will limit the swing at the output of its first integrator. To suppress its offset, the OTA is auto-zeroed

Fig. 12. Simplified schematic of the auto-zeroed OTA.

with the help of an auxiliary amplifier [Fig. 12 (red)]. This is implemented with long devices in strong inversion, resulting in a small transconductance (gm ~ 0.06 mS) and a negligible contribution to the main OTA's thermal noise. Due to the use of large hold capacitors ( $C_{\rm H} \sim 7$  pF) and lowleakage minimum-size AZ switches, the OTA only needs to be auto-zeroed once at the start of each TD sensor conversion. The OTA consumes ~500  $\mu$ A from a 1.8-V supply, of which about 20% is due to the auxiliary amplifier.

#### C. Kelvin Connection and Integration

A multiplexer is required to connect either the WB sensor or the TD sensor to the input of the PD $\Delta \Sigma M$ . A straightforward multiplexer would only involve two switches, as shown in Fig. 13(a). However, this will introduce an extra switch resistance ( $R_{on}$ ) in series with the WB filter, whose spread will then degrade the filter's accuracy.

In this work, the  $R_{on}$  error is removed by Kelvin connections, as shown in Fig. 13(b). In this configuration, almost no current flows through the sense switches, while the force switches, like the chopper switches, are in the feedback loop of the first integrator. In this way, the multiplexer's switch resistance has a negligible effect on the WB filter's accuracy.

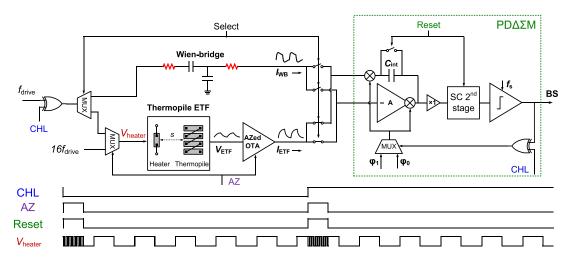

#### D. System Operation

Fig. 14 shows the complete circuit diagram of the hybrid sensor and the timing of signals in the TD sensor mode. To further suppress the residual offset of the AZed amplifier and the charge injection of the demodulating choppers, the entire signal path is chopped once per conversion (CHL). The AZ signal, together with the reset signal of the PD $\Delta \Sigma M$ , is triggered at the start of each CHL phase (0.5 s each). To reduce its ac output during AZ, which will appear as noise, while preserving its dc output, the ETF is driven at a higher frequency ( $16 \cdot f_{drive}$ ). The driving frequencies and phase references required by the WB and TD filters are derived from an external frequency reference by on-chip divider with a phase step of 22.5°. Different reference frequencies are used for WB/TD modes.

Fig. 13. Sensor integration using (a) multiplexer connection and (b) Kelvin connection.

#### V. MEASUREMENT RESULTS

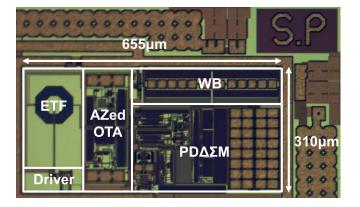

The sensor is fabricated in a standard  $0.18-\mu m$  CMOS technology. Four hybrid sensors were implemented per die, with identical WB sensors and readout circuits but different ETF test structures. The micrograph of one sensor is shown in Fig. 15. In TD mode, each sensor consumes 5.1 mW (4.2-mW heater, 0.9-mW analog, and  $0.6-\mu W$  digital) from a 1.8-V supply. In the WB mode, the heater and the OTA are turned off, and its power consumption drops to 66  $\mu W$  at room temperature (RT). The sensor has an active area of 0.2 mm<sup>2</sup>, of which ~40% is occupied by the ETF and OTA. For flexibility, the decimation filters (sinc<sup>2</sup>) are implemented off-chip. At RT, dc supply sensitivities of 0.27 °C/V (WB) and 0.4 °C/V (ETF) were observed for a supply voltage range from 1.6 to 2 V. The latter is mainly due to the sensor's self-heating.

#### A. Sensor Characteristic Without Calibration

Twenty samples from one wafer in ceramic dual in-line packages were characterized from -55 °C to 125 °C in a temperature-controlled oven (Vötsch VT7004). To suppress the effects of oven drift, the chips were mounted in good thermal contact with a large metal block, and a calibrated Pt-100 was used as the temperature reference.

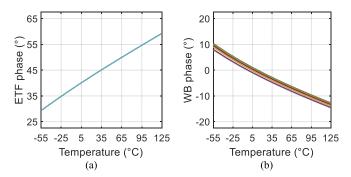

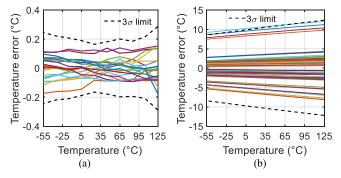

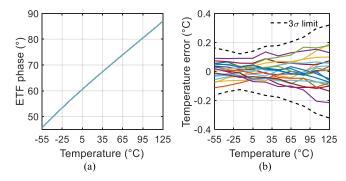

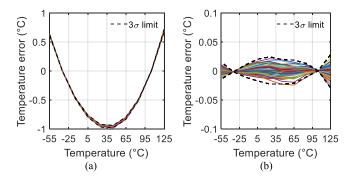

Fig. 16 shows the ETF/WB sensor characteristic at driving frequencies of 31.25/500 kHz and phase digital-to-analog converter (DAC) ranges of  $[22.5^{\circ}, 67.5^{\circ}]/[-22.5^{\circ}, 22.5^{\circ}]$ , respectively. Within a batch, the spread of the ETF sensor is much less than that of the WB sensor. After correcting its systematic nonlinearity (SNL) with a fixed fifth-order polynomial, the ETF sensor achieves an untrimmed inaccuracy of less than 0.2 °C ( $3\sigma$ ) at RT, as shown in Fig. 17(a). The inaccuracy of the WB sensor is much worse, being about 10 °C ( $3\sigma$ ).

The main sources of error in the TD sensor are expected to be self-heating and extra delay due to the limited bandwidth

Fig. 14. Simplified circuit diagram of the hybrid sensor and its timing diagram under the TD mode.

Fig. 15. Chip photograph of the fabricated sensor.

Fig. 16. Phase output characteristic of (a) TD and (b) WB temperature sensors.

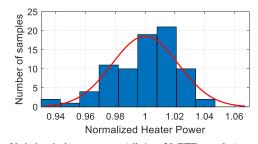

of the front-end. To investigate the effect of self-heating, the heater power dissipation of all the samples (4  $\times$  20) was measured, as shown in Fig. 18. The  $3\sigma$  variation is about  $\sim$ 0.3 mW within a batch. Together with the estimated thermal impedance of a ceramic package ( $\sim$ 60 °C/W), this translates into less than 0.02 °C of self-heating error. To examine the effect of electrical delay of the ETF front-end and the PD $\Delta\Sigma M$ , its driving frequency was approximately doubled (60 kHz), which would be expected to double the effect of any electrical delay. As shown in Fig. 19, although the ETF's phase sensitivity increases (by  $\sim$ 30%), the RT error

Fig. 17. Temperature error of (a) TD and (b) WB temperature sensors.

Fig. 18. Variation in heater power (all  $4 \times 20$  ETF samples).

Fig. 19. (a) Phase output characteristic. (b) Temperature error of the TD sensor with  $f_{\rm drive}$  of 60 kHz.

remains almost the same, implying that electrical delay is not a significant contributor. It should be noted that since the output amplitude of the ETF is now smaller, increasing the sensor's drive frequency actually reduces its resolution slightly.

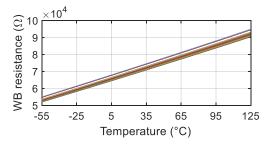

Fig. 20. Calculated resistance over temperature of the WB sensors.

Fig. 21. WB sensor error after (a)  $\mu$ -*R* mapping and two-point calibration and (b)  $\mu$ -*R* mapping, two-point calibration, and systematic error removal.

#### B. Temperature Calibration

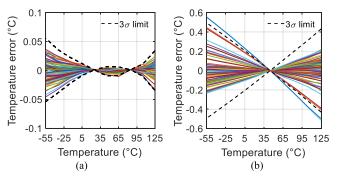

Traditionally, WB sensors are temperature-calibrated. To achieve the best inaccuracy after trimming, the nonlinearity of the WB and that of the PD $\Delta \Sigma$ M was first removed by a fixed seventh-order polynomial that maps the bitstream average to the WB resistance ( $\mu$ -R mapping), as shown in Fig. 20. As in [8] and [9], this polynomial is determined from simulation, assuming ideal PD $\Delta \Sigma$ M and temperature-independent WB capacitors (5 pF). Afterward, the sensor is trimmed at -35 °C and 105 °C. As shown in Fig. 21(a), the remaining error, which is mainly due to the sensing resistor's higher order TC, is quite systematic and can be corrected by a fixed fourth-order polynomial obtained from batch calibration [8], [9]. Finally, the WB sensor achieves a  $3\sigma$  error of 0.03 °C over a 180 °C temperature range, as shown in Fig. 21(b).

In a production environment, temperature calibration below RT and above 100 °C is both difficult, because the former requires a cooling system, while the latter requires either an oil bath or a temperature-controlled oven. To reduce the calibration cost, the WB sensors can be calibrated at 25 °C and 85 °C, at the expense of a slight degradation in inaccuracy: 0.05 °C ( $3\sigma$ ), as shown in Fig. 22(a). Alternatively, a correlation-based single-point calibration [8] can be used. Unfortunately, this results in much worse inaccuracy: ~0.5 °C ( $3\sigma$ ) over the same temperature range, as shown in Fig. 22(b).

#### C. Self-Calibration

For self-calibration, the TD sensor is used to calibrate the WB sensor. Since both the sensors are on the same die and thus are at the same temperature, the strict temperature settling requirement of traditional temperature calibration can

Fig. 22. WB sensor error after (a) two-point calibration at 25  $^\circ C$  and 85  $^\circ C$  and (b) one-point calibration at 45  $^\circ C.$

Fig. 23. WB sensor error after (a) two-point self-calibration at 25  $^{\circ}$ C and 85  $^{\circ}$ C, (b) 1-pt trim at 25  $^{\circ}$ C and a 1-pt self-calibration at 85  $^{\circ}$ C, and (c) 1-pt self-calibration at 45  $^{\circ}$ C.

be greatly relaxed. In fact, the temperature at which the sensor is calibrated does not need to be well-defined.

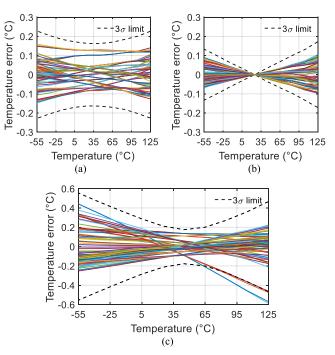

To minimize calibration time, the WB/TD sensors are first read out at room temperature, and then at an elevated temperature ( $\sim$ 85 °C). This results in a WB inaccuracy of 0.25 °C (3 $\sigma$ ), as shown in Fig. 23(a).

As a compromise between calibration cost and accuracy, the hybrid sensor could be temperature-calibrated at RT, which allows the TD sensor to be offset-trimmed before it is used to calibrate the WB sensor at an elevated temperature. Compared with normal two-point temperature calibration, this method only requires a temperature-stabilized environment at RT, which is easier to achieve. The result is a somewhat improved WB inaccuracy of 0.15 °C, as shown in Fig. 23(b). With only a one-point self-calibration, an inaccuracy of 0.6 °C is achieved, which is slightly worse than obtained with a one-point temperature calibration, as shown in Fig. 23(c).

|                                                             | van Vroonhoven<br>ISSCC'10 [16]            | Souri<br>JSSC'13 [4] | Yousefzadeh<br>ISSCC'17 [5]                                        | Pan<br>JSSC'18 [8] | Pan<br>ISSCC'19 [9] | This work            |                   |             |

|-------------------------------------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------------------|--------------------|---------------------|----------------------|-------------------|-------------|

| Sensor type                                                 | Thermal diffusion                          | BJT                  | BJT                                                                | Resistor<br>WB     | Resistor<br>WB      | Thermal<br>diffusion | Resistor<br>WB    |             |

| CMOS Technology                                             | 0.18µm                                     | 0.16µm               | 0.16µm                                                             | 0.18µm             | 0.18µm              | 0.18µm               |                   |             |

| Area (mm <sup>2</sup> )                                     | 0.18                                       | 0.08                 | 0.17                                                               | 0.72               | 0.12                | 0.20                 |                   |             |

| Temperature range                                           | -55°C to<br>125°C                          | −55°C to<br>125°C    | −55°C to<br>125°C                                                  | -40°C to<br>85°C   | -40°C to<br>180°C   | -15°C to<br>105°C    | -55°C to<br>125°C |             |

| 3σ inaccuracy (°C)<br>(Temp. trimming points <sup>a</sup> ) | 0.2                                        | 0.15 <sup>b</sup>    | 0.3 <sup>b</sup>                                                   | 0.03<br>(2)        | 0.1<br>(2)          | 0.2                  | 0.25              | 0.03<br>(2) |

| 1/f noise corner (Hz)                                       |                                            |                      |                                                                    | <1                 | ~1                  |                      | <0.01             |             |

| Power (mW)                                                  | 3                                          | 0.005                | 0.007                                                              | 0.16               | 0.052               | 5.1                  | 0.066             |             |

| Conversion time (ms)                                        | 6250                                       | 5.3                  | 5                                                                  | 5                  | 10                  | 1000                 | 10                |             |

| Resolution (mK)                                             | 20                                         | 20                   | 15                                                                 | 0.41               | 0.46                | 15                   | 0.45              |             |

| Resolution FoM (pJ·K <sup>2</sup> ) <sup>c</sup>            | $7.5 \times 10^{6}$                        | 11                   | 7.8                                                                | 0.13               | 0.11                | 1.2×10 <sup>6</sup>  | 0.13              |             |

| <sup>a</sup> Trimming points that requir                    | <sup>b</sup> Requires a voltage reference. |                      | $^{\circ}$ FoM = Energy / Conversion × (Resolution) <sup>2</sup> . |                    |                     |                      |                   |             |

TABLE I PERFORMANCE SUMMARY AND COMPARISON TO PRIOR ART

Fig. 24. Noise power spectral densities of the WB and TD sensors.

#### D. Resolution and FoM

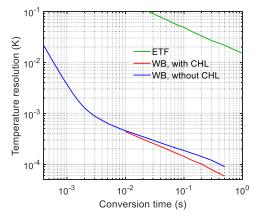

After decimated by sinc<sup>2</sup> filters, the sensors' power spectral densities (100-s interval, Hanning window, 3× averaging) are shown in Fig. 24, and the corresponding resolution versus conversion time plots are shown in Fig. 25. To accurately determine the WB sensor resolution, a differential measurement is used, that is, it is calculated from the standard deviation of the output difference between two identical sensors on the same die. The WB sensor achieves 450  $\mu$ K<sub>rms</sub> resolution with  $T_{\rm conv} = 10$  ms with a 1-s interval, which corresponds to a 0.13-pJ·K<sup>2</sup> resolution figure-of-merit (FoM). After enabling system-level chopping ( $f_{CHL} = 100 \text{ Hz}$ ), its 1/f noise corner drops from  $\sim 1$  Hz to below 10 mHz. In comparison, the TD sensor's resolution is only 15 mK with  $T_{\text{conv}} = 1$  s and  $f_{\text{CHL}} =$ 1 Hz, which corresponds to a resolution FoM of 1.2  $\mu$ J·K<sup>2</sup>.

#### E. Comparison to Previous Work

Table I summarizes the performance of the proposed hybrid sensor prototype and compares it with previous WB sensors [8], [9] as well as other sensors with low-cost calibration (BJT [4], [5] or TD [16]). Compared with previous WB sensors, this work achieves a state-of-the-art relative inaccuracy after a 2-pt temperature calibration and the lowest

Fig. 25. Resolution versus conversion time of different sensors.

reported 1/f noise corner, while the resolution FoM remains roughly the same. After a cost-effective heating-assisted self-calibration that does not require accurate temperature information, this sensor achieves an inaccuracy of 0.25 °C from -55 °C to 125 °C (3 $\sigma$ ), which is comparable to that of the voltage-calibrated BJT sensors. Although slightly less accurate than the state-of-the-art TD sensor [16], this sensor is  $6 \times$  more energy-efficient. More importantly, it can achieve sufficient resolution for self-calibration with a short conversion time of 1 s. It is also worth noting that this work serves as a prototype of the TD/resistor hybrid temperature sensor. Due to the scalability of TD sensors, better performance can be expected in nanometer CMOS processes.

#### VI. CONCLUSION

A hybrid TD/resistor-based temperature sensor has been realized in a standard 0.18-µm CMOS technology. By self-calibrating an inaccurate, but energy-efficient, resistor-based sensor using an inherently accurate, but power-hungry, TD sensor, the hybrid sensor achieves both high energy efficiency and decent accuracy. As the need for external references and temperature-stabilized environments is obviated by the use of an on-chip reference, calibration time and costs can be greatly reduced. Also, the chip area overhead

is suppressed by reusing the PD $\Delta\Sigma$ M readout circuit. The sensor dissipates 66  $\mu$ W from a 1.8-V supply and achieves an inaccuracy of 0.25 °C (3 $\sigma$ ) from -55 °C to 125 °C after self-calibration at room temperature (RT, ~25 °C) and an elevated temperature (~85 °C). It also achieves a sub-10-mHz 1/*f* noise corner and a resolution FoM of 0.13 pJ·K<sup>2</sup>.

#### ACKNOWLEDGMENT

The authors would like to thank Z.-Y. Chang, L. Pakula, and R. van Puffelen, for their assistance with the measurements.

#### REFERENCES

- [1] M. A. P. Pertijs, K. A. A. Makinwa, and J. H. Huijsing, "A CMOS smart temperature sensor with a  $3\sigma$  inaccuracy of  $\pm 0.15$  °C from -55 °C to 125 °C," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2805–2815, Dec. 2005.

- [2] B. Yousefzadeh, S. H. Shalmany, and K. A. A. Makinwa, "A BJTbased temperature-to-digital Converter with ±60mK (3σ) Inaccuracy from -55°C to +125°C in 0.16µm Standard CMOS," *IEEE J. Solid-State Circuits*, vol. 52, is. 4, pp. 1044–1052, Apr. 2017.

- [3] M. A. P. Pertijs, A. L. Aita, K. A. A. Makinwa, and J. H. Huijsing, "Low-cost calibration techniques for smart temperature sensors," *IEEE Sensors J.*, vol. 10, no. 6, pp. 1098–1105, Jun. 2010.

- [4] K. Souri, Y. Chae, and K. A. A. Makinwa, "A CMOS temperature sensor with a voltage-calibrated inaccuracy of ±0.15°C (3σ) from -55°C to 125°C," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 292–301, Jan. 2013.

- [5] B. Yousefzadeh and K. A. A. Makinwa, "9.3 A BJT-based temperature sensor with a packaging-robust inaccuracy of ±0.3°C (3σ) from -55°C to +125°C after heater-assisted voltage calibration," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 162–163.

- [6] B. Yousefzadeh and K. A. A. Makinwa, "A BJT-based temperatureto-digital converter with a ±0.25 °C 3σ -Inaccuracy from -40 °C to +180 °C using heater-assisted voltage calibration," *IEEE J. Solid-State Circuits*, vol. 55, no. 2, pp. 369–377, Feb. 2020.

- [7] P. Park, D. Ruffieux, and K. A. A. Makinwa, "A thermistor-based temperature sensor for a real-time clock with ± 2ppm frequency stability," *IEEE J. Solid-State Circuits*, vol. 50, no. 7, pp. 1571–1580, Jul. 2015.

- [8] S. Pan, Y. Luo, S. H. Shalmany, and K. A. A. Makinwa, "A resistorbased temperature sensor with a 0.13 pJ·K<sup>2</sup> resolution FoM," *IEEE J. Solid-State Circuits.*, vol. 53, no. 1, pp. 164–173, Jan. 2018.

- [9] S. Pan, C. Gurleyuk, M. F. Pimenta, and K. A. A. Makinwa, "10.3 A 0.12 mm<sup>2</sup> wien-bridge temperature sensor with 0.1°C (3σ) inaccuracy from -40°C to 180°C," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 184–186.

- [10] S. Pan and K. A. A. Makinwa, "A 10 fJ·K<sup>2</sup> wheatstone bridge temperature sensor with a tail-resistor-linearized OTA," *IEEE J. Solid-State Circuits*, vol. 56, no. 2, pp. 501–510, Feb. 2021.

- [11] K. Pelzers, H. Xin, E. Cantatore, and P. Harpe, "A 2.18-pJ/conversion, 1656-μm<sup>2</sup> temperature sensor with a 0.61-pJ·K<sup>2</sup> FoM and 52-pW standby power," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 82–85, 2020.

- [12] Y. Lee, W. Choi, T. Kim, S. Song, K. A. A. Makinwa, and Y. Chae, "A 5800- $\mu$ m<sup>2</sup> resistor-based temperature sensor with a one-point trimmed inaccuracy of ±1.2 °C (3 $\sigma$ ) from -50 °C to 105 °C in 65-nm CMOS," *IEEE Solid-State Circuits Lett.*, vol. 2, no. 9, pp. 67–70, Sep. 2019.

- [13] J. A. Angevare, Y. Chae, and K. A. A. Makinwa, "5.3 A highly digital 2210μm<sup>2</sup> resistor-based temperature sensor with a 1-Point trimmed inaccuracy of ± 1.3 °C (3σ) from -55 °C to 125 °C in 65nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 76–78.

- [14] K. A. A. Makinwa. Smart Temperature Sensor Survey. Accessed: Apr. 15, 2021. [Online]. Available: http://ei.ewi.tudelft.nl/ docs/TSensor\_survey.xls

- [15] C. P. L. van Vroonhoven and K. A. A. Makinwa, "Thermal diffusivity sensing: A new temperature sensing paradigm," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2011, pp. 1–6.

- [16] C. P. L. van Vroonhoven and K. A. A. Makinwa, "A thermal-diffusivitybased temperature sensor with an untrimmed inaccuracy of ±0.2°C (3σ) from -55 to 125°C," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2010, pp. 314–315.

- [17] U. Sonmez, F. Sebastiano, and K. A. A. Makinwa, "Compact thermaldiffusivity-based temperature sensors in 40-nm CMOS for SoC thermal monitoring," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 834–843, Mar. 2017.

- [18] S. Pan, J. A. Angevare, and K. A. A. Makinwa, "5.4 a hybrid thermaldiffusivity/resistor-based temperature sensor with a self-calibrated inaccuracy of ±0.25° C(3σ) from -55°C to 125°C," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2021, pp. 78–79.

**Sining Pan** (Graduate Student Member, IEEE) was born in Beijing, China, in 1991. He received the B.Sc. degree in electronic engineering from Tsinghua University, Beijing, in 2013, and the M.Sc. and Ph.D. degrees in electrical engineering both (cum laude) from Delft University Technology, Delft, The Netherlands, in 2016 and 2021, respectively. He is now a Post-Doctoral Researcher with the Electronic Instrumentation Laboratory, Delft University of Technology. His research interests include smart sensors, CMOS frequency references,

and  $\Delta \Sigma$  modulators.

Dr. Pan was a recipient of the ADI Outstanding Student Designer Award (2019) and the IEEE SSCS Pre-Doctoral Achievement Award (2020). He serves as a reviewer for the JSSC, TCAS-I, TCAS-II, TIM, Sensors Journal, and T-VLSI.

Jan A. Angevare (Graduate Student Member, IEEE) was born in Leiden, The Netherlands, in 1990. He received the B.Sc. and M.Sc. degrees in electrical engineering from the Delft University of Technology, Delft, The Netherlands, in 2012 and 2015, respectively, where he is currently pursuing the Ph.D. degree.

His research interests include mixed-signal design and smart sensors.

Kofi A. A. Makinwa (Fellow, IEEE) received the B.Sc. and M.Sc. degrees from Obafemi Awolowo University, Ife, Nigeria, in 1985 and 1988, respectively, the M.E.E. degree from the Philips International Institute, Eindhoven, The Netherlands, in 1989, and the Ph.D. degree from the Delft University of Technology, Delft, The Netherlands, in 2004.

From 1989 to 1999, he was a Research Scientist with Philips Research Laboratories, Eindhoven, The Netherlands, where he worked on interactive displays and digital recording systems. In 1999, he

joined the Delft University of Technology, where he is currently an Antoni van Leeuwenhoek Professor and the Head of the Microelectronics Department. His research interests include the design of mixed-signal circuits, sensor interfaces, and smart sensors. This has led to 16 books, over 300 technical papers, and over 30 patents.

Dr. Makinwa has been on the program committees of several IEEE conferences, and was the Analog Subcom Chair of ISSCC. He has also served the Solid-State Circuits Society as a Distinguished Lecturer and as an Elected Member of its Adcom. He is currently one of the organizers of the Advances in Analog Circuit Design Workshop and the Sensor Interfaces Meeting. He is an ISSCC top-10 contributor, and a co-recipient of 16 best paper awards, from the JSSC, ISSCC, VLSI, ESSCIRC, and Transducers, among others. He is a member of the Royal Netherlands Academy of Arts and Sciences.