# Design of a Readout Scheme for a MEMS Microphone

**Ameng Cheng**

Submitted to the Electrical Engineering, Mathematics and Computer Science Department of Delft University of Technology, in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

> TU Delft Supervisor: **Prof. Kofi A.A. Makinwa**

NXP Supervisors: Robert H.M. van Veldhoven Twan van Lippen Geert Langereis

## Abstract

This design mainly proposes a readout scheme for MEMS microphone with positive feedback to decrease the parasitic capacitance. It is designed in CMOS014 technology with a supply voltage of 3.3 V. The proposed architecture can increase the microphone's sensitivity with a comparatively low bias voltage. It enables the microphone to achieve high sensitivity even if it is loaded by an amplifier with large input capacitance. In the mean time, the SNR and THD are not affected much. The Spectre simulation shows that the system can achieve 61 dB SNR (A-weighted), 0.5% THD (1Pa sound pressure) and 1 mW power consumption. Several traditional readout schemes for MEMS microphone are also discussed and compared. The scheme which is based on amplitude modulation is tested and measured on PCB level.

## Acknowledgement

I would like to express my gratitude to all those who give me the opportunity to complete the research. The achievement I have made through this project would not have been possible without the enlightenment, support and encouragement from a lot of people.

I started the one-year research in NXP Semiconductors from September 1, 2008 as my graduation project of Delft University of Technology. Thanks a lot to my professor Kofi A.A. Makinwa from TUDelft, my supervisors Robert H.M. van Veldhoven, Twan van Lippen and Geert Langereis from NXP Semiconductors. They provided me this opportunity to have a close vision about MEMS world and the analog circuit design.

Special thanks are given to my daily supervisor Mr. Robert van Veldhoven, a talented and professional engineer, who gave me a lot of important guidance in this research. He can point out my mistakes in the very first time and in this way he helps me set up a strict attitude to science which is beneficial to my future work. He gives me a free atmosphere to do the research without too much pressure. His encouragements in the proper time help me go through the darkest period of the project.

I also want to thank my professor Dr. Kofi Makinwa who has provided me with a large number of important and stimulating suggestions which helps me to know the intrinsic nature behind the problems. Not only he gave me directions in the project but he also gave me instructions about how to be a good engineer.

In addition, I want to thank Mr. Twan van Lippen and Mr. Geert Langereis who always provide me with the most detailed and professional answers to my questions. Their positive attitude to my work gives me a lot of confidence. I also want to thank Mr. Carel Dijkmans for his valuable and experienced suggestions on this project. In the mean time, I want to thank Ms. Agnese Bargagli-Stoffi for her patience and friendly manners when dealing with my questions.

Although I did not spend a lot of time with my friends and group members in TUDelft in the past year, I still want to thank them for their help and valuable input to this project. Special thanks are given to Rong Wu and Qinwen Fan who spend time to review my thesis and give me important feedback. Thanks also go to my friends in Shanghai. Their caring between whiles make me feel attached to each other.

Last but no least, I would like to thank my parents and my little sister. Their unconditional love, support and encouragements enable me to finish this work. The thesis is dedicated to them.

| CHAPTER 1. INTRODUCTION                                                                     | 1  |

|---------------------------------------------------------------------------------------------|----|

| 1.1 What is a MEMS Microphone?                                                              | 1  |

| 1.2 Characteristics of the Microphone from NXP                                              | 3  |

| 1.3 Sensitivity                                                                             | 5  |

| 1.4 VerilogA Model for Microphone from NXP                                                  | 7  |

| <b>1.5 Specification to be Achieved</b> 1.5.1 Sound Pressure Level         1.5.2 A-weighted | 9  |

| 1.6 Motivation                                                                              |    |

| 1.7 Outline of the Thesis                                                                   | 11 |

| CHAPTER 2. READOUT SCHEME                                                                   | 12 |

| 2.1 Read-out schemes for Capacitive Microphone                                              | 12 |

| 2.2 DC Biasing                                                                              | 15 |

| 2.2.1 Signal Level                                                                          |    |

| 2.2.2 Noise Calculation                                                                     | 16 |

| 2.3 Charge Amplifier                                                                        |    |

| 2.3.1 Signal Level                                                                          |    |

| 2.3.2 Noise Calculation                                                                     |    |

| 2.4 AC Biasing                                                                              | 19 |

| 2.4.1 Signal Level                                                                          |    |

| 2.4.2 Noise Calculation                                                                     |    |

| 2.5 Practical Measurement                                                                   |    |

| 2.5.1 Amplitude Modulation                                                                  |    |

| 2.5.2 AC Biasing Setup                                                                      |    |

| 2.5.3 Noise Analysis                                                                        |    |

| 2.5.4 Check Functionality<br>2.5.5 Conclusion                                               |    |

|                                                                                             |    |

| 2.6 Conclusion                                                                              |    |

| CHAPTER 3. NEW READOUT SCHEME WITH POSITIVE FEEDBACK                                        | 35 |

| 3.1 Miller Effect                                                                           | 34 |

|                                                                                             |    |

| 3.2 Miller Effect in DC Biasing                                                             |    |

| 3.3 System Level Analysis                                                                   |    |

| 3.3.1 Define the Gain of the Preamplifier                                                   |    |

| 3.3.2 Diode Connected MOSFET                                                                |    |

# Content

| 3.3.3 Stability                                                                      | 41 |

|--------------------------------------------------------------------------------------|----|

| 3.4 Specification for Preamplifier                                                   | 42 |

| 3.5 Conclusion                                                                       | 43 |

| CHAPTER 4. PREAMPLIFIER DESIGN                                                       | 44 |

| 4.1 Amplifier Topology                                                               | 44 |

| 4.2 Noise Analysis in Folded-Cascode Amplifier                                       |    |

| 4.3 Reference Current Source                                                         | 49 |

| 4.4 Size of the Devices in the Preamplifier                                          | 51 |

| CHAPTER 5. SYSTEM IMPLEMENTATION                                                     | 54 |

| 5.1 Parasitic Capacitance                                                            | 54 |

| 5.2 Stability Check by AC Simulation                                                 | 55 |

| 5.3 Programmable C <sub>f</sub>                                                      | 56 |

| 5.4 Conclusion                                                                       | 59 |

| CHAPTER 6. SIMULATION RESULT                                                         | 60 |

| 6.1 Stability Check by Transient Simulation                                          | 60 |

| 6.2 Signal-to-Noise Ratio                                                            | 62 |

| 6.3 Total Harmonic Distortion                                                        | 62 |

| 6.4 Sensitivity                                                                      | 63 |

| 6.5 Process Corners Simulation                                                       |    |

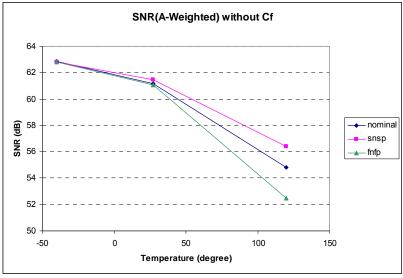

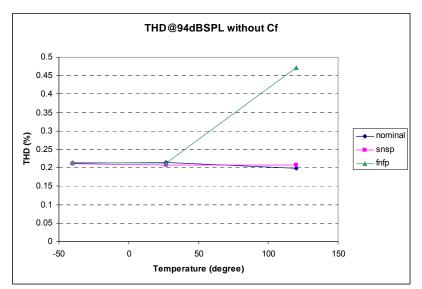

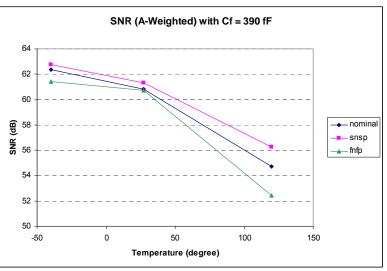

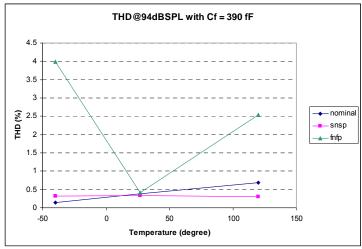

| 6.5.1 Corner Simulation without $C_f$<br>6.5.2 Corner Simulation with $C_f$ = 390 fF |    |

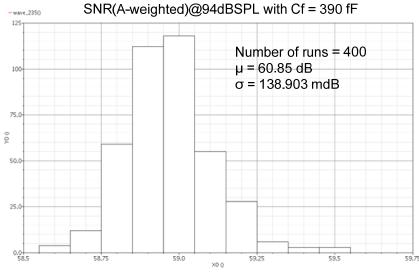

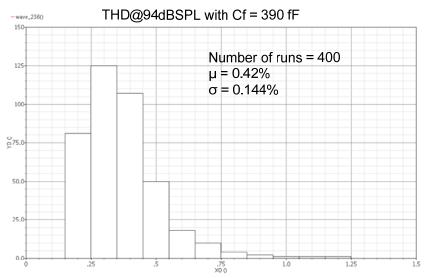

| 6.6 Monte-Carlo Simulation                                                           | 66 |

| 6.7 Comparison                                                                       | 67 |

| 6.8 Conclusion                                                                       | 68 |

| CHAPTER 7 CONCLUSION AND FUTURE WORK                                                 | 69 |

| 7.1 Conclusion                                                                       | 69 |

| 7.2 Future Work                                                                      | 69 |

|                                                                                      | 71 |

| APPENDIX B |  |

|------------|--|

|            |  |

| APPENDIX C |  |

# List of Figures

| Figure 1. 1 The cross-sectional view of a typical MEMS capacitive microphone           | 2    |

|----------------------------------------------------------------------------------------|------|

| Figure 1. 2 Cross-sectional view of Bourouina et al.'s condenser microphone [9]        |      |

| Figure 1. 3 Spring supported membrane [11].                                            | 3    |

| Figure 1. 4 Topview on the back electrode side.                                        | 3    |

| Figure 1. 5 Cross section of the microphone.                                           |      |

| Figure 1. 6 Force diagram of a microphone in equilibrium.                              |      |

| Figure 1. 7 Capacitance variance with different voltage                                |      |

| Figure 1.8 Membrane's deflection without bias voltage.                                 |      |

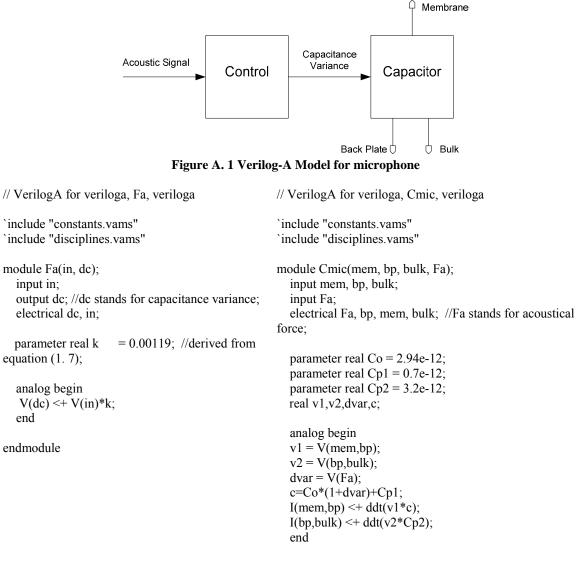

| Figure 1. 9 VrilogA Model for Microphone                                               |      |

| Figure 1. 10 A-weighting Curve                                                         |      |

|                                                                                        |      |

| Figure 2. 1 Traditional readout scheme for ECM.                                        | .12  |

| Figure 2. 2 Typical voltage-readout scheme for MEMS capacitive microphone [20]         |      |

| Figure 2. 3 Scheme of the integrated capacitive microphone with dc-dc voltage          |      |

| converter and preamplifier [6].                                                        | .13  |

| Figure 2. 4 Schematic of the preamplifier used in [22].                                |      |

| Figure 2. 5 Scheme of the integrated microphone by using frequency modulation [23].    |      |

| Figure 2. 6 DC biasing scheme.                                                         |      |

| Figure 2. 7 Noise sources in DC biasing scheme                                         |      |

| Figure 2. 8 Charge Amplifier.                                                          |      |

| Figure 2.9 V <sub>out</sub> 's amplitude versus radio frequency                        |      |

| Figure 2. 10 Noise Source in Charge Amplifier                                          |      |

| Figure 2. 11 AC biasing scheme.                                                        |      |

| Figure 2. 12 Spectrum of the amplitude modulated signal.                               |      |

| Figure 2. 13 Mixer demodulation.                                                       |      |

| Figure 2. 14 (a) Scheme for realizing amplitude modulation. (b) Frequency response o   |      |

| the transfer function.                                                                 |      |

| Figure 2. 15 Amplitude-modulated signal's spectrum                                     | .24  |

| Figure 2. 16 Magnitude of the side band under different bias voltage.                  |      |

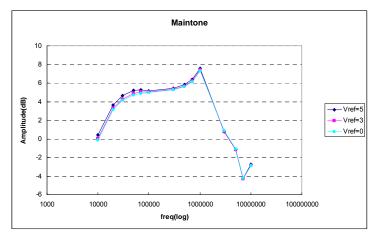

| Figure 2. 17 Magnitude of the main tone under different bias voltage                   |      |

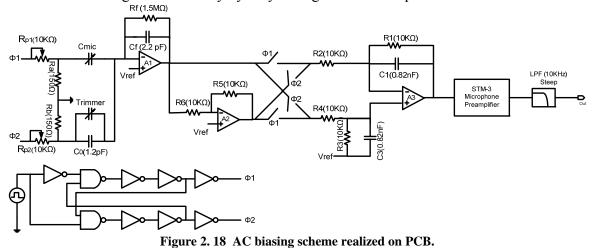

| Figure 2. 18 AC biasing scheme realized on PCB.                                        |      |

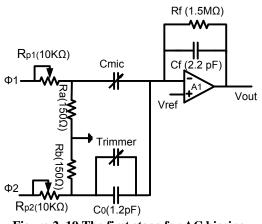

| Figure 2. 19 The first stage for AC biasing.                                           | .27  |

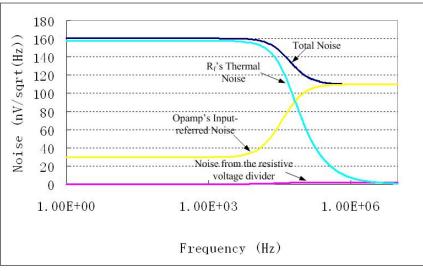

| Figure 2. 20 Noise versus frequency for the first stage of AC biasing                  | .28  |

| Figure 2. 21 Comparison of the noise measurement and calculation result for AC biast   | ing. |

|                                                                                        |      |

| Figure 2. 22 Response to oscillation frequency with different oscillation amplitude in |      |

| normal mode.                                                                           | .29  |

| Figure 2. 23 Equivalent voltage's waveform exerted on the microphone under two cas     | es.  |

|                                                                                        |      |

| Figure 2. 24 Different average sensitivity in two cases.                               | .30  |

| Figure 2. 25 Demodulated signal in normal mode                                         | .31  |

| Figure 2. 26 Comparison of frequency response between normal mode and collapse         |      |

| mode                                                                                   | .31  |

| Figure 2. 27 The nonlinear demodulated signal in collapse mode at 100KHz oscillation   |      |

| frequency                                                                              |      |

| Figure 2. 28 The demodulated signal in collapse mode at 120KHz oscillation frequent                                              | ncy. |

|----------------------------------------------------------------------------------------------------------------------------------|------|

|                                                                                                                                  | •    |

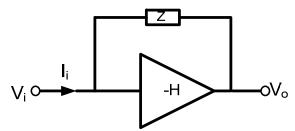

| Figure 2. 1 Impedance connected from input to output of an amplifier                                                             | 25   |

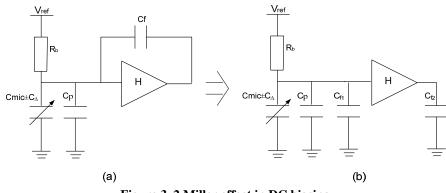

| Figure 3. 1 Impedance connected from input to output of an amplifier<br>Figure 3. 2 Miller effect in DC biasing                  |      |

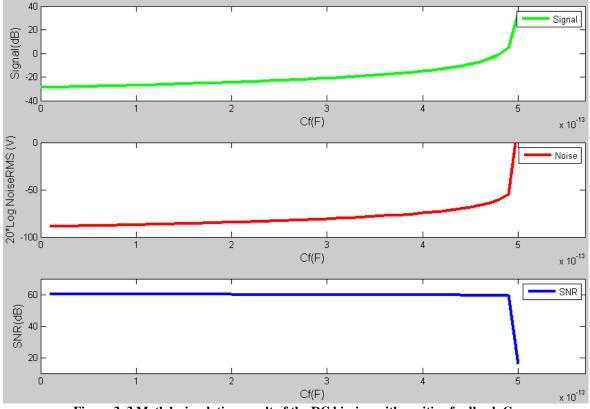

| Figure 3. 2 Miller effect in DC biasing<br>Figure 3. 3 Matlab simulation result of the DC biasing with positive feedback $C_{f}$ |      |

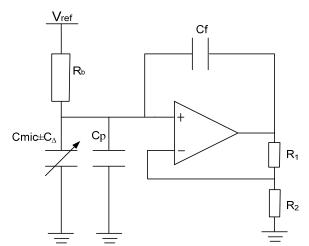

| Figure 3. 4 A non-inverting amplifier with closed loop gain                                                                      |      |

| Figure 3. 5 A non-inverting amplifier with AC-coupled closed loop gain                                                           |      |

| Figure 3. 6 A non-inverting amplifier with voltage regulator                                                                     |      |

| Figure 3. 7 DC biasing with positive feedback on system level.                                                                   |      |

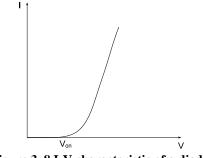

| Figure 3. 8 I-V characteristic of a diode                                                                                        |      |

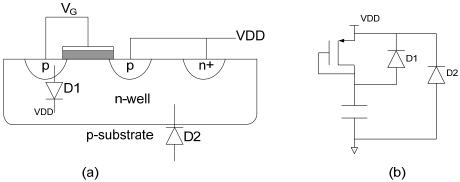

| Figure 3. 9 (a) Cross section of a diode-connect PMOS. (b) Equivalent schematic                                                  |      |

| Figure 3. 10 (a) Cross section of a diode-connect NMOS. (b) Equivalent schematic.                                                |      |

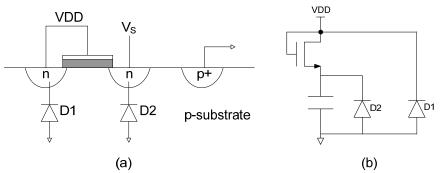

| Figure 3. 11 Positive feedback system                                                                                            |      |

|                                                                                                                                  |      |

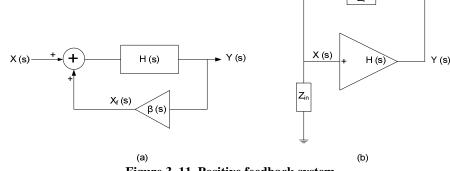

| Figure 4. 1 Input common mode range for an NMOS input differential amplifier wit                                                 |      |

| a current mirror load (b) folded-cascode with current source load                                                                |      |

| Figure 4. 2 A folded-cascode amplifier                                                                                           |      |

| Figure 4. 3 Simple amplifier with source degeneration at load.                                                                   |      |

| Figure 4. 4 The basic topology of the preamplifier                                                                               |      |

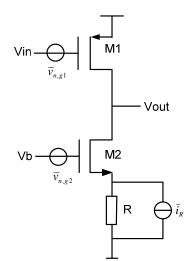

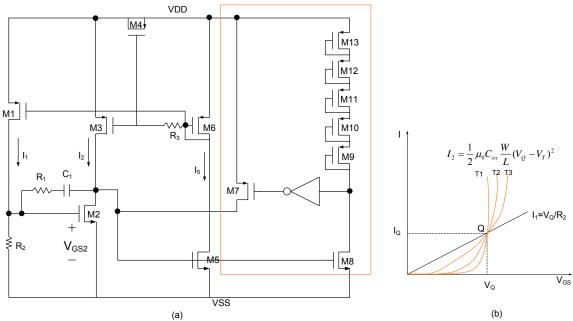

| Figure 4. 5 (a) Bootstrap current source. (b) I-V characteristic curves of $R_2$ and M2.                                         |      |

| Figure 4. 6 Equivalent model for bootstrap current source                                                                        |      |

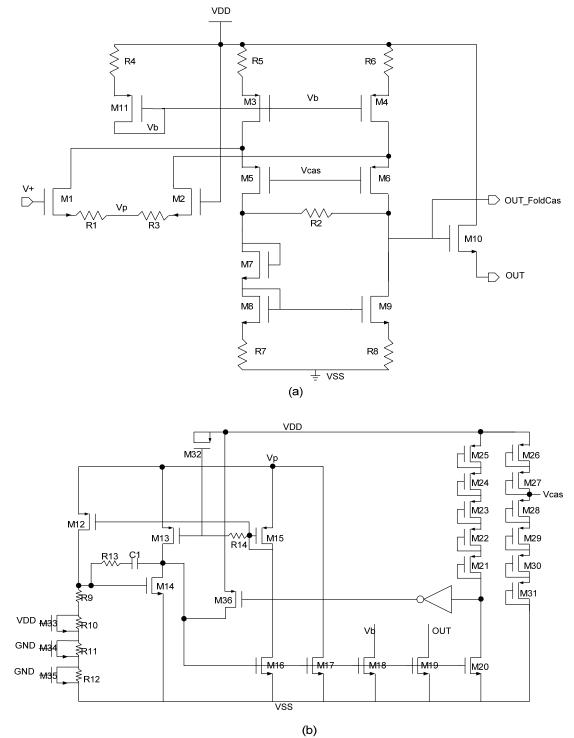

| Figure 4. 7 (a) Schematic of preamplifier. (b) Biasing schematic.                                                                | 51   |

| Figure 5. 1 The scheme to decide the input capacitance of the preamplifier                                                       | 54   |

| Figure 5. 2 Scheme for loop gain simulation.                                                                                     |      |

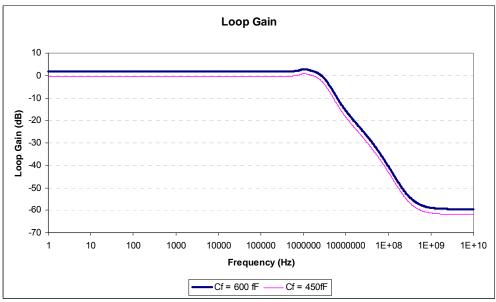

| Figure 5. 2 Scheme for loop gain sinulation for Loop Gain with two different $C_{f}$                                             |      |

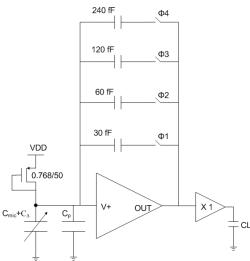

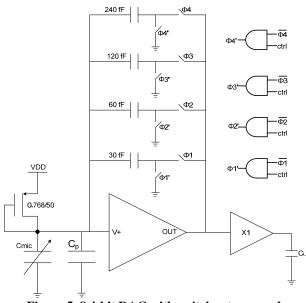

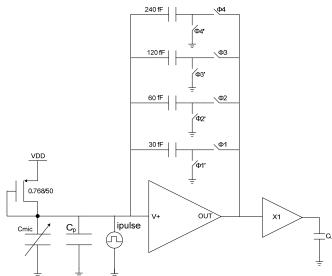

| Figure 5. 4 Readout scheme with 4-bit DAC.                                                                                       |      |

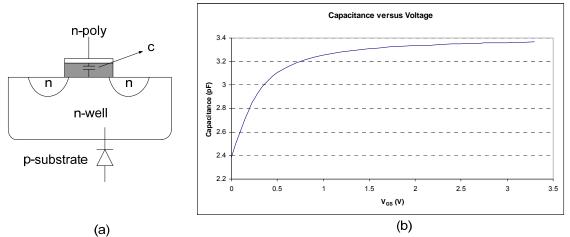

| Figure 5. 5 Cross section of a Npoly-Nwell capacitor.                                                                            |      |

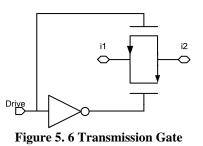

| Figure 5. 6 Transmission Gate                                                                                                    |      |

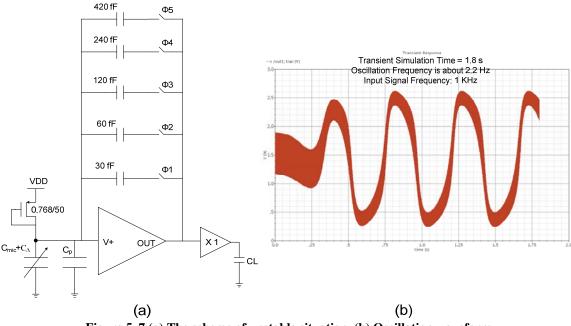

| Figure 5. 7 (a) The scheme of unstable situation. (b) Oscillation waveform                                                       |      |

| Figure 5. 8 4-bit DAC with switches to ground.                                                                                   |      |

|                                                                                                                                  |      |

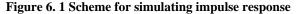

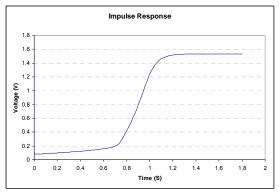

| Figure 6. 1 Scheme for simulating impulse response                                                                               | 60   |

| Figure 6. 2 Impulse response                                                                                                     | 60   |

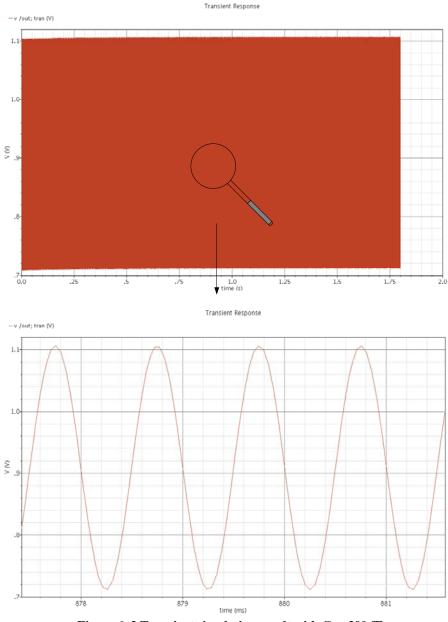

| Figure 6. 3 Transient simulation result with $C_f = 390$ fF.                                                                     |      |

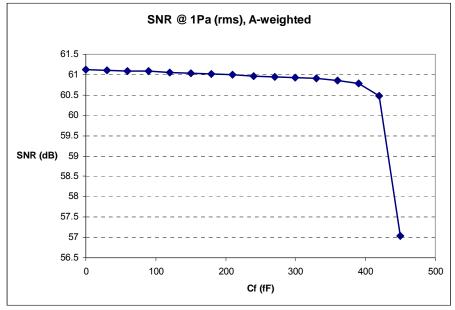

| Figure 6. 4 SNR versus C <sub>f</sub> (all available value of DAC)                                                               | 62   |

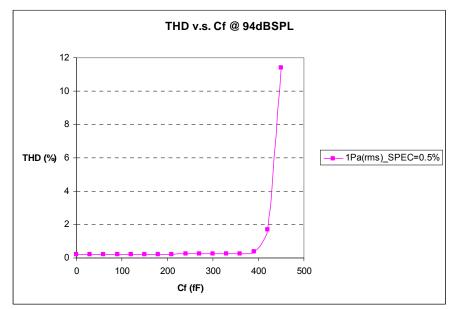

| Figure 6. 5 THD versus different C <sub>f</sub> . (all available value of DAC)                                                   |      |

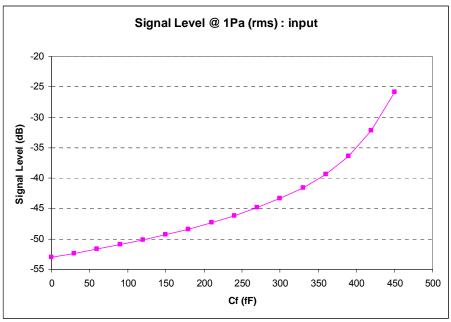

| Figure 6. 6 Signal Level versus different C <sub>f</sub>                                                                         |      |

| Figure 6. 7 Corner simulation for SNR when there is no $C_{\rm f}$                                                               |      |

| Figure 6. 8 Corner simulation for THD when there is no $C_{f}$                                                                   |      |

| Figure 6. 9 Corner simulation for SNR when $C_f = 390$ fF                                                                        |      |

| Figure 6. 10 Corner simulation for THD when $C_f = 390$ fF                                                                       |      |

| Figure 6. 11 Monte-Carlo simulation for SNR with $C_f = 390$ fF at 94dBSPL input                                                 |      |

| Figure 6. 12 Monte-Carlo simulation for SNR with $C_f$ = 390 fF at 94dBSPL input                                                 | 67   |

# List of Tables

| Table 1. 1 Notation used in the equation (1.4) to (1.7)                    | 7  |

|----------------------------------------------------------------------------|----|

| Table 1. 2 Notation used in the equation (1.8) and (1.9)                   |    |

| Table 1. 3 The specification of the MEMS microphone products on the market | 8  |

| Table 1. 4 Relation between sound pressure level and sound pressure [16]   | 10 |

| Table 2. 1 Measurement in DC biasing with different bias voltage.          | 30 |

| Table 2. 2 Comparison between three schemes                                |    |

| Table 2. 3 Advantages and disadvantages for the three schemes.             |    |

| Table 4. 1 Size of the devices.                                            | 52 |

| Table 4. 2 Specifications for the preamplifier                             |    |

| Table 6. 1 Comparison between this design and the products on market       | 68 |

# Chapter 1. Introduction

A microphone is an acoustic-to-electric transducer or sensor that converts an acoustical signal into an electrical signal. They are used in many applications such as telephones, hearing aids, mobile phones and personal audio systems. Many transduction principles have been used, leading to the development of transduction have been developed, including the piezoelectric, the piezoresistive, the capacitive and the contact microphones. The first microphone fabricated by silicon micromaching has been around for more than 20 years [1]. The introduction of silicon technology allows high precision and batch fabrication of the devices at low cost and with high reproducibility [2].

The most commonly used microphones are based on the capacitive principle for their lowpower and tolerance to high temperature [3]. They also have advantages of large bandwidth and high sensitivity [4]. The capacitive microphone can be divided into two categories, namely the electret condenser microphone (ECM) and the condenser microphone. An ECM employs an electret, a component with a built-in charge-accumulating layer, which has the function of accumulating charges in the absence of an applied bias voltage. The first ECM which is based on silicon technology was presented by jHohm and Gerhard-Multhaupt in 1984 [5]. The charge on the electrets, however, was susceptible to temperature and suffered from long-term drift, which affected the sensitivity of the microphone [6]. The authors of[7] describe a promising teflon electret for use in a silicon microphone but the use of teflon in a standard industrial production process gives rise to a lot of difficulties [8].

The condenser microphone does not require an electret material. To accumulate charge, it requires an applied bias voltage. It has moderate sensing sensitivity and low sensitivity to temperature. They are usually fabricated as Micro-Electro-Mechanical System (MEMS) because of this results in small size, low cost and batch fabrication. Reading out such microphones is the main objective of this thesis and this topic will be explained in detail in the next section.

Therefore, for simplicity, the term "MEMS microphone" quoted frequently in the following text refers to a condenser microphone based on silicon.

## 1.1 What is a MEMS Microphone?

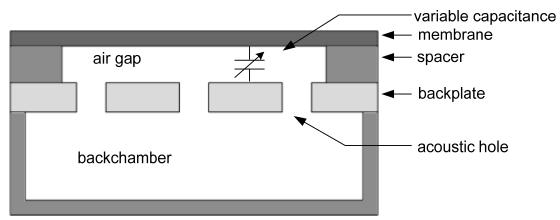

The MEMS condenser microphone is a design based on microminiaturized mechanical structures which can be integrated with CMOS process and other audio electronics. It can be viewed as a parallel plate capacitor that consists of a top membrane and a bottom back plate separated by a small air gap acting as a dielectric material. The back chamber acts as a reference chamber. Figure 1. 1 shows a cross-sectional view of a typical MEMS capacitive microphone. The acoustic holes on the back plate are used to alleviate air damping. An incident acoustic sound wave causes the membrane to deflect. As the membrane vibrates in accordance with the frequency and amplitude of the sound wave, the capacitance between the membrane and backplate changes accordingly due to the variable air gap. The aim of the readout circuit is thus to transform the capacitance variations into electric signals.

Figure 1. 1 The cross-sectional view of a typical MEMS capacitive microphone.

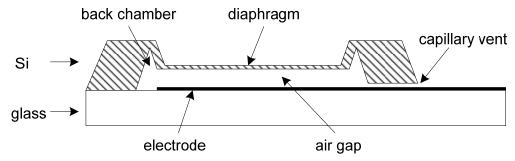

In the past 20 years, many researchers have investigated the fabrication of MEMS microphone with different structures or materials to improve their sensitivity and reduce their noise level. In 1992, T. Bourouina et al. proposed a condenser microphone with a p+ silicon membrane without acoustic holes that is shown schematically in Figure 1. 2 [9]. Because of the absence of acoustic holes, the air gap is increased to 7.5um to alleviate the air damping effect which results in a flat frequency response up to 10KHz.

Figure 1. 2 Cross-sectional view of Bourouina et al.'s condenser microphone [9].

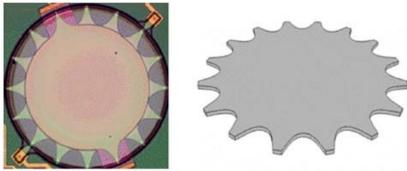

Since the stress of the membrane defines the microphone's sensitivity [1], the author in [10] proposes a microphone with a sandwich structure membrane which combines layers of compressive stress and tensile stress together to decrease the stress in the membrane. Another option to increase the sensitivity is to adjust the connection between back plate and membrane. The author in [11] reported that a spring type support rather than fully clamping the membrane at the whole circumference will increase the sensitivity by a factor of two. The picture of the spring-supported membrane is shown in Figure 1. 3.

Although there are still many ways to optimize the microphone's sensitivity by choosing different structures or materials, the design in this report will focus on the readout scheme which is at the circuit level. Therefore, the following sections describe a readout circuit for a MEMS microphone fabricated by NXP Semiconductors.

Figure 1. 3 Spring supported membrane [11].

## 1.2 Characteristics of the Microphone from NXP

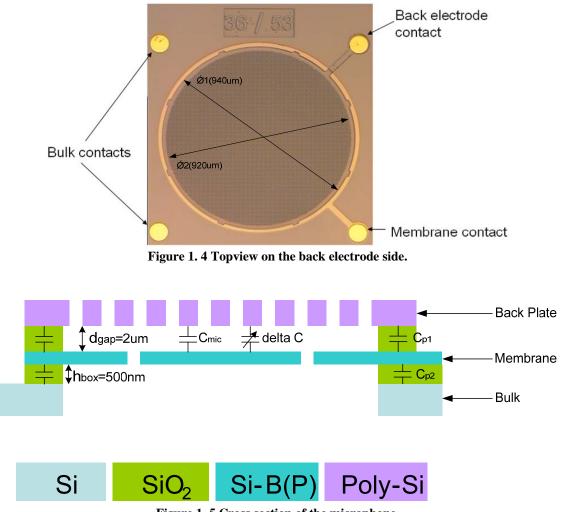

The MEMS microphone in this design is manufactured by NXP Semiconductors. The membrane and perforated back plate are round in shape as shown in Figure 1. 4. The two electrodes are supported or connected by a silicon dioxide ring at the edge of the round plate. Figure 1. 5 illustrates the cross section of the microphone.

Figure 1. 5 Cross section of the microphone.

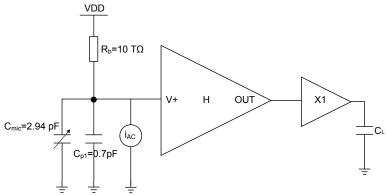

From the dimensions shown in Figure 1. 4 and Figure 1. 5, we can calculate the capacitance of the microphone when the membrane is not deflected. It is given by:

$$C_{mic} = \frac{\varepsilon_0 \varepsilon_{r1} \pi R^2}{d_{gap}} = \frac{1*8.85 e^{-12} * 3.14 * (460 e^{-6})2}{2e^{-6}} \approx 2.94 \ pF \tag{1.1}$$

where  $\varepsilon_0$  is vacuum permittivity,  $\varepsilon_{r1}$  is relative static permittivity of air, R is the radius of the membrane and  $d_{gap}$  is the quiescent air gap thickness.

In normal operation, the membrane and bulk are shorted together and biased at ground to eliminate  $C_{p2}$ . Thus  $C_{p1}$  shown in Figure 1. 5 is the main contribution for parasitic capacitance. The value of  $C_{p1}$  is given by:

$$C_{p1} = \frac{\varepsilon_0 \varepsilon_{r_2} \pi \left( (\frac{\phi_1}{2})^2 - (\frac{\phi_2}{2})^2 \right)}{d_{gap}} = 0.7 \, pF \tag{1.2}$$

where  $\varepsilon_{r^2}$  is 4.5 which is the relative static permittivity of SiO2,  $\phi$ 1 is the diameter of the membrane and  $\phi$ 2 is the effective diameter of the membrane.

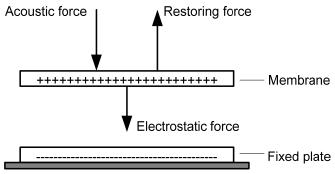

A MEMS microphone needs a bias voltage across its two plates. During operation, there are mainly four different types of forces exerted on the capacitor structure: the mechanical input from the acoustical wave, the elastic (restoring) force generated in the vibrating membrane in response to the deflection, the electrostatic force caused by the bias voltage on the two electrodes, and the damping force generated by the air gap[12]. They are illustrated in Figure 1. 6 without the damping force since it can be neglected in equilibrium. And the electrostatic force shown in Figure 1. 6 is given by:

$$F_{es} = \frac{\varepsilon_0 A V^2}{2(d_{gap} - x)^2}$$

(1.3)

where A is the area of the capacitor plate and x represents the displacement of the membrane. Equation (1. 3) indicates that the electrostatic force varies quadratically with the distance between the membrane and the back plate. This effect is the main reason for the microphone's nonlinearity.

Figure 1. 6 Force diagram of a microphone in equilibrium.

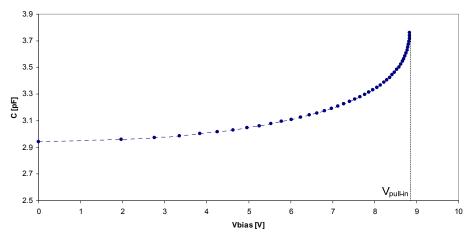

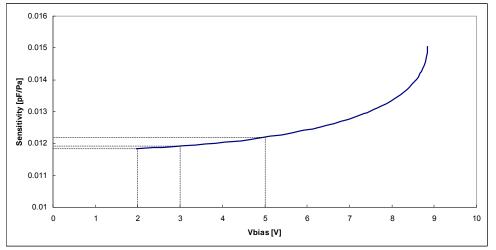

Therefore the force acting on the membrane is the sum of the external mechanical pressure, the electrostatic force and the counterbalancing elastic force. When the electrostatic force exceeds the mechanical restoring force, we call the corresponding critical bias voltage the pull-in voltage. If the voltage is increased beyond this pull-in voltage, the membrane will collapse onto the fixed back plate. Figure 1. 7 illustrates the capacitance of the microphone with different voltages by finite-element simulation [13]. The pull-in voltage of the microphone is around 8V by experiment and 8.8V by simulation which can also be derived from Figure 1. 7.

Figure 1.7 Capacitance variance with different voltage

#### 1.3 Sensitivity

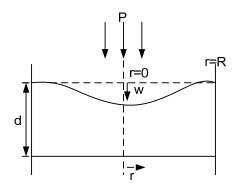

When there is no bias voltage across the two electrodes, the deflection of the membrane with an acoustical pressure, which is shown in Figure 1. 8, can be expressed as <sup>14</sup>:

$$w(r, P) = \frac{P}{4\sigma h} (R^2 - r^2)$$

(1.4)

Figure 1.8 Membrane's deflection without bias voltage.

Consequently, the capacitance between membrane and back plate is given:

$$C(P) = \int_{0}^{R} \frac{\varepsilon_0 \cdot 2\pi r}{d_{gap} - w(r, P)} dr \approx \frac{\varepsilon_0 A}{d_{gap}} \cdot (1 + \frac{1}{2} \cdot \frac{R^2}{4\sigma h d_{gap}} P + \frac{1}{6} \left(\frac{R^2}{4\sigma h d_{gap}}\right)^2 P^2 + \dots) \cdot [F]$$

(1.5)

With  $\frac{R^2}{4\sigma h d_{gap}} = 2.38 \cdot 10^{-3} \text{ m}^2/\text{N}$ , the third term in the bracket on the right side of equation (1.

5) can be neglected. Thus the sensitivity to acoustical pressure is:

$$S_{d} = \frac{\partial C(P)}{\partial P} \approx \frac{\varepsilon_{0}A}{d_{gap}} \cdot \frac{R^{2}}{8\sigma h d_{gap}} = \frac{\varepsilon_{0}\pi R^{4}}{8\sigma h d_{gap}^{2}} \cdot [F / Pa]$$

(1.6)

If we substitute the value of  $\frac{R^2}{4\sigma h d_{gap}}$  into equation (1. 5), it gives the linear relation between the microphone's capacitance and the acoustical pressure which is given by:

$$C_{mic}(P) \approx \frac{\varepsilon_0 A}{d_{gap}} \cdot (1 + 0.00119 \cdot P) = C_{mic}(1 + kP) \cdot [F], \text{ for } k = 0.00119 \cdot [Pa^{-1}]$$

(1.7)

where  $C_{mic}$  is the quiescent capacitance of the microphone which is calculated in equation (1. 1). For convenience and clarity, 0.00119 is replaced with a symbol k.

From this chapter on, the frequently mentioned term  $C_{\Delta}$  represents the capacitance variance in the time domain and it is equal to  $C_{mic}kP$ . If the acoustical pressure P can be represented as  $\hat{P}\sin(\omega t)$ , where  $\hat{P}$  is the amplitude of the sound and  $\omega$  is the frequency of the sound, then the amplitude of the capacitance variance in the frequency domain is  $C_{mic}k\hat{P}$  and it is symbolized as  $C_v$ . Consequently, the rms value of the capacitance variance  $C_{v,rms}$  is  $\frac{C_v}{\sqrt{2}}$

Table 1. 1 shows the notation used in the above equations.

| Symbol | Explanation                    |

|--------|--------------------------------|

| W      | Deflection of the membrane [m] |

| Radius of the membrane [m]                                  |

|-------------------------------------------------------------|

| Radial position [m]                                         |

| Initial stress of membrane [Pa], 30MPa                      |

| Thickness of membrane [m], 0.38e-6                          |

| Acoustical Pressure [Pa]                                    |

| Quiescent air gap between membrane and back plate [m], 2e-6 |

| Permittivity of free space [F/m], 8.854e-12                 |

| Area of the membrane [m <sup>2</sup> ]                      |

|                                                             |

Table 1. 1 Notation used in the equation (1. 4) to (1. 7)

When there is a bias voltage, the author in [15] gives the sensitivity under this condition which is given by:

$$S_{el}^{mech} = K_{cell} \frac{V_{bias}}{d} \cdot [V/m] [15]$$

$$S_{el}^{ac} = K_{cell} \frac{V_{bias}}{d} S_d \cdot [V/Pa] [15]$$

(1.8)

(1.9)

Table 1. 2 shows the notations used in the above equations.

Since the movable membrane will be attracted to the fixed back plate when a bias voltage is exerted, the air gap distance becomes smaller and results in a larger sensitivity. Consequently a larger signal will be generated by the microphone with a larger bias voltage.

| Symbol              | Explanation                                                                  |  |  |  |

|---------------------|------------------------------------------------------------------------------|--|--|--|

| $S_{el}^{\it mech}$ | Mechanical sensitivity in electrical domain                                  |  |  |  |

| $S^{ac}_{el}$       | Acoustical sensitivity in electrical domain                                  |  |  |  |

| K <sub>cell</sub>   | Holes in the cell and the fringing fields at the edges                       |  |  |  |

| $V_{bias}$          | Voltage exerted on the microphone                                            |  |  |  |

| $S_d$               | Acoustical sensitivity without bias voltage which is shown in equation(1. 6) |  |  |  |

| d                   | Air gap between membrane and back plate                                      |  |  |  |

Table 1. 2 Notation used in the equation (1. 8) and (1. 9)

## 1.4 VerilogA Model for Microphone from NXP

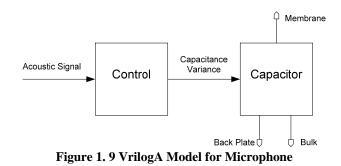

Given the basic characteristics of the microphone, a behavioral model of the microphone is essential for simulation. Ideally, this model should be accurate and include the non-idealities of the sensor which limit the performance. But a simple model can speed up the simulation process and reduce the design time. In this design, a proper functionality is the main objective for the model. Therefore a very simple model is coded in Verilog-A which does not consider the nonlinearity and electrostatic force limit of the microphone. The effect that sensitivity increases with increasing bias voltage is not included as well. If specification can be achieved with the lowest sensitivity, it will also be achieved with higher sensitivity. The basic principle behind the model is regarding the microphone as a variable capacitance and its capacitance variance is controlled by a voltage source which represents the acoustical signal. The related code can be found in Appendix A.

## 1.5 Specification to be Achieved

In the current MEMS microphone products market, the major manufacturers are Knowles Electronics, Analog Devices, Infineon, Akustica and Pulse MEMS. They produce both analog microphones and digital microphones. With the datasheets of these products, the main characteristics of those analog microphones are listed in Table 1. 3. There exists another design which is based on the microphone from NXP Semiconductors already. It adopts charge pump to move the bias voltage across microphone up to 5V. Its specifications are also listed in Table 1. 3.

| Specification<br>Product             | SNR@1Pa<br>(dB)(A-<br>weighted) | Sensitivity<br>@1Pa<br>(dBV/Pa) | Current<br>(uA)                      | Band-<br>width<br>(HZ) | THD(%)        |

|--------------------------------------|---------------------------------|---------------------------------|--------------------------------------|------------------------|---------------|

| SPM0204HE5<br>(Knowles<br>Acoustics) | 59                              | -42                             | 100<br>(V <sub>DD</sub> =1.5~3.6V)   | 14K                    | 1%@100dBSPL   |

| ADMP401-1<br>(ADI)                   | 62                              | -37                             | 200<br>(V <sub>DD</sub> =1.5~3.6V)   | 12K                    | 3%@105dBSPL   |

| AKU1126<br>(Akustica)                | 58                              | -42                             | 150<br>(V <sub>DD</sub> =1.65~3.6V)  | N/A                    | 5%@115dBSPL   |

| SMM310<br>(Infineon)                 | 59                              | -42                             | <b>80</b><br>(V <sub>DD</sub> =2.1V) | 10K                    | 0.1%@104dBSPL |

| TC200A<br>(Pulse<br>MEMS)            | 61                              | -40                             | 330<br>(V <sub>DD</sub> =1.64~2.86V) | 20K                    | 10%@110dBSPL  |

| Previous<br>Design                   | 60                              | -46                             | 450                                  | 20K                    | 1%@100dBSPL   |

Table 1. 3 The specification of the MEMS microphone products on the market.

The table shows a general idea about the behavior of the current MEMS microphone products on the market. It also indicates the most important specifications when designing the interface circuit for MEMS microphone. The data in bold type states that it exceeds the behavior of other products in this specification.

By comparing the data listed in Table 1. 3, we can have a rough idea about the specifications which are going to be satisfied. SNR at 1Pa should not be lower than 58 dB. Sensitivity at 1 Pa should not be lower than -42 dB. The current consumption is supposed to be kept as small as possible. The bandwidth which is mainly decided by the frequency response of the microphone should be the same as the previous design. And the total harmonic distortion (THD) is also expected not to exceed that of the previous design.

Since the previous design uses charge pump to increase the bias voltage across the sensor which increases the complexity of the circuit, the aim of this design is thus trying to achieve the same specification of the previous design with a lower bias voltage.

## 1.5.1 Sound Pressure Level

The "dBSPL" shown in the last column of Table 1. 3 is the unit of sound pressure level (SPL) which is often denoted as sound level Lp. It is a logarithm decibel scale measurement of the rms (Root Mean Square) sound pressure of a sound relative to a reference value[16]. From this section on, if not explicitly mentioned, sound pressure will be expressed in terms of its effective value (rms). The reference value is 20uPa which is the threshold of hearing (roughly the sound of a mosquito flying 3 meters away). The relation between sound pressure and sound pressure level is given by:

$$L_{p} = 10\log_{10}(\frac{p_{rms}^{2}}{p_{ref}^{2}}) = 20\log_{10}(\frac{p_{rms}}{p_{ref}})$$

(1.10)

where  $p_{rms}$  is the rms value of the sound pressure being measured and  $p_{ref}$  is the reference sound pressure.

Table 1. 4 shows a comparison of sound pressure level and corresponding sound pressure which gives a general idea of the relation between the common sound source in human life and the abstract sound pressure level.

| Examples                     | Sound Pressure Level | Sound Pressure p (N/m <sup>2</sup> =Pa) |

|------------------------------|----------------------|-----------------------------------------|

|                              | (dBSPL)              |                                         |

| Jet aircraft, 50 m away      | 140                  | 200                                     |

| Threshold of pain            | 130                  | 63.2                                    |

| Disco, 1 m from speaker      | 100                  | 2                                       |

| Diesel truck, 10 m away      | 90                   | 0.63                                    |

| Kerbside of busy road, 5 m   | 80                   | 0.2                                     |

| Vacuum cleaner, distance 1 m | 70                   | 0.063                                   |

| Conversational speech, 1 m   | 60                   | 0.02                                    |

| Quiet library                | 40                   | 0.002                                   |

| Quiet bedroom at night       | 30                   | 0.00063                                 |

| Background in TV studio      | 20                   | 0.0002                                  |

| Rustling leaf        | 10 | 0.000063 |

|----------------------|----|----------|

| Threshold of hearing | 0  | 0.00002  |

Table 1. 4 Relation between sound pressure level and sound pressure [16].

## 1.5.2 A-weighted

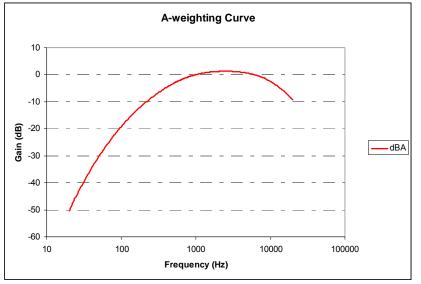

When SNR specifications are stated in Table 1. 3, the term A-weighted is used. Since the human ear is most sensitive to sounds at frequencies between 1 KHz to 5 KHz, frequency-weighting curves are often incorporated with sound pressure level meters to produce a result which conforms to what we hear [17]. The weighting curves were originally different with different sound level, but A-weighting, which was originally used for low level sounds, is now often used for measuring environmental noise and the output of audio systems. The A-frequency-weighting curve is shown in Figure 1. 10. The gain curve crosses 0dB at 1 KHz. The function defining the A-weighting curve in terms of poles and zeros comes from IEC/CD 1672 (and ANSI S1.42-2001):

$$G_A(s) = \frac{k_A \cdot s^4}{(s+129.4)^2 (s+676.7)(s+4636)(s+76655)^2}$$

(1.11)

where k<sub>A</sub>≈7.39705\*10<sup>9</sup>

Figure 1. 10 A-weighting Curve

## 1.6 Motivation

As has been stated above, a large bias voltage exerted on the microphone can generate large signal until the voltage exceeds the pull-in voltage. The fact that mainstream CMOS technology cannot handle voltages greater than a few volts, however, indicates that realizing a high bias voltage will bring more difficulties. Moreover, the signal generated from the MEMS microphone needs to be readout by an interface circuit. For a specific microphone, different interface circuits will drive the microphone to have different specifications.

Therefore, the main purpose of this project is to investigate the possible interface structures and finally develop an interfacing principle which can drive a microphone biased with a low bias voltage in such a way to achieve the specification.

## 1.7 Outline of the Thesis

The thesis is composed of seven chapters presenting different aspects of the investigation. Following this introduction chapter, Chapter 2 describes the investigations of several possible readout schemes for a capacitive MEMS microphone sensor. These comparisons mainly focus on the signal-to-noise ratio (SNR), linearity and sensitivity. Chapter 3 proposes a new readout scheme which can increase the sensitivity of the microphone by the use of positive feedback capacitor. It mainly deals with the principle behind this scheme. The specification of the preamplifier will also be given. Chapter 4 describes the process of designing a lownoise operation amplifier (opamp) on transistor level. The design of the current source used in the biasing circuit is included as well. In Chapter 5, the opamp will be simulated with the microphone model in the whole scheme. The practical implementation issues of the system are discussed. The simulation results and the analysis of them are both presented in Chapter 6. Finally, in Chapter 7, the conclusion of the project and recommendations for future improvement are given.

## **Chapter 2. Readout Scheme**

This section mainly analyzes the possible readout schemes for MEMS microphone. It starts with the background of some common readout schemes in literature (section 2.1). Then three different schemes will be analyzed (section  $2.2 \sim 2.4$ ). Both the advantage and disadvantage of these schemes will be explained in detail. The chapter ends with a comparison among the three schemes (section 2.5).

#### 2.1 Read-out schemes for Capacitive Microphone

A typical MEMS microphone front-end interface has to transfer the capacitive changes in the sensor to voltage or current variations. It has relatively fixed specification driven by the characteristic of the microphone. The interface circuit also has to minimize the most critical non-idealities of the sensor (e.g. parasitic capacitance) to maximize its sensitivity [18].

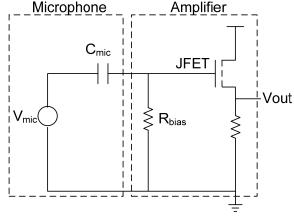

In traditional design, a Junction-Field-Effect-Transistor (JFET) in the source-follower configuration is used to buffer the signal from the electret microphone which is shown in Figure 2. 1 [19]. The voltage source  $V_{mic}$  represents the input sound which is also proportional to the sound pressure. The value of  $R_{bias}$  needs to be very large to move the  $k_BT/C$  noise corner generated by the microphone and  $R_{bias}$  to low frequency where it is of no importance.

Figure 2. 1 Traditional readout scheme for ECM.

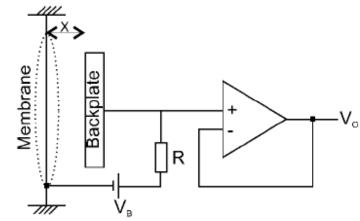

The microphone in Figure 2. 1 is an electret microphone which has long-term drift problems as mentioned in Chapter 1. For a MEMS capacitive microphone, i.e. without an electret, a typical voltage-readout scheme is shown in Figure 2. 2 [20]. The microphone is biased with a dc voltage through a large resistor. The resulting large RC time constant can guarantee that the microphone works under constant charge condition. However, the bias resistor needs to be very large (depending on the microphone's capacitance and bandwidth) which is not easy to implement in a standard CMOS technology. The sensitivity is limited by the parasitic capacitances both of the sensor itself and of the preamplifier

Figure 2. 2 Typical voltage-readout scheme for MEMS capacitive microphone [20].

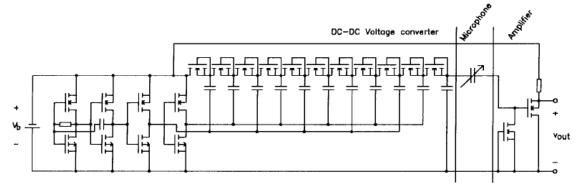

The MEMS microphone can achieve high sensitivity with high bias voltage. Thus the author in [6] proposed a scheme which is shown in Figure 2. 3. A MEMS microphone without an electret is biased by a dc-dc converter. The Dickson type dc-dc converter behaves like a charge pump and it builds up charge at the output by the two anti-phase oscillation clocks [21].What makes this design novel is that the dc-dc converter enables the microphone to achieve high sensitivity at a low supply voltage. The main disadvantage of this design is the linearity. It has 10.1% distortion under 20 Pa sound pressures.

Figure 2. 3 Scheme of the integrated capacitive microphone with dc-dc voltage converter and preamplifier [6].

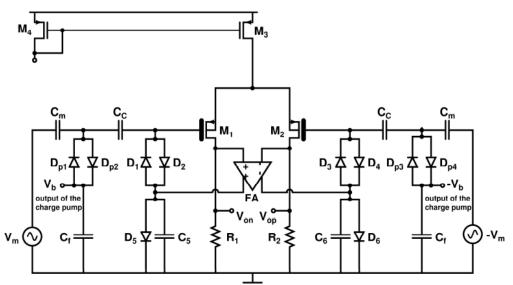

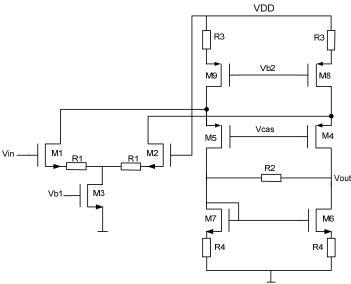

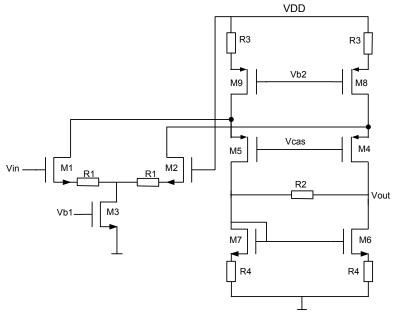

Recently the authors in [22] propose a solution which implements two microphones biased by voltages having opposite polarities. The SNR is thus increased by 3 dB. The bias voltage for the microphone is  $\pm$  10V which is generated from a charge pump. A 6V PMOS differential pair forms the basic gain stage. Another novel point of this design is the feedback amplifier (FA). It not only speeds up the start up transient time but also increases the insensitivity to the supply-induced noise and electro-magnetic interference (EMI). The schematic of the preamplifier used in this design is shown in Figure 2. 4. One distinct disadvantage of the design is the cost since two microphones are used.

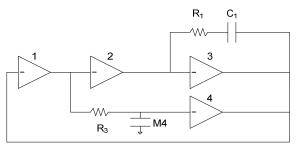

Figure 2. 4 Schematic of the preamplifier used in [22].

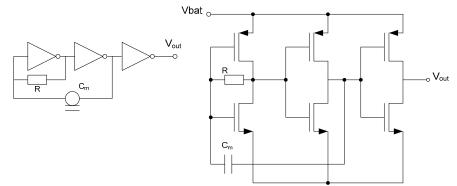

Another option for readout capacitive microphone adopted a different detecting principle, frequency modulation. The scheme is shown in Figure 2. 5. Cm represents the capacitive microphone and it plays the role of timing capacitance in the ring oscillator due to its variable capacitance. In this design, the microphone does not need extra dc bias. Therefore the microphone behaves more linearly to the acoustic pressure due to the small electrostatic force between the membrane and back plate. Moreover, the frequency modulated output is convenient for further digital signal processing. However, the major disadvantage of the design is its low SNR (about 60 dB SNR under 20 Pa) and high power consumption (1.96 mW) [23].

Figure 2. 5 Scheme of the integrated microphone by using frequency modulation [23].

From the above literature study, it can be seen that there are two designs use charge pump to bias the microphone. Since a charge pump is not easy to implement and the distortion increases sharply as bias voltage approaches the pull-in voltage [24], the aim of the design is thus to find out a suitable readout scheme which will get rid of the charge pump and maximize the sensitivity of the microphone under a low supply voltage. It starts with the most traditional and typical scheme and then moves on to a new scheme by reducing the drawbacks of the old design.

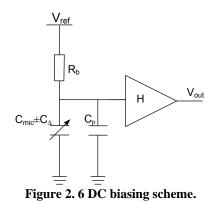

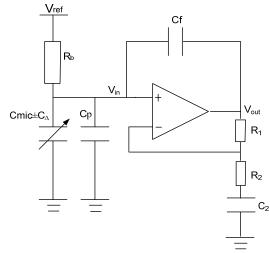

#### 2.2 DC Biasing

In DC biasing, which is shown in Figure 2. 6, there is a very large resistor  $R_b$  (in the order of Giga-Ohms) connected between the microphone and a dc voltage source which is indicated as  $V_{ref.}$  The name "dc biasing" comes from the electrical characteristics of the reference source  $V_{ref.}$  The charge accumulated on the microphone does not change by much because of the large RC time constant. The charging current is given by:

$$I = \frac{V_{ref}}{R_b} e^{-\frac{t}{R_b C_{mic}}} \quad [A]$$

If  $R_b$  is infinite,  $I = \frac{\partial Q}{\partial t} = \frac{V_{ref}}{R_b} \approx 0$  which means Q can be regarded as constant. The following equation is based on constant charge assumption which is given by:

$$V_o = \frac{Q_{mic}}{C_{mic}} = \frac{Q_{mic}}{A\varepsilon} d \quad [V]$$

(2.2)

where  $Q_{mic}$  the total charge accumulated on the sensor,  $C_{mic}$  is the static capacitance of the sensor, A is the area of the effective membrane,  $\varepsilon$  is the permittivity of the medium between the membrane and the back plate and d is the distance between the membrane and the backplate.

#### 2.2.1 Signal Level

Based on constant charge assumption, we can derive that:

$$Q_{const} = (C_{mic} + C_p) * V_{ref} = (C_{mic} + C_p \pm C_\Delta) (V_{ref} \mp \Delta V) [F \cdot V]$$

(2.3)

where  $C_{\Delta}$  is  $C_{mic}kP$  which comes from equation (1. 7) and the value of  $C_{mic}$  is denoted in equation (1. 1). From this section on,  $C_p$  not only represents  $C_{p1}$  which is mentioned in section (1.3) but also includes the parasitic capacitance from the preamplifier.

(Since it is impossible to have a resistor with infinite large resistance, the calculation of the output signal without the constant charge assumption is included in Appendix B.)

As a result, the signal generated on the microphone in the time domain is:

$$\Delta V = \frac{(C_{mic} + C_p) * V_{ref}}{C_{mic} + C_p - C_\Delta} - V_{ref} = \frac{C_\Delta * V_{ref}}{C_{mic} + C_p - C_\Delta} \quad [V]$$

(2.4)

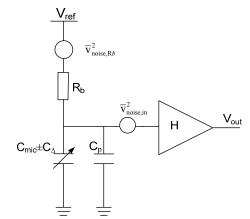

#### 2.2.2 Noise Calculation

There are mainly two noise sources in DC biasing scheme which are shown in Figure 2. 7. One is the thermal noise from the bias resistor which is represented by noise power spectrum density  $\overline{v}_{noise,R_b}^2$ . It is filtered by the microphone and the parasitic capacitance. The other one is the input-referred noise density of the preamplifier which is represented by  $\overline{v}_{noise,in}^2$ . Although the voltage source  $V_{ref}$  also contributes noise, its noise is filtered by the R<sub>b</sub> and microphone as well. Even though, a clean bias voltage is also demanded in DC biasing scheme. For simplicity, the following calculation is based on the assumption that the bias voltage is noise free. Therefore the total input-referred noise at the input of the preamplifier is given by:

$$v_{noise}^{2} = \overline{v}_{noise,R_{b}}^{2} * \left| \frac{1}{1 + j * \omega R_{b} * (C_{mic} + C_{p})} \right|^{2} + \overline{v}_{noise,in}^{2} [V^{2} / Hz]$$

(2.5)

Referring the noise voltage power spectrum to a capacitive noise power spectrum by using the voltage-to-capacitance transfer function (assuming  $C_{\Delta}$  is much smaller than  $C_{mic}+C_p$ ) yields:

$$C_{noise}^{2} = \left(\frac{C_{mic} + C_{p}}{V_{ref}}\right)^{2} \overline{v}_{noise,R_{b}}^{2} \left|\frac{1}{1 + j * \omega R_{b} * (C_{mic} + C_{p})}\right|^{2} + \left(\frac{C_{mic} + C_{p}}{V_{ref}}\right)^{2} \overline{v}_{noise,in}^{2} [F^{2} / Hz] \quad (2.6)$$

Figure 2. 7 Noise sources in DC biasing scheme.

Equation (2. 6) indicates that for a certain capacitance variance  $C_v$ , large value of  $V_{ref}$  and  $R_b$  will yield large SNR.

Although the DC biasing scheme is simple, its dominant disadvantage is that the large resistor is difficult to implement in IC technology. Moreover, in the audio bandwidth which

is from 20 Hz to 20 KHz the 1/f noise of the opamp dominates which is not beneficial to achieve a good SNR. Equation (2. 4) also shows that the electrical sensitivity of the microphone is inversely proportional to the quiescent capacitance ( $C_{mic}+C_p$ ) of the microphone. If the preamplifier connected afterwards has large input parasitic capacitance (for low noise or coupling reason), the sensitivity of the microphone is deteriorated even more. As a result, the input-referred noise of the preamplifier has to be reduced to compensate for the sensitivity reduction. Another drawback of this scheme is the nonlinearity. Rewriting equation (2. 4) into:

$$\Delta V = \frac{C_{\Delta} * V_{ref}}{(C_{mic} + C_p) \left(1 - \frac{C_{\Delta}}{C_{mic} + C_p}\right)} \quad [V]$$

(2.7)

In the ideal case, the signal should be linearly proportional to the capacitance variance of the microphone. The factor  $\frac{C_{\Delta}}{C_{mic} + C_p}$  in the denominator of equation (2. 7), however, affects the linearity. This factor is supposed to be small which implies that  $C_{mic}+C_p$  should be large. A large value of  $C_{mic}+C_p$ , however, will kill the signal level which is indicated from equation (2. 4). Therefore, there exists a trade off between the signal level and linearity when the DC biasing scheme is used.

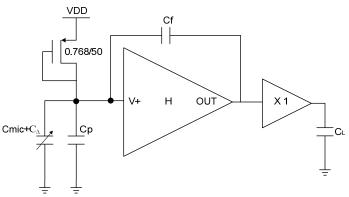

### 2.3 Charge Amplifier

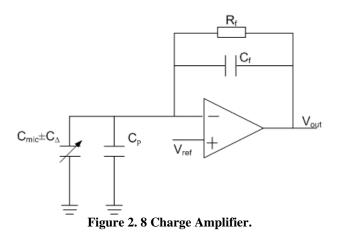

In order to avoid the impact of parasitic capacitance, another interfacing scheme was investigated. This is shown in Figure 2. 8. Because of feedback, the voltages on the two inputs of the amplifier will follow each other and so the bias voltage across the microphone will be stable. The voltage across the parasitic capacitor will also be stable. Consequently,  $C_p$  can be neglected in the calculation of AC transfer function which is shown below

#### 2.3.1 Signal Level

When there is an acoustical signal exerted on the microphone, the time-varying capacitance will generate time-varying current which turns out to be time-varying voltage at the output because of the feedback network. The time-varying current is expressed as:

$$i_{mic}(t) = \frac{d(C_{mic} + C_{\Delta})}{dt} V_{ref} = \frac{\varepsilon_0 A}{d_{gap}} k V_{ref} \frac{dP(t)}{dt}$$

(2.8)

The frequency-varying current is then given by:

$$i_{mic}(\omega) = \frac{\varepsilon_0 A}{d_{gap}} k \hat{P} V_{ref} \omega$$

(2.9)

Therefore, the voltage on the output in the frequency domain is given by:

$$V_{out}(\omega) = \frac{\varepsilon_0 A}{d_{gap}} k \hat{P} V_{ref} \left( \frac{\omega R_f}{1 + j \omega R_f C_f} \right) = C_v \cdot V_{ref} \left( \frac{\omega R_f}{1 + j \omega R_f C_f} \right)$$

(2.10)

The above calculations are all based on the assumption that the input acoustic signal is a pure sine wave and can be expressed as  $\hat{P}\sin(\omega t)$ , where  $\hat{P}$  is amplitude of this sine wave signal. This assumption will also be used in the following parts.

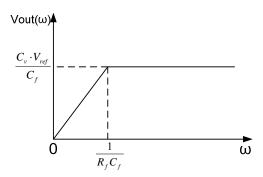

Figure 2. 9 shows the amplitude of V<sub>out</sub> versus frequency. Since the audio frequency that human being can hear is from 20Hz to 20KHz, the pole which is decided by  $\frac{1}{2\pi R_f C_f}$  should be much lower than 20Hz to avoid attenuation on the signal. Thus the amplitude of the output signal in the audio band is  $\frac{C_v \cdot V_{ref}}{C_f}$ , assuming that this pole is much lower than 20Hz. Since C<sub>f</sub> should be kept small in order not to attenuate the signal, the only way to move the pole downwards is to increase R<sub>f</sub>. Assuming C<sub>f</sub> is 1 pF, R<sub>f</sub> should be about 8 G  $\Omega$  to make the pole locate at 20Hz. And for noise consideration, the pole should be moved to even lower frequencies to minimize the thermal noise from R<sub>f</sub>. Therefore DC biasing with virtual ground

still can not avoid the implementation and noise issues associated with a huge resistor.

Figure 2. 9  $V_{out}$ 's amplitude versus radio frequency.

### 2.3.2 Noise Calculation

Compared to DC biasing, this scheme can achieve high signal level at the output of the amplifier if  $C_f$  is smaller than  $C_{mic}$ . While for noise consideration, both of these two schemes

can not avoid the filtered huge resistance's noise, the 1/f noise from the preamplifier and the noise from the reference voltage or bias voltage. For simplicity, the following noise derivation will not take the reference voltage noise into consideration. If we denote the input referred noise of the amplifier as  $\overline{v}_{noise,in}^2$  which is shown in Figure 2. 10, the total noise at the output can be expressed as:

$$v_{noise,out}^{2} = \bar{v}_{noise,in}^{2} \left( \frac{1 + j\omega R_{f}(C_{mic} + C_{p} + C_{f})}{1 + j\omega R_{f}C_{f}} \right)^{2} + \bar{v}_{noise,R_{f}}^{2} \left( \frac{1}{1 + j\omega R_{f}C_{f}} \right)^{2} [V^{2}/Hz]$$

(2.11)

Referring the noise voltage power in equation (2. 11) back to a capacitive noise power at input by using the transfer function in equation (2. 10) yields:

$$C_{noise}^{2} = \overline{v}_{noise,in}^{2} \frac{1}{V_{ref}^{2}} \left( \frac{1 + j\omega R_{f} (C_{mic} + C_{p} + C_{f})}{\omega R_{f}} \right)^{2} + \overline{v}_{noise,R_{f}}^{2} \frac{1}{V_{ref}^{2}} \left( \frac{1}{\omega R_{f}} \right)^{2} [F^{2} / H_{z}]$$

$$(2.12)$$

$$V_{noise,in}$$

$$V_{ref}$$

Figure 2. 10 Noise Source in Charge Amplifier

Equation (2. 11) shows that the input-referred noise of amplifier is amplified by the factor  $\frac{C_{mic} + C_p + C_f}{C_f}$ in audio bandwidth (assume  $\frac{1}{2\pi R_f C_f}$  is much smaller than 20Hz ). To get

higher signal level we need small C<sub>f</sub> while the noise of the amplifier is amplified even more.

Moreover, the 1/f noise of the amplifier still dominates.

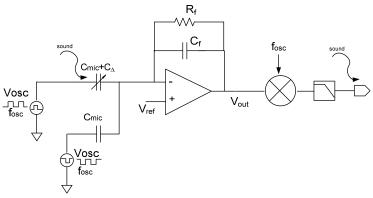

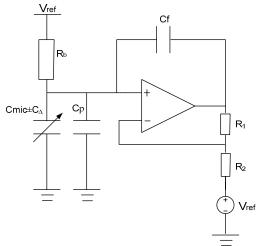

#### 2.4 AC Biasing

The problem with the charge amplifier scheme is mainly caused by input-referred noise of the amplifier. Normally, the 1/f noise of the amplifier will be dominant in the audio bandwidth. If we want to avoid the 1/f noise of the amplifier, one option is to modulate the signal to higher frequencies. That's why we introduce AC biasing to excite the microphone in order to realize amplitude modulation (AM). It is also expected that the noise level at high frequency is small and it will benefit the SNR result. The name "AC biasing" is derived from the property of the excitation source.

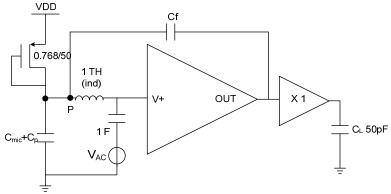

The AC biasing scheme is shown in Figure 2. 11. The large resistor is not necessary any more since the signal is moved to much higher frequency band and 1/f noise does not dominate as well. Moreover, this scheme is not sensitive to the parasitic capacitor since the voltage applied to the parasitic capacitor is constant due to the virtual ground.

Figure 2. 11 AC biasing scheme.

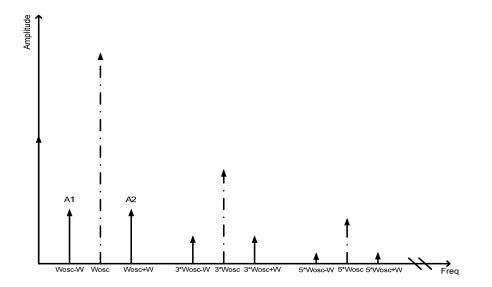

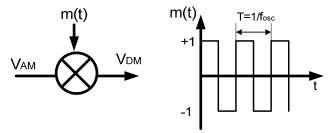

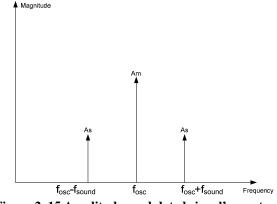

The principle behind the AC biasing is mainly about amplitude modulation and demodulation. The microphone's capacitance varies with the sound signal. Meanwhile, the capacitor is excited by the AC source. Therefore, amplitude modulated current is generated. And with the feedback RC network, the modulated current generates a voltage at the output of the amplifier. The spectrum of the voltage here is composed of three components. One is carrier signal which is at the frequency of AC source. The other two are modulated signal at both sides of the carrier signal. The distance between the sidebands and carrier signal is exactly equal to the frequency of the sound. Figure 2. 12 illustrates the spectrum of the amplitude modulated signal with a square wave carrier.

Figure 2. 12 Spectrum of the amplitude modulated signal.

Usually the carrier signal is much higher than the sidebands. The large amplitude of the carrier signal may cause saturation problem in the amplifier. Since it does not contain the sound's information, it can be reduced by a capacitor connected in parallel with the

microphone. The added capacitor has the same capacitance as  $C_{mic}$  and it is driven by the oscillation source which is 180 degrees out of phase with the source connected to the microphone. Thereby the signal at the output of the amplifier contains only the sidebands which have the information we want.

In order to demodulate sound from the signal, a synchronized mixer is added afterwards. The mixer is driven by the same frequency as the excitation source. Therefore, the two modulated sidebands are moved back and mixed together at the sound's frequency.

In ideal situation, the excitation source should generate a pure sinusoidal wave as carrier because it contains only one frequency component which is good for linearity of the sensor and filtering after demodulation. In IC design, however, it is much more difficult to implement a sinusoidal wave than generating a square wave. Therefore a square wave is chosen as excitation source. The spectrum of a square wave, however, contains odd harmonics of the base frequency. As a result, the demodulated signal is composed of several sidebands of the odd harmonics at sound's frequency and other higher frequency components which is shown in Figure 2. 12.

Therefore a low pass filter (LPF) is necessary to filter out the higher frequency components to limit the demodulated signal as pure as possible in the audio bandwidth.

## 2.4.1 Signal Level

To make the idea more distinct, a mathematical derivation of the principle is given below. Assume the excitation source is a square wave with amplitude  $V_{osc}$  and frequency  $f_{osc}$ , the Fourier Transform of the square wave is shown below:

$$F(t) = \frac{V_{osc}}{2} + \frac{2V_{osc}}{\pi} [\cos(\omega_{osc}t) - \frac{1}{3}\cos(3\omega_{osc}t) + \frac{1}{5}\cos(5\omega_{osc}t) - \dots], \quad for \ \omega_{osc} = 2\pi f_{osc}$$

(2.13)

Since the higher odd harmonics have decreasing amplitude and they will be filtered out in the end, the following derivation will only consider the base frequency component which is  $2V_{osc} \cos(\alpha - t)$

$$\frac{-\tau_{osc}}{\pi}\cos(\omega_{osc}t)$$

Then the current through the microphone and the parallel capacitor is given by:

$$I(t) = \frac{V_{osc}(t)}{Z_{mic}} + \frac{-V_{osc}(t)}{Z_{Co}}$$

=  $jw_{osc} \frac{2V_{osc}}{\pi} C_v * \frac{1}{2} [\sin((w_{osc} + w)t) - \sin((w_{osc} - w)t)], \quad for \ C_v = C_{mic} k\hat{P}$  (2.14)

Consequently, the amplitude of the sidebands at the output of the first amplifier can be expressed as:  $(A_1 \text{ and } A_2 \text{ are shown in Figure 2. 12.})$

$$A_{1} = A_{2} = \left| I(t) * \frac{R_{f}}{1 + j\omega_{osc}R_{f}C_{f}} \right| = C_{v} \frac{V_{osc}}{\pi} \frac{w_{osc}R_{f}}{\sqrt{1 + (\omega_{osc}R_{f}C_{f})^{2}}} [V]$$

(2.15)

If  $\frac{1}{2\pi R_f C_f}$  is much lower than the oscillation frequency  $f_{osc}$ , the amplitude of A<sub>1</sub> and A<sub>2</sub> can

be expressed as  $\frac{V_{osc}}{\pi} \frac{C_v}{C_f}$  which is about 10 dB ( $20\log_{10} \pi$ ) lower than the signal level of the charge amplifier scheme.

When the mixer is added, the sidebands of all harmonics are moved back and mixed together at the base frequency. (So does the noise.) The mixer can be regarded as the input multiplied with a symmetric square wave which is indicates in Figure 2. 13[25]. The Fourier transform of the symmetric square wave is given by:

$$F(m(t)) = \frac{4}{\pi} [\cos(\omega_{osc}t) + \frac{1}{3}\cos(3\omega_{osc}t) + \frac{1}{5}\cos(5\omega_{osc}t) + \dots]$$

(2.16)

Then the demodulated signal at the output of the LPF is given by:

$$A_{2}' = 2 * \left[ A_{2} * \frac{4}{\pi} + (\frac{1}{3})^{2} * A_{2} * \frac{4}{\pi} + (\frac{1}{5})^{2} * A_{2} * \frac{4}{\pi} + ... \right]$$

$$\approx 3.1432 * C_{v} \frac{V_{osc}}{\pi} \frac{w_{osc} R_{f}}{\sqrt{1 + (\omega_{osc} R_{f} C_{f})^{2}}} \cdot [V]$$

(2.17)

Figure 2. 13 Mixer demodulation.

#### 2.4.2 Noise Calculation

The noise calculation of AC biasing before adding the synchronized mixer is almost the same as that of the charge amplifier scheme which is given by:

$$v_{noise,out}^{2} = \overline{v}_{noise,in}^{2} \left( \frac{1 + j\omega R_{f} (2 * C_{mic} + C_{p} + C_{f})}{1 + j\omega R_{f} C_{f}} \right)^{2} + \overline{v}_{noise,R_{f}}^{2} \left( \frac{1}{1 + j\omega R_{f} C_{f}} \right)^{2} \quad [V^{2} / H_{Z}] \quad 18)$$

(Although the excitation source has phase noise, the noise calculation above is based on the assumption that the excitation source is noise free.)

Refer the output noise voltage power back to the capacitive noise power at input yields:

$$C_{noise}^{2} = \overline{v}_{noise,in}^{2} \left(\frac{\pi}{V_{osc}}\right)^{2} \left(\frac{1 + j\omega R_{f} (2 * C_{mic} + C_{p} + C_{f})}{\omega R_{f}}\right)^{2} + \overline{v}_{noise,R_{f}}^{2} \left(\frac{\pi}{V_{osc}}\right)^{2} \left(\frac{1}{\omega R_{f}}\right)^{2} [F^{2} / Hz]$$

(2.19)

Equation (2. 19) is similar to equation (2. 12). The difference is that the input referred noise of the amplifier in AC biasing is mainly thermal noise rather than 1/f noise and it is amplified by  $\frac{2*C_{mic} + C_p + C_f}{C_f}$ around the oscillation frequency since a compensation capacitor is added

to decrease the carrier signal.

The noise calculation in equation (2. 18), however, does not consider the 1/f noise coming from the oscillator. Since the bias voltage across the sensor is of square wave type and swings from ground to supply voltage, the electrostatic force between the membrane and the back plate is changing from now and then which will introduce nonlinearity problem.

## 2.5 Practical Measurement

Since we have the MEMS microphone in hand, it is interesting to test how it behaves with electronics. Thus a PCB (Printed Circuit Board) level investigation is made mainly for the AC biasing scheme.

#### 2.5.1 Amplitude Modulation

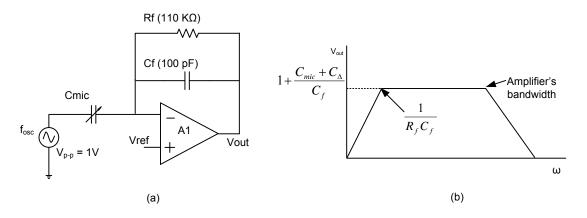

As has been explained in section 2.4, the principle behind the AC biasing scheme is based on amplitude modulation. It is also indicated in section 2.4 that the oscillation source used to drive the microphone should be of square wave type for considering a sine wave is more difficult to be implemented on transistor level. Since the measurement is at PCB level, a pure sine wave can be generated from an outside signal generator to drive the microphone. Consider the scheme in Figure 2. 14 (a), the signal generator which is connected to the microphone generates a pure sine wave with 0.5 voltage amplitude. The amplifier labeled as A1 is opamp NE5512 coming from the NXP Semiconductors. The sound is generated by PM5138A function generator through a speaker. It generates a sine wave with 10 V peak to peak amplitude and 1 KHz frequency. Due to the lack of a reference microphone, it is difficult to measure the actual sound pressure exerted on the membrane. The measurement is undertaken by setting V<sub>ref</sub> with different voltages to prove that the sensitivity of the microphone is increased by increasing the equivalent bias voltage exerted on it. The transfer function from the input to output of A1 behaves like a band-pass filter which is shown in Figure 2. 14 (b). The lower limit of the frequency is decided by  $\frac{1}{2\pi R_f C_f}$  which is about 14

KHz. And the higher limit of the frequency is decided by the bandwidth of the NE5512 which is about 3 MHz.

Figure 2. 14 (a) Scheme for realizing amplitude modulation. (b) Frequency response of the transfer function.

Due to the amplitude modulation, the signal at the output of A1 is composed of a main tone at the oscillation frequency with two relatively small sidebands which can be noticed on the spectrum analyzer. It is illustrated in Figure 2. 15 where  $f_{osc}$  represents the oscillation frequency;  $f_{sound}$  means the frequency of the input sound,  $A_m$  represents the magnitude of the main tone and  $A_s$  means the magnitude of the sidebands. If the pure oscillation sine wave can be represented by  $V_{osc}*sin(2\pi f_{osc}t)$  with  $V_{osc}$  as its amplitude,  $A_m$  and  $A_s$  in the flat band are given by:

$$A_m = \frac{C_{mic}V_{osc}}{C_f} \quad [V]$$

(2. 20)

and

$$A_s = \frac{1}{2} \frac{C_{mic} V_{osc} k \hat{P}}{C_f} \quad [V]$$

$$(2.21)$$

where  $C_f$  is the feedback capacitor, k has been mentioned in equation (1. 7) and P is the rms sound pressure exerted on the membrane. From equation (2. 21), it can be seen that the output signal is proportional to the amplitude of the oscillation source.

Figure 2. 15 Amplitude-modulated signal's spectrum.

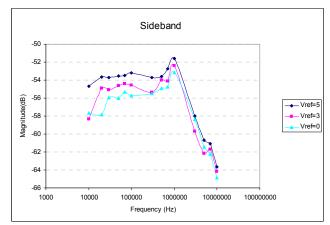

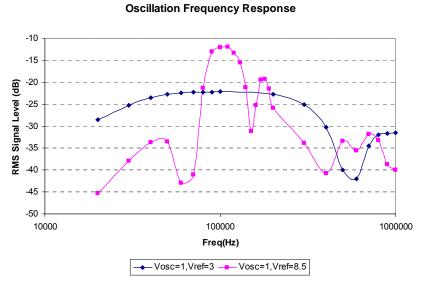

Figure 2. 16 shows the magnitude of the side band versus oscillation frequency under different bias voltages. The trend of these curves roughly performs like a band-pass filter as has been mentioned before. These curves in the band (14 KHz - 3 MHz) are not uniform as it is supposed to be. The peak sensitivity appears at 1 MHz.

Figure 2. 16 Magnitude of the side band under different bias voltage.

This effect may caused by the sensor itself. For a normal MEMS microphone, the curve of the sensitivity versus acoustical frequency is supposed to be flat at least in the audio band which is from 20 Hz to 20 KHz. The microphone used in the measurement can guarantee a flat frequency response up to 100 KHz acoustic frequency. When an oscillation source is exerted, the membrane of the microphone also vibrates with the oscillation frequency. Since the 3 MHz oscillation frequency has exceeded the flat frequency response band, there is possibility that the microphone dose not perform normally.

Figure 2. 16 not only proves that the sensitivity increases with increasing bias voltage but also provides a rough idea about the performance of the microphone driven by a sine wave oscillation source of different oscillation frequency.

The magnitude of the main tones versus oscillation frequency with different bias voltage is shown in Figure 2. 17. The trends of these three curves are almost the same with the side band in Figure 2. 16.

Figure 2. 17 Magnitude of the main tone under different bias voltage.

Comparing the magnitude in Figure 2. 16 and Figure 2. 17, we can see that the magnitude of the main tone is almost 60 dB higher than that of the side band. Therefore, it is necessary to reduce the main tone otherwise it may cause saturation problem of the preamplifier.

## 2.5.2 AC Biasing Setup

Figure 2. 18 shows the AC biasing scheme implemented at PCB level. The chain composed of NANDs and inverters is used to setup a two-phase non overlapping clock by decreasing the duty cycle of the square wave generated from an external signal generator. Since the supply voltage of all the NANDs and inverters on the board are 14V, clock signal  $\Phi$ 1 and  $\Phi$ 2 swings from 0 to 14V consequently. Therefore a resistive voltage divider is added to decrease the swing to a lower value. The potentiometer  $R_{p1}$  and  $R_{p2}$  are for the purpose of making the swing of  $\Phi$ 1 and  $\Phi$ 2 more tunable.

The opamps which are labeled as A1, A2 and A3 are opamp NE5512 coming from the NXP Semiconductors which has  $30 nV / \sqrt{Hz}$  as input referred noise and 3 MHz as small signal unity gain bandwidth. The STM-3 Microphone Preamplifier is for the purpose of amplifying the demodulated signal more easily by only tuning the mounted potentiometer.

The supply voltage is affected by the clock due to the fact that all the devices on the board share the same supply voltage. Thus, the system generates more harmonics than we expected. The RC network (R1&C1, R3&C3 in Figure 2. 18) which provides 20 KHz first-order cut-off frequency is not enough to reduce the harmonics. Therefore a 4<sup>th</sup>-order LPF with 10 KHz cut-off frequency is placed after to filter out the unexpected interferences from the clock and the higher harmonics.

## 2.5.3 Noise Analysis

We are interested in the noise behavior on the first stage of AC biasing which is shown in Figure 2. 19. The reason is that the first stage mainly decides the sensitivity of the scheme and the noise calculation is comparatively less complicated which will reduce the difference between the theoretical calculation and measurement.

Figure 2. 19 The first stage for AC biasing.

The total noise at the output is given by:

$$V_{_{mov}}^{2}(f) = 2 * \left( 4k_{B}TR_{p1} * \left(\frac{R_{a}}{R_{a} + R_{p1}}\right)^{2} + 4k_{B}TR_{a} * \left(\frac{R_{p1}}{R_{a} + R_{p1}}\right)^{2} \right) \cdot \left(\frac{j\omega R_{f}C_{mic}}{1 + j\omega R_{f}C_{f}}\right)^{2} + V_{_{n,opamp,in}}^{2} \cdot \left(\frac{1 + j\omega R_{f}(C_{f} + C_{mic} + C_{mic})}{1 + j\omega R_{f}C_{f}}\right)^{2} + 4k_{B}TR_{f} \cdot \left(\frac{1}{1 + j\omega R_{f}C_{f}}\right)^{2} [V^{2}/Hz]$$

$$(2.22)$$

where  $R_{p1}=R_{p2}=1950 \ \Omega$  (to decrease swing of the excitation voltage exerted on the microphone to 1 V),  $R_a=R_b$  and  $V_{n,opamp,in}^2$  is the input referred noise of the amplifier labeled as A1.

Equation (2. 22) was used to write a MATLAB script which yields Figure 2. 20. It shows the noise spectral density at the output of A1. It gives a general idea about the noise distribution at different frequencies. The plot shows that the noise level is low at high frequencies. Thus the amplitude modulation is expected to operate at high frequencies to get better signal-to-noise ratio.

Figure 2. 20 Noise versus frequency for the first stage of AC biasing.

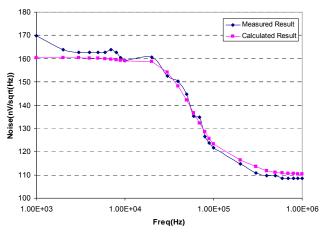

The noise at the output of A1 is also measured to check if the calculation in equation (2. 22) is correct. The noise measurement is undertaken by shorting the oscillation source to the ground. The result is shown in Figure 2. 21. The two curves agree to each other.

We can also predict the input-referred thermal noise level of the preamplifier by using equation (2. 15) and equation (2. 22). Assuming the amplitude of the oscillation source is 3.3 V and the feedback capacitor is 200 fF, the thermal noise level of the preamplifier is approximately  $7 nV / \sqrt{Hz}$  to achieve 60 dB SNR on the first stage without considering the thermal noise generated from the feedback resistor. It is not easy to realize such an amplifier on transistor level.

Figure 2. 21 Comparison of the noise measurement and calculation result for AC biasing.

## 2.5.4 Check Functionality

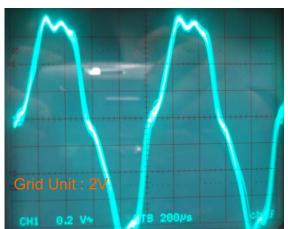

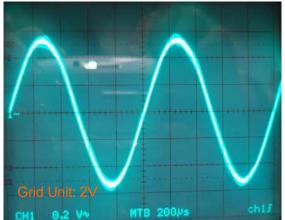

According to equation (1. 8) and (1. 9), the sensitivity of a microphone is proportional to the bias voltage exerted on it. And as has been mentioned in section 1.2, the pull-in voltage of the microphone is around 8V by experiment. Thus it is interesting to test the behavior of the microphone with different bias voltage and especially with pull-in voltage. Therefore, two

modes are tested. One is the normal mode which means that the equivalent bias voltage does not exceed the pull-in voltage. The other one is the collapse mode which means equivalent bias voltage exerted on the microphone is close or equal to the pull-in voltage. The collapse mode is expected to have high sensitivity because of the high bias voltage.

#### Normal Mode

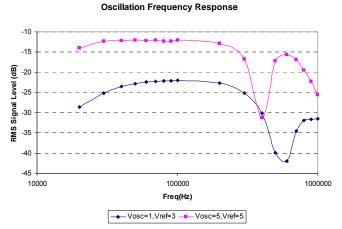

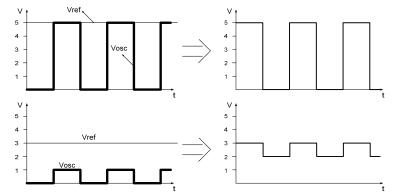

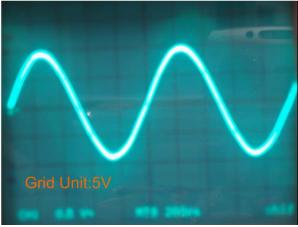

Figure 2. 22 illustrates the signal level to oscillation frequency response with two different biasing setups. The lower curve is tested with  $V_{ref} = 3$  V and  $V_{osc} = 1$  V. The higher curve is tested with  $V_{ref} = 5$ V and  $V_{osc} = 5$ V.  $V_{osc}$  is the amplitude of the oscillation source exerted on the microphone. Since the DC value of a square wave is half of its peak to peak amplitude, the equivalent DC voltage exerted across the microphone are both 2.5 V under two cases. It is illustrated in Figure 2. 23. The aim is trying to keep the sensitivity of the microphone same under these two cases.

Figure 2. 22 Response to oscillation frequency with different oscillation amplitude in normal mode.

Figure 2. 23 Equivalent voltage's waveform exerted on the microphone under two cases.

The two curves are flat when the oscillation frequency is lower than 200 KHz. They drop suddenly at 400 KHz and 600 KHz respectively. It may caused by the characteristic of the microphone itself. With oscillation source connected to the fixed back plate, the membrane will vibrate at the oscillation frequency without any acoustical signal input. It will cause nonlinearity and resonant issues. The microphone might behave badly under certain oscillation frequency. The two curves also imply that the maximum oscillation frequency of a

square wave type excitation source that the microphone can handle is approximately 200 KHz.

Equation (2. 15) indicates that the amplitude of the modulated signal which contains the sound's information is linear with the oscillator's amplitude. Therefore, the signal of the case

with  $V_{osc} = 5$  V should be 14 dB  $(20 \log \frac{5}{1})$  larger than that of the case with  $V_{osc} = 1$  V.