### Computer Engineering

Mekelweg 4, 2628 CD Delft The Netherlands https://qce.ewi.tudelft.nl/

## MSc THESIS

# A Dynamically Reconfigurable RISC-V Processor Based on the MOLEN Paradigm

D.M. van den Berg

#### Abstract

In this thesis, we present a RISC-V processor that is extended with the MOLEN ISA extension, thereby granting it dynamic reconfiguration capabilities. The reconfigurable microcode ( $\rho\mu$ -code) of the MOLEN paradigm is modified to be suitable for (FPGA) implementation in the 64-bit Linux-capable CVA6 RISC-V processor. The set instruction performs reconfigurations by pointing it to a partial bitstream address, after which the execute instruction can perform operations on the reconfigured hardware. To this end, the concept of nested  $\rho\mu$ -code is presented, in which the reconfigurable opcodes are encapsulated in regular RISC-V instructions. Furthermore, a status instruction is introduced to enable the reconfiguration to be performed in the background. Consequently, the reconfiguration latency can be hidden, by allowing the CPU to do useful work during the reconfiguration. Using various experiments, it is demonstrated that the proposed implementation has a near-optimal reconfiguration performance and that the reconfiguration latency can be effectively hidden in typical cases.

Keywords: MOLEN Processor, RISC-V, reconfigurability, microcode

# A Dynamically Reconfigurable RISC-V Processor Based on the MOLEN Paradigm

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

COMPUTER ENGINEERING

by

D.M. van den Berg born in Dordrecht, the Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# A Dynamically Reconfigurable RISC-V Processor Based on the MOLEN Paradigm

by D.M. van den Berg

#### Abstract

In this thesis, we present a RISC-V processor that is extended with the MOLEN ISA extension, thereby granting it dynamic reconfiguration capabilities. The reconfigurable microcode  $(\rho\mu-\text{code})$  of the MOLEN paradigm is modified to be suitable for (FPGA) implementation in the 64-bit Linux-capable CVA6 RISC-V processor. The set instruction performs reconfigurations by pointing it to a partial bitstream address, after which the execute instruction can perform operations on the reconfigured hardware. To this end, the concept of nested  $\rho\mu-\text{code}$  is presented, in which the reconfigurable opcodes are encapsulated in regular RISC-V instructions. Furthermore, a status instruction is introduced to enable the reconfiguration to be performed in the background. Consequently, the reconfiguration latency can be hidden, by allowing the CPU to do useful work during the reconfiguration. Using various experiments, it is demonstrated that the proposed implementation has a near-optimal reconfiguration performance and that the reconfiguration latency can be effectively hidden in typical cases.

**Laboratory** : Computer Engineering

Committee Members :

Advisor: Dr. ir. J.S.S.M. Wong, CE, TU Delft

Chairperson: Dr. ir. J.S.S.M. Wong, CE, TU Delft

Member: Dr. ir. T.G.R.M van Leuken, SPS, TU Delft

Dedicated to my family and friends

# Contents

| Li | st of      | Figures                                            | vii      |

|----|------------|----------------------------------------------------|----------|

| Li | st of      | Tables                                             | ix       |

| Li | st of      | Acronyms                                           | xii      |

| A  | cknov      | wledgements                                        | xiii     |

| -  | <b>T</b> , |                                                    | -        |

| 1  |            | oduction                                           | 1        |

|    | 1.1<br>1.2 | Motivation                                         | 1        |

|    | 1.3        | Problem statement and goals                        | 2<br>3   |

|    | 1.4        | Thesis structure                                   | 4        |

|    | 1.7        |                                                    | 7        |

| 2  | Bac        | kground                                            | 5        |

|    | 2.1        | Reconfigurable architectures                       | 5        |

|    |            | 2.1.1 Application domains                          | 5        |

|    |            | 2.1.2 Reconfigurable granularity                   | 6        |

|    |            | 2.1.3 Coarse-Grained Reconfigurable Arrays (CGRAs) | 6        |

|    | 2.2        | The MOLEN polymorphic processor                    | 7        |

|    |            | 2.2.1 MOLEN ISA extension                          | 7        |

|    |            | 2.2.2 MOLEN organization                           | 8        |

|    | 2.3        | The RISC-V architecture                            | 8        |

|    | 2.4        | FPGA platform                                      | 10       |

|    | 2.5        | RISC-V implementation                              | 10       |

|    |            | 2.5.1 Requirements                                 | 10       |

|    | 2.6        | 2.5.2 Core selection                               | 11<br>14 |

|    | 2.0        | Related work                                       | 14       |

|    |            | 2.6.2 Comparison                                   | 16       |

|    | 2.7        | Conclusions                                        | 17       |

| 3  | Des        | ign                                                | 19       |

|    | 3.1        | RISC-V instruction formats                         | 19       |

|    | 3.2        | RISC-V opcode space                                | 21       |

|    | 3.3        | Microcode design                                   | 22       |

|    |            | 3.3.1 Reconfiguration microcode                    | 22       |

|    |            | 3.3.2 Execution microcode                          | 23       |

|    | 3.4        | Proposed ISA extension                             | 24       |

|    | 2 5        | Canalusians                                        | 25       |

| 4  | Imp     | plementation                          | <b>27</b> |

|----|---------|---------------------------------------|-----------|

|    | 4.1     | Implementation overview               | 27        |

|    | 4.2     | Memory interface                      | 30        |

|    | 4.3     | Instruction decoder                   | 31        |

|    | 4.4     | MOLEN functional unit                 | 31        |

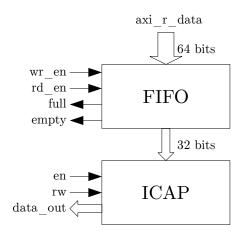

|    |         | 4.4.1 Partial reconfigurator          | 33        |

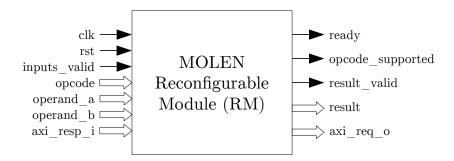

|    |         | 4.4.2 MOLEN reconfigurable module     | 34        |

|    |         | 4.4.3 AXI interface                   | 35        |

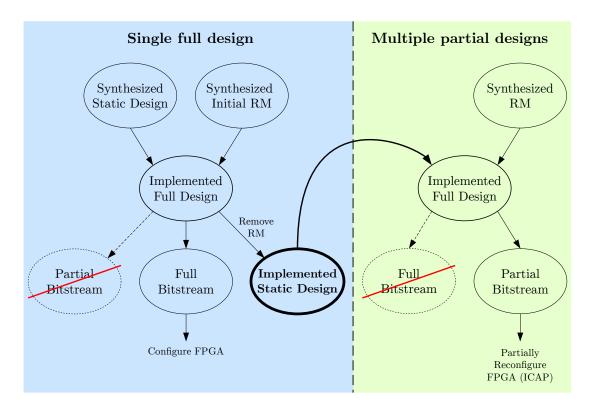

|    | 4.5     | Reconfigurable design flow            | 36        |

|    | 4.6     | Software design                       | 38        |

|    | 4.7     | Conclusions                           | 39        |

| 5  | Res     | aults                                 | 41        |

|    | 5.1     | Test setup                            | 41        |

|    | 5.2     | Functional tests                      | 42        |

|    | 5.3     | FPGA synthesis results                | 43        |

|    | 0.0     | 5.3.1 Timing results                  | 43        |

|    |         | 5.3.2 Resource utilization            | 44        |

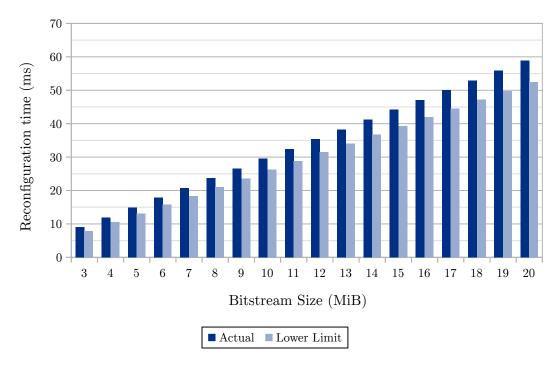

|    | 5.4     | Reconfiguration performance benchmark | 45        |

|    |         | 5.4.1 Benchmark description           | 45        |

|    |         | 5.4.2 Discussion                      | 47        |

|    | 5.5     | Matrix multiplication benchmark       | 49        |

|    |         | 5.5.1 Benchmark description           | 49        |

|    |         | 5.5.2 Discussion                      | 50        |

|    | 5.6     | Discussion                            | 52        |

|    | 5.7     | Conclusions                           | 53        |

| 6  | Cor     | nclusion                              | 55        |

| Ū  | 6.1     | Summary                               | 55        |

|    | 6.2     | Main contributions                    | 58        |

|    | 6.3     | Future work                           | 59        |

|    | 0.0     | 6.3.1 ASIC implementation             | 59        |

|    |         | 6.3.2 Microcode redesign              | 60        |

| D: | hlias   | graphy                                | 66        |

| D  | เกเเดีย | graphy                                | OO        |

# List of Figures

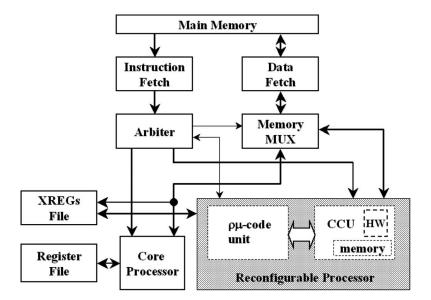

| 2.1 | The MOLEN machine organization. Image courtesy of [1]                                                                              | 8  |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

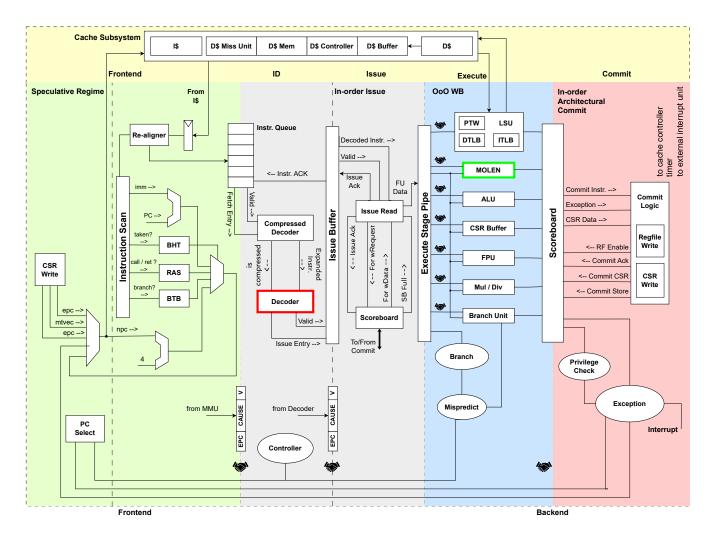

| 4.1 | The CVA6 architecture with the modified and added components. Image adapted from [2]                                               | 29 |

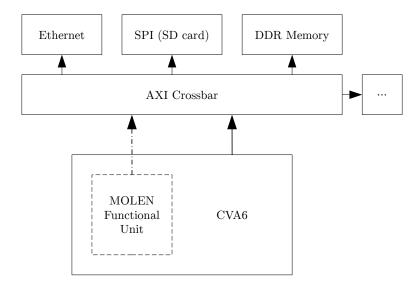

| 4.2 | The CVA6 interface diagram highlighting the AXI interfaces. The arrows point from the AXI master ports towards the AXI slave ports | 30 |

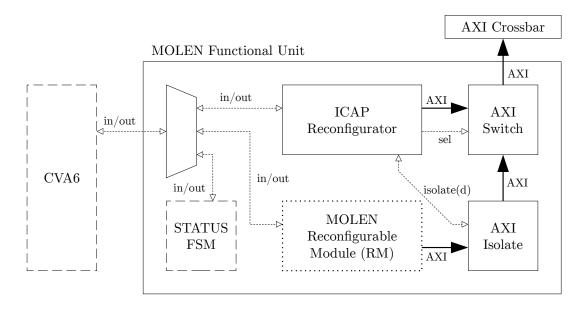

| 4.3 | An overview of the implementation of the MOLEN functional unit                                                                     | 32 |

| 4.4 | An overview of the implementation of the partial reconfigurator                                                                    | 33 |

| 4.5 | The MOLEN reconfigurable module, highlighting the inputs and outputs.                                                              | 34 |

| 4.6 | A simplified overview of the two design flows for a partially reconfig-                                                            |    |

|     | urable design                                                                                                                      | 37 |

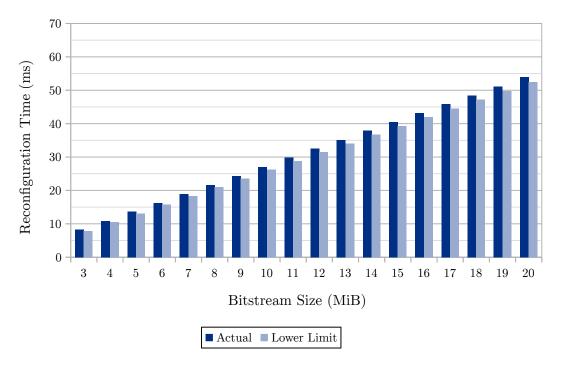

| 5.1 | Reconfiguration times compared with the theoretical lower limit, running                                                           |    |

|     | at 50 MHz                                                                                                                          | 46 |

| 5.2 | Reconfiguration times compared with the theoretical lower limit, running                                                           |    |

|     | at 55 MHz                                                                                                                          | 47 |

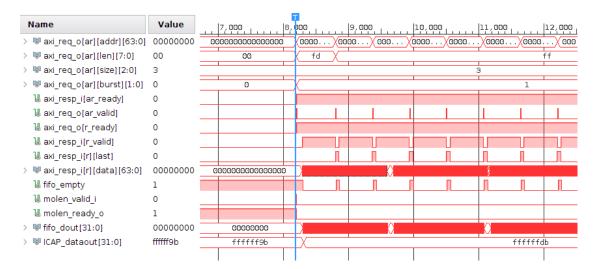

| 5.3 | Waveform data captured at the start of the reconfiguration                                                                         | 48 |

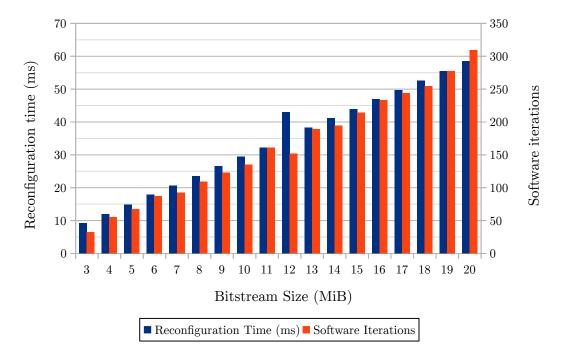

| 5.4 | Reconfiguration time and number of software iterations for the 8x8 Ma-                                                             |    |

|     | trix multiplication                                                                                                                | 49 |

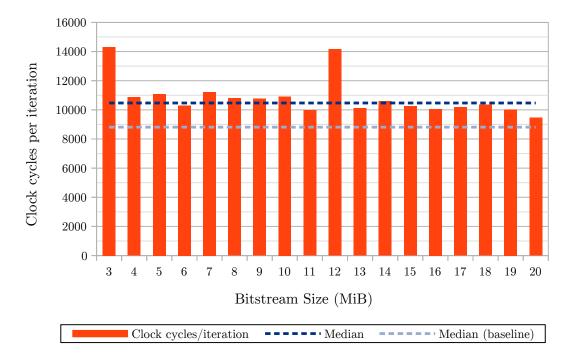

| 5.5 | Average clock cycles per software iteration of the 8x8 matrix multipli-                                                            |    |

|     | cation benchmark                                                                                                                   | 50 |

# List of Tables

| 2.1 | Overview of RISC-V cores that have a permissive license and use a classical Hardware Description Language (HDL) | 13 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

| 3.1 | 32-bit RISC-V instruction formats. Adapted from the RISC-V Instruction Set Architecture (ISA) specification[3]  | 10 |

| 3.2 | RV32/64G opcode map, inst[1:0]=11. Adapted from Table 24.1 of the                                               | 19 |

| 0.2 | RISC-V ISA specification[3]                                                                                     | 21 |

| 3.3 | The proposed RISC-V MOLEN extension, consisting of three R-type                                                 |    |

|     | instructions. The funct10 field refers to the combined funct7 and funct3                                        |    |

|     | fields                                                                                                          | 24 |

| 5.1 | Overview of the functional tests that were performed on the implemented                                         |    |

|     | design                                                                                                          | 42 |

| 5.2 | Timing results for the base CVA6 and MOLEN CVA6 implementations.                                                |    |

|     | A checkmark indicates that all timing constraints are met                                                       | 44 |

| 5.3 | Resource utilization of the base CVA6 design and the modified design                                            | 44 |

# List of Acronyms

ALU Arithmetic Logic Unit

ASIC Application Specific Integrated Circuit

AXI Advanced eXtensible Interface

**CCA** Configurable Compute Accelerator

CCU Custom Configured Unit

CGRA Coarse-Grained Reconfigurable Array

CPU Central Processing Unit

CSR Control and Status Register

**DMA** Direct Memory Access

FIFO First-In-First-Out

FPCA Fully Pipelined Composable Architecture

FPGA Field Programmable Gate Array

$\mathbf{FPU}$  Floating Point Unit

FSM Finite State Machine

**HDL** Hardware Description Language

**HLS** High-Level Synthesis

IC Integrated Circuit

ICAP Internal Configuration Access Port

ILA Integrated Logic Analyzer

**ISA** Instruction Set Architecture

LSU Load Store Unit

**LUT** Lookup Table

**OS** Operating System

PC Program Counter

**PE** Processing Element

PULP Parallel Ultra Low Power

**RAM** Random Access Memory

**RTL** Register-Transfer Level

RTOS Real-time Operating System

${\bf SIMD}\,$  Single Instruction, Multiple Data

SoC System on Chip

$\mathbf{XREG}$  Exchange Register

# Acknowledgements

At the end of the journey that this MSc. project has been, there are some people I would like to express my gratitude to. Without them, completing this thesis would have been much harder, or perhaps even impossible.

First of all, I want to thank dr. ir. Stephan Wong, my thesis supervisor, for all of his advice and guidance. I would also like to thank him for his patience and understanding when I was putting too much pressure on myself.

I also want to thank dr. ir. René van Leuken for being part of my thesis committee, as well as for accommodating my thesis defense close to his retirement.

Furthermore, I want to thank my family for their continued support, without which I probably would not have been able to see this project through to the end.

Finally, I would like to thank Eline, whose insights have helped me to get back on track when things got tough.

D.M. van den BergDelft, The NetherlandsNovember 12, 2024

Introduction

In this thesis, the design of a dynamically reconfigurable processor is documented. The MOLEN paradigm is applied to the open-source RISC-V Instruction Set Architecture (ISA), resulting in a reconfigurable design that could aid the adoption of reconfigurable architectures in multiple domains.

In Section 1.1, the motivation of this project is discussed. Subsequently, the main research question and goals are formulated in Section 1.2. These goals are then adapted into the methodology of the project in Section 1.3. Finally, the structure of this thesis is outlined in Section 1.4.

#### 1.1 Motivation

Historically, the widely known observation known as Moore's law ensured a continuous progression of the Integrated Circuit (IC) design process, by setting the industry goals. Back in 1965, it described the transistor scaling as a doubling of the IC transistor count every year [4]. Ten years later, it was adjusted to a doubling every two years [5], a trend that continued even in recent years.

Another observation that aided in this progression is Dennard Scaling, which describes that the power density of the transistors stays constant as the size decreases [6]. As a result, the (single-core) processor performance was able to continuously increase by developing larger and faster cores.

However, Dennard Scaling ceased to hold true around 2005 [7], resulting in increased power and heat buildups that halted single-core improvements [8]. This problem was mitigated by switching to multi-core processors, allowing the additional available transistors (resulting from Moore's law) to be used for additional cores instead of larger and faster cores [8] [9].

Though the switch to multi-core has extended Moore's law, it has become clear in recent years that CMOS transistor scaling is coming to an end due to physical limitations. This limit is expected to be a channel length of around 3 nm, but the practical limit could be even higher [10].

In addition to the absolute scaling limit, recent chips already suffer from another effect known as dark silicon: due to the end of Dennard scaling, power constraints limit the amount of transistors that can be used at the same time, causing parts of the chip to remain "dark" (turned off) [9]. Decreasing the transistor sizes worsens this effect due to the higher relative power consumption.

Finally, the limited inherent parallelism of typical software applications poses limits on the simultaneously usable chip area, in which case the power limitations do not even come into play [9].

The previous observations make it clear that new innovations are necessary in order to continue the performance increases and power decreases. Such innovations can take place in the following abstraction layers:

- 1. The **architecture** deals with the conceptual structure of the design and the functional behavior as observed by the user or developer. This includes the ISA.

- 2. The **implementation (micro-architecture)** defines how the architecture is implemented on a logical level.

- 3. The **realization** provides the physical structure of the micro-architecture. This includes the process technology and the physical layout of the transistors in that technology.

Potentially, changes in the lower abstraction levels will also require changes to the higher levels. For example, in a shift to quantum computing, all levels would be drastically changed. By extending the architecture with reconfigurability, compatibility with regular architectures can be maintained, while at the same time being able to use the available hardware more efficiently for the specific task at hand. Instead of having a lot of fixed, specialized units that cannot all be used at the same time due to the dark silicon effect, a reconfigurable unit provides an effective method of using the available area for functional units or accelerators that can be used at the same time. For that reason, reconfigurability is the chosen improvement avenue in the MSc. project described in this thesis. Moreover, associated with reconfigurability is always the reconfiguration latency of the underlying (reconfigurable) hardware fabric. Consequently, reconfiguration latencies (or the hiding thereof) will also be part of our project.

## 1.2 Problem statement and goals

Based on the motivation of the previous section, the research question can be formulated as follows:

Will the application of the MOLEN paradigm to a modern processor allow for hiding reconfiguration latencies?

From this research question, the main goal can be derived, namely to introduce reconfigurability to an existing processor by implementing the MOLEN instruction set extension. Specifically, a functional reconfigurable design will be implemented, by using an existing RISC-V core and integrating the MOLEN scheme into it. In order to make this feasible, a minimal working design is considered sufficient. In other words, the goal of the implementation is to provide a proof of concept rather than a full-fledged design. This means the MOLEN scheme will be simplified to a minimal version. Specifically:

Having a single reconfigurable area in which custom designs can be loaded is sufficient. Having multiple reconfigurable areas from the start would increase the complexity of the implementation towards a full-fledged design, which is not the goal of this project as stated before.

- The reconfigurable unit is intended for executing single (custom) instructions (or small sequences of instructions). No branching capabilities will be added.

- A single location will be used for storing the reconfigurable code (the main memory). No distinction will be made between often and less often used code, simplifying the loading of the programs.

In contrast with the original MOLEN scheme, the  $\rho\mu$ -code (as introduced in Section 2.2) is intended for use by developers/programmers instead of being hidden from them like traditional microcode. The reason for that is that the proposed design is a proof-of-concept, which should enable developers to experiment with the reconfigurable hardware, instead of locking them out from the specifics.

The desired outcome of this project is an FPGA-based implementation of a (soft-) RISC-V core with the described reconfiguration capabilities, using the MOLEN instruction set extension.

## 1.3 Methodology

In order to achieve the goals from the previous section and be able to answer the research question, the following set of milestones is followed during the MSc. project described in this thesis:

- 1. **Literature Study:** Compare existing reconfigurable architectures, such that the use of the MOLEN paradigm for this project can be justified.

- 2. **Minimal working design:** A minimal working implementation of a RISC-V core that is able to run (C) programs. No reconfiguration is performed in this stage. This design will also function as reference implementation during the final milestone.

- (a) **Select the RISC-V core:** Choose a core implementation that is suitable for extension with reconfigurability.

- (b) **Design the basic SoC:** Integrate the chosen core into a SoC containing memory and all necessary interfaces/buses. If possible, an existing SoC design could also be chosen, simplifying this milestone.

- (c) **Test the design:** Verify correct working of the design by compiling and running some basic code.

- 3. **Reconfigurable design:** Extend the minimal design with reconfigurability such that it can execute  $\rho\mu$ -code.

- (a) **Design the reconfigurable unit:** Design a standalone reconfigurable unit that is able to reconfigure the hardware and perform instructions on that hardware, using  $\rho\mu$ -code.

- (b) Integrate the reconfigurable unit: Integrate the reconfigurable unit into the core by implementing the arbiter that distinguishes between  $\rho\mu$ -code and

regular instructions (as introduced in Section 2.2). This may include a minimal compiler/assembler modification such that the *set/execute* instructions can be performed.

- 4. **Result verification:** Once the design is completed and functional, the performance and (resource) costs need to be compared to the standalone RISC-V implementation without reconfigurability.

- (a) **Select Application:** Choose a suitable application that can highlight the benefits of the reconfigurable design by allowing the reconfiguration latency to be hidden. For example, JPEG compression could be chosen in line with the previous work on the MOLEN architecture. Instead of a real-world application, a simplified benchmark may also be chosen.

- (b) **Implement software-only application:** Implement the chosen application on the regular RISC-V design.

- (c) **Implement soft-/hardware application:** Implement the chosen application on the reconfigurable RISC-V design.

- (d) **Result comparison:** Compare the results of both designs in terms of performance and resource usage.

#### 1.4 Thesis structure

The remainder of this thesis is structured in the following way: in Chapter 2, the concepts that this work builds on are introduced, a RISC-V core is selected for the modifications of this project, and related work is explored. In Chapter 3, the MOLEN paradigm is adapted to the RISC-V ISA, resulting in a proposed ISA extension. In Chapter 4, the implementation of the proposed extension into the selected RISC-V core is discussed. The resulting implementation is subjected to a number of experiments in Chapter 5. Finally, this thesis is summarized and concluded in Chapter 6.

Background

As the research question stated in Chapter 1 pertains to reconfigurable architectures, this chapter will briefly introduce related concepts and related work to better understand the work of this MSc thesis project.

First, a general introduction to reconfigurable architectures is given in Section 2.1. Subsequently, the MOLEN paradigm is introduced in Section 2.2, followed by the introduction of the RISC-V architecture in Section 2.3. The Field Programmable Gate Array (FPGA) platform that was used for this project is introduced in Section 2.4, after which an existing RISC-V implementation is selected for modification with the MOLEN paradigm in Section 2.5. Following that, related work is explored in Section 2.6. Finally, this chapter is concluded in Section 2.7.

## 2.1 Reconfigurable architectures

With the need for reconfigurable architectures being explained in Section 1.1, the current section can focus on the types of reconfigurable architectures and their use cases. First, two common application domains are described. Subsequently, the primary architectural classification of reconfigurable systems is introduced. Finally, an introduction to a common type of reconfigurable architecture is given.

#### 2.1.1 Application domains

Reconfigurability seems to be primarily applied in the following two domains: high performance computing and embedded systems. This section provides an introduction into both domains.

In the case of **high performance computing**, it is usually applied by means of reconfigurable accelerators (FPGAs). There, speedups of a factor 32 and energy reductions of a factor 36 have been achieved [11]. Logically, the reconfigurable hardware increases the (programming) complexity, but frameworks and high level languages can help mitigate this added complexity. For example, OpenCL can be used for these kind of accelerators.

The use of a separate reconfigurable accelerator poses a bandwidth limitation on the speed and amount of data that can be processed at once. A bus must be used to interface the processor and accelerator, resulting in communication overhead.

In the case of **embedded systems**, performance and energy efficiency is not necessarily the motivation for applying reconfigurability. Typically, embedded systems need to deal with time-critical operations, in addition to non time-critical ones. Traditionally, embedded processors took care of the non time-critical tasks, whereas Application Specific Integrated Circuits (ASICs) performed the time-critical ones. However, ASIC

development results in lengthy design cycles. With FPGA performance approaching ASIC performance over the years, FPGAs became the component of choice in typical embedded systems [12]. Not only did this shorten the design cycle, it also allowed for loading new configurations onto the reconfigurable fabric when needed.

More recently, embedded processors became capable enough to meet the timing constraints of the time-critical tasks, reducing the need for ASICs or FPGAs next to the processor. However, specialized tasks such as multimedia processing will still require hardware implementation in order to meet timing constraints. In addition to that, reconfigurable hardware increases the flexibility of the system and allows for future changes without needing a new platform. Finally, in cases where reconfigurability would not be required for performance reasons, it could still be useful for energy efficiency, as it allows a smaller processor to be used by implementing the time-critical functions in the reconfigurable fabric.

#### 2.1.2 Reconfigurable granularity

Different kinds of reconfigurable systems exist. An important architectural distinction can be made between fine-grained and coarse-grained reconfigurable systems. Fine-grained reconfigurable systems allow for complete reconfiguration at the lowest level (gate level), whereas coarse-grained reconfigurable systems only allow a higher-level reconfiguration on a block level.

Though fine-grained systems offer more flexibility, they typically use more power and run at lower clock speeds. Coarse-grained systems decrease the flexibility but can run at higher clock speeds and are more energy efficient. However, recent FPGAs often provide coarse-grained blocks in addition to fine-grained ones. Therefore, the choice of FPGA already influences the reconfigurable granularity.

#### 2.1.3 Coarse-Grained Reconfigurable Arrays (CGRAs)

A specific, common type of coarse-grain reconfigurable architecture is the Coarse-Grained Reconfigurable Array (CGRA). Its name is derived from its structure: a CGRA consists of an array of Processing Elements (PEs). Each PE can be seen as a tiny processor that has access to some memory, logic and arithmetic units. The precise structure of the PEs varies between CGRA implementations and is determined by the use case of the system. As such, the PE structure can vary from a small processor with its own instruction set to a data flow unit that only has a few instructions. Such a data flow unit can quickly compute and accumulate results once the inputs are ready. The results can then be passed around to other PEs.

Though the variety in the PE structure results in an equal variety in the CGRA use cases and performance, the parallel nature of the structure implies that it is mostly suitable for speeding up computations on large amounts of data.

## 2.2 The MOLEN polymorphic processor

Historically, microcode was used to implement (emulate) instructions that could not be implemented in hardware at that time. Thanks to Moore's law, those instructions could then be converted to hardware instructions in later designs. This way, the ISA could be developed independently from the technological state of the hardware. Even though some instructions required emulation using microcode, software developers were presented with a uniform set of instructions, without being able to distinguish between microcoded and hardware instructions.

The MOLEN polymorphic processor takes this concept to a new level, by defining reconfigurable microcode ( $\rho\mu$ -code) [1]. This new kind of microcode can be used to perform the reconfiguration of the reconfigurable fabric, as well as to execute custom operations on the configured fabric. Because microcode is used for these operations, a one-time ISA extension is sufficient. This extension contains a set and execute instruction. The set instruction configures the reconfigurable fabric, whereas the execute instruction performs operations on the configured hardware. Both of these instructions work by taking the address of the to-be-executed microcode. Microcode execution will then commence at that address, after which it continues until a special end\_op micro-instruction is encountered. set instructions are derived from the reconfiguration file (bitstream) by splitting that file into equally sized blocks, to which the set opcode is then appended.

#### 2.2.1 MOLEN ISA extension

The one-time architectural extension required for implementing the MOLEN machine can be one of the following [1]:

- Minimal extension: this extension contains only the essential instructions that are required for a working implementation. These are set, execute, movtx and movfx. Here, set and execute reconfigure the Custom Configured Unit (CCU) (as introduced in Section 2.2.2) and execute code on the reconfigured CCU, respectively. The movtx and movfx instructions allow arguments to be written to and loaded from the exchange registers, respectively. The set instruction is actually a c-set instruction that configures the entire CCU.

- **Preferred extension:** This extension adds a *p-set* instruction that (pre-)configures parts of the CCU. The *c-set* instruction that was already present then configures only the remaining part of the CCU. Additionally, this extension defines *prefetch* instructions for the *set* and *execute* instructions, that enable microcode loading before it is needed. This diminishes the loading times.

- Complete extension: This final extension adds a *break* instruction that allows synchronization between the Central Processing Unit (CPU) and reconfigurable unit, such that parallel execution can take place. Now, the CPU and reconfigurable unit will run in parallel when an *execute* instruction is issued. Subsequently, the *break* instruction is used to wait for the termination of the CPU and reconfigurable instructions.

Figure 2.1: The MOLEN machine organization. Image courtesy of [1].

#### 2.2.2 MOLEN organization

An overview of the MOLEN machine organization is depicted in Figure 2.1. The MOLEN machine extends a regular von Neumann architecture with the following components:

- The Reconfigurable Processor provides (as the name implies) the actual reconfigurable hardware and the control of that hardware. It consists of a CCU and a  $\rho\mu$ -code unit. The CCU provides the reconfigurable fabric, whereas the  $\rho\mu$ -code unit deals with the microcode initialization, loading, execution and storage. In order to have a tight integration of the reconfigurable hardware with the other parts of the system and boost performance, the CCU has Direct Memory Access (DMA). It should also be noted that the  $\rho\mu$ -code unit does not decode the actual micro-instructions, leaving this to the CCU instead (or optionally to a fixed or hybrid decoder).

- The **Arbiter** decodes the fetched instructions and issues them to either the Core Processor (regular instructions) or the  $\rho\mu$ -code unit (set/execute instructions).

- The Exchange Registers (XREGs) enable the Core Processor to pass function arguments to the reconfigurable unit, and to retrieve the corresponding results.

#### 2.3 The RISC-V architecture

The RISC-V architecture is an open-source ISA that originated in the Parallel Computing Laboratory (Par Lab) at UC Berkeley [13]. The Par Lab was funded by Intel and Microsoft to advance parallel computing and ran from 2008 to 2013. Halfway through, in May 2010, this resulted in the inception of the RISC-V instruction set. This was followed by the first specification of the ISA in 2011 [14]. Influenced by many previous

ISAs [15], the RISC-V specification was not originally a goal of the project, but rather a means to achieve the goals relating to research into parallel processing systems [13]. However, the open nature of the specification attracted worldwide attention, because it allows anyone to develop their own hardware, while being able to share the software. Since its inception, work on the RISC-V ISA has continued, and in 2015 the RISC-V Foundation was formed to direct the development and stimulate the adoption of the ISA [16].

Despite parallel processing systems being the initial motivation for the creation of the ISA, it supports a wide range of applications. This is due to the highly modular design of the ISA with multiple bases and extensions [3]. Specifically, the following base instructions sets are defined:

- RV32I: A 32-bit (integer) instruction set covering 40 basic instructions such as load and store operations.

- RV32E: A 32-bit (integer) instruction set for embedded systems. This instruction set limits the number of registers to 16, as opposed to 32 for the RV32I instruction set. It is equal otherwise.

- RV64I: A 64-bit (integer) instruction set. This instruction set is also based on the RV32I instruction set, but widens the registers to 64 bits. Furthermore, 15 instructions are added to the base RV32I instruction set.

- RV128I: A 128-bit (integer) instruction set. Like the RV64I instruction set, it expands the register widths, albeit to 128 bits instead of 64. It is primarily intended for future use cases, when address spaces larger than 64 bits might be required [3].

Because these base instruction sets define only simple operations, several standard extensions are also defined, providing operations such as integer multiplication and division or atomic instructions. By making the instruction set modular in this way, it is suitable for a wide range of applications, ranging from high-performance computing to general purpose computing and embedded systems.

In addition to its modularity, the instruction set also supports custom extensions and has special opcodes reserved for such extensions [3]. This enables hardware developers to include their own (specialized) instructions to make their processor implementation suitable for the envisioned application domain.

These advantages, as well as the available compiler and simulator support, make the RISC-V architecture very suitable for extension with reconfigurability. By basing such a design on the RISC-V ISA, it is implicitly made suitable for a broad range of applications. The ability to add custom instructions ensure that the one-time ISA extension as defined by the MOLEN paradigm can also be added. Finally, the open nature of the RISC-V ISA enables developers to built on previous work and re-use existing open-source processor implementations instead of having to reinvent the wheel.

## 2.4 FPGA platform

The hardware platform that is used for the implementation of this project is the Xilinx VC707 evaluation kit [17], which is built around the Virtex-7 XC7VX485T-2FFG1761C FPGA. It has 485760 logic cells and 37080 KB of on-chip memory. The board also includes 1 GB DDR3 memory with speeds up to 1600 Mbps. All in all this should provide enough resources for the implementation of the project. Partial reconfiguration is also supported, allowing the intended reconfiguration of this project.

## 2.5 RISC-V implementation

As mentioned in Section 2.3, a major advantage of the RISC-V ISA is that it is open-source and can be implemented by anyone. As a result, multiple open-source core implementations have been developed. Instead of having to reinvent the wheel, it is possible to select an existing RISC-V core and extend it with the proposed reconfigurability. Since the design of a RISC-V core is not one of the goals of this thesis, the additional efforts in implementing and testing such a core can be saved.

Instead of just cores, open-source Systems on Chip (SoCs) are available as well. These SoCs use one of the cores and add memory, peripherals and interconnects to the chip. This results in a ready-to-use or nearly ready-to-use design. Such a design is preferable for this project, for the same reason as stated before.

#### 2.5.1 Requirements

Because multiple implementations are available, the most suitable one needs to be selected. To do so, a set of requirements must be specified. Most of those requirements focus on the core (and SoC) being small or simple, in order to aid the implementation of the reconfigurable extension. The following list of requirements is used:

- Hardware support: The core should be compatible with the Xilinx VC707 board that is used in this project. Having official support in addition to that would be a nice-to-have.

- Instruction width: Preferably, the core should be 32-bit to reduce the complexity of the design. However, a 64-bit core would be acceptable, as long as it fits on the FPGA.

- **Single core:** Instead of using multiple cores and complicating the design, a single core is sufficient for this project.

- Extensibility: The SoC must accommodate the extension with the proposed reconfigurability. This includes the ability for DMA from within the reconfigurable part of the system.

- **Simulation and debugging support:** In order to successfully develop hardware designs, proper simulation and debugging support is essential.

- Scalar execution: Instead of using redundant functional units to achieve superscalar execution, the core should be scalar to reduce its complexity.

- Hardware Description Language (HDL) implementation: The core should be implemented in one of the classical HDL languages (VHDL, Verilog or SystemVerilog). Compared to High-Level Synthesis (HLS) languages, these are more widely supported and enable more reusability.

- **Documentation:** In order to be usable, the core should have proper documentation or at least use clean and well-written code.

- Community backing: in any open-source project, including SoC implementations, sufficient community backing is vital to the viability of the project. Projects with single developers behind them are more prone to being abandoned or insufficiently maintained than projects with large communities behind them. To ensure future work on the proposed design is feasible, the selected core should have sufficient community support.

- Compliance Suite: The implementation should preferably pass the (draft) RISC-V compliance suite, since doing so provides guarantees about the correctness and compatibility of the core.

- **ASIC support:** In addition to supporting FPGA synthesis, the SoC should be suitable for ASIC implementation, in order to accommodate future work on the proposed design.

- **Permissive license:** For the SoC to be usable in this project, the license under which it is released must allow using, modifying and distributing the source code. This means that no commercial implementations will be considered.

- Operating System (OS) support: To allow a future continuation of this project, readily available support for an OS is preferable. This opens the possibility for future research into OS integration of the current design.

Using this set of requirements, the available SoC implementations can be evaluated. An overview of available cores and SoCs on the RISC-V website is used as starting point [18]. The first step consists of evaluating the available cores. When the suitable cores are identified, the SoC implementations using those cores (or custom cores) can be evaluated.

#### 2.5.2 Core selection

Inspecting the list of available cores, the first observation that can be made is that a large number of cores is released under a commercial or restrictive license. Following the requirements, these cores will not be considered for this project. At the time of writing, 66 RISC-V cores are available, of which 35 are released under a permissive license. Of these 35 cores, 12 are implemented in (novel) high-level languages, such as Chisel or Bluespec. These cores will not be considered per the requirements, which leaves the 23 cores listed in Table 2.1 for consideration.

It can be observed from the table that only a few cores offer OS support out of the box. Most of these cores support the Zephyr OS, which is an (embedded) Real-time Operating System (RTOS). Preferred over an RTOS would be a full-fledged OS such as Linux, due to its larger range of use cases. Two of the available cores offer support for Linux: The CVA6 and the biRISC-V. The biRISC-V core appears to be the work of a single developer and lacks community backing. By looking further into the CVA6 core, we can now decide if it suitable or if the requirement of having OS support must be dropped.

| Name                | Instruction width | Privileged specification | User<br>specifica-<br>tion | ISA                 | Implementation language | OS support |

|---------------------|-------------------|--------------------------|----------------------------|---------------------|-------------------------|------------|

| CVA6                | 64                | 1.11                     | 2.3                        | RV64GC              | SystemVerilog           | Linux      |

| CV32E40P            | 32                | 1.11                     | 2.1                        | RV32IMC             | SystemVerilog           | -          |

| Ibex                | 32                | 1.11                     | 2.1                        | RV32I[M]C/RV32E[M]C | SystemVerilog           | -          |

| Kronos              | 32                | 1.11                     | 2.1                        | RV32I               | SystemVerilog           | -          |

| Roa Logic<br>RV12   | 32/64             | 1.10                     | 2.2                        | RV32I/RV64I         | SystemVerilog           | -          |

| RSD                 | 32                | unknown                  | unknown                    | RV32IM              | SystemVerilog           | Zephyr     |

| SCR1                | 32                | 1.10                     | 2.2                        | RV32I[MC]/RV32E[MC] | SystemVerilog           | Zephyr     |

| SweRV EH1           | 32                | 1.11                     | 2.1                        | RV32IMC             | SystemVerilog           | -          |

| SweRV EH2           | 32                | 1.11                     | 2.1                        | RV32IMAC            | SystemVerilog           | -          |

| SweRV EL2           | 32                | 1.11                     | 2.1                        | RV32IMC             | SystemVerilog           | -          |

| Taiga               | 32                | unknown                  | unknown                    | RV32IMA             | SystemVerilog           | -          |

| biRISC-V            | 32                | 1.11                     | 2.1                        | RV32I[M]            | Verilog                 | Linux      |

| DarkRISCV           | 32                | -                        | incomplete                 | RV32I               | Verilog                 | -          |

| Hummingbird<br>E200 | 32                | 1.10                     | 2.2                        | RV32IMAC            | Verilog                 | -          |

| mRISC-V             | 32                | unknown                  | unknown                    | RV32IM              | Verilog                 | -          |

| PicoRV32            | 32                | -                        | unknown                    | RV32I[MC]/RV32E[MC] | Verilog                 | -          |

| SERV                | 32                | incomplete               | unknown                    | RV32I               | Verilog                 | Zephyr     |

| SSRV                | 32                | 1.10                     | unknown                    | RV32IMC             | Verilog                 | -          |

| Maestro             | 32                | -                        | incomplete                 | RV32I               | VHDL                    | -          |

| ORCA                | 32                | unknown                  | unknown                    | RV32IM              | VHDL                    | -          |

| ReonV               | 32                | unknown                  | unknown                    | RV32I               | VHDL                    | -          |

| RV01                | 32                | 1.7                      | 2.0                        | RV32IM              | VHDL                    | -          |

| RPU                 | 32                | -                        | unknown                    | RV32I               | VHDL                    | Zephyr     |

Table 2.1: Overview of RISC-V cores that have a permissive license and use a classical HDL.

The CVA6 processor [2] is a 64-bit, 6-stage in-order single-core processor with a focus on efficiency. It was developed as part of the Parallel Ultra Low Power (PULP) platform, a collaboration between ETH Zürich and the University of Bologna to research ultra-low-power architectures. The core was originally named Ariane, but it was donated to the OpenHW Group and renamed to CVA6 in June 2020. The core has a wide community and extensive documentation. It is actively maintained at the time of writing. ASIC synthesis is also supported, which was demonstrated by creating a 1.7 GHz implementation in 22 nm technology. The modular and well-structured design make it suitable for the addition of custom extensions. As such, the requirements of the previous section are met, and the CVA6 processor is selected for the ISA extension of this project.

The CVA6 is not just a core, but a SoC platform containing the core. This means other SoC platforms do not need to be considered, and no SoC has to be developed manually around the core. It also means that the second milestone of Section 1.3 is simplified to loading the CVA6 design onto the FPGA and verifying that the OS can boot.

It should be noted that, during the course of the MSc. project described in this thesis, a 32-bit version of the CVA6 core was developed, which can be implemented by selecting the appropriate configuration options in the design files. However, because the development of the proposed implementation had already started before that time, no attempt was made to transform the design into a 32-bit version. Although doing so would be a trivial task, it would not substantially change the results of this project.

#### 2.6 Related work

In order to justify the MOLEN paradigm as the architecture to implement, other reconfigurable architectures must first be reviewed. Though the original MOLEN dissertation [12] also reviews related work, almost two decades have passed since then. Therefore, a new literature study must be performed to look into alternative reconfigurable designs. In this section, an overview of existing architectures is first presented, after which they are compared to each other and to the MOLEN paradigm.

#### 2.6.1 Overview of existing architectures

The Fully Pipelined Composable Architecture (FPCA) [19] is a loosely coupled CGRA, meaning it acts as a separate co-processor instead of being integrated into the processor pipeline. It consists of an array of PE clusters, each containing a set of PEs. It aims to parallelize all operations from the user application, or even dynamically duplicate single operations if resources remain unused.

The Configurable Compute Accelerator (CCA) [20] is a CGRA that is designed to efficiently implement many common dataflow subgraphs. Such a subgraph is essentially a slow execution path in the application code. By collapsing these subgraphs into new instructions that can be executed on the CCA, the execution bottlenecks can be removed. This process can happen dynamically at run time, or statically at compile time. The CCA consists of a matrix of two types of functional units. One type performs

addition, subtraction and logical operations, whereas the other type can only perform the logical operations.

Blocks [21] is a novel CGRA design that separates the data and control paths. There is a focus on energy efficiency, including the reconfiguration energy overhead. Blocks primarily performs well in applications where data-level parallelism is present. Its CGRA consists of 6 different kinds of functional units, connected by a data network for direct data transfers. The control network allows the instruction fetcher and decoder units to be arbitrarily connected to one or more functional units, allowing Single Instruction, Multiple Data (SIMD) processors to be constructed. As such, VLIW-like instructions can be created and used.

The **Dynamically Specializing Execution Resources (DySER)** [22] architecture is a CGRA focusing on both data-level parallelism and functionality specialization. Functionality specialization means that custom hardware is used to optimize the application-level performance (in the same way as the CCA architecture). The CGRA consists of 6 functional units, that perform integer and floating point operations. DySER was compared to a GPU and SIMD implementation, and outperformed both of them while significantly reducing the energy consumption.

The Advanced Space-Time Reconfigurable Architecture (ASTRA) [23] is an FPGA based design that uses CLBs as (fine-grained) building blocks, instead of the coarse-grained blocks of the previous architectures. The unique feature of this architecture is that these ASTRA cells can be configured in either spatial or temporal mode. In temporal mode, the least amount of cells is used, at the cost of a higher latency. In spatial mode, the amount of cells is maximized such that the latency is minimized. Different applications can use the different modes at the same time.

The **Chameleon** [24] architecture is a CGRA that consists of multiple PE arrays. The configuration of the arrays is specified using 32-bit words, that can be translated from high-level instructions. The Chameleon architecture is tailored for MapReduce (big data) applications, in which it is able to achieve significant energy savings.

SmartCell [25] is a power efficient CGRA that is specialized towards data streaming applications. It consists of blocks containing four PEs and a switch box. The cells are connected by a three-level interconnection network. A Serial Peripheral Interface (SPI) is used to reconfigure the cells, enabling low reconfiguration times. On a set of 7 benchmarks, SmartCell was able to use 75% less power than an FPGA implementation.

The Polymorphic Pipeline Array (PPA) [26] is a CGRA that focuses on mobile multimedia applications. It consists of an array of simple cores that are coupled using a mesh-style interconnect. Each core can execute its own instruction stream and consists of four PEs. However, multiple cores can be combined into a larger (logical) core, such that fine-grained parallelism can be accommodated more easily. In that case, the logical cores can be used to create pipelines, such that multiple consecutive operations can be performed without additional communication overhead in between. The complexity of this design is high, as schedules need to be generated for the execution, and dynamic hardware allocation is applied.

Heterogeneous Arrays for Reconfigurable and Transparent Multicore Processing (HARTMP) [27] is an architecture consisting of Dynamic Adaptive Processors (DAPs). Each DAP is a single-threaded processor, using a reconfigurable datapath.

In this way, thread-level parallelism is available as result of the total amount of DAPs. Instruction-Level Parallelism (ILP) is achieved by means of the reconfigurable datapaths. Larger cores allow for a higher ILP. Despite having different core sizes, a homogeneous ISA is used, hiding the heterogeneity of the cores from the programmers.

The Dual-Track Coarse-Grained Reconfigurable Architecture (DT-CGRA) [28] is a CGRA design tailored for stream processing in the machine learning domain. It consists of a set of Stream Buffer Units (SBUs) and a Computing Array (CA). The SBUs cache the input and output data, as well as the intermediate results. The CA forms the actual CGRA and consists of different types of reconfigurable cells, some of which are specialized to calculate interpolations and power functions. The rows of cells are connected with a multi-channel data bus, which in turn are connected to the SBUs using a crossbar.

### 2.6.2 Comparison

From the presented set of architectures, two observations stand out. The first one is that coarse-grained architectures seem to be the preferred choice in recent designs. This is because they allow for a lower power consumption and higher performance than finegrained systems. Furthermore, the reconfiguration times can be significantly lower [24]. However, they also limit the flexibility of the system significantly: most designs seem to be focused on optimizing inner loops of user programs, typically present in computations on large datasets. The functional units can be seen as small general-purpose processors. In some cases, they approach regular processor cores, or can be used to construct SIMD cores [21]. Because of this, they mostly improve the performance by exploiting parallelism. However, recent CPUs already consist of multiple cores and (hardware) threads. Often, user applications tend to be sequential in nature, and current multi-core processing remains under-utilized (within single applications). In this situation, adding more parallelism will not be useful. The MOLEN paradigm resolves this issue by not necessarily adding parallelism, but by adding support for any kind of custom operation that can be synthesized to the reconfigurable fabric. This ensures a greatly increased flexibility, without compromising the ability to exploit parallelism. As many parallel units can be implemented in the reconfigurable fabric as allowed by the size of the fabric.

The other observation is that most designs are tailored for specific applications. This might improve the performance and energy efficiency for their respective applications, but reduces their overall usability. Especially when used with a general-purpose processor can this observation be disappointing. By implementing the MOLEN paradigm on a RISC-V processor, the design of this thesis is applicable to a broad range of applications. Fine-grained reconfigurability and the modular design of the RISC-V ISA enable this.

The clear disadvantages of the proposed design are the expected reconfiguration overhead and energy efficiency penalty of using a fine-grained reconfigurable fabric. However, recent FPGAs contain an increasing amount of coarse-grained blocks (such as DSPs). Therefore, these problems have already diminished to a certain degree and are expected to continue to do so in the future.

A final remark on the disadvantages further supports the proposed design as viable architecture: MOLEN does not enforce using fine-grain reconfigurability. All that is

defined by the machine organization is that a CCU is available. By making that CCU coarse-grain reconfigurable, the reconfiguration overhead diminishes and the energy efficiency penalty disappears. At the same time, the power of the MOLEN paradigm is preserved, depending on the design of the PEs. The currently proposed, fine-grained design, is an initial working version of the design, that can be expanded in the future to a coarse-grained design. Alternatively, a more efficient fine-grain fabric [29] can be used to increase the energy efficiency and performance.

#### 2.7 Conclusions

In this chapter, relevant background information was provided on reconfigurable architectures, the MOLEN processor, and the RISC-V architecture.

Two main application domains for reconfigurable architectures were first identified: accelerators for **high-performance computing** and specialized or time-critical tasks in **embedded systems**. Reconfigurable architectures can be distinguished in terms of granularity. Fine-grained systems use the smallest building blocks and can be fully configured. Coarse-grained systems are less flexible and use larger building blocks, allowing for increased clock speeds and a greater energy efficiency.

After establishing a basic understanding of reconfigurable architectures, the MOLEN polymorphic processor could be introduced. In this paradigm, a one-time ISA extension introduces reconfigurable microcode ( $\rho\mu$ -code), which is used to perform reconfigurations and execute custom operations on the reconfigured hardware. This extension mainly consists of a set instruction that loads a reconfigurable design, and an execute instruction that performs the custom operations. The von Neumann architecture is extended with a reconfigurable processor that performs the custom instructions, an arbiter that passes the instructions to either the core processor or reconfigurable processor, and a number of exchange registers that are used for storing the input and output operands of the custom instructions.

After introducing the MOLEN paradigm, the RISC-V architecture was introduced. This open-source ISA offers multiple base instruction sets and extension instruction sets, thereby making it suitable for a wide range of applications. Support for custom instructions is also included, enabling its use for this project.

Having introduced the RISC-V architecture and the MOLEN paradigm, existing RISC-V processor implementations were compared, such that the most suitable one could be selected for extension with the MOLEN paradigm. The CVA6 core was chosen for this purpose, because it supports the Linux OS, is actively maintained and has a community with extensive documentation.

Before pursuing the actual implementation of the MOLEN paradigm on the RISC-V architecture, related work had to be examined, in order to substantiate the potential benefits of a novel implementation. Several existing reconfigurable implementations were compared. It was observed that most existing architectures are coarse-grained and application-specific. The proposed design improves upon this by allowing a wide range of applications, while not imposing a coarse-grained or fine-grained design.

Design

Now that the MOLEN paradigm and RISC-V architecture have been introduced in Chapter 2, this chapter focuses on adapting the MOLEN design to the RISC-V architecture such that it can be implemented in Chapter 4. Specifically, the design is discussed from the perspective of the RISC-V ISA and the reconfigurable microcode ( $\rho\mu$ -code) of the MOLEN paradigm.

In Section 3.1, the different instruction formats of the RISC-V ISA are introduced. The available opcode space is investigated in Section 3.2. Following that, both the reconfiguration and execution microcode of the MOLEN design are adapted to the RISC-V architecture in Section 3.3. The initial adaptation of the microcode is then shaped into an actual proposed ISA extension in Section 3.4, after which this chapter is concluded in Section 3.5.

### 3.1 RISC-V instruction formats

| 31             | 27     | 26   | 25       | 24 | 20     | 19 | 15  | 14  | 12  | 11   | 7       | 6    | 0      |         |

|----------------|--------|------|----------|----|--------|----|-----|-----|-----|------|---------|------|--------|---------|

| funct7         |        |      | r        | s2 | rs     | s1 | fun | ct3 | 1   | rd   | ope     | code | R-type |         |

| rs             | s3     | fun  | ct2      | r  | s2     | rs | s1  | fun | ct3 | 1    | rd      | opo  | code   | R4-type |

|                |        | imm  | [11:0    | )] |        | rs | s1  | fun | ct3 | 1    | rd      | ope  | code   | I-type  |

| j              | imm[1  | 1:5] |          | r  | s2     | rs | s1  | fun | ct3 | imn  | n[4:0]  | ope  | code   | S-type  |

| in             | nm[12] | 10:5 | <u>[</u> | r  | s2     | rs | s1  | fun | ct3 | imm[ | 4:1 11] | ope  | code   | B-type  |

| imm[31:12]     |        |      |          |    |        |    | 1   | rd  | opo | code | U-type  |      |        |         |

| imm[20 10:1 11 |        |      |          |    | 19:12] |    |     |     | 1   | rd   | opo     | code | J-type |         |

Table 3.1: 32-bit RISC-V instruction formats. Adapted from the RISC-V ISA specification[3].

Before the MOLEN ISA extension can be designed in the following sections, we first need to examine the main instruction types of the RISC-V instruction set, as depicted in Table 3.1. Suitable instruction formats for the custom instructions can then be identified in the following sections. All instruction types apart from the R4-type are defined by the RV32I base instruction set. The R4-type is defined by the F/D/Q standard extensions, which specify the single-/double-/quad-precision floating point instructions, respectively.

Before the different types can be compared, the following fields are first distinguished in the instruction formats:

- opcode: The field that (fully or partially) specifies the operation to perform.

- rd: The destination register that the result of the operation should be written to.

- rs1, rs2, rs3: The source registers that supply the operands that the operation is performed on.

- funct7, funct3, funct2: if present, these function values are combined with the opcode to fully specify the operation to perform.

- *imm*: An immediate value that is passed into the instruction itself instead of loaded from a register.

Now, the different instruction types can be explained:

- R-type (R4-type): This type is a register-register instruction. It takes two (R-type) or three (R4-type) source registers to perform the operation on and the destination register to put the result into. An example of an R-type instruction is the RV32I ADD instruction, which adds the values in rs1 and rs2 and puts the result in rd.

- I-type: A register-immediate instruction that takes a 12-bit immediate value, a single source register and the destination register. An example of an I-type instruction is the RV32I ADDI instruction, which adds the sign-extended immediate value *imm* to the value in rs1 and puts the result in rd. The I-type is also used for loads, such as the RV32I LW instruction that loads the value at memory address rs1 + imm (with imm being sign-extended) and puts the result in rd.

- S-type: A store-type instruction that takes a 12-bit immediate value and two source registers. Note that the immediate value is split up across two portions. The reason for that is to allow all other fields to be in the same position as for the other instructions that have those fields. This simplifies the hardware design by allowing for as much overlap in the logic as possible.

- An example of an S-type instruction is the RV32I SW instruction, which stores the value in rs2 at memory address rs1 + imm (with imm being sign-extended).

- B-type: A branch-type instruction that is a variation of the S-type instruction. The difference with the S-type is the interpretation of the immediate value. Instead of it being 12 bits like for the S-type, the immediate value is 13 bits, but the lowest bit is an implicit 0. In other words, it is a 12 bit immediate that is left-shifted by one bit. As depicted in Table 3.1, the immediate bits are ordered differently than for the S-type. This maximizes the overlap of the bits with those of the immediate value of the S-type, allowing as much re-use of the same logic as possible. The exception to that is that the bit at position 31 is not bit 11 of the immediate (like for the S-type), but bit 12 instead. This is done because bit 12 is the most significant bit of the immediate, and as such, no changes to the sign-logic are needed compared to that of the S-type.

An example of a B-type instruction is the RV32I BEQ instruction, which adds the sign-extended immediate value imm to the program counter (Program Counter (PC)) if the values in rs1 and rs2 are equal. This also reveals why the lowest bit of the immediate value is always 0: we can only jump in multiples of 2 bytes to

end up at a potentially valid instruction address. Normal instructions are 32 bits, or 4 bytes, but the compressed instructions that are introduced in Section 3.1 are 16 bits, or 2 bytes.

- U-type: This type is an upper immediate instruction. It takes a 20-bit (upper) immediate value and the destination register rd. The most basic RV32I example is the LUI instruction, which loads the immediate value into bits 31-12 of rd and fills the lowest 12 bits of rd with zeroes. In the case of the RV64I instruction set, it is sign-extended to 64 bits.

- **J-type**: A jump-type instruction that is a variation of the U-type instruction. Like for the B-type, the difference can be found in the interpretation of the immediate value: PC-relative jumps can only (viably) target an offset that is a multiple of 2 bytes. Therefore, the immediate value is interpreted as 21-bit value instead of a 20 bit value, with the least significant bit being an implicit 0. Likewise, the bit ordering of the immediate value is chosen to match that of the U-type where possible, while placing the sign bit at the most significant position.

The only example of the J-type instruction is the RV32I JAL instruction, which adds the sign-extended immediate value imm to the PC, and loads the address of the instruction after the jump into rd.

# 3.2 RISC-V opcode space

| inst[6:5] | inst[4:2] |          |             |          |        |          |                |          |  |  |

|-----------|-----------|----------|-------------|----------|--------|----------|----------------|----------|--|--|

|           | 000       | 001      | 010         | 011      | 100    | 101      | 110            | 111      |  |  |

| 00        | LOAD      | LOAD-FP  | custom- $0$ | MISC-MEM | OP-IMM | AUIPC    | OP-IMM-32      |          |  |  |

| 01        | STORE     | STORE-FP | custom-1    | AMO      | OP     | LUI      | OP-32          | reserved |  |  |

| 10        | MADD      | MSUB     | NMSUB       | NMADD    | OP-FP  | reserved | custom-2/rv128 | > 32b    |  |  |

| 11        | BRANCH    | JALR     | reserved    | JAL      | SYSTEM | reserved | custom-3/rv128 |          |  |  |

Table 3.2: RV32/64G opcode map, inst[1:0]=11. Adapted from Table 24.1 of the RISC-V ISA specification[3].

After highlighting the different instruction types in the previous section, we first need to investigate the available opcode space for our one-time ISA extension, before proceeding with the design in the following sections. Table 3.2 highlights the RISC-V instructions and instruction groups for the different opcodes. An instruction group refers to a set of operations for which the opcode alone does not fully specify the operation (instead being complemented by one or more *funct* fields).

First, it should be noted that the lowest two bits of instruction (and opcode) are both 1 in this table. Any other variation of the lowest two bits is reserved for the compressed 16-bit instructions that are specified in the "C" standard extension [14]. Since the opcode space defined in that extension is fully exhausted, no custom ISA extension can be added there. As such, only the regular opcode space is investigated.

Inspecting Table 3.2 reveals the *custom-0*, *custom-1*, *custom-2* and *custom-3* opcode spaces. These spaces are reserved for custom extensions and are guaranteed to be avoided

by future standard extensions [14]. The exception to that are the future RV128 standard extensions that will occupy the *custom-2* and *custom-3* opcode spaces. It is also possible to identify instructions or instruction groups that are not used in the chosen CPU design, and use those for the custom extension. However, doing so would limit the possibilities for implementing the proposed extension in other micro-architectures. To allow for the most future possibilities, the *custom-0* or *custom-1* opcode space should be chosen. Since no further advantages in favor of either one could be identified, the *custom-0* opcode space is chosen for the proposed design. Therefore, the opcode for the one-time custom extension will be 0001011.

## 3.3 Microcode design

Following the overview of the RISC-V instruction formats in Section 3.1 and the exploration of the available opcode space in Section 3.2, we can now design the MOLEN reconfigurable microcode ( $\rho\mu$ -code), as introduced in Section 2.2. This microcode is used for both the act of reconfiguration, as well as the execution of operations on the reconfigured hardware. In order to adapt this microcode to the RISC-V processor, we need to take into account the hardware limitations of the chosen FPGA. Because of their different nature, the reconfiguration microcode and execution microcode are considered separately.

### 3.3.1 Reconfiguration microcode

As mentioned in Section 2.2, the original MOLEN design [12] proposes a straightforward method of generating the reconfiguration microcode: the bitstream of the reconfigurable partition is split into equal blocks, to which the *set* opcode is then appended to create the micro-instructions that perform the reconfiguration. Such micro-instructions are easily generated from the bitstream.

An underlying assumption in the original work is that (partial) reconfigurable designs can be placed into different areas of the reconfigurable fabric as desired. Multiple reconfigurable designs of various sizes can then be loaded and connected to each other using microcode. However, the way that partial reconfiguration works on the Xilinx FPGA family, is that a partial bitstream is loaded into a matching reconfigurable partition, which is a predefined physical area on the FPGA. It is important to note that a partial bitstream can only be loaded into the reconfigurable partition for which it was generated, and not into any other reconfigurable partition. Therefore, in a design with multiple reconfigurable partitions, a separate partial bitstream has to be generated for each partition that the reconfigurable module is used in. Having the exact same physical dimensions for the reconfigurable partitions does not change this fact. Work has been done to change this and allow for sharing of bitstreams between partitions [30], but such tools are not publicly available yet.

This limitation on the bitstreams and reconfigurable partitions has major implications on the implementation of the MOLEN design: having smaller reconfigurable building blocks (such as full adders) that can be joined into a larger design would require many small reconfigurable partitions. For each of those partitions, the bitstream of each small design would need to be separately generated. At the same time, having multiple small partitions makes it impossible to design larger, more complex building blocks, because they would not fit into a single (small) partition. Furthermore, it was already decided in Chapter 1 to use a single reconfigurable partition for the current design.

An alternative method for the reconfiguration microcode is also mentioned in the original MOLEN design [12]: instead of directly loading the bitstreams, a higher level microcode could be achieved by comparing synthesis results or partial bitstreams and identifying the parts responsible for the reconfiguration of specific areas of the reconfigurable partition. Those areas could then be individually reconfigured on a very small scale. Though theoretically possible, this requires reverse-engineering the bitstreams, which are specific to each separate FPGA family, instead of being generalizable. Because of the complexity of such an endeavor, this approach is not considered feasible for the current work.

A final method for the reconfiguration microcode is to take a more coarse-grain approach: instead of loading a bitstream into a reconfigurable partition, a static set of PEs could take the place of the reconfigurable fabric. Those PEs could then be dynamically configured and chained to achieve the desired functionality. This method circumvents the mentioned problems with the partial bitstreams and reconfigurable partitions. However, it poses a limit on the possible functionalities that can be implemented. Although this method could be viable for implementing specific functionality types (such as matrix multiplication), it is less suitable for the implementation of arbitrary functions. The careful PE design that would be needed to ensure a wider range of functions is outside the scope of this work.

Following the previous observations, it is decided to apply the original proposal of wrapping partial bitstreams into micro-instructions for this project. Because such reconfiguration microcode is merely a shell to transport the partial bitstream, it can even be simplified further. The *set* instruction would then point directly to the address of the partial bitstream, instead of the address of the reconfiguration microcode. This will be further expanded on in Section 3.4.

#### 3.3.2 Execution microcode

After designing the reconfiguration microcode in the previous section, we can now consider the execution microcode, which is also affected by the previously mentioned limitations. Having a single reconfigurable partition, means that a single bitstream should contain all functions that can be used simultaneously. In other words, the reconfiguration flow that is envisioned in [12], where the bitstreams of the required building blocks are reconfigured separately, is not feasible when only a single reconfigurable partition is used.

By extension, this means that the execution microcode, which was envisioned to connect the building blocks to each other and to their inputs and outputs, is also not viable in the current design. Instead, having a single reconfigurable partition implies that all of the required functions should be fully implemented and connected within the reconfigurable design itself. This also means there is no need for the execution microcode to connect the individual components, inputs and outputs. Instead, its only function is

to perform the required operations when needed, like regular instructions.

When deciding how to design such microcode, the RISC-V architecture has to be taken into account. Specifically, the dedicated opcode space that is available for custom instructions as introduced in Section 3.2, is very suitable for the design of the (modified) microcode. Instead of having a complete microprogram that needs to be loaded from a control store or from memory, a **nested microcode** can be designed using the available opcode space.