# Hierarchical EMC Design for Inverters in Motor Drive Systems

# Hierarchical EMC Design for Inverters in Motor Drive Systems

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. dr. ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 7 december 2009 om 15.00 uur door

Dongsheng ZHAO

elektrotechnisch ingenieur geboren te Yining City, China. Dit proefschrift is goedgekeurd door de promotoren:

Prof. dr. J. A. Ferreira

en

Prof. dr. ir. F.B.J. Leferink

#### Samenstelling promotiecommissie:

Rector Magnificus Voorzitter, Technische Universiteit Delft Prof. dr. J.A. Ferreira Technische Universiteit Delft, promotor

Prof. dr. ir. F.B.J. Leferink Universiteit Twente, promotor Prof. dr. A.G. Tijhuis Technische Universiteit Eindhoven

Prof. dr. A. Consoli University of Catania

Prof. ir. L. van der Sluis Technische Universiteit Delft Prof. dr. T.D. Visser Technische Universiteit Delft

Prof. dr. M. Zeman Technische Universiteit Delft, reservelid

This research was supported financially by SenterNovem in the framework of the "Innovatiegerichte Onderzoeks Programma ElektroMagnetische Vermogens Techniek" (IOP-EMVT).

#### Copyright © 2009 by D. Zhao

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without the prior permission of the author.

ISBN 978-90-9024883-7

Author email: dongsheng.zhao@gmail.com

# **Abbreviations**

AC Alternating Current Av Average detector

BJT Bipolar Junction Transistor

CM Common Mode

CMC Common Mode Choke CSR Current Source Rectifier

DC Direct Current

DM Differential Mode

EDM Electrical Discharge Machining

EMC ElectroMagnetic Compatibility

EMI ElectroMagnetic Interference

EUT Equipment Under Test

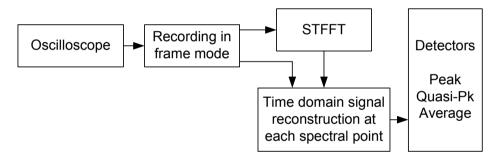

FEMIT Fast Emission Measurement In Time domain

FFT Fast Fourier Transform

IFBW Intermediate Frequency BandWidth IGBT Insulated Gate Bipolar Transistor

IT Information Technology

LISN Line Impedance Stabilization Network

MM Mixed Mode

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PCB Printed Circuit Board PFC Power Factor Corrector

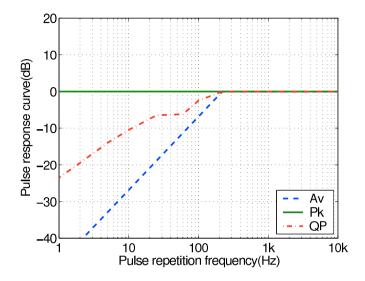

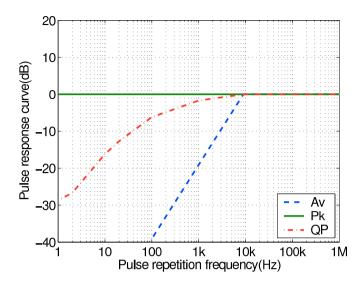

Pk Peak detector

PWM Pulse Width Modulation QP Quasi-Peak detector

SPWM Sinusoidal Pulse Width Modulation STFFT Short Time Fast Fourier Transform SVPWM Space Vector Pulse Width Modulation

#### ii ABBREVIATIONS

| TDEMI | Time Domain EMI measurement    |

|-------|--------------------------------|

| TDR   | Time Domain Reflectometry      |

| TRIAC | TRIode for Alternating Current |

| UPS   | Uninterruptible Power Supply   |

|       |                                |

VSD Variable Speed Drive

VSI Voltage Source Inverter

VSR Voltage Source Rectifier

ZCS Zero Current Switching

ZVS Zero Voltage Switching

# **Acknowledgements**

Owning a doctoral degree is a dream of my childhood, but the road has been rather long. It has however been my good fortune to encounter many people who have given me much of their professional and personal help. When writing this acknowledgment, I realized that many individuals have lent me a hand. I cannot even recall the names of some of them but without them I could not have made all these things happen. I would like to convey my sincerest gratitude and appreciation to them.

I would first of all like to thank my promotor, Professor Braham Ferreira who gave me the opportunity to do this research at TU Delft. He supported and encouraged me all the time, not only in scientific matters, but also in coping with my mental and work conditions. Professor Frank Leferink, was my primary supervisor in my master study, and my promotor in my PhD study. His experience, and unique knowledge and enthusiasm in the EMC field have always been my support.

Dr. Henk Polinder, was my daily supervisor in the first two years. He gave me lectures to fill my gaps in the knowledge of machine and power electronics and support me in the anxiety during the beginning stage of my research. He also helped me to find a suitable apartment for my family which really saved me at that time.

I would like to thank my doctoral examination committee for studying the draft of the thesis and giving their valuable comments.

I would like to acknowledge the staff members in the EPP research group, Rob Schoevaars, Bart Roodenburg, Sjoerd de Haan and Paul Bauer for their help in the laboratory and their lectures.

I would like to thank the people who sit on the IOP-EMVT coaching committee. We had conferences twice a year and it was valuable to learn from your comments and suggestions. Thank you, Jasper Goedbloed and Lex van Deursen.

Thank you to my ex-colleagues in NEDAP, who helped me to find the chance

to do the PhD research at TU Delft and sent me to the interview. These include Randolph Browne, Ton Scharenborg, Richard Hogenkamp, Gerben Hoeksma, Gerhard van Eerden and many people. I do not remember all their names but thank you!

I would also like to thank Anne Roc'h, the fellow researcher with whom I have spent three years. We had many times of discussion, went together on industry investigations several times and co-operated in writing several papers.

Also, I want to thank many authors and specialists who I had communicated with. Special thanks go to Jin Meng, David Gonzalez, Christoph Keller, Peter van Duijsen and Norbert Hanigovszki. Furthermore, to the partners in industry, Evert Raaijen from Exendis in Ede, Jan-Kees van der Ven from Imtech Marine in Rotterdam and Jan Zinger from Eekels Elektrotechniek in Hoogezand for their hospitality during my visits to their companies.

It has been a great pleasure to work with so many talented colleagues and excolleagues in the EPP research group. I would especially like to thank Yi Zhou, Xun Gong, Deok-Je Bang, Zhihui Yuan, Yi Wang, Ghanshyam Shrestha, Marcelo Gutierrez-Alcaraz, Ivan Josifovic, Aleksandar Borisavljevic, Dalibor Cvoric, Johan Wolmarans, Hung Vu Xuan, Sam Ani, Frank van der Pijl, Johan Morren, Evandro Meurer, Milan Hajder, Jenela Popovic, Mark Gerber, Eric de Jong and Martin Pavlovsky. We are roommates, co-workers and classmates that I have worked, talked and lunched with over the years. I treasure the memories. I would like to thank Leo Breebaart. The LATEX typesetting of this thesis is based on his public code. I would like to thank Ralf, Neil and Jan for their help in grammar check. A special word of gratitude goes to Tjerk Steenstra. Thank you for translating my proposition and summary into Dutch.

Moving towards more personal acknowledgements, I would like to thank many friends, especially Ankie, Erdogan, Bo Cui, Dazhao Xu, Ziye Han, Erwa Ke, Qian Xu and Chen Liu. Last but not the least; I would like to thank Oma, Jan, Edith, Jianguang, my parents and my brother, for their monumental, unwavering support and encouragement on all fronts. Finally, and most importantly, I would like to thank my wife, Ran, for her love, understanding, support and sacrifice during all the stages of my PhD studies. Thanks to my lovely sons, Chengji and Xingqi, who bring me the pride and happiness of being a father.

Dongsheng Zhao

# **Contents**

| Αľ | obrevi       | ations                                                | i   |  |  |

|----|--------------|-------------------------------------------------------|-----|--|--|

| Ac | know         | rledgements                                           | iii |  |  |

| 1  | Introduction |                                                       |     |  |  |

|    | 1.1          | The growth of power electronic converters             | 1   |  |  |

|    | 1.2          | The EMC requirements                                  | 2   |  |  |

|    | 1.3          | Problem description and research object               | 3   |  |  |

|    | 1.4          | Research method                                       | 4   |  |  |

|    | 1.5          | Thesis layout                                         | 5   |  |  |

| 2  | Con          | figurations of AC-AC converters                       | 7   |  |  |

|    | 2.1          | Introduction                                          | 7   |  |  |

|    | 2.2          | Topologies of AC-AC converters                        | 8   |  |  |

|    |              | 2.2.1 Single-stage AC-AC converter topologies         | 9   |  |  |

|    |              | 2.2.2 Two-stage AC-AC converter topologies            | 11  |  |  |

|    |              | 2.2.3 Three-stage AC-AC converter topologies          | 11  |  |  |

|    |              | 2.2.4 Four-stage AC-AC converter topologies           | 12  |  |  |

|    |              | 2.2.5 Five-stage AC-AC converter topologies           | 13  |  |  |

|    |              | 2.2.6 Selected topologies for case study              | 13  |  |  |

|    | 2.3          | The capacitive coupling mechanism                     | 14  |  |  |

|    | 2.4          | The inductive coupling mechanism                      | 18  |  |  |

|    | 2.5          | Rectifier configurations                              | 20  |  |  |

|    | 2.6          | Grounding configurations                              | 24  |  |  |

|    |              | 2.6.1 Possible grounding methods                      | 24  |  |  |

|    |              | 2.6.2 The impact on the noise propagation path        | 25  |  |  |

|    |              | 2.6.3 The impact on the generation of bearing current | 27  |  |  |

#### vi CONTENTS

|   | 2.7   | DC-bus configurations                                                     |

|---|-------|---------------------------------------------------------------------------|

|   | 2.8   | Inverter configurations                                                   |

|   | 2.9   | EMC modeling                                                              |

|   | 2.10  | Summary                                                                   |

| 3 | Hiera | archical EMC design procedures 33                                         |

|   | 3.1   | Introduction                                                              |

|   | 3.2   | Present EMI modeling methods                                              |

|   |       | 3.2.1 Time domain method                                                  |

|   |       | 3.2.2 Frequency domain method                                             |

|   | 2.2   | **                                                                        |

|   | 3.3   | Approach to a hierarchical EMC design procedure                           |

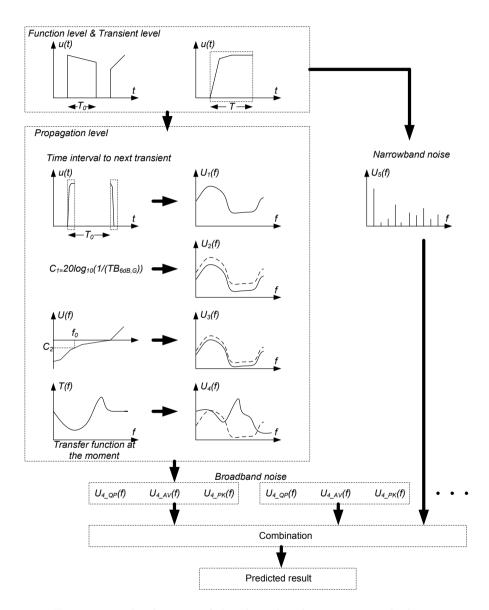

|   | 3.4   | Functional level                                                          |

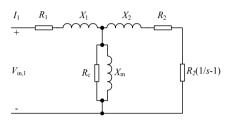

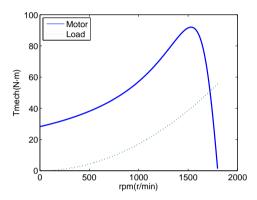

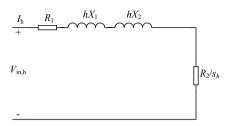

|   |       | 3.4.2 Induction motor operating point determination                       |

|   |       | 3.4.3 PWM output current spectrum                                         |

|   |       | 3.4.4 Switching events                                                    |

|   | 3.5   | Transient level                                                           |

|   |       | 3.5.1 Basic noise cell model                                              |

|   |       | 3.5.2 Slope of the transients                                             |

|   | 0.0   | 3.5.3 The impact of a noise source                                        |

|   | 3.6   | Propagation level                                                         |

|   | 3.7   | Summary                                                                   |

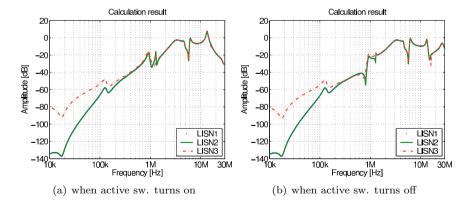

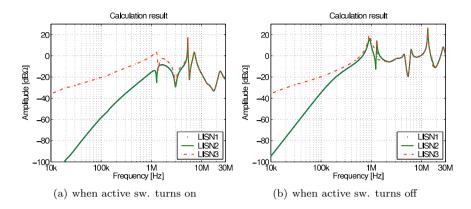

| 4 |       | pression along the propagation path 63                                    |

|   | 4.1   | Introduction                                                              |

|   | 4.2   | Decoupling the propagation path and the noise source 64                   |

|   | 4.3   | Analysis of the propagation path 60                                       |

|   | 4.4   | The observation in the time domain                                        |

|   | 4.5   | Passive filter for noise suppression and the influence of installation 76 |

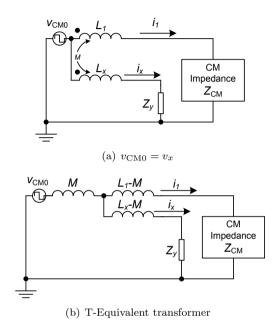

|   |       | 4.5.1 CM equivalent model                                                 |

|   | 4.6   | DC-bus filter                                                             |

|   | 4.0   |                                                                           |

| _ |       | v                                                                         |

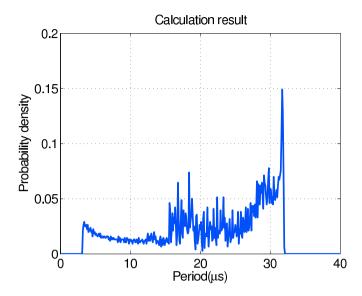

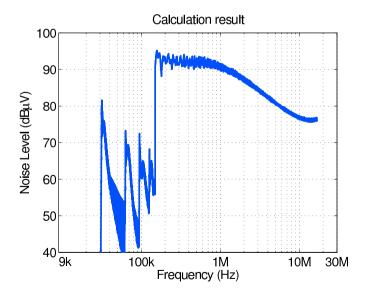

| 5 |       | e source analysis 91                                                      |

|   | 5.1   | Noise source characteristics                                              |

|   |       | 5.1.2 Aperiodic noise source                                              |

|   | 5.2   | An improved method to analyze noise sources                               |

|   | 5.3   | Compliance measurement correction 94                                      |

|   |       |                                                                           |

|     |         | CONTENTS                                                                                                                         | vii      |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------|----------|

|     |         | 5.3.1 Detector correction                                                                                                        | 95<br>97 |

|     | 5.4     | Noise source of a resonant converter $\dots \dots \dots \dots$ .                                                                 | 98       |

|     | 5.5     | Experimental verification                                                                                                        | 105      |

|     | 5.6     | Summary                                                                                                                          | 108      |

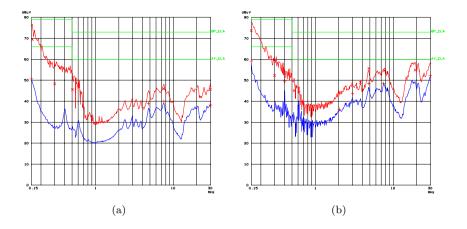

| 6   | Sup     | pression in the noise source                                                                                                     | 109      |

|     | 6.1     | $Introduction \dots \dots$ | 109      |

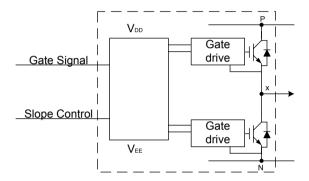

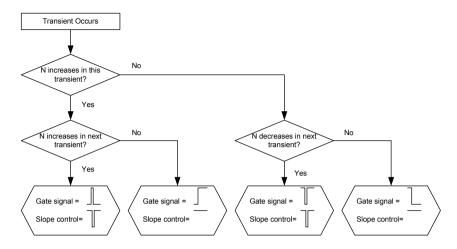

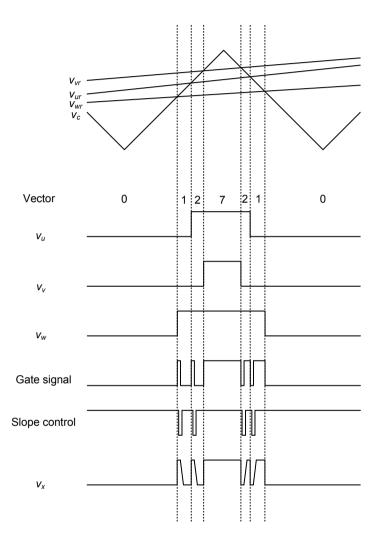

|     | 6.2     | Operation principle                                                                                                              | 112      |

|     | 6.3     | The determination of the values of magnetic components                                                                           | 114      |

|     |         | 6.3.1 Ideal coupling                                                                                                             |          |

|     |         | 6.3.2 Nonideal coupling                                                                                                          |          |

|     | 6.4     | The control method                                                                                                               |          |

|     | 6.5     | The method to generate variable voltage transient slopes                                                                         |          |

|     | 6.6     | Summary                                                                                                                          | 122      |

| 7   | Con     | clusions and recommendations                                                                                                     | 123      |

|     | 7.1     | Conclusions                                                                                                                      | 123      |

|     | 7.2     | Outlook towards future development                                                                                               |          |

|     |         | 7.2.1 Systematic EMC design tool                                                                                                 |          |

|     |         | 7.2.2 Statistical method                                                                                                         |          |

|     |         |                                                                                                                                  | 123      |

| Re  | feren   | ces                                                                                                                              | 127      |

| Lis | st of p | publications                                                                                                                     | 137      |

| Su  | mma     | ry                                                                                                                               | 139      |

| Sa  | menv    | ratting                                                                                                                          | 141      |

| Cu  | rricu   | lum Vitae                                                                                                                        | 143      |

# Introduction

# 1.1 The growth of power electronic converters

After the continuous technological evolution of the last five decades, power electronics has become completely indispensable in our everyday lives. Power converters are present wherever there is a need to modify form of the electrical energy in every corner of industrial, commercial, residential environments [Bos00].

One of the principal advantages of power electronics is that it improves efficiency during the energy form conversion. Higher efficiency means that less energy is lost during the conversion. Less energy is dissipated today in the conversion compared to conventional methods. It has been estimated that roughly 15% - 20% of electricity consumption can be saved by the extensive application of power electronics [Bos00].

Another advantage of using power electronics is that it makes many functions or features possible. Examples of such improvements include the following:

#### Flexibility

- a wider range of input voltage provided by a universal power adapter,

- a programmable output voltage of an uninterruptible power supply (UPS),

#### • Controllability

- an accurate positioning capability provided by a servo system,

- a variable output frequency provided by a variable speed drive (VSD),

#### Efficiency

2 INTRODUCTION 1.2

optimized operating points for the fluorescent lamp powered by an electronic ballast,

- energy regenerated from a braking motor.

Because of these outstanding benefits, the market of power electronics keeps growing and extending to many new application fields. The market penetration is surprisingly unbalanced in different application fields. Almost 100% of AC-DC power supplies for information technology (IT) equipment use power electronics. In contrast, approximately 5% of motors are controlled by VSD [Onl05]. Hence, there is still a large potential market for power electronics.

## 1.2 The EMC requirements

The benefits gained are due to developments in the field of solid state devices. Power electronic applications are working at a high switching frequency to transfer the input energy to its output by bursts. The size of many passive components can be reduced because the intermediate stored energy becomes less or not necessary. Some side effects appear, for instance, the switching loss increases with the switching frequency. To limit the total switching losses per unit time, the switching losses during each switching transient must be reduced. To achieve this goal, the switching transient time needs to be very short. The insulated gate bipolar transistors (IGBTs) can switch much faster than conventional bipolar junction transistor (BJTs). Reducing dissipation has many advantages, including higher reliability and smaller heat sink. But, many side effects emerge with the high switching frequency and the short switching transient time. The high switching frequency lifts the level of electromagnetic interference (EMI) and the short switching transient time extends the EMI to a high frequency range.

EMI may cause degradation of performance of the converter or other devices [Ott88]. It is a critical design aspect today. Designers must do more things than just make their products workable. The converter needs to be functionally compatible with other electronic systems in the same electromagnetic environment, and must avoid any interference effects. This work is called electromagnetic compatibility (EMC) design.

It is mentioned above that converters are becoming a main EMI source. This is the main reason for controlling the EMI of converters. There are more reasons to apply stringent standards to control EMI. For instance, the modern electronic circuits around the power electronics have become more and more sensitive since the general working voltage of the embedded logical devices is reducing from 5V to about 0.9 V - 3.3 V. Another reason is that the noise can be coupled more easily from the noisy power electronics circuit to the electronics circuit around it since these circuits are being crowded into smaller spaces.

Many regulations or standards are imposed by authorized departments to limit EMI levels. The requirements on EMC are not endless, actually, consideration must be given to many other aspects, including functionality, volume and thermal performance. Otherwise, the cost may exceed the benefit obtained.

At the end of 2004, the Delft University of Technology and the University of Twente, both of them in the Netherlands, began a joint research project entitled "Multi-domain Optimization of Power Electronics (MOPE)". This project is funded by the IOP-EMVT which supports research and collaboration among academia and industry. The study is dedicated to the multi-domain design of power electronics, taking into account the major constraints of EMI, and considering also the thermal and spatial issues, using state of the art technologies.

# 1.3 Problem description and research object

The first problem is that there is no systematic approach to designing for EMC, especially in a complex power electronic system. Most EMC engineers may have experienced situations whereby a solution may suppress the noise in some frequency ranges but lift the noise level in other frequency ranges. The trial-and-error method is very time-consuming for this kind of application.

Because it is so easy to access advanced computing capability, there is a trend towards solving the problem using numerical methods. For a complex EMC issue, many factors come together simultaneously to determine the final EMI level. It is not an easy task to figure out a solution without logical thinking.

Circuit simulation is used widely to predict the EMI of a converter [Won01; Gra04]. Before the simulation, an accurate model must be built including all the components inside a converter. These models are entered into the simulation program and then the simulation runs in the time domain. The simulation may take several minutes before the final result is available. The result is unknown until the simulation is finished and then it is transformed to the frequency domain. A troublesome thing is that the simulation has to be run again from the beginning if any component inside the system changes its value.

Therefore, attempts are also made in the frequency domain, for instance, the work in [Ran98]. The noise source is translated to the frequency domain first by including the finite switching time, and then the equivalent circuits for the common mode (CM) and differential mode (DM) are introduced individually. Spectra of the noise received by the line impedance stabilization network (LISN) can be calculated in the frequency domain. It is mentioned in [Ran98] that a very large error is possible if the pulse rise times are not taken into account. In [Gon03], the impedance matrix is used to calculate the disturbance. An unavoidable prerequisite using this method is that the whole equivalent circuit must be time invariant.

Because of the shortcomings listed above, the present methods for EMC design need improvement. This is the first objective of this project.

The second problem is that the remedies for EMC suppression are limited. Literatual study shows that there are at least 14 kinds of remedies are proposed

4 INTRODUCTION 1.4

by acadamy, but only passive filter approach becomes the most widely adpated solution. For the rest solutions, the benefits achived are not attractive enough for industry to compensate the costs.

The second objective of this project is clarified as: finding innovative EMI suppression methods which are:

- effective in improving EMC performance,

- easy to implement,

- able to reduce the volume and weight of the power conversion systems,

- not having significant impact on functional and thermal issues.

#### 1.4 Research method

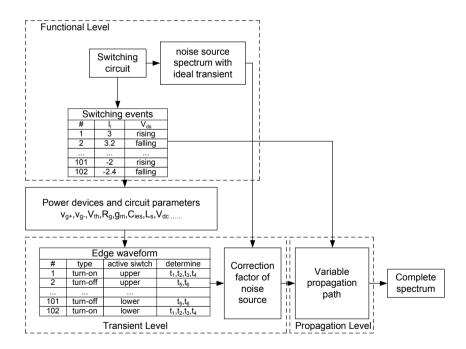

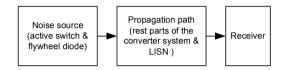

To achieve the goal, the hierarchical procedures are first established to replace the trial-and-error method. These are utilized to analyze the motor drive system. Possible solutions are then proposed and discussed.

The methodology used in this thesis is a hierarchical method. It divides the whole problem into three levels. For each level, models are built in different ways to reach a compromise between the accuracy and speed.

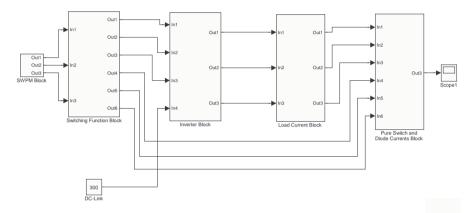

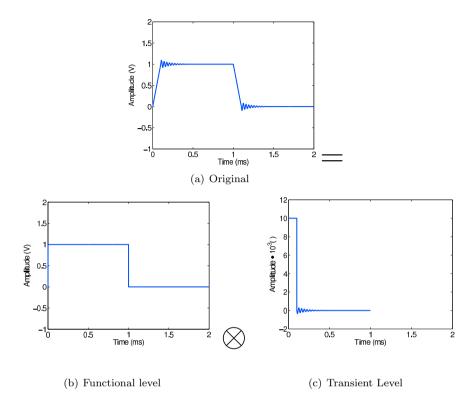

The first level is the functional level. On this level, parasitic parameters are omitted. The circuit can be modeled by switch function and all switches are idealized. Power electronics engineers are quite familiar with this level. The voltage and current waveforms are calculated by the fastest method. On this level, the computation speed needs to be as fast as possible to support a relatively long period of simulation. We want the "worst-case scenario" can be included in the simulation.

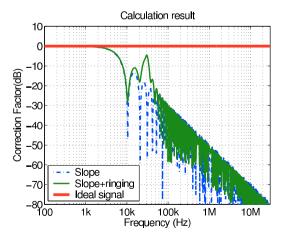

The second level is the transient level. Detailed behavior models of switches are utilized to get the voltage and current waveform of the very fast transient. The calculation is based on the information of operating points obtained on the functional level. On this level, only the parasitic inductors and capacitors around the switch are taken into account because they have an impact on the behavior of the switch. The analysis on the transients level obtains the details around the transient. The spectrum of the noise source is known using the analysis based on the functional level and the transient level.

The third level is the propagation level. All parasitic components are part of the propagation path. The ratio between the noise source and the measurement result is defined as a transfer ratio. The transfer ratio considers all possible topologies of different switching patterns.

With this method, much intermediate data is generated. This helps us to find the deviation in the middle way by comparing the intermediate data with additional measurements. The improvement of the EMC design is also traceable.

1.5 Thesis layout 5

Although the functional, spatial and thermal issues are mentioned in this objective, the functional issue is considered the most closely related to the EMC issue. The design interdependency will be studied in this thesis. The volume and weight requirements are only analyzed qualitatively. This means a traditional suppression method with bulky filters cannot be applied and an innovative method is necessary. Thermal issues are not defined in this research.

In this research, VSDs are chosen for investigation. The first reason is that in industrial applications, a large part of energy is consumed in this form. It is estimated that 60% - 65% of generated electricity in the United States is consumed in motor drives, and of those motors, 60% operate pumps and fans [Bos00]. For such kind of applications, optimizing motor speed can benefit the most. With VSD, the motor would not run at full speed all the time. There is a great potential to utilize power electronics to upgrade these motor drives to variable speed motor drives since the market penetration of VSD is only 5% at present. That is, the research is practical. Another consideration is that the high rated power and the fast switching transient make the EMC issue unavoidable.

In this research, the focus is narrowed down to control the  $conducted\ EMI$  of  $inverters\ in\ motor\ drive\ systems$ , within a frequency range of interest from 9 kHz to 30 MHz.

# 1.5 Thesis layout

Chapter 2 considers the configurations of the AC-AC converter. The mechanisms of noise sources are identified and analyzed. Chapter 3 begins the main contribution of the thesis. The hierarchical EMC design procedure is established and it is used for the modeling of an existing motor drive. The motivation and procedure to implement this approach are presented. Chapter 4 presents the observations in the time domain. After understanding how noise is propagated, a DC-bus filter is proposed to suppress the noise along the propagation path. The design procedures and benefits of this remedy are presented. Chapter 5 clarifies the EMC noise sources. A relationship is established between calculated results and compliance measurement results. Chapter 6 reviews firstly various EMC remedies which are implemented on the noise source side. A new active filter approach called "fourth leg compensator" is proposed. Its principle and simulation results are presented. Finally, Chapter 7 gives the conclusions and recommendations for future development.

Chapter 4 has been partly published in the IEEE Transaction on Power Electronics [Zha09] and at the EPE Aalburg conference in 2007 [Zha07]. Chapter 3 and 5 have been partly presented at PESC 2008 Greece conference [Zha08a]. Chapter 6 has been partly presented at EMC Europe 2008 Hamburg conference [Zha08b].

# **Configurations of AC-AC converters**

#### 2.1 Introduction

In many industrial or commercial applications, the loads need provision of AC power. The loads include motors, sodium vapor lamps, induction heating coils, and many other miscellaneous components. The power requirements are all in AC form but with different amplitudes, frequencies or phases. Normally, these values are variable during operation of the load. Also, the power distribution network has different standards around the world. AC-AC conversion is necessary when the requirements of the load are not compatible with the electric power provided by the public power grid. One good example is when a yacht is moored in a harbor. To use the local power network, the functions of the converter in the yacht should include voltage scaling, frequency conversion and galvanic isolation. The galvanic isolation is required especially for safety reasons and to prevent corrosion of the ship's hull.

Even though AC-AC converters are built for the same purpose, this is to bridge the different AC forms of the electric utility source and the load, many configurations exist due to various design specifications and requirements of the source and the load. The differences in the configurations have many aspects, including topology, rectifier, grounding, DC-bus, inverter and load type.

In this chapter, we first discuss the possible AC-AC converter topologies. They are ordered from the simplest to the most complicated. There can be one to five conversion stages. The bus types used in the power conversion process are illustrated with diagrams. Three topologies are selected for case study. After that, the noise source generation mechanisms are identified and the noise propagation paths are pointed out.

The influences of diverse configurations are discussed from the EMC point of view. The impact on EMC of different rectifiers, ground configurations, DC- bus and inverters are discussed. These configurations are specially defined for functional, safety and other requirements. At the same time, they have significant impact on the modes of noise propagation and the EMI level.

The discussion ends with the requirement of a new approach to analyze the EMC performance for AC-AC converters.

# 2.2 Topologies of AC-AC converters

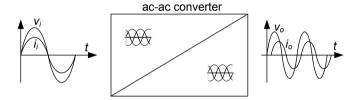

In AC-AC converters, the alternating currents and alternating voltages appear both on the source side and on the load side. The converters change amplitude, frequency and phase of the AC current and voltage waveforms between the source and the load. The conversion is normally controlled to reach the optimal operating points of the load. For an ideal AC-AC converter, the input voltage and the input current are in phase on the source side, and the relationship between the output voltage and the output current is according to the property of the load. The converter with sinusoidal waveforms is illustrated in Figure 2.1.

Figure 2.1: Voltage and current waveforms in an AC-AC converter

However, the voltage and current waveforms are not limited to be sinusoidal. The waveforms can be arbitrary provided they contain essential fundamental component. This gives much more freedom as long as the following conditions are satisfied for different applications:

- emissions stay below the limits for harmonics and EMI,

- the input power factor satisfies standards,

- efficiency requirements are met,

- specific requirements, for instance, the galvanic isolation can be provided.

Many topologies are available for AC-AC converters. Each of them has advantages and disadvantages, and is suitable for a particular range of applications.

#### 2.2.1 Single-stage AC-AC converter topologies

A conventional 50 Hz transformer is probably the simplest device that performs the AC-AC voltage scaling function. It is irreplaceable in the voltage scaling application due to its high efficiency and reliability, but strictly speaking, a transformer is not a converter.

The conventional AC-AC transformer cannot be used for frequency conversion since the variable voltage scaling depends on movable mechanical contacts and its limitations are evident. Therefore, power electronics devices are used in AC-AC conversion, which is called AC-AC converters.

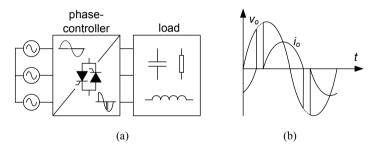

AC phase-controlled voltage controllers use TRIACs (TRIode for Alternating Current) or thyristors to conduct the load. The conducting angle depends on the firing angle and the load angle because a half-controlled switch can only turn off when the current returns to zero. Figure 2.2 shows the converter in block diagram form. The main drawback of this controller is that it draws distorted current from the supply line, and the input power factor is poor.

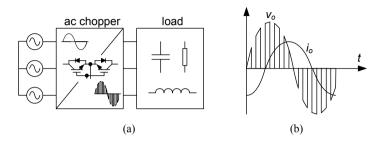

Figure 2.2: AC phase-controlled voltage controller; (a) diagram, (b) output voltage and current waveforms

The AC-AC chopper, illustrated in Figure 2.3 allows for controlling the output voltage. The variable output voltage scaling can be achieved by changing the duty cycle of the chopper circuit. For the AC-AC chopper, fully-controlled bidirectional power switches are necessary to turn off the current at an arbitrary moment. The output frequency stays the same as the input frequency. Low-pass filters are connected to both the input and output side of the AC chopper circuit in order to remove the switching ripples and harmonics. The ripples can also be filtered by load inductance itself.

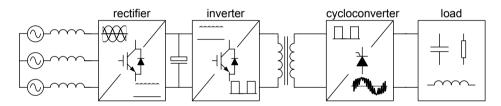

Cycloconverters can convert an AC source to another AC waveform of a lower frequency. They are normally used in a fixed input frequency and amplitude application with very high power rating. Both the amplitude and the frequency of the output voltage can be variable. The diagram and output voltage waveform are shown in Figure 2.4. The turn-off is normally by natural commutation. The limitation of the output frequency range exists.

Figure 2.3: AC-AC chopper; (a) diagram, (b) output voltage and current waveforms  $\,$

Figure 2.4: Cycloconverter; (a) diagram, (b) output voltage waveforms

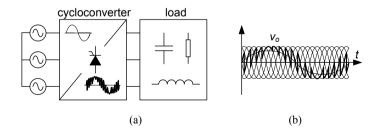

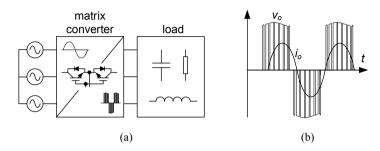

By replacing the natural commutation components with full controllable bidirection switches, the cycloconverter evolves into a matrix converter. The diagram is shown in Figure 2.5.

Figure 2.5: Matrix converter; (a) diagram, (b) output voltage and current waveforms

A single-stage AC-AC converter does not use energy storage components. It is a type of direct converter. The concept is simple and elegant. However, a main intrinsic drawback is that the output voltage is limited to 87% of the input voltage. Also it cannot ride through a voltage sag and the conduction losses are inherently high. The unavailability of fully controllable bidirectional semiconductor switches is the main limit of this topology.

## 2.2.2 Two-stage AC-AC converter topologies

Another class of AC-AC converters is the compound converter. A voltage or current link is used for energy storage. The converter changes input AC to an intermediate form of voltage or current and then converts the intermediate form to output AC with variable amplitude and frequency. The intermediate link decouples these two conversion stages, therefore, two conversions need not to be extractly synchronized and the control is simplified. Although the average energy flow is equal between input and output, the instantaneous input power does not need to be equal to the instantaneous output power. The difference between the instantaneous input and output power can be absorbed or delivered by the energy storage element in the intermediate link. The energy storage element can be either a capacitor or an inductor according to the control scheme.

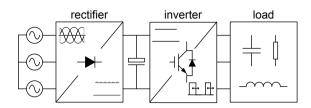

Figure 2.6 shows the diagram of an AC-AC converter with DC voltage as the intermediate link. A capacitor is used as the energy storage element.

# 2.2.3 Three-stage AC-AC converter topologies

To realize galvanic isolation function, the most common solution is using a transformer. Because the DC components cannot pass through the transformer, the

Figure 2.6: Block diagram of voltage source DC-bus converter

previous topologies are not feasible to provide galvanic isolation function.

One possibility is converting the DC intermediate form to an AC high frequency square wave. Then, the square wave passes through the high frequency transformer to achieve galvanic isolation. The high frequency AC square wave is available at the transformer secondary side and is synthesized to low frequency AC using a cycloconverter [Wik07; Kre02]. The topology is shown in Figure 2.7.

Figure 2.7: Block diagram of three-stage AC-AC converter with galvanic isolation

## 2.2.4 Four-stage AC-AC converter topologies

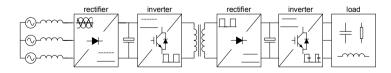

If a cycloconverter is not used in the previous topology, the AC square wave is rectified to DC voltage firstly, then a pulse width modulation (PWM) inverter is used to generate the fundamental component of the AC waveform. The topology is shown in Figure 2.8.

Figure 2.8: Block diagram of four-stage AC-AC converter with galvanic isolation

#### 2.2.5 Five-stage AC-AC converter topologies

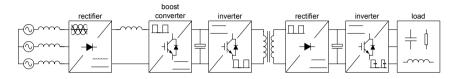

In some applications, a unity power factor input is required. This is realized by adding a boost DC-DC converter behind the diode rectifier. The boost converter is used to step up the DC-bus voltage, so that the DC-bus current is reduced. The topology of this popular configuration in AC-AC converters is shown in Figure 2.9.

Figure 2.9: Block diagram of five-stage AC-AC converter with galvanic isolation and a unity power factor

When using an active rectifier to replace a diode rectifier, one can achieve the same functions. An additional benefit is that it supports bidirectional power flow, but it needs more active components.

#### 2.2.6 Selected topologies for case study

In this project, three representative topologies are selected as study objects. The three selected objects have different numbers of conversion stages.

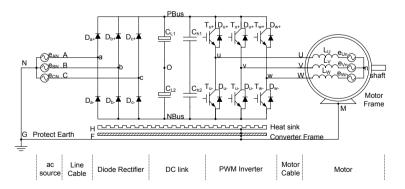

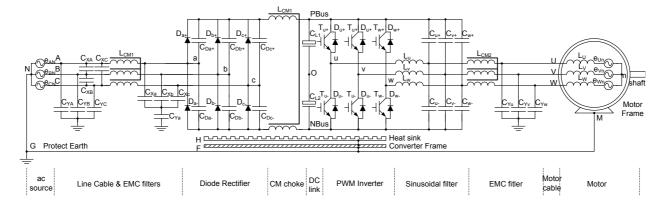

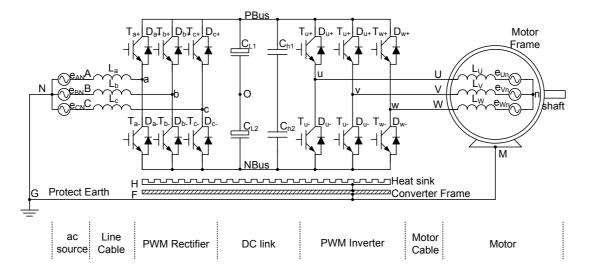

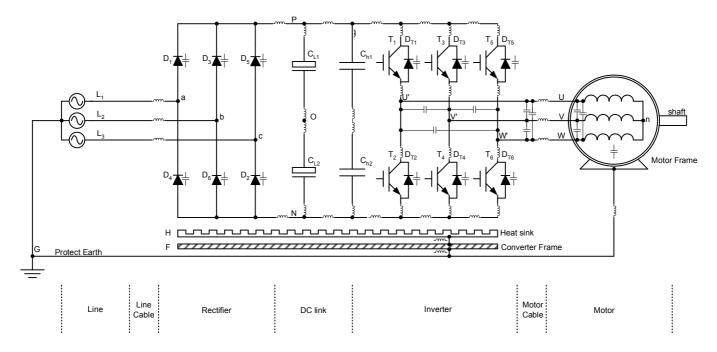

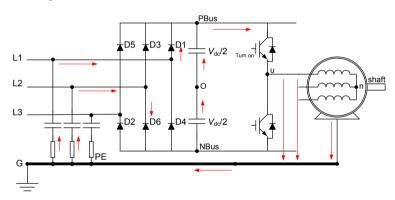

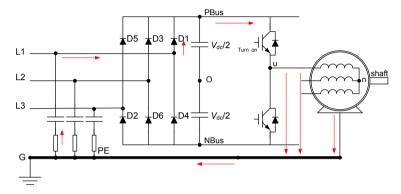

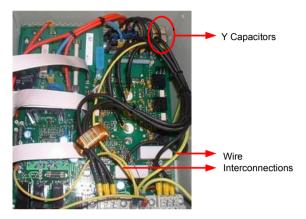

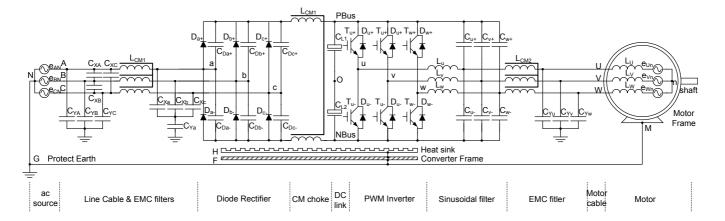

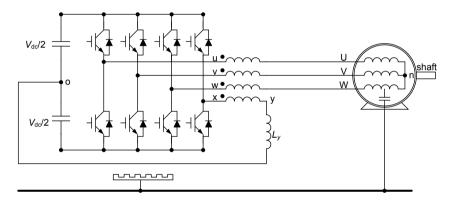

A voltage source inverter with a DC-bus capacitor and a diode rectifier front end is the most popular AC-AC converter used for motor drives. Its complete diagram is shown in Figure 2.10.

Figure 2.10: Block diagram of DC-bus voltage source inverter

A resonant pole inverter is shown in Figure 2.11. This inverter is working by

zero voltage switching (ZVS) at variable switching frequency. It is also used as a study object.

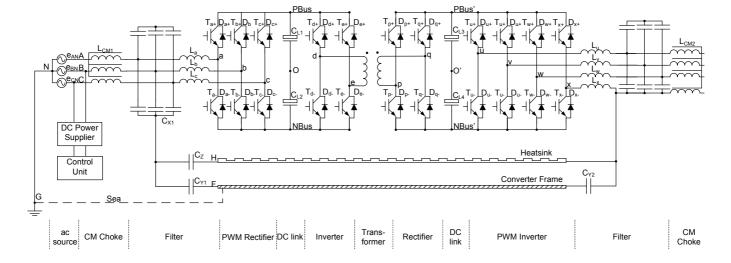

The third topology used in investigation is a four-stage AC-AC converter with galvanic isolation. It is used as a power interface between a public power grid and an offshore application. Because sinusoidal input currents with a unity power factor and bidirectional power flow are required, a three-phase PWM boost rectifier is included. In addition, it also includes DC capacitor banks on the primary and secondary side, a three-phase inverter system that is able to generate variable frequency and variable voltage, a DC-DC converter with isolation transformer, sinusoidal and EMC filters, a DC power supply, control circuits and sensors, protection circuits, a cooling system and a start up circuit to limit the current charging the DC-bus capacitor. The diagram is shown in Figure 2.12.

# 2.3 The capacitive coupling mechanism

Capacitive coupling is caused by a varying voltage source. It occurs between adjacent conductors or circuits. Since the dimensions of most components inside the drive system are substantially smaller than one wavelength at 30 MHz, the capacitive coupling mechanism can be modeled by lumped components when we consider the conduction emission issues of AC-AC converter systems.

The varying voltage source is called a capacitive coupling point if it has a fast transient voltage, and it has parasitic capacitances with surrounding circuits. A fast transient implies the presence of many high frequency components. In the high frequency range, parasitic capacitances form low impedance paths for the current.

Inside a converter system, there are numerous capacitive coupling points. The switches are components that form such points which generate the noise current by the capacitive coupling mechanism. Inevitable parasitic capacitances normally exist between these points and ground. The reason for using ground as reference is because we are investigating the noise current that flows between the phase lines and the ground.

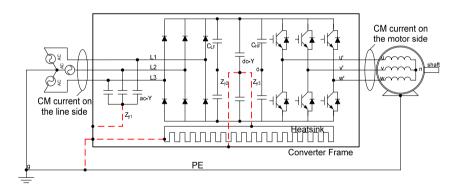

Figure 2.13 illustrates how current is generated by the capacitive mechanism in a drive system.

The noise current depends not only on the voltage transient, but also on the impedance of the current loop. The loop impedance includes the coupling impedance and the return impedance from ground back to the coupling point. The return impedance includes the impedances of ground, the power source and the input stage of the converter. Ground in the current loop may be the safety ground cable or the ground plane. In [Nav91], they are named as CM type I and CM type II. The impedance value can influence the noise current significantly.

For instance, for the coupling points of the output terminals of the transistor, coupling impedances exist between the die of the transistors and ground. The transistors are normally mounted on a heat sink. Because the cooling fin of the

Figure 2.11: Block diagram of resonant pole inverter

Figure 2.12: Block diagram of four-stage AC-AC converter with galvanic isolation

Figure 2.13: Capacitive coupling in a motor drive system

heat sink is exposed to the outside, it is commonly grounded for safety reasons. With the grounding of the heat sink, the coupling impedance has two parts. The first part is the impedance of the capacitor formed by the die of the transistors and the heat sink which are separated by a high thermal conductivity insulating film. The second part is the impedance of the wire connecting the heat sink to ground.

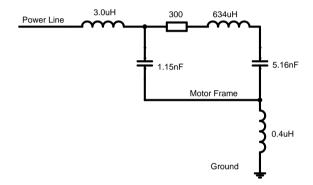

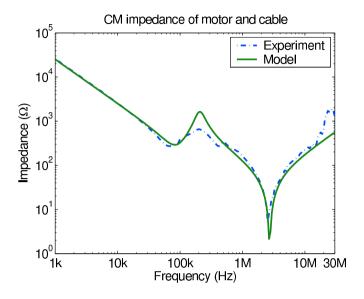

For motor drive applications, the capacitive coupling points also include the motor cable and the motor windings. This is because of the parasitic capacitances between the cable wire and ground. Also, there exists a capacitive coupling between the motor winding and the motor frame.

The fast voltage transients are generated by the switching of the transistors. In most cases, the transistors are not switched at the same time, otherwise the converter has no purpose because no load currents are built up with synchronized switching of transistors. In other words, the voltage transients at different capacitive coupling points have different waveforms.

If the coupling impedances are the same in three phases of the circuit and the circuit are exactly symmetrical, one approach to simplify the analysis is to decompose the voltage sources into CM and DM components. Assuming we have voltage source  $v_1$ ,  $v_2$  and  $v_3$  for three switches. The symbols  $v_{\rm DM(1,2,3)}$  and  $v_{\rm CM(1,2,3)}$  are used to represent the DM and the CM voltage sources. Ideally, we have,

$$v_{\text{CM1}} = v_{\text{CM2}} = v_{\text{CM3}} = \frac{v_1 + v_2 + v_3}{3}$$

(2.1)

$$v_{\text{DM(i)}} = v_{(i)} - v_{\text{CM(i)}}, i = 1, 2, 3$$

(2.2)

$$v_{\rm DM1} + v_{\rm DM2} + v_{\rm DM3} = 0 (2.3)$$

The DM components would not make any contribution to the flow of current through the ground. They produce the DM current flowing between phase lines. The CM components drive the current flowing through ground, and the currents flowing through the phase lines are evenly distributed. By combining CM and DM components, we find that the currents flow unevenly through the phase lines even for this capacitive coupling mechanism. For the DM component, it is called a mixed mode (MM) component in literature since it is a capacitive coupling mechanism and represents a differential format [Men04a; Men04b].

An easy approach to validate the existence of the MM component is to compare the DM components with and without the grounding strap of the LISN. The MM component should disappear when the CM current loop is broken. However, the DM component which is caused by functional switching should stay at the same level even if the grounding configuration changes.

The decomposition approach is based on an assumption that the values of the parasitic components in each phase are the same and fixed. If the symmetry condition does not exist, then the decomposition approach is not valid. Considering that the parasitic values of the components change with operating point, the coupling impedances are time-variant. The decomposition approach is limited to giving an intuitive explanation for qualitative analysis. To get a precise prediction, the decomposition approach is not enough.

# 2.4 The inductive coupling mechanism

Together with the capacitive coupling mechanism, the inductive coupling is another main mechanism. A source current loop with a fast transient current can couple noise through the mutual inductance to a victim loop. The induced noise sources can be modeled as controlled voltage sources according to Faraday's law of induction.

Inductive coupling is introduced by a varying current source. It can be modeled by mutual inductance between two inductor when the distance between two adjacent loops is shorter than one wavelength at 30 MHz. An inductive coupling mechanism is a major mechanism of noise generation for drive system since current abruptly changing is quite normal due to the operation principle of power electronics.

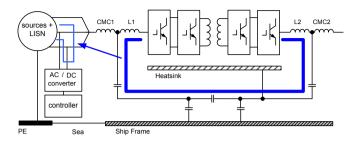

In an AC-AC converter investigated in [Roc07], a current loop is formed by bypass capacitors connecting the output neutral wire to the input neutral wire. Noise current with the same resonance frequency is found at the entrance of the AC-DC converter which provides power for controller and sensors. It can be explained through the inductive coupling mechanism. Figure 2.14 illustrates the inductive coupling in this AC-AC converter.

Figure 2.14: Inductive coupling in an AC-AC converter

Two aspects determine the effectiveness of the coupling. One is the value of the mutual inductance. We use the mutual inductance equation of a pair of loops to show what factors have an influence on the coupling efficiency:

$$M = \frac{\mu_0 N_1 N_2(\pi r_1^2)(\pi r_2^2) \cos \theta}{2\pi h^3}$$

(2.4)

Here  $N_1$  is the number of turns of the source loop,  $N_2$  is the number of turns of the victim loop,  $r_1$  is the radius of the source loop,  $r_2$  is the radius of the victim loop, h is the distance between the centers of two loops,  $\theta$  is the angle that the axis of the source loop makes with the axis of the victim loop.

The source loop or the victim loop can be a component, for instance, an inductor, the parasitic inductance of a capacitor [Che06], a CM choke [He05]. The loop can also be a printed circuit board (PCB) trace loop, a motor winding [Mue04], or ground loop. The induced voltages become the source of DM noise [He05]. If the victim loop includes ground, then CM noise is also generated [Poo03; Men08].

According to the equation above, the coupling effect can be significant when there are many turns in the source or the victim loop. This is the reason that placing a component has significant influence on the EMC performance [Che06]. In [Wan05], inductive coupling is used to cancel the parasitic inductance of a capacitor.

The second aspect that determines the effectiveness of the coupling includes the geometry and relative position of these two loops. With large areas and a small angle between the source and the victim, the coupling can also be aggravated. This extreme situation arises when two loops are placed concentrically.

To reduce stray inductance, the loop area can be minimized or be twisted in a clever way [Ros00]. While in some cases, hidden noise sources cannot be easily deduced. Some noise sources with subtle coupling paths can present a major source of EMI. For instance, a snubber circuit which is helpful in functional improvements can be a harmful EMI noise since the loop that is formed by the snubber and the transistor is accompanied by fast current transients [Poo03].

## 2.5 Rectifier configurations

There are two types of rectifier circuits that convert an AC supply into a DC voltage, namely, line-commutated rectifiers and self-commutated rectifiers. The main difference is in the commutation cells, which work under uncontrolled and controlled modes, respectively.

The rectifier with a diode front-end is line-commutated. Ideally, the diodes can be regarded as switches operating in neutral switching mode [Onl07]. That is, the diode is turned on when the voltage across the diode reaches the turn-on voltage and is turned off when the switch current is zero. Its commutation process depends on other components.

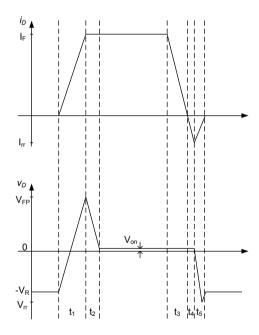

The diodes are often simplified as ideal switches, i.e., they have zero forward voltage drop and zero reverse bias current. From the EMC point of view, the transient phenomena and high frequency characteristics have significant impacts. The components cannot be idealized in EMC analysis. The typical turn-on and turn-off waveforms of a diode are presented in Figure 2.15.

Figure 2.15: Voltage and current waveforms for a power diode during turn-on and turn-off

For a diode-bridge three-phase rectifier with a filter capacitor connected on the output side, the commutations of diodes need to be calculated in steps. Firstly, the waveforms of the currents flowing through diodes are calculated numeri-

cally [Moh03]. With large capacitor or light load, the output current of the rectifier can be discontinuous. In this case, the currents through the diodes become zero prior to each commutation. Because no reverse recovery occurs, the EMI generated by a diode is quite low. In a continuous output current operation condition, the diodes need to commutate from one to another every 60 degrees. The diode now becomes a main high frequency noise source due to the reverse recovery current. The transient waveform is determined by the amplitude of the flowing current before the commutation and also the AC-side inductance and resistance.

When an extra finite inductor is used to improve the current waveforms and the ripple in the DC voltage output, the commutation can be much smoother. Another solution is using paralleled small capacitors with the diodes. In Figure 2.11, this strategy is used in the rectifier.

The diode bridge rectifier also brings voltage fluctuation of the DC-bus as referred to the neutral point of the AC-source. The voltage ripple is a triangular voltage with a frequency of 150 Hz. The amplitude is around 20% of the DC-bus voltage. This voltage increases the possibility of breakdown of the bearing lubrication when the motor is used as load. This mechanism generates the electrical discharge machining (EDM) bearing current. For the capacitive bearing current and ground leakage current, the influence of the diode rectifier can be ignored due to its very low frequency.

To achieve the capability of delivering sinusoidal input currents, the power factor corrector (PFC) rectifier uses a PWM mode. There is a tendency towards more and more PWM rectifier converters being used in power supply systems. They can be classified as voltage source rectifier (VSR) and current source rectifier (CSR) according to their energy-storage components. Compared to the diode rectifiers, PWM rectifiers have much faster transients. Also, these transients repeat more frequently than the diode rectifier. This makes the PWM rectifier a main noise source for EMI.

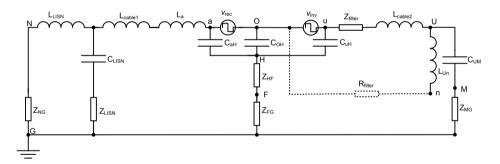

Figure 2.16 shows the PWM inverter with boost PWM rectifier. The three-phase AC input source is star connected. The neutral point of the AC-source (point "N" in Figure 2.16) is connected to ground (point "G" in Figure 2.16). The voltage difference between the rectifier input terminals and "N" is described by

$$\begin{cases} v_{aN} = v_{aA} + e_{AN} = i_a s L_a + e_{AN} \\ v_{bN} = v_{bB} + e_{BN} = i_b s L_b + e_{BN} \\ v_{cN} = v_{cC} + e_{CN} = i_c s L_c + e_{CN} \end{cases}$$

(2.5)

The switching functions of the boost rectifier and inverter are defined using  $s_i(i=a,b,c,u,v,w)$ , where  $s_i=1$  when the upper switch is turned on and the lower switch is turned off, and  $s_i=0$  when the upper switch is turned off and the lower switch is turned on. The voltage difference between the DC-bus midpoint (point "O" in Figure 2.16) and the rectifier input terminals can be expressed by

Figure 2.16: Block diagram of PWM inverter with boost PWM rectifier

$$\begin{cases} v_{Oa} = (\frac{1}{2} - s_a)V_{dc} \\ v_{Ob} = (\frac{1}{2} - s_b)V_{dc} \\ v_{Oc} = (\frac{1}{2} - s_c)V_{dc} \end{cases}$$

(2.6)

From Equation (2.5), (2.6) and the assumption that the three-phase source is balanced,  $v_{ON}$  can be expressed as

$$v_{ON} = \frac{1}{3}(v_{aG} + v_{bG} + v_{cG}) + \frac{1}{3}(v_{Oa} + v_{Ob} + v_{Oc})$$

=  $\frac{1}{3}(i_a s L_a + i_b s L_b + i_c s L_c) + (\frac{1}{2} - (\frac{s_a + s_b + s_c}{3}))V_{dc}$  (2.7)

Normally, the boost inductors have the same value. The first term of Equation (2.7) is the voltage drop across the boost inductors when conducting CM current. The second term is caused by switching on and off of the transistors in the PWM rectifier.

Using the same procedure to model the inverter part of this PWM inverter, the voltage difference between the neutral point of the load (point "n" in Figure 2.16) and the DC-bus midpoint (point "O" in Figure 2.16) can be expressed as

$$v_{nO} = \frac{1}{3}(i_u s L_u + i_v s L_v + i_w s L_w) + ((\frac{s_u + s_v + s_w}{3}) - \frac{1}{2})V_{dc}$$

(2.8)

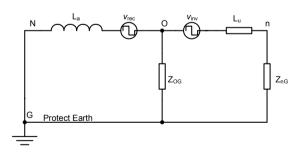

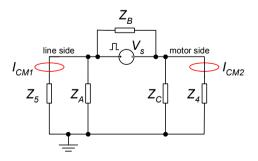

A simplified high frequency equivalent circuit of this kind of rectifier can be drawn in Figure 2.17, here,

$Z_{OG}$  is the impedance between the DC-bus and ground,

$Z_{nG}$  is the impedance between the load (the motor in this case) and ground,  $L_u$  is the winding inductance of the motor.

Figure 2.17: Equivalent circuit of PWM inverter system with PWM boost rectifier

Because the CM current is determined by the difference between CM voltages  $v_{\rm rec}$  and  $v_{\rm inv}$ , a strategy is proposed in [Lee00; Lee01] to reduce the CM current, by synchronizing the control signals of the rectifier and the inverter.

From the EMC point of view, the CM EMI produced by a rectifier will overwhelm that produced by the inverter due to the shorter distance to the mains power. The DC-bus midpoint potential fluctuation range is very large with a PWM front end. The CM voltage in the inverter output imposes on the DC-bus midpoint potential fluctuation, which doubles the amplitude of the CM voltage in the load. The increasing CM voltage drastically increases the possibility of bearing deterioration if the motor is used as the load. Also, these transients have very high dv/dt and di/dt, causing interference sources with a very wide spectrum.

# 2.6 Grounding configurations

There are many grounding methods in drive systems. They are chosen to ensure various requirements, for instance, meeting safety standards, limiting the transient overvoltage to ground, or riding through interrupted processes. In addition, one important aspect of grounding method consideration is its impact on EMC performance.

As explained above, the voltage and current noise sources are affected by the configuration of the rectifier and the inverter. The following discussions are based on the general and idealized grounding method. Changing the grounding configuration will not significantly change the characteristics of the noise sources. Actually, the grounding configuration has impact on the EMC performance by changing the path for high frequency current circulation.

# 2.6.1 Possible grounding methods

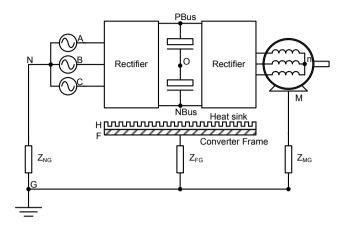

In Figure 2.18, the impedance between the neutral point of AC-source and ground is designated by  $Z_{NG}$ . Also, the impedance between the converter frame and ground and the impedance between the motor frame and ground are notated as  $Z_{FG}$  and  $Z_{MG}$ . Different choices of these impedances give different grounding configurations.

Reference [Das98] discusses the various possibilities of grounding methods for low-voltage and medium-voltage drive systems. Four grounding methods are discussed according to  $Z_{NG}$ . They are solidly grounding, low-resistance grounding, high-resistance grounding, and ungrounded systems. Generally, the solidly grounding method is adopted, because of its simplistic structure. The ungrounded system is not a standard due to its uncertain capacitance between phase lines and ground. It is advised in [Das98; Nel99] that a properly implemented high-resistance grounding system should become an industry standard.

In most cases, the motor frame is grounded. Inserting a damping resistor between the motor frame and ground is also an option for  $Z_{MG}$  [Mut02].

The grounding configurations mainly influence the current flowing through ground. Therefore, the CM noise is of the most concern. The simplified CM

Figure 2.18: Diagram of possible grounding methods

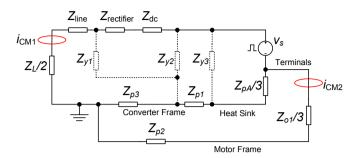

equivalent circuit in Figure 2.19 can be achieved. For this figure, the symbols and relative components are explained in Table 2.1.

Figure 2.19: CM equivalent circuit used including grounding configuration parameters  ${\cal C}$

## 2.6.2 The impact on the noise propagation path

EMI is a high frequency noise, and the measurement is normally done with LISN inserted between the mains and the equipment under test (EUT). According to the suggestion in the measurement standard [CIS99b], the earth of the LISNs needs to be tightly connected to the ground plane. The high frequency noise generated by the EUT is bypassed through the LISN, therefore, the  $Z_{NG}$  has no influence on the noise propagation path.

Table 2.1: Explanation of the symbols in the CM equivalent circuit

| Symbols             | Modeled components                                                   |

|---------------------|----------------------------------------------------------------------|

| $L_{ m LISN}$       | High frequency blocking inductor in the LISN                         |

| $Z_{ m LISN}$       | Constant measuring impedance in the LISN                             |

| $C_{\rm LISN}$      | Bypassing capacitor in the LISN                                      |

| $L_{\text{cable}1}$ | Inductance of the mains cable of converter                           |

| $L_{\text{cable}2}$ | Inductance of the motor cable of converter                           |

| $L_a$               | Boost inductance of the rectifier                                    |

| $L_{Un}$            | Winding inductance of the motor                                      |

| $C_{aH}$            | Capacitance between the rectifier input terminals and the heat sink  |

| $C_{OH}$            | Capacitance between the DC-bus and the heat sink                     |

| $C_{uH}$            | Capacitance between the inverter output terminals and the heat sink  |

| $C_{UM}$            | Capacitance between the motor winding and the motor frame            |

| $Z_{FG}$            | Impedance between the converter frame and ground                     |

| $Z_{HF}$            | Impedance between the heat sink and the converter frame              |

| $Z_{NG}$            | Impedance between the system neutral and ground                      |

| $Z_{MG}$            | Impedance between the motor frame and ground                         |

| $Z_{ m filter}$     | Impedance of the output filter of converter                          |

| $R_{ m filter}$     | Resistor between the motor neutral point and the mid-point of DC-bus |

On the contrary,  $Z_{FG}$  and  $Z_{MG}$  have significant impacts on the noise propagation path. When a solid connection is used between the motor frame and the ground, the high frequency current flows through the motor winding to the motor frame and then to ground efficiently. One approach to suppressing the CM current flowing on the motor side is adding the damping impedance in  $Z_{MG}$  [Mut02]. Adding damping impedance in  $Z_{FG}$  is also helpful when a PWM rectifier is used instead of a diode rectifier. The noise generated by voltage source  $v_{\rm rec}$  can be mainly damped by  $Z_{FG}$ , while compromises are expected when choosing the right value of  $Z_{FG}$  and  $Z_{MG}$  since a large  $Z_{FG}$  degrades the effect of the Y capacitor installed inside the converter and the value of  $Z_{MG}$  is limited by the safety standards of industry.

#### 2.6.3 The impact on the generation of bearing current

The grounding method has impact on the generation of the bearing current. There are several mechanisms which take effect simultaneously in the generation of bearing current. One is called circulating bearing current which is caused by capacitive and magnetic coupling effects [Mue04]. For this parasitic coupling phenomenon, it can be modeled as an equivalent lumped parameter network [Che96]. The grounding method affects this kind of bearing current by changing the component values in the noise propagation path.

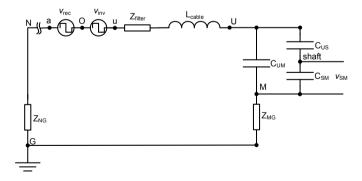

The equivalent circuit of the generation of shaft voltage is shown in Figure 2.20. The shaft voltage can be derived easily from the figure,

$$v_{SM} = \frac{C_{US}}{C_{US} + C_{SM}} v_{UM} = K v_{UM}$$

(2.9)

Figure 2.20: The impact of grounding method to circulating bearing current

The coefficient K is a constant according to the motor size and geometry. The voltage  $v_{UM}$  is rather dependent on the grounding method. Taken together, the grounding method determines the ratio between the shaft voltage and the

CM voltage of the inverter. With large  $Z_{MG}$ , the the circulating bearing current becomes much smaller.

Contrary to circulating bearing current which is caused directly by the high frequency component of CM voltage, the EDM bearing current has another mechanism. It is produced when the amplitude of the CM voltage drop over the motor bearing exceeds the breakdown voltage of the bearing lubricant.

With large  $Z_{NG}$  and  $Z_{MG}$ , the  $v_{UM}$  becomes much smaller, and so does the shaft voltage. This decreases the possibility of the occurrence of an EDM bearing current. It is noted that the impedance of LISN is not included in the equivalent circuit when considering the EDM bearing current. This is because the LISN is equivalent to open circuit in the low frequency range. On the contrary, the LISN impedance conceals the influence of  $Z_{NG}$  when considering the circulating bearing current.

# 2.7 DC-bus configurations

The DC-bus exists in multi-stage AC-AC converters. It can be galvanically connected by filter capacitor or filter inductor. To provide galvanic isolation between the input and the output, a high frequency transformer is sometimes used in the DC-bus.

In a DC-bus with capacitor, the potentials of the two rails of the DC-bus change simultaneously, and so does the midpoint of the DC-bus. The voltage differences between them are fixed as the DC voltage dropped on filter capacitors. Therefore, the DC-bus rails and the midpoint are modeled as the point "O" in Figure 2.19.

DC-bus configuration has influence on bearing current by changing the precondition of the generation of the second level effects, for instance, the EDM bearing current. The point "O" can be used for suppressing EMI noise. By adding a low impedance  $R_{\rm filter}$  between the point "O" and the point "n", the  $v_{UM}$  is much smaller because most of  $v_{\rm inv}$  appears across  $Z_{\rm filter}$ . This approach is followed by [Aka04a; Aka04b]. Most of the CM noise generated by the inverter can be suppressed. A main drawback as the author mentioned is that the point "n" in the motor is not always accessible. For the rectifier, the same idea can be applied. For a diode rectifier, it is not a problem because the noise generated by a diode has a much lower level. For the PWM rectifier, by connecting point "N" and "n" with a low impedance path, the same goal can be achieved. The point "N" is accessible by the star point of the input filter.

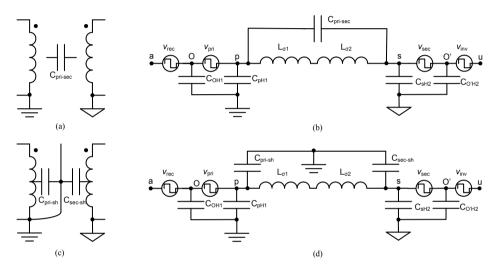

When a high frequency transformer is used on the DC-bus, one more inverter and one more rectifier are used. The noise sources created by them are named  $v_{\rm pri}$  and  $v_{\rm sec}$ . The high frequency model of the DC-DC converter part is shown in Figure 2.21.  $L_{\sigma 1}$  and  $L_{\sigma 2}$  are the primary and secondary leakage inductance. The coupling capacitor  $C_{\rm pri-sec}$  plays a very important role in the noise current. The noise current may flow through this coupling capacitor between the primary

side and the secondary side of the transformer. As a remedy, a metallic shield winding may be used to reduce the coupling. This arrangement creates the capacitance  $C_{\rm pri-sh}$  between the primary winding and the shield winding, and also the capacitance  $C_{\rm sec-sh}$  between the secondary winding and shield winding. This remedy is helpful if the shield is grounded on the mains side by guiding the noise currents directly to ground [Pau06]. Therefore, less  $v_{\rm sec}$  and  $v_{\rm inv}$  are transferred to the mains side.

Figure 2.21: The diagram of the model of HF transformer in the DC-bus: (a) without shield winding; (b) model of the transformer without shielding winding; (c) with shield winding; (d) model of the transformer with shielding winding.

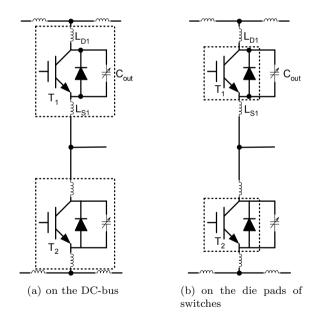

# 2.8 Inverter configurations

In all PWM DC-DC and DC-AC converters listed in Section 2.2, the switches are operated in different modes to turn on and turn off. Hard switching can produce a much higher EMI level than ZVS and zero-current switching (ZCS). The configuration of the converter has an impact on the EMC performance in the noise source.

In hard switching operation mode, the di/dt and dv/dt is largely due to the factor that the switches are turned on when the switch voltage is not zero and turned off when the switch current is not zero. Overvoltage and reverse recovery current of diodes are also causes of EMI.

The ZVS and ZCS conditions can be created by adding resonant components

or snubber circuits. The former is letting the switch load be a resonant circuit, and the latter is shifting stress voltage or current to snubber circuits.

In [Jon90], a new switch control method is proposed by adding a LC-filter between the bridge and the load. The filter lets the transistor current fall back to zero in every switch cycle, so that the ZVS condition is satisfied.

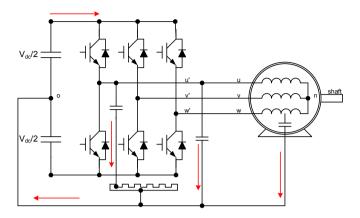

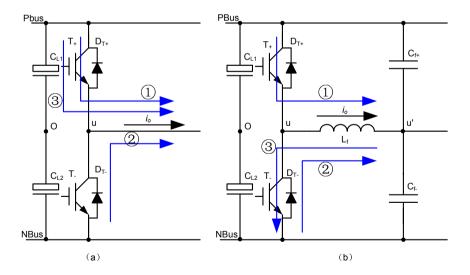

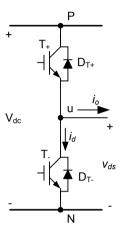

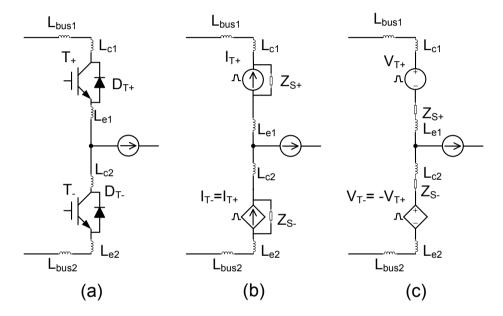

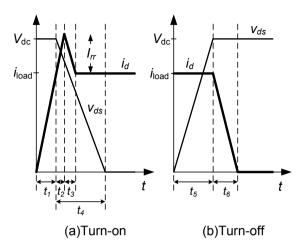

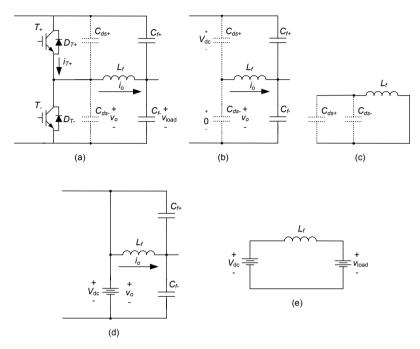

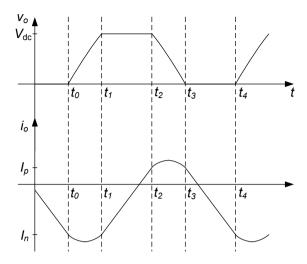

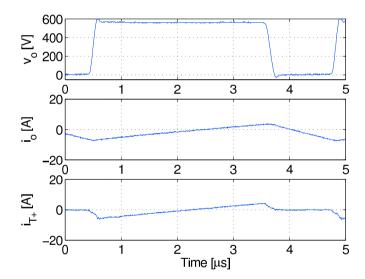

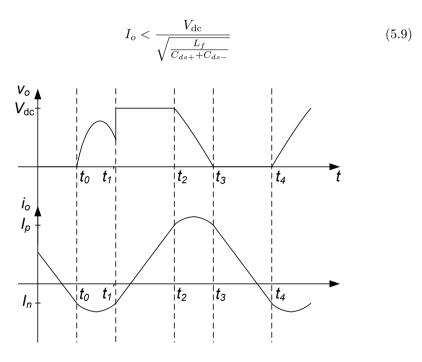

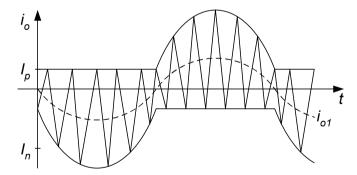

In Figure 2.22, an inverter leg of the ZVS inverter is shown. Initially,  $i_o$  is assumed to be flowing through  $T_+$  and  $L_f$ , and  $v_u = v_{PBus}$ . The current  $i_o$  is increasing according to

$$\frac{di_o}{dt} = \frac{v_{PBus} - v_{u'}}{L_f}$$

When  $i_o$  exceeds a preset value (when the preset value is positive),  $T_+$  is turned off. The current flowing through the freewheel diode  $D_{T-}$  decreases, and  $v_u = v_{NBus}$ . As long as the current falls back to zero,  $T_-$  is turned on at zero voltage (ZVS condition), and the diode  $D_{T-}$  is turned off at zero current. Therefore, the reverse recovery current is minimized. The benefit of the LC-filter here not only provides ZVS conditions but also filters the pulsating voltage to become a sinusoidal waveform.

Figure 2.22: Diagram of an inverter leg of: (a) a hard switch inverter; (b) a ZVS switch inverter.

# 2.9 EMC modeling

From the discussion above, we conclude that the influence of changing the configurations has two effects. One is the impact on the noise source, and the other is on the modification of the propagation path. The noise sources change their amplitude and repetition cycles according to the control scheme and the operating point. Any parasitic components formed by particular configurations can produce essential coupling paths even though the values are small.

The configurations have a significant influence on the final result. Choosing the most suitable EMC design is not an easy task. Previous methods need complete models including the full circuit before achieving EMC prediction. Any evaluations of changes to the configurations requires the calculation to be run from the beginning to end. The interactions between the configurations and the final result are not direct and easy to understand. Therefore, a hierarchical approach is required for an EMC analysis of such complicated, mutable AC-AC converter systems.

# 2.10 Summary

In this chapter, various configurations of AC-AC converters are considered. The purpose of using AC-AC converters are introduced in Section 2.1. The classification is based on the number of cascaded stages. These are described in Section 2.2 and can be summarized as:

- 1. Single-stage AC-AC converter topologies (AC-AC)

- 2. Two-stage AC-AC converter topologies (AC-DC-AC)

- 3. Three-stage AC-AC converter topologies (AC-DC-AC-AC)

- 4. Four-stage AC-AC converter topologies (AC-DC-AC-DC-AC)

- 5. Five-stage AC-AC converter topologies (AC-DC-DC-AC-DC-AC)

The transformation of the voltage forms are indicated between parentheses. The basic conversions of AC-DC and DC-AC are done by a rectifier and an inverter. The DC-DC conversions are inserted in the chain of conversion to change the DC-bus voltage. The AC-AC conversion is adopted in a three stage AC-AC converter to reduce the high frequency to output frequency only. For AC-AC conversion in a single stage AC-AC converter, not only the frequency, but also the amplitude and phases are controlled. The conversion is done by switching and keeps the fundamental components required.

Two mechanisms of coupling are introduced in Section 2.3 and Section 2.4. For analysis of EMI, these subtle coupling paths present the main mechanisms beside the tracks and components shown up explicitly in the circuit. The mechanisms are

explained so that the equivalent circuits and models can be built in the following chapters.

Various configurations of rectifier are used to achieve the same purpose of converting AC to dc. The impact on EMI is considered in Section 2.5. In Section 2.6, the possible grounding methods and their influence on EMI are discussed. There are two DC-bus configurations, with and without a high frequency transformer which change the noise source and propagation path. These are discussed in Section 2.7. The different types of inverters are considered in Section 2.8.

In Section 2.9, the necessity of using a hierarchical approach for EMC analysis is briefly discussed. This is because of the variable and complex interaction characteristics of the AC-AC converter system. The hierarchical approach is proposed in detail and implemented in Chapter 3.

# Hierarchical EMC design procedures

#### 3.1 Introduction

The topologies of various AC-AC converters are described in Chapter 2. Emphasis is placed on how these topologies relate to EMC issues and the mechanisms of noise generation inside AC-AC converters. Available suppression remedies are reviewed.

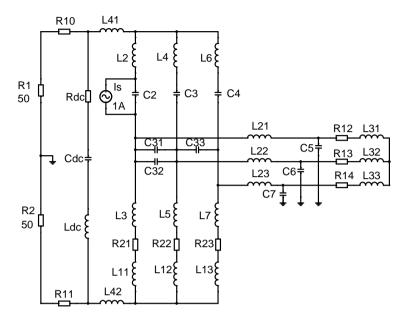

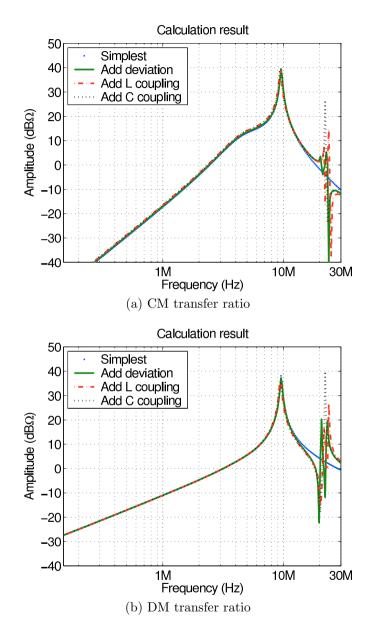

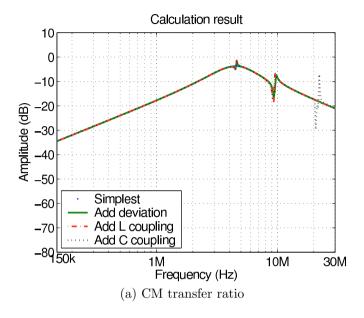

In this chapter, a hierarchical approach for better EMI modeling in AC-AC converters is presented. The approach is based on dividing the causal chain into segments, in order to avoid the bi-directional interaction between cause and result. Therefore, straightforward calculation becomes possible and it gives more insight into how the noise level can be suppressed. It is not necessary to start from the beginning to calculate the EMI level after some parameters have been modified. This helps us to compare several setups within a reasonable time-frame.

In Section 3.2, the difficulties of EMI modeling of the AC-AC converters due to the special characteristics of the applications are pointed out. Present methods of EMC design are reviewed next, and advantages and disadvantages are compared.

The feasibility of the proposed hierarchical approach is discussed in Section 3.3. The assumptions of using the approach are figured out and proven to be acceptable. The steps to applying this approach are also laid out in this section.

The concrete steps are described from Section 3.4 till Section 3.6. The chapter is summarized in Section 3.7.

# 3.2 Present EMI modeling methods

In an AC-AC converter, several timescales exist.

In the filtered output voltage and load current, the concerned time constants are in the range as long as 20 ms and as short as 500  $\mu$ s. In the frequency domain, it corresponds with the range between 50 Hz and 2 kHz (40th harmonic of fundamental frequency). This timescale is important to determine the overall mission of the system, for instance, the working frequency and amplitude of the power supply for load. It is concerned by specifications, for instance, the harmonic requirements of EMC and the power factor requirement. The time constant on this level can last even longer than several seconds or hours if we consider long term effects, such as acceleration process or the temperature rising before stabilization.

Inside the converter, the time constant ranges from the sampling time to generate the switching waveform to the switching period. The value is in the range as long as 500  $\mu$ s and as short as 2  $\mu$ s (depending on PWM frequency) and corresponds to a frequency range between 2 kHz and 500 kHz. This timescale is important for the duty cycle calculation and switching waveform generation. It concerns the low frequency range part of the EMC requirement.

In this thesis, these two timescales are named "functional level" because they relate to the function realization of a converter.

For components of the converter, the time constant ranges from 2  $\mu$ s to 10ns for normal applications of AC-AC converters. The corresponding characteristic frequency ranges from 500 kHz to 100 MHz. In this range, the phenomena of interest include turn-on and turn-off transients and ringing. It concerns the high frequency range part of the EMC requirement.

The level using this timescale is called transient level because transient is most concerned.

In power electronic applications, we are facing the difficult task of EMI modeling in the presence of large differences between the time constants which span several orders of magnitude.

The present methods used in EMI modeling can be classified into two kinds according to the working domain: time domain method and frequency domain method. The time domain method is based on a switch model and the frequency domain method is based on a noise source model.

#### 3.2.1 Time domain method

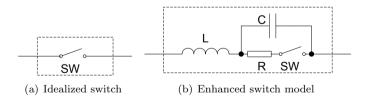

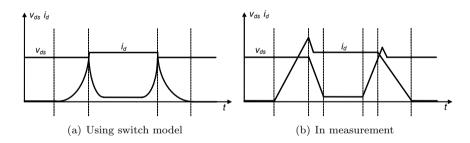

In a time domain method, the switching devices are modeled by ideal switches and other components to simulate the behavior of the switches.

This method is applied to the EMC analysis of DC-DC converters [Lab96; Lee99; Xu91; Swa95] and seldom used in AC-AC converters. This is due to the long time constants on the functional level of an AC-AC converter compared to a DC-DC converter. The time constant of an AC-AC converter is normally several

milliseconds, which means that the simulation must run for a long time to avoid missing the "worst" situation of interference.

The large difference between the time constants implies that we need to take very small time steps to get a sufficiently accurate EMI model at high frequencies. Assuming the calculation lasts for 5 periods, which is 100 ms for 50 Hz working frequency, at least 100 ms/10 ns=  $1\times 10^7$  points are needed to calculate the final result. This requires huge amounts of space for data storage and a long computation time to process the data. This makes it almost impossible to evaluate the impact of EMC performance if there is a slight change in component values, because the calculation has to then be done from the beginning which makes the optimization of components values very difficult.

In reference [Won01], the switch model is used for a three-phase motor drive. This simulation was repeated on a generally configured desktop computer and it took 53 minutes to get a set of simulation results that include a detailed spectrum in the full conducted emission frequency range.

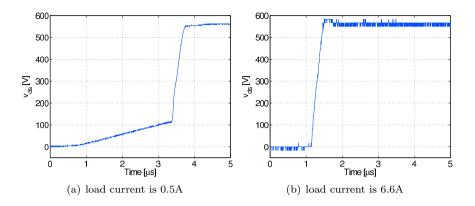

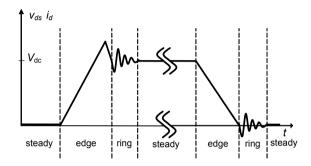

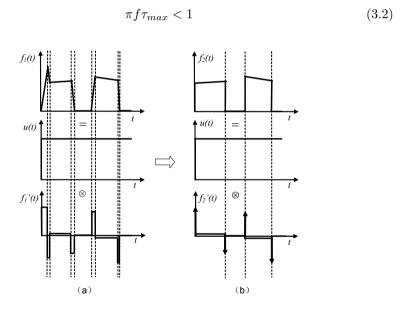

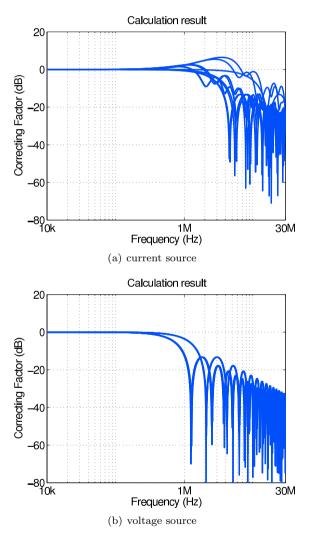

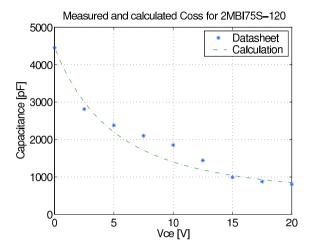

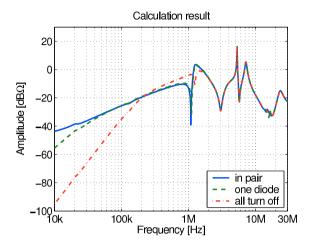

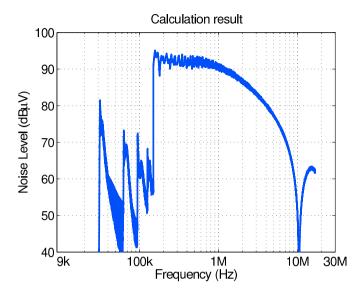

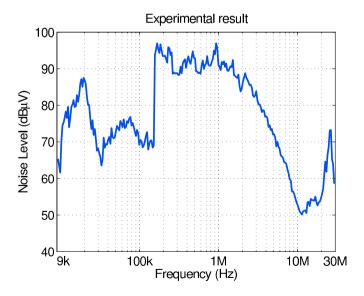

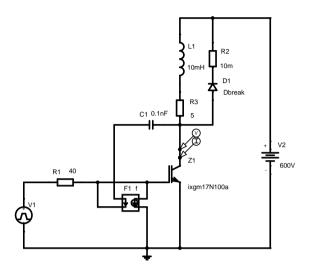

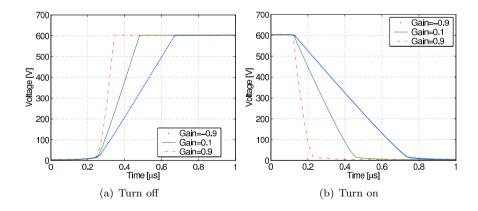

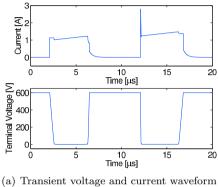

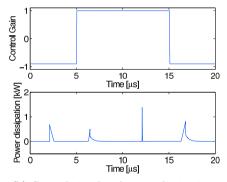

One extreme approach is to assume that the transient time is instantaneous and the switches are idealized. An ideal switch in "on" state is an ideal conductor and in "off" state it is an ideal isolator. This property can be described as: