# Synthetic X-Ray Image Generation Using FPGA-Based Hardware Acceleration

by

P.J. Aanhane

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Friday March 7, 2025 at 14:00

Student number:4644581Project duration:May, 2024 - March, 2025Thesis committee:Dr. ir. C. StrydisTU Delft, ChairDr. ir. R. RemisTU Delft, CoreR. de Jong, BSc.Philips Medical Systems, supervisorDr. ir. Z. Al-ArsTU Delft, supervisor

An electronic version of this thesis is available at https://repository.tudelft.nl/

## Abstract

Synthetic image generation involves the creation of artificially generated images that are indistinguishable from real ones. This field is an answer to challenges in the world of data acquisition, where the need for data is outpacing the availability. In cooperation with Philips Medical Systems, the generation of synthetic X-ray images is studied. Using datasets derived from such images, equipment testing and physician training can be improved. Additionally, training data can be generated for machine learning purposes.

The generation of synthetic X-ray images has been an area of research since at least 1994. The images have traditionally been generated using ray-tracing techniques on CPUs or GPUs. While effective, these methods are computationally expensive and demand high memory bandwidths. More recently, machine learning techniques have been explored for X-ray image generation. These approaches are promising. However, they require large labelled datasets which are often unavailable and the quality of the results is difficult to predict.

The aim of this thesis is to investigate whether hardware acceleration using a field programmable gate array (FPGA) can solve the challenges other methods face. Specifically, it discusses an architecture that can handle the large amount of computations in parallel. The memory architecture required to handle the high bandwidth demands is also explained. The performance of the proposed architecture is studied to see whether it is a viable solution.

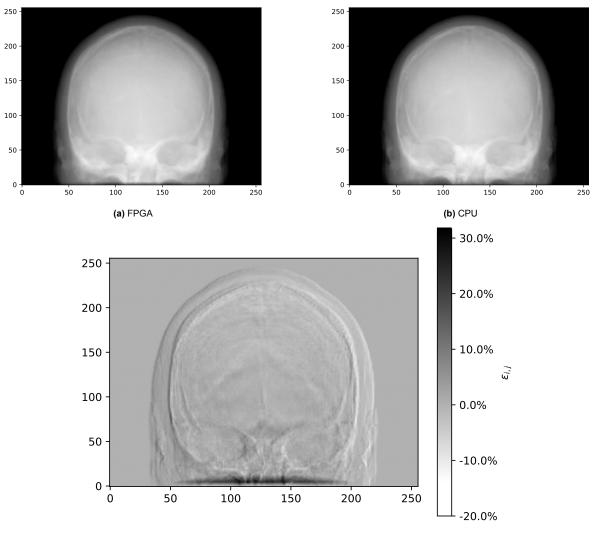

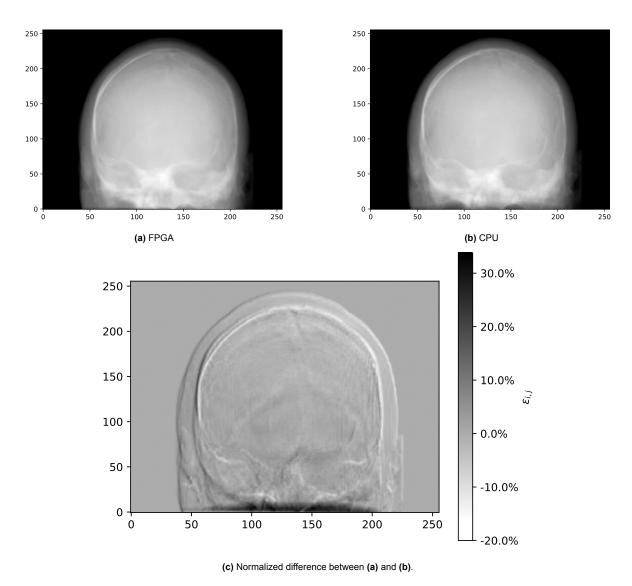

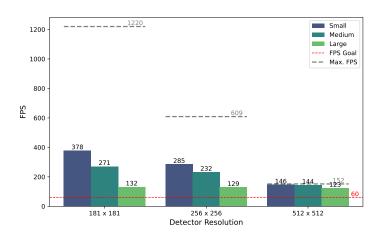

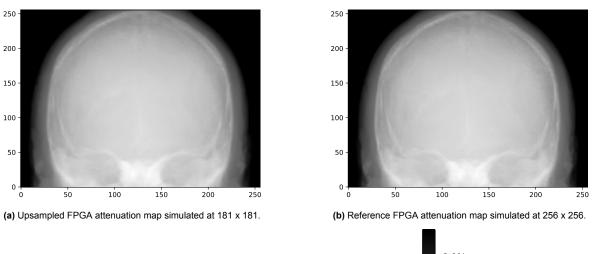

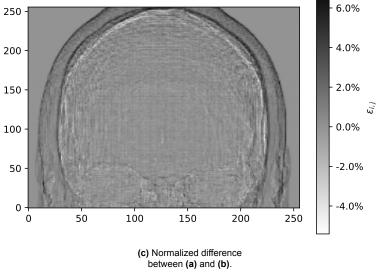

By simulating the traversal of rays through a voxelized model, an attenuation map was computed which can be used to determine X-ray intensities on a detector. The design separates computational tasks between a host machine and an FPGA, with an optimized High Bandwidth Memory architecture to maximize data throughput. Results demonstrated that the simulation produced realistic images with minimal error (2.26% - 3.00% deviation from CPU results), and performance is dependant on the detector resolution, achieving frame rates between 123 and 378 frames per second which are well above the goal of 60 frames per second. If more performance is required, upsampling can be used to speed up image generation by 33% at an increased error of 0.6% for an upsampling factor of two. These findings highlight the advantages of FPGA acceleration for deterministic, high-speed synthetic image generation without the need for large labelled datasets as required by machine learning algorithms.

## Preface

During my master studies, my interest in computer hardware continued to grow. My study programme was filled with as many performance- and architecture related courses as possible. Outside of my studies, I have worked as a software developer because of my enjoyment of programming. These interests came together perfectly in the research topic for this thesis. Being able to apply them in the field of medical technologies proved to be very satisfactory. Effectively using hardware to accelerate software is something I will definitely be spending more time on in the future.

I consider myself lucky to have been able to work on a topic which remained interesting for the entire nine month period. After the usual start-up problems everybody experiences, as soon as the project gained direction I have been nothing but enthusiastic. This made the months fly by and I am proud of what I was able to achieve.

I am grateful to everyone who supported me throughout my studies and this project. This includes my family, friends, and roommates, who patiently listened to my many discussions on the topic. I also want to thank my fellow TASTI team members for their valuable insights. A special thanks to Melis Umay Tekbas for her support in developing the hardware and to Klaus Juergen Engels for his deep knowledge and helpful guidance on the physical characteristics of X-rays and their simulation. I am also thankful to Per Knops for his assistance in transferring the project and for his openness to all my questions.

I would also like to thank my supervisor Zaid AI-Ars for his supporting role in the project and his helpful feedback. Finally, a special word of gratitude to my supervisor from Philips, Rob de Jong. You have taught me a lot about everything ranging from medical imaging to FPGAs, and I really enjoyed our many off-topic discussions on things like computers and cameras. I could not have done it without you and I look back on this internship with a lot of enjoyment, regardless of the four-hour-long travel days.

P.J. Aanhane Rotterdam, February 2025

## Contents

| Ab      | ostrad                                 | ct                                                                                                                                                                                                                                                                                                                                                  | i                                                               |  |  |  |  |  |  |  |  |  |  |

|---------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Preface |                                        |                                                                                                                                                                                                                                                                                                                                                     |                                                                 |  |  |  |  |  |  |  |  |  |  |

| No      | omen                                   | clature                                                                                                                                                                                                                                                                                                                                             | iv                                                              |  |  |  |  |  |  |  |  |  |  |

| 1       | Intro<br>1.1<br>1.2<br>1.3             | oduction<br>Challenge                                                                                                                                                                                                                                                                                                                               | 1<br>2<br>2<br>2                                                |  |  |  |  |  |  |  |  |  |  |

| 2       | 2.1                                    | kground         X-rays and imaging systems         2.1.1       X-ray generation         2.1.2       Matter interaction         2.1.3       Imaging systems         FPGA       Related work                                                                                                                                                          | <b>3</b><br>3<br>4<br>5<br>5<br>6                               |  |  |  |  |  |  |  |  |  |  |

| 3       | 3.1                                    | 3.1.3       Voxel model         3.1.4       Detector         3.1.5       Computational model         Algorithm                                                                                                                                                                                                                                      | 8<br>8<br>10<br>10<br>11<br>11<br>12<br>12<br>14<br>15          |  |  |  |  |  |  |  |  |  |  |

| 4       | <b>Sys</b> t<br>4.1<br>4.2             | Requirements                                                                                                                                                                                                                                                                                                                                        | <b>17</b><br>17<br>17<br>17<br>19<br>19                         |  |  |  |  |  |  |  |  |  |  |

| 5       | <b>Sys</b><br>5.1<br>5.2<br>5.3<br>5.4 | Processor       Ray generator         Ray generator       Engines         5.3.1       Computations         5.3.2       Engine memory         Ray scaler       Sale         5.4.1       First order approximation         5.4.2       Second order approximation         5.4.3       Final approximation         5.4.4       Hardware implementation | <b>21</b><br>22<br>23<br>24<br>25<br>26<br>28<br>28<br>28<br>30 |  |  |  |  |  |  |  |  |  |  |

|         | 0.0                                    | 5.5.1 Error definition                                                                                                                                                                                                                                                                                                                              | 30<br>31<br>31                                                  |  |  |  |  |  |  |  |  |  |  |

|    |                                        | 5.5.3                                                                                           | ι                                               | Jp                                                        | sa                                                                 | mp                                          | olin                                                       | ١g                                         |                         |                  |                     |                                       |                                       |         |                         |   | -  |                     |    |                       |                     |                     |                       |                                       |       |   |                                       |                       |                                       |                                           |                     |                         |                     |                       |                                       |  |                         |                                  |                   |                       | : | 33                                                                    |

|----|----------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------|--------------------------------------------|-------------------------|------------------|---------------------|---------------------------------------|---------------------------------------|---------|-------------------------|---|----|---------------------|----|-----------------------|---------------------|---------------------|-----------------------|---------------------------------------|-------|---|---------------------------------------|-----------------------|---------------------------------------|-------------------------------------------|---------------------|-------------------------|---------------------|-----------------------|---------------------------------------|--|-------------------------|----------------------------------|-------------------|-----------------------|---|-----------------------------------------------------------------------|

|    | Men<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5 | HBM a<br>Reque<br>Respo<br>6.4.1<br>6.4.2<br>6.4.3<br>Model<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4 | arcest<br>on:<br>ory<br>L<br>L c<br>E<br>S<br>S | ch<br>t n<br>se<br>/ la<br>Sm<br>Jan<br>Err<br>Str<br>Str | ite<br>nai<br>ayc<br>nal<br>ediu<br>rge<br>npi<br>or<br>ate<br>ate | ctu<br>nao<br>an<br>out<br>I m<br>um<br>e m | ire<br>ger<br>ag<br>iod<br>mot<br>sic<br>nct<br>/ 1<br>/ 2 | r<br>ger<br>del<br>noc<br>del<br>on<br>tio | I<br>dei<br>I<br>n<br>n |                  | · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · ·   | · · ·<br>· · ·<br>· · · |   |    | · · · · · · · · · · |    | ·<br>·<br>·<br>·<br>· | · · · · · · · · · · | · · · · · · · · · · | · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · |   | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | <br>· · · · · · · · · · · · · · · · · · · | · · · · · · · · · · | · · ·<br>· · ·<br>· · · | · · · · · · · · · · | · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |  | - · ·<br>- · ·<br>- · · | · · ·<br>· · ·<br>· · ·<br>· · · | · · · · · · · · · | ·<br>·<br>·<br>·<br>· |   | <b>35</b><br>35<br>37<br>37<br>39<br>40<br>40<br>41<br>42<br>42<br>42 |

| 7  | 7.1<br>7.2                             | ults an<br>Materi<br>CPU-<br>FPGA<br>7.3.1<br>7.3.2<br>7.3.3<br>Upsan                           | ial<br>ar<br>p<br>T<br>A                        | e<br>nd<br>er<br>Th<br>Ne                                 | rro<br>FF<br>for<br>eoi<br>as                                      | r<br>PG<br>ma<br>reti<br>sure<br>vsis       | A-l<br>anc<br>ica<br>ed                                    | ba<br>ce<br>al p                           | perf                    | ed<br>rfc<br>for | l re<br>orr<br>rm   | es<br>na<br>nai                       | an<br>nc                              | t c<br> | <br><br>                | m | ра | ari:                | sc | on                    |                     |                     |                       | - ·<br>- ·<br>- ·                     | · ·   | • |                                       |                       |                                       |                                           |                     | <br><br>                |                     | ·<br>·<br>·           |                                       |  | - · ·                   | <br><br>                         |                   |                       |   | <b>47</b><br>49<br>50<br>52<br>52<br>52<br>53                         |

| 8  | <b>Con</b><br>8.1<br>8.2               | <b>clusio</b><br>Conclu<br>Recon                                                                | us                                              | io                                                        | n                                                                  |                                             |                                                            |                                            |                         |                  |                     |                                       |                                       |         |                         |   |    |                     |    |                       |                     |                     |                       |                                       |       |   |                                       |                       |                                       |                                           |                     |                         |                     |                       |                                       |  |                         |                                  |                   |                       | ţ | <b>56</b><br>56<br>57                                                 |

| Re | ferer                                  | nces                                                                                            |                                                 |                                                           |                                                                    |                                             |                                                            |                                            |                         |                  |                     |                                       |                                       |         |                         |   |    |                     |    |                       |                     |                     |                       |                                       |       |   |                                       |                       |                                       |                                           |                     |                         |                     |                       |                                       |  |                         |                                  |                   |                       | ļ | 58                                                                    |

### Nomenclature

#### List of abbreviations

- ASIC Application Specific Integrated Circuit

- **AXI** Advanced eXtensible Interface

- BRAM Block Random Access Memory

- CLB Configurable Logic Block

- CT Computed Tomography

- **DDR** Double Data Rate

- **DRR** Digitally Reconstructed Radiographs

- DSP Digital Signal Processing

- FIFO First In First Out

- FPD Flat Panel Detector

- FPGA Field Programmable Gate Array

- FPU Floating Point Unit

- **GAN** Generative Adversarial Network

- GPU Graphics Processing Units

- HBM High Bandwidth Memory

- ISO Isocenter

- LUTRAM Lookup Table Random Access Memory

- PCIe Peripheral Component Interconnect Express

- RISC Reduced Instruction Set

SDRAM Synchronous Dynamic Random-Access Memory

SID Source-Image-Distance

TASTI Application-Tailored Synthetic Image Generation

**URAM** Ultra Random Access Memory

#### **Engine variables**

$x_{step}/y_{step}$  Horizontal or vertical distance between projection pixels

$x_{inc}/y_{inc}$  Increment in x or y position between layers

$x_{inc\_step}/y_{inc\_step}$  Change in x or y increment between projection pixels

$x_{inc\_start}/y_{inc\_start}$  Increment in x or y position for the first projection pixel

$x_{inc\_start}/y_{inc\_start}$  Increment in x or y position for the first projection pixel

$x_{min}/y_{min}$  Lowest x or y coordinate of the projected boundary

$x_{max}/y_{max}$  Highest x or y coordinate of the projected boundary

## Introduction

Synthetic image generation involves the creation of artificially generated images that are indistinguishable from real ones. This field is an answer to challenges in the world of data acquisition for machine learning and artificial intelligence applications. As the demand for high-quality datasets continues to grow, reliance on real data alone proves increasingly impractical. In the healthcare industry especially, gathering real-world data can be unsafe for the patient, unethical, or restrictive due to privacy legislation protecting against sharing sensitive data. Synthetic data offers a good alternative, enabling the usage of safe, high-quality, and privacy compliant datasets that can be used in the development of the smart systems of tomorrow.

This thesis is part of an internship project at the Dutch company Philips Medical Systems. The project is part of TASTI (Application-TAilored SynThetic Image generation) [32], which is a European funded initiative with the goal of developing a modular framework of transferable technology to innovate synthetic image generation tailored towards applications in several industries. Philips has been an industry leading expert in medical imaging systems and has done a lot to innovate the healthcare industry. The interventional X-ray department aims to improve patient healthcare and build systems that can save lives. These systems have strict real-time processing requirements which are often solved using streaming-based processing. At the TU Delft EEMCS Computer Engineering group, a lot of effort has gone into techniques that can meet these demands, ranging from the development of stream-based processing applications [16] to composable streaming interfaces defined using software [10].

For Philips specifically, the TASTI project is about creating a virtual testing platform using synthetic image generation, for which three different applications have already been identified:

- Equipment testing: Synthetic images can simplify the process of system integration tests. Real tests require the X-ray source, which can be inconvenient. The restriction because of safety, though justified, can also be time consuming. Through elimination of the X-ray source while maintaining the ability to produce an image, system development can be accelerated and quality is maintained.

- Physician training: A virtual environment that simulates the operation of medical equipment accurately allows a physician to gain hands-on experience in a safe setting without relying on harmful radiation sources or involving actual patients. Such a platform ensures risk-free training, making the process both efficient and accessible.

- 3. Al data generation: Computer vision algorithms are employed for the purpose of system validation. They can be used to judge image quality and perform simple medical analysis. Such algorithms require large datasets for training purposes. These can be generated using the virtual testing platform.

#### 1.1. Challenge

The virtual platform currently under development consists of an exam room containing the controls and a technical room containing a system cabinet for simulations. This simulation is CPU-based and operates on a full-body model, also known as a phantom. Currently, it produces about 5 frames per second, which is insufficient for real-time performance.

The bottleneck of the simulation lies in the high memory throughput necessary to produce each frame. Without optimizations, generating a frame using a whole-body phantom requires a memory transfer of approximately 2 GB. To achieve a speed of 60 frames per second, a transfer rate of 120 GB per second would be required. Such speeds are infeasible for regular PC hardware. This estimate does not even consider the huge amount of calculations required for processing this data.

#### 1.2. Research questions

The aim of this Master's thesis is to determine whether computational- and memory throughput challenges existing solutions face can be addressed using hardware acceleration kernels. Specifically, it seeks to investigate whether a custom FPGA architecture can be used for real-time synthetic image generation of X-ray images at the rate of existing detectors. To answer this question, the following sub-questions are posed:

- 1. What system architecture is needed to support real-time generation of synthetic X-ray images?

- 2. What memory architecture is required to handle the high data throughput?

- 3. What is the maximum performance achievable using FPGAs and does it satisfy the necessary application performance?

#### 1.3. Thesis outline

This thesis will start with some background information in Chapter 2. It will give a short introduction on X-ray radiation and imaging systems. It will also explain the FPGA. Next, Chapter 3 will show the steps and components required to simulate an accurate X-ray image. The following chapters talk about the architecture. Chapter 4 explains the design of the system and introduces the architecture. In Chapter 5, the implementation of the components is discussed. This includes both the software and hardware components. How the memory communication is implemented is mentioned in Chapter 6. Finally, Chapter 7 provides an analysis of the simulation results and Chapter 8 will conclude the thesis.

# $\sum$

# Background

In this chapter, the required background knowledge is discussed to provide context into X-ray based imaging systems. In Section 2.1, the physics behind X-rays is summarized and the concept of X-ray imaging systems is introduced. Section 2.2 will provide an explanation on FPGAs, heavily utilised in this thesis. Section 2.3 will cover related work.

#### 2.1. X-rays and imaging systems

The history of medical and industrial X-rays and the evolution of the technology of its sources has been ongoing for about 125 years. The first indirect discovery has been attributed to Julius Pluecker, who reported a greenish fluorescence on a glass wall while studying Geissler discharge tubes in a partial vacuum [8]. This glow is characteristic evidence of electrons hitting a wall and producing X-rays, but the underlying mechanism was not yet known at the time . In 1895, while experimenting with electric current in cathode-ray tubes, Wilhelm Röntgen observed similar effects and theorized that electrons striking the glass tube produced unknown radiation. He called the phenomenon X-radiation because of its uncertain nature and connection to light [13].

X-rays are electromagnetic radiation. Electromagnetic radiation transports energy, also called radiant energy, through space using waves and photons just like radio waves, visible light or microwaves. As with all forms of light, X-rays are characterized by their frequency or wavelength. In literature, most sources define the wavelength range of X-rays to be between 0.01 nanometres and 10 nanometres [31] [21]. This corresponds to an energy range of 100 eV up to 100 keV.

#### 2.1.1. X-ray generation

There are two main ways X-rays are generated. The first is related to their initial discovery. This method, known as Bremsstrahlung derived from the German word for slowing down, involves the interaction of high-speed electrons with the anode of an X-ray tube. Electrons are accelerated by the tube's acceleration voltage, moving them from the negative cathode to the positive anode. When these high-energy electrons collide with the anode material, they are decelerated and deflected by the electric fields of the atoms in the anode. The deceleration produces X-rays with a continuous energy spectrum [21].

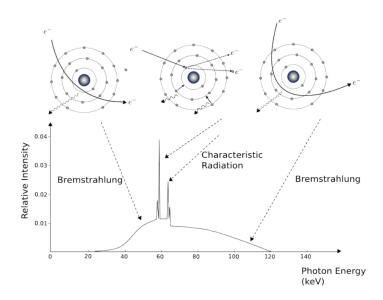

Characteristic X-rays are produced when high-energy electrons eject inner-shell electrons from atoms in the anode material, creating vacancies. To stabilize, electrons from outer shells transition into these vacancies, releasing X-ray photons with energies equal to the difference between the two shell levels. These energies are unique to the atomic structure of the target material, resulting in a discrete spectrum with sharp peaks corresponding to specific transitions [21]. When the continuous and discrete spectra are combined, the spectrum shown in Figure 2.1 is produced. An X-ray beam consisting of radiation with multiple energy levels is referred to as polychromatic. When only a single energy level is present, it is called monochromatic.

Figure 2.1: Energy spectrum produced by a tungsten tube [21].

#### 2.1.2. Matter interaction

X-rays have the ability to penetrate matter, but the amount is dependent on both the material as well as the X-ray energy. In the energy range that is used for medical imaging, there are three kinds of relevant interactions, described in [21], that can occur when X-rays pass through matter. The first two are physical and occur when X-rays collide with either nucleons or electrons. The third happens when X-rays are influenced by an electric field.

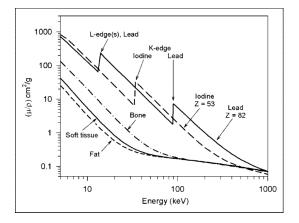

These interactions can lead to radiation absorption, but are also responsible for scattering. Both are responsible for X-ray attenuation. The linear attenuation coefficient  $\mu$  is a material property and a measure for how much the intensity of an X-ray beam is reduced the further it penetrates matter. The linear attenuation takes the density of a material into account, expressed at  $\frac{\mu}{\rho}$ . Figure 2.2 shows how the mass attenuation can change depending on the material and the X-ray photon energy. Using the linear attenuation of a material, the Lambert-Beer's law [21] describes the radiation intensity as it passes through a material:

$$I = I_0 e^{-\int_0^l \mu(x) dx}$$

(2.1)

where  $I_0$  describes the incident X-ray intensity, l the thickness of the material, and  $\mu(x)$  the linear attenuation at x.

Figure 2.2: Plot which shows the linear attenuation for different materials and different energies [28].

Figure 2.3: Illustration describing the Compton effect, where an incident photon strikes an outer shell electron, scattering the photon [15].

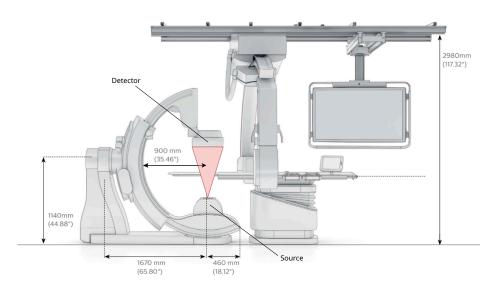

Figure 2.4: Philips Azurion 7 B20/15 bi-plane imaging system showing the location of the source and the detector, adapted from [1].

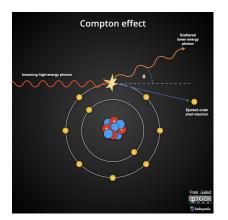

In the case of scatter, the most prevalent for high-energy radiation is Compton scattering [15]. The cause of this type of scattering is an incident X-ray photon hitting an electron which ejects it from its orbit. The photon is also scattered. The ejected electron is referred to as the recoil electron. The scattered photon will have both a different direction as well as a different energy. Figure 2.3 shows an illustration of the phenomenon.

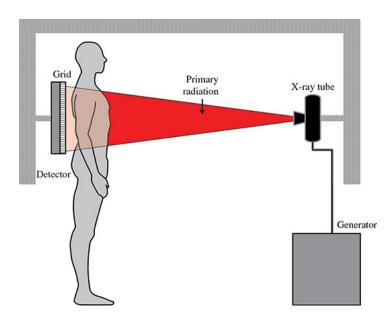

#### 2.1.3. Imaging systems

Figure 2.4 shows an interventional X-Ray system by Philips with its most important components. The process begins at the X-ray tube, also known as the source. The source produces the radiation which moves through the subject. In medical imaging, low energy X-rays are removed using a thin metal plate as a filter. This is because the low energy rays are largely absorbed by a patient, resulting in a higher patient dose without improving the image quality. The type of beam is referred to as a cone beam, due to its outward portraying direction [21].

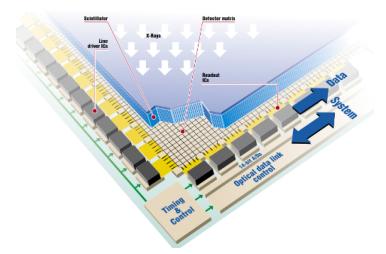

In modern systems, the flat panel detector (FPD) has become the standard. FPDs can either directly or indirectly capture the radiation. Direct conversion FPDs contain an X-ray sensitive photoconductor which detects the presence of radiation. Indirect conversion FPDs contain a scintillating layer which first converts X-ray photons into visible light. The detectors used by Philips have indirect conversion FPDs. The detector is covered by an anti-scatter grid, which limit the degrading effects of this phenomenon. A diagram of the detector used in Philips systems can be seen in Figure 2.5. Note the scintillating layer, shown in blue, that covers the detector matrix.

#### 2.2. FPGA

An FPGA is a type of integrated circuit which is designed to be reconfigurable. Unlike traditional logic devices such as application-specific integrated circuits (ASICs), the connections between logic gates and components on an FPGA can be modified after the chips have been produced. This ability makes FPGAs suitable devices for prototyping high-performance applications.

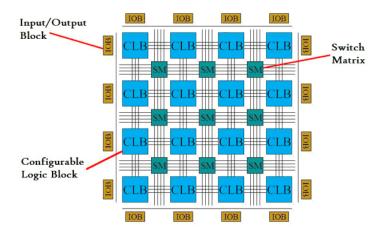

Reconfiguration is achieved through an array of fixed configurable logic blocks (CLBs) and flexible interconnects that can be configured to perform either complex operations or to serve as simple logic gates. The structure is shown in Figure 2.6. FPGAs can also include static hardware ranging from dense memory arrays to dedicated hardware multipliers which can be incorporated in a design through the interconnect [17]. FPGAs are useful for prototyping high-performance applications and can support most designs, provided it has the required resources available. Highly parallel parts of an application can efficiently be implemented with custom logic. This is different from a conventional CPU where one

Figure 2.5: Diagram showing the components that make up a detector [34].

Figure 2.6: Structure within an FPGA [25].

is restricted by the hardware implementation which cannot be altered after production.

#### 2.3. Related work

The generation of synthetic X-ray imagery is not a novel field, with research on rendering techniques and computational algorithms dating back to at least 1994. Over the past two decades, there has been a strong focus on digitally reconstructed radiographs (DRRs) as the primary method for simulating X-ray images. DRRs are computational approximations of X-ray images. They are based on 3D imaging datasets derived from computed tomography (CT) or reconstructed rotational X-ray images. There are several approaches to the usage of these dataset for the image generation process.

It was discovered early on that approaches involving the simulation of rays moving through the model, also known as ray tracing, are computationally expensive and require a high memory bandwidth. [27] describes the usage of attenuation fields that extend ray tracers, allowing most computations to be performed in a preprocessing step. This method significantly accelerates DRR generation. The attenuation field are more memory efficient than storing precomputed DRR tables used in conventional methods. Using this approach, a speed of roughly twenty images per second can be achieved.

In order to speed up the computations, graphics processing units (GPUs) are a good candidate due to the large number of processing cores available. [29] achieves a performance of approximately 100 images per second through algorithmic simplifications and specialized ray casting techniques. [33] optimizes DRR rendering on GPUs and evaluates performance across four commercially available devices. They were able to achieve a performance ranging from 190 to 370 images per second. Both

techniques used small models however of approximately 60 MB, which means the models used were either not very large or not very detailed.

More modern approaches advocate the usage of machine learning algorithms to aid the X-ray image generation process. The problem with these techniques is that they rely on large amounts of labelled images which are rarely available. To address this, [9] introduces a multi-stage Generative Adversarial Network (GAN) to generate synthetic images with semantic labels for data augmentation. This approach performs well on small datasets. [24] attempts to generate synthetic CT images from Magnetic Resonance Imaging (MRI) data using GANs with cycle consistency. Cycle consistency refers to the similarity between images translated from one domain to another, and back to the initial domain. The implementation included additional improvements such as perceptual loss, coordinated convolutional layers, and super-resolution techniques. Both methods report accurate images compared to other methods, though no note is made of relevant performance metrics.

# 3

# Simulation outline and algorithm explanation

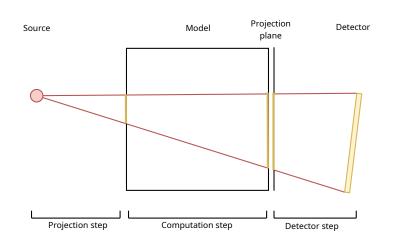

In this chapter an outline of the simulation setup will be provided. This outline includes a description of the simulation model, including some definitions and the components modelled by the system. Furthermore, the algorithm itself is explained which consists of a projection step, a computation step, and a detector step.

#### 3.1. Simulation model

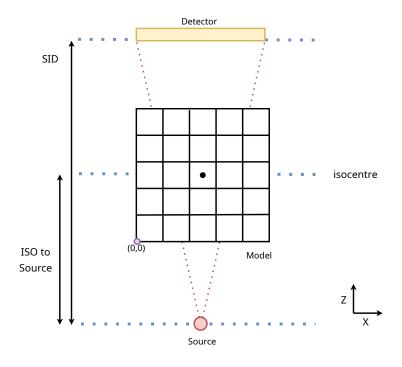

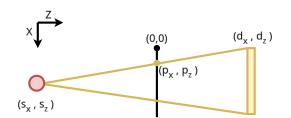

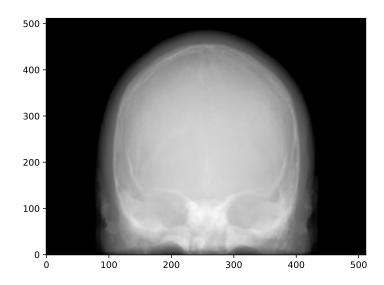

In order to simulate an X-ray image, three important components need to be simulated. These three components, visible in Figure 3.1, are the source, physical model, and detector. The source should accurately represent how X-rays are produced and how they move through physical space. The model serves as a stand-in for the subject and describes how X-rays are altered as they penetrate material. The detector is responsible for registering the X-ray intensities which are used to produce the final image.

#### 3.1.1. Simulation arrangement

To set up the simulation of X-ray images, the spatial arrangement of the components is critical. Figure 3.2 shows the arrangement and coordinate system used in the simulation. The source is positioned to emit X-rays directed towards the model. The model is placed at the centre, with the frontal bottom-left corner placed at the origin. Behind the model, the detector is placed to capture the X-rays measuring their intensity to construct the final image.

The isocentre (ISO) is defined as the point around which the source and detector rotate. it is not a fixed point but it can move as well. The movement is dictated by the rotation and translation of the source and detector with respect to the model. For the purpose of consistency, all simulations used throughout this thesis have placed the ISO at the centre of the model. Any realistic position is supported however. The ISO-to-source distance is also fixed in all simulations. The source-to-image distance (SID) can vary however, affecting the shape of the beam. This is summarised in table 3.1.

| Parameter     | Value           |

|---------------|-----------------|

| SID           | 89.5 - 119.5 cm |

| ISO to Source | 81 cm           |

Table 3.1: Value range of SID and ISO to source.

Figure 3.1: Diagram showing the source, model, and detector which need to be modelled in the simulation [18].

Figure 3.2: Diagram showing the arrangement of the components in the coordinate system.

Figure 3.3: Example voxel model of a skull. This model is used throughout this thesis.

Figure 3.4: Example of how the voxel model is constructed out of individual layers or planes.

#### 3.1.2. Source

The source is defined by a three-dimensional vector containing an X, Y, and Z component. Throughout the simulation this vector can be transformed, as a real imaging system can also move to different positions. This transformation, which can be a combination of rotation and translation, also affects the trajectory of the rays that the source produces.

The source is modelled as a single point in space and produces a pyramid-shaped beam consisting of individual rays. The simulated source is a simplification compared to its physical counterpart because of two reasons. First, the beam produced by the source is modelled as radiation with an energy of 75 keV. As explained in Chapter 2, this means the beam is monochromatic rather than polychromatic. This assumption simplifies the simulation by eliminating the need to account for the varying absorption of X-rays at different energy levels. This approximation is considered valid because, as shown in Figure 2.2, the linear attenuation coefficients for soft tissue, fat, and bone show a similar dependency on the X-ray energy for higher levels. However, this simplification is not able to represent physical effects like beam hardening, which is an increase in the mean energy of the X-ray spectrum as radiation moves through an object. Artifacts caused by such effects like cupping and streak artifacts [3] are therefore not visible.

Second, the simulated source produces radiation which does not scatter. This is not representative of a physical system, which predominantly suffers from Compton scatter in the medical imaging energy range [15]. Compton scatter is not only a source of noise, but can also cause artifacts in dense materials appearing as blurs in the image [14]. Because such effects do not dominate the final image, is was not considered for this thesis and its inclusion is recommended as future work.

#### 3.1.3. Voxel model

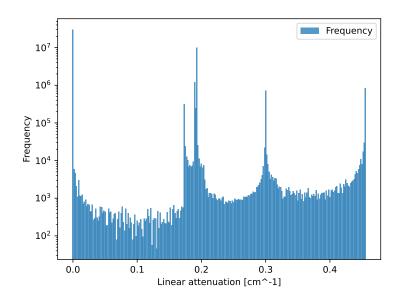

The model depicts the subject of the imaging process. In the simulation, the model consists of a large amount of voxels, also known as three-dimensional pixels, containing linear attenuation coefficients which describe how the X-ray intensity is reduced as rays move through the voxel. Throughout this thesis, a voxel model of a skull is used. This model is shown in Figure 3.3. The model is divided into layers which are traversed from the front to the back. This is shown in Figure 3.4. There are little restrictions on the size of the model. It can both be a cube or a rectangular cuboid. The only requirement is that all layers run parallel to each other. The skull model has a size of  $384 \times 297 \times 384$  voxels. The largest model which must be supported has a size of  $1024 \times 1024 \times 1024$  voxels. In case the model is larger than this, a slice can be created which fits within these dimensions. As long as the rays do not pass voxels outside of this slice, these voxels can safely be ignored. In case the source and detector move, the slice can be reconstructed.

The voxel values of the model represent linear attenuation coefficients. Initially, these coefficients

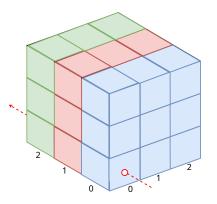

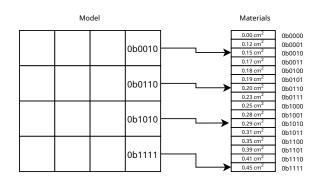

Figure 3.5: Example of the voxel model compression concept, adapted from [19]. Each voxel contains an index into a materials table, greatly reducing the memory footprint.

are represented using 32-bit floating point numbers making the range of possible values practically continuous. This is inconvenient for two reasons. First, floating point operation require a large area of dedicated hardware. Second, many voxels which are close to each other will have values in a similar range because they represent the same physical material like tissue or bone. If these sets of roughly equivalent voxels can be grouped, the memory footprint can be decreased if the groups can be referenced using a single number instead of 32 bits.

To implement this, the model is limited to 16 different material values. This limit means that a material can be referenced by a 4-bit integer acting as the index for a lookup table instead. This lookup table contains the actual linear attenuation coefficient represented using fixed point notation for efficient processing. An uncompressed model of 1024 x 1024 x 1024 voxels would require roughly 4.3 GB of storage. A model utilizing the compression trick only requires 536 MB of storage. The compression concept is illustrated in Figure 3.5.

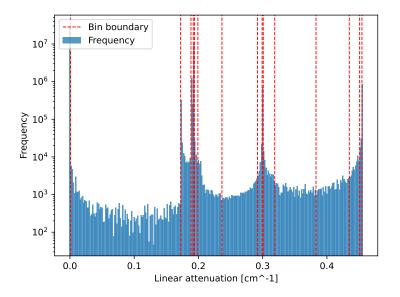

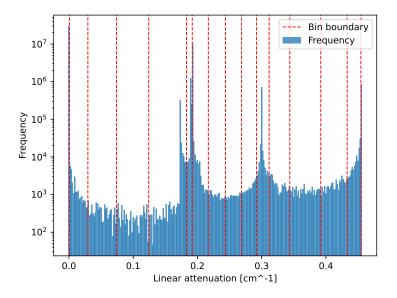

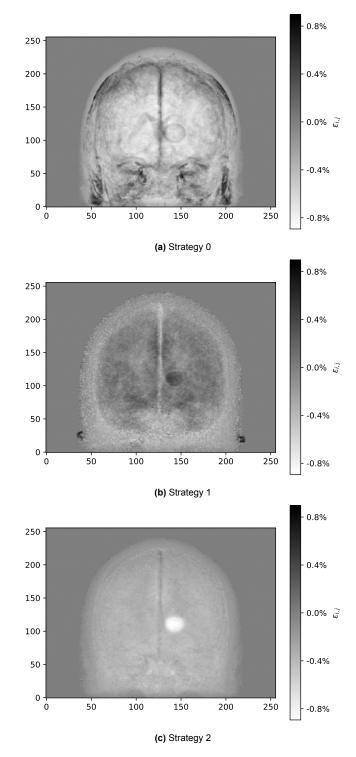

The compression of the model is a trade-off between processing speed and representation accuracy. The main advantage is a large reduction in memory bandwidth, enabling faster processing. However, averaging attenuation coefficients introduces some error compared to the original model. In Chapter 6, various strategies will be explored to minimize this error while maintaining performance. If the resulting error is deemed too large, future work could explore the impact of increasing the material count on image quality and system performance.

#### 3.1.4. Detector

The detector is the final component in the simulation. Its functionality is not modelled, but it is still an important part of our representation. This is because it plays a large part in the generation of the X-ray beam. The detector is treated as a rectangle for simplicity, but it does not need to be. Different shapes would work as well. The detector is based on the Allura Xper FD20, which has a size of 293.2 x 398.2 millimetres.

The detector is defined by a centre point and horizontal- and vertical spans. Based on this information, the detector corners can be accurately represented. The most significant parameter of the detector is its resolution, which directly influences the quality and computational complexity of the simulation. Each pixel in the detector corresponds to a single ray traced from the X-ray source, resulting in a computational complexity which is linear to the number of detector pixels.

#### 3.1.5. Computational model

At its core, the simulation is about calculating the intensity of a ray using the Lambert-Beer law stated in Equation 2.1. A line integral needs to be evaluated to determine the intensity. The voxel model is discrete, so the integral can be replaced by a simple summation:

$$I = I_0 e^{-\sum \mu_{x,y,z} \cdot l_{x,y,z}}$$

(3.1)

Figure 3.6: Overview of the 3 steps making up the algorithm, adapted from [19].

where  $\mu_{x,y,z}$  represents the linear attenuation coefficient of a specific voxel and  $l_{x,y,z}$  the length of the path through this voxel.

For the purpose of computational efficiency, only a single voxel per layer is considered. This voxel contains the longest path segment of the ray. The contribution of neighbouring voxels are ignored and the length of the ray through those voxels are added to the voxel under consideration. Thus, since the angle of a ray does not change as it moves through the model, for each particular ray its length through every intersected voxel is constant. Therefore, Equation 3.1 can be further simplified to include a constant length L, shown in Equation (3.2)

$$I = I_0 e^{-L \cdot \sum \mu_{x,y,z}} \tag{3.2}$$

Equation 3.2 shows that the intensity of a ray can be calculated if the scaled sum of linear attenuation coefficients is known. This is not a costly operation. The summation of the attenuation coefficients is the expensive part. The goal of the algorithm is therefore to compute this sum for every ray efficiently. The end result is a two-dimensional matrix containing the total linear attenuation for every ray, referred to as the attenuation map.

#### 3.2. Algorithm

This section explains the algorithm used to compute the attenuation map for a given voxel model and detector, outlining the steps involved in the process. The algorithm is structured into three steps: the projection step, the computation step, and the detector step. These steps are shown in Figure 3.6. The projection step focuses on projecting the detector onto the voxel model in order to determine the boundary of the beam. This boundary is used to calculate a grid of projection pixels which mark the entry points of the rays in the model. The computation step handles the propagation of the rays through the model, determining the cumulative linear attenuation on the projection plane. Finally, the detector step is responsible for transforming the attenuation map from the projection plane onto the detector.

#### 3.2.1. Projection step

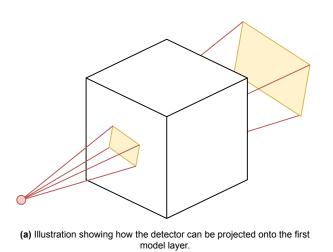

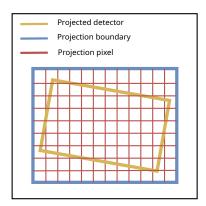

In the first step of the algorithm, the detector is projected onto the first model layer. This step is important because the projection confines the X-ray beam. Figure 3.7a shows a visualization of how the detector can be projected onto the first model layer.

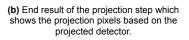

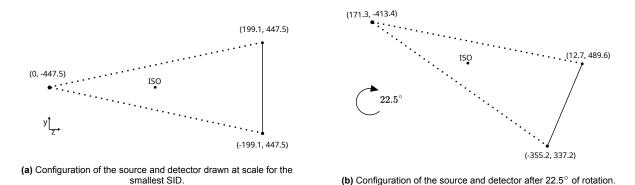

There are a couple of parameters that influence the size and shape of the projection. The first is the SID, which determines the size of the projection which is shown in figure 3.8a. The closer the detector is to the voxel model, the larger the projection will be for a given detector shape. The second parameter is the orientation of the source and detector. They are able to rotate around the ISO centre inside of the model. Rotation along either the X- or Y-axis influences the shape of the projection, as shown in figure 3.8b and figure 3.8c.

Figure 3.7: Illustration of projected detector and resulting projection grid.

Figure 3.8: Effects of distance and orientation of the detector on the projected projection.

Figure 3.9: Using simple trigonometry, a point can be projected on the first model layer based on the source and the detector.

Before the detector can be projected, the position of the source and the detector in three-dimensional space must be known. For the first image, this position is equal to the initial configuration. For the other images, the positions need to be adjusted according to the provided trajectory if present. In the case of translation, all relevant positions can simply be moved since they all move an equal amount. In the case of rotation, a few calculations are required to determine the new position.

Based on Euler's rotation theorem [20], an arbitrary three-dimensional rotation can be split up into three two-dimensional rotations. To achieve this, a standard rotation matrix described by [36] is used. This results in the following equations:

$$R_{x}(\theta) = \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} z \\ y \end{bmatrix}$$

$$R_{y}(\phi) = \begin{bmatrix} \cos(\phi) & -\sin(\phi) \\ \sin(\phi) & \cos(\phi) \end{bmatrix} \begin{bmatrix} x \\ z \end{bmatrix}$$

$$R_{z}(\psi) = \begin{bmatrix} \cos(\psi) & -\sin(\psi) \\ \sin(\psi) & \cos(\psi) \end{bmatrix} \begin{bmatrix} x \\ y \end{bmatrix}$$

(3.3)

Once the position is known, the detector can be projected onto the first layer. The equations shown in Equation 3.4 can be derived from the setup shown in Figure 3.9.

$$p_{x} = \frac{-s_{z}}{d_{z} - s_{z}} * (d_{x} - s_{x}) + s_{x}$$

$$p_{y} = \frac{-s_{z}}{d_{z} - s_{z}} * (d_{y} - s_{y}) + s_{y}$$

(3.4)

Once the detector has been projected a boundary can be constructed. This boundary covers the projection with some additional padding, which benefits the detector step. Within this boundary a grid can be constructed. This grid determines the entry points of the ray in the model. An example of this grid is shown in Figure 3.7b.

#### 3.2.2. Computation step

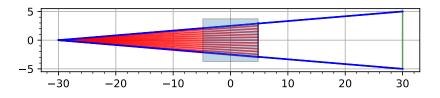

In the computation step the traversal of rays through the voxel model is simulated. The path of the rays is based on the result from the projection step. Equally spaced rays are generated with their entry points chosen at the centre of the projection pixels shown in Figure 3.7b. For every voxel intersected by a ray, the linear attenuation coefficient corresponding to this voxel is added to the sum of the previous layers. Figure 3.10 shows how a set of rays move through the centred model.

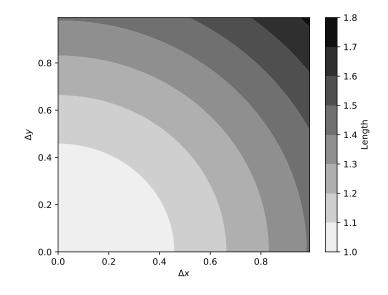

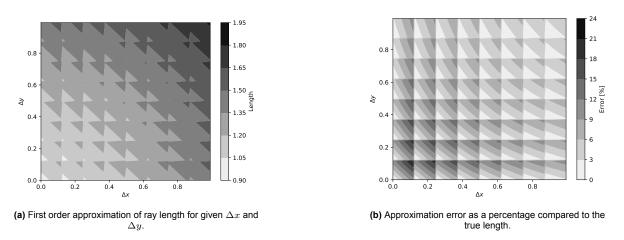

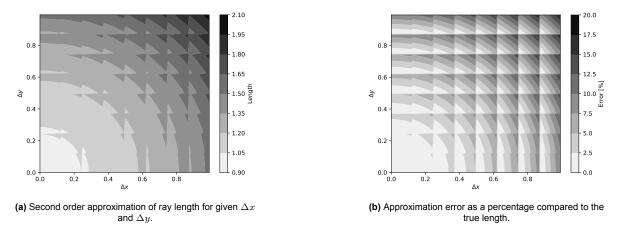

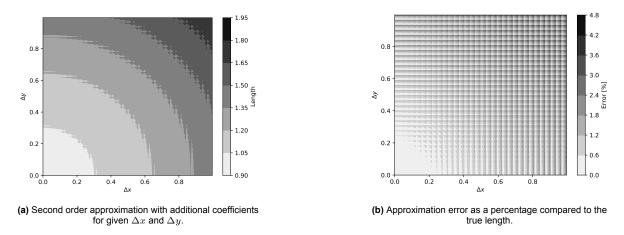

The attenuation coefficients provided by the model are based on a length of one unit, which would describe a path perpendicular to the xy voxel plane. Because the ray can move angulated against the voxel plane normal, the end result needs to be scaled according to the length of the ray in a voxel in accordance with Equation 3.2. Let  $\vec{R}(\alpha, \beta)$  be the path of a ray through a voxel in the z-direction, where  $\alpha$  and  $\beta$  describe the slope in the x- and y-direction respectively. The length of a segment is then equal to the magnitude of this vector, shown in Equation 3.5.  $\hat{x}$ ,  $\hat{y}$ , and  $\hat{z}$  are the unit vectors. An example of an attenuation map produced by the computation step can be seen in Figure 3.12.

Figure 3.10: Side view of a set of rays (red) as they move through a model (light blue), generated with code from [19].

Figure 3.11: Path which a ray traces through the model. In this illustration, one engine is responsible for two model layers. The yellow voxels represent intersected voxels. The blue voxel is not considered.

$$\overrightarrow{R}(\alpha,\beta) = \alpha \widehat{x} + \beta \widehat{y} + \widehat{z}$$

$$l = |\overrightarrow{R}(\alpha,\beta)| = \sqrt{\alpha^2 + \beta^2 + 1}$$

(3.5)

Many rays can be simulated in parallel through the use of compute engines. These engines, described in detail in Chapter 5, are responsible for contiguous model layers and compute the path and accumulated attenuation for a given ray. Figure 3.11 shows an example of the path of a ray through a voxel model. It is important to note that in this algorithm only a single voxel per layer is considered. This is a simplification however, because in reality up to three voxels can be crossed at a time in three-dimensional space. As a suggestion for future work, quantifying and possibly reducing the error caused by this simplification can be investigated.

#### 3.2.3. Detector step

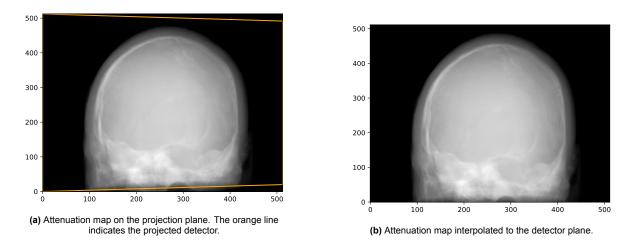

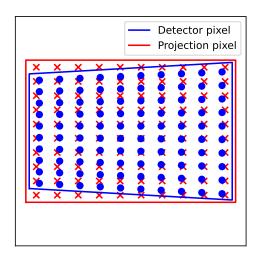

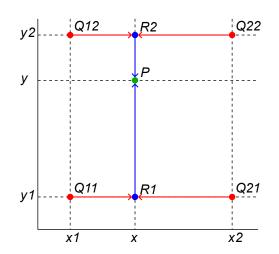

After the computation step, an attenuation map of the X-rays has been produced. This map is based on the projection plane, which is the exit plane of the final model layer. The rays are equally spaced in this plane. This is a result of the computation step. However, the detector pixels which detect the X-rays are not equally spaced. Their location can significantly differ from the projection pixels based on the amount of padding used to construct the boundary and rotation of the system. Figure 3.13a shows an example of an attenuation map for approximately 15 degrees of rotation around the y-axis. This map is in the projection plane. The orange line shows the border of the detector projected onto this plane. All detector pixels are within this boundary. To determine the attenuation registered by these pixels, they have to be interpolated based on the projection pixels. Section 5.5 will explain this process in more detail.

Using interpolation, intensities from one pixel grid are resized to another by estimating the intensities at the interpolated positions. Several algorithms are available to do this. In order to make a decision, three different algorithms will be explored. The three different algorithms are discussed in detail in Section 5.5.

Figure 3.12: Example of an attenuation map produced by the computation step.

Figure 3.13: Attenuation before and after the detector step, generated with approximately 15° of vertical rotation.

The first interpolation method is the nearest neighbour interpolation. Several variations of this algorithm exist. For this thesis the easiest variant will be considered, which simply finds the nearest pixel and assigns its value to the pixel to be interpolated. The second interpolation which will be studied is the bilinear interpolation. It is a well known extension of a linear approximation to two-dimensional space. Using this approach, an interpolated value is based on four points surrounding it. The third interpolation method which will be studied is the Lanczos interpolation. This technique is proven to work well in three-dimensional reconstruction in the context of medical volumes [22] and is based around the Lanczos kernel.

4

# System architecture

In this chapter, an overview of the system architecture will be provided, starting with a list of requirements that serve as the foundation for the design. Based on these requirements, a design is presented which is also motivated by the need for real-time behaviour.

#### 4.1. Requirements

As outlined in Chapter 1, the purpose of the simulator is to replicate the experience of a real imaging system, delivering realistic X-ray images. Ultimately, the goal is to generate image passable as real images at speeds on par with real imaging systems, providing a safe and effective alternative for machine testing and operator training. Based on this goal the following list of requirements can be established.

- 1. The hardware must target the Alveo U50 Data Accelerator card;

- 2. The simulator must support models up until a depth of 1024 voxels;

- 3. The simulator must support a resolution of at least 512 projection pixels;

- 4. The simulator must produce realistic results in the operating range of a real X-ray system;

- 5. The simulator must produce images at a speed of 60 images per second;

- 6. The accuracy of the implementation must be precise up to 1/16th of a projection pixel;

#### 4.2. System design

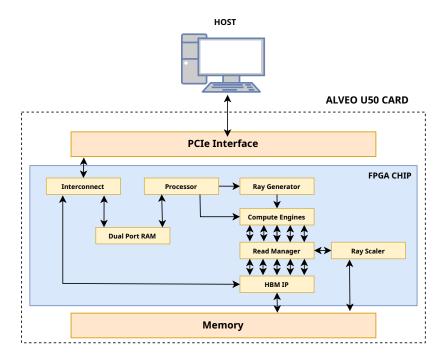

An overview of the main system components needed to meet the requirements and achieve real-time behaviour can be seen in Figure 4.1. The diagram specifies two independently operating regions. The host machine is connected to the X-ray system and accepts simulation parameters. The FPGA is connected to the host through the Peripheral Component Interconnect Express (PCIe) and computes the X-ray attenuation maps.

#### 4.2.1. Host machine

The host machine is a Linux PC which houses the FPGA and handles all forms of communication. Its main responsibility is supplying the FPGA with the correct simulation data. This data includes the following information:

- · The voxel model;

- The material values of the voxel model;

- The source position;

- The detector position and resolution;

- The trajectory describing the change in source-detector orientation and position.

Figure 4.1: Diagram showing the main components of the system. It shows how the host interfaces with the FPGA and how the components required to run the algorithm are interconnected.

The voxel model and material values need to be send ahead of time to the FPGA. The largest model has a compressed size of 536.9 MB. One model covers approximately 22.5 degrees of rotation in each direction. If this range is exceeded, the model needs to be recalculated in order to adjust the orientation such that the total rotation does not exceed the 22.5 degree limit. This can be done ahead of time. For every base model, the material values only need to be send once. The host must however make sure that each model is present on the FPGA ahead of time. The model data is stored in the memory of the Alveo U50 card. The material values are stored in Lookup Table Random Access Memory (LUTRAM) blocks within each engine, later referred to as the parameter RAM.

The other parameters are inputs which define the simulation configuration. The positions of the source and the detector determine the path the rays take through the model. The resolution of the detector defines the amount of rays which are simulated, which has a large impact on the image quality. The trajectory describes how the source-detector orientation changes between frames. These parameters only need to be send once to the FPGA, as long as the trajectory does not change and the source-detector orientation of the trajectory parameter means the simulation configuration can be updated on the FPGA. This decreases the amount of communication between the systems, which is necessary to achieve real-time behaviour. The input parameters are stored in Block RAM (BRAM) connected to a processor on the FPGA. Communication with the host is also supported through the BRAM.

#### Detector

The final stage of the X-ray image simulation algorithm involves transforming the produced attenuation map onto the detector. While the majority of the simulation is implemented on the FPGA, the detector step is performed on a PC. This stage begins by taking the output from the FPGA, an attenuation map, and interpolating it to account for distortions introduced by the projection onto the model.

Although this process could be implemented on an FPGA, it is not timing-critical and involves relatively few calculations, making it more practical to handle on a PC. Additionally, performing this step on a PC enables post-processing operations, such as filtering and upsampling, which can enhance image quality. This approach also provides flexibility for future extensions, such as integrating GPU-based processing to further accelerate or enhance the simulation pipeline.

#### 4.2.2. FPGA components

The FPGA handles the execution of the simulation. It should independently operate as a pipeline, requiring as little directions from the host machine as possible. To realize the algorithm outlined in Section 3.2 in hardware, the system shown in Figure 4.1 was created. The diagram shows the most important components and how they are connected.

As described in the previous section, the initial parameters and model data are send to the FPGA through a PCIe interface and the interconnect of the chip. The parameters are stored in memory blocks exposed to a micro controller. These blocks allow for bidirectional communication between the FPGA and the host, though this has not yet been realized for this project. The model data is stored in memory chips on the Alveo U50 card.

#### Processor

The first task of the FPGA is to project the detector onto the model. Because this step requires complex operations which are expensive to implement accurately in hardware like trigonometric functions, it is implemented using a MicroBlaze processor. The MicroBlaze is a 32-bit soft-core processor and has many different hardware configurations. It can be optimized for area or performance and can be configured to include additional hardware like fast multipliers. It can be programmed using C allowing a flexible implementation of the non-critical parts of our system. Once the micro controller has finished processing the initial parameters, its output is communicated to the rest of the system. For the ray generator component this includes the projection boundary which confines the rays. For the compute engines, this includes the material values stored in the parameter RAM and a line offset.

#### Ray generator

The ray generator is responsible for providing the input to the compute engines. It does this by calculating where a ray enters the model as well as how the position of a ray changes between model layers. This information is all the engines need to determine how the ray traverses the model.

#### **Compute engines**

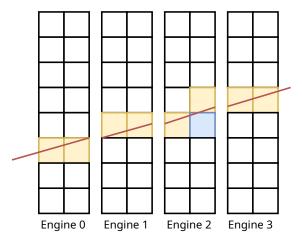

The compute engines play a crucial role in the system. They calculate the sum of attenuation coefficients for specified ray directions and positions and update the position of rays as they move through the model. Their functionality and implementation was first introduced in [19].

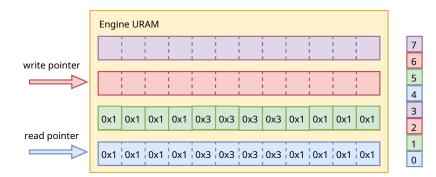

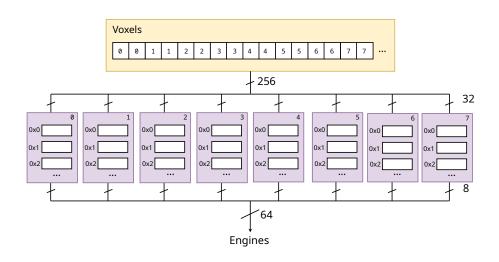

Each engine handles eight model layers. The engines form a chain. This means that the number of rays which can be processed concurrently is equal to the number of engines in the system. The engines requests voxel lines from memory in advance to accelerate processing. They operate in groups of sixteen. Within a group, the engines are connected to the same read manager. They must wait for their memory requests to be processed if other requests are handled first. This can potentially delay individual computations.

#### Ray scaler

The ray scaler handles the final step of the computational model explained in Section 3.1.5. This step includes properly scaling the computed attenuation according to the length of a ray segment. This is because the attenuation calculated by the engines assume a ray length of one unit. It is important that the ray scaler does not introduce any latency in the system, because every single ray must be processed by this component. Therefore, a fast implementation of this component is important.

#### 4.2.3. Memory components

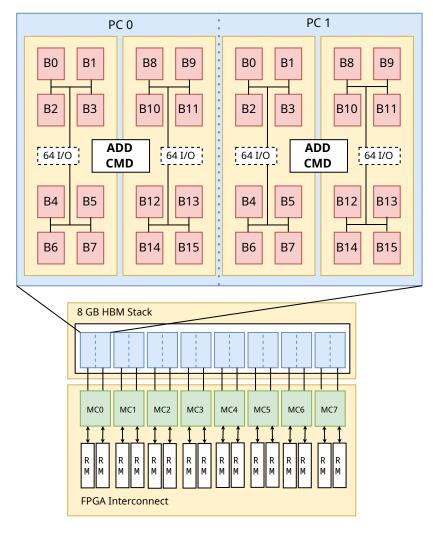

Earlier work focused on the Versal FPGA device, where memory bandwidth proved to be a significant bottleneck. Based on request and access times gathered through simulations, engines had to be run at half their possible speed in order to prevent delays. To address this issue, the Alveo U50 Data Accelerator card was considered due to its High Bandwidth Memory (HBM) architecture. This architecture is well-suited for the application, as it can handle large volumes of data in parallel, benefiting from the highly predictable access patterns of the processing engines.

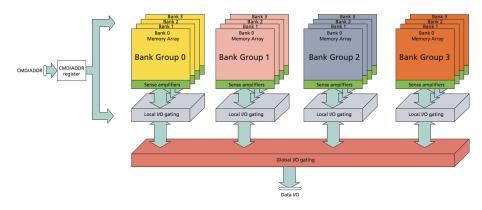

As shown in Figure 4.2, the Alveo U50 card features two 32 Gb HBM stacks, composed of DDR4 (Double Data Rate) memory chips. Each stack consists of sixteen pseudo channels, each with a dedicated memory interface and a capacity of 2 Gb. These channels can be accessed almost entirely in parallel,

| ++++++++++++++++++++++++++++++++++++++                 | MC_         MC_         MC_         MC_ | General Interconnec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  | ++++++<br>+++++++<br>MC_ MC_                      |                                        |

|--------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|----------------------------------------|

| 0 1 2<br>2 2 2 2 2<br>6 6 6 6 6<br>b b b b b b 3<br>32 | b b b b b b b                           | 7         0         1           2         2         2         2         2         2         2         2         2         2         2         2         2         2         5         6         G         G         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6         6 | 2 3<br>2 2 2 2<br>6 6 6 6<br>5 b b 5<br>32 Gb HB | 4 5<br>2 2 2 2 2<br>G G G G<br>b b b b<br>M Stack | 6 7<br>2 2 2 2 2<br>G G G G<br>b b b b |

Figure 4.2: Alveo U50 HBM two stack configuration [5]

Table 4.1: Summary of the amount of bits returned for a given model width.

| Model Width | Bits | 32-byte Bursts |

|-------------|------|----------------|

| 256         | 1024 | 4              |

| 384         | 1536 | 6              |

| 512         | 2048 | 8              |

| 1024        | 4096 | 16             |

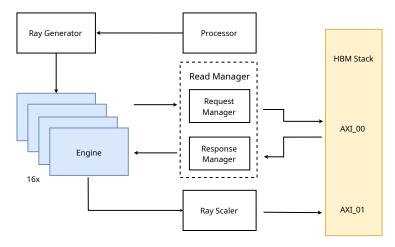

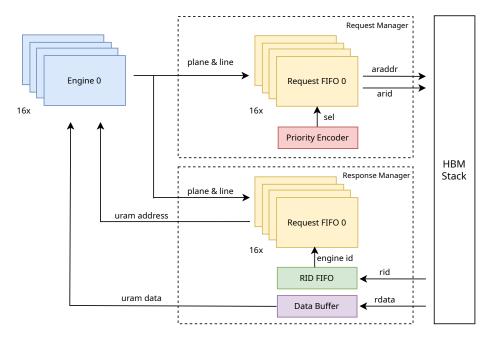

significantly improving data throughput. However, engines are not directly connected to the memory interface. Instead, a read manager is responsible for the retrieval of voxel lines requested by the engines, providing access to the corresponding pseudo channel.

#### Read manager

In software, the operating system is responsible for handling the memory management of an application. In an FPGA, this is the responsibility of the application itself. The read manager is therefore one of the most important components in the system. One read manager is responsible for serving voxel data to sixteen engines at most. It sits between the engines and the Alveo U50 memory.

Compute engines can request a model line with a single request. Memory is returned in bursts of 256 bits. The read managers must therefore be able to handle these bursts and return them in the correct order to the compute engines. Table 4.1 shows how many bits are returned per line for a given model width and the number of bursts during which this happens.

# 5

# System implementation

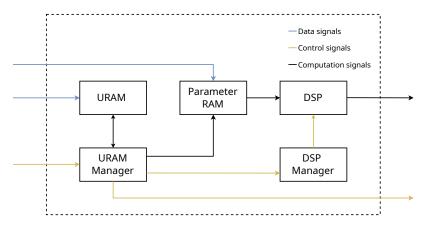

This chapter will discuss the implementation details of the system. Specifically, it will explain the hardware and software components required for the computation of an attenuation map. An overview of the hardware components and their connections are shown in Figure 5.1. The details of the read manager and memory are discussed in Chapter 6.

Figure 5.1: Functional diagram showing how the components discussed in this chapter are related. The number of components will vary depending on the model size.

#### 5.1. Processor

The purpose of the processor is to take the parameters supplied by the host machine and compute the input parameters for the simulation. It is implemented using the MicroBlaze Micro Controller System IP supplied by Xilinx. The MicroBlaze is a 32-bit Reduced Instruction Set (RISC) soft-core processor with a three-stage pipeline. It has an integrated IO module which can be used to communicate with the rest of the system.

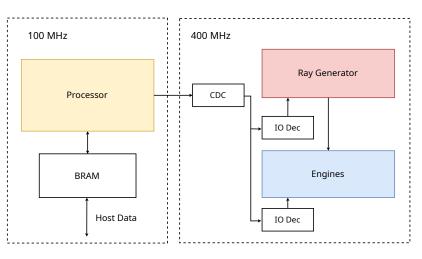

The MicroBlaze calculates a set of parameters used by the ray generator component to generate the rays. It calculates an initial vertical offset which describes the entry point of the first ray for the engines. Additionally, it sends the material coefficients used for the attenuation computations to the engines. The processor operates at 100 MHz. The other hardware components operate at 400 MHz. To prevent data hazards from interfering with the communication, clock domain crossing logic is required. This logic consists of double buffering the MicroBlaze IO bus and generating a simple ready-valid handshake in the corresponding clock domain using a pulse generator provided by Xilinx [6]. Figure 5.2 shows how the processor is connected to the other components.

| Task                                                   | Time                 |

|--------------------------------------------------------|----------------------|

| Precompute trigonometric values                        | <b>123</b> μs        |

| Update source and detector according to the trajectory | <b>239</b> <i>µs</i> |

| Project detector points onto the model                 | <b>178</b> μs        |

| Construct boundary used for ray generation parameters  | <b>3</b> μs          |

| Compute ray generation parameters                      | <b>59</b> µs         |

| Send ray generation parameters over IO bus             | <b>2</b> µs          |

| Calculate and send vertical offsets to engines         | <b>255</b> µs        |

| Total:                                                 | 859 $\mu s$          |

Table 5.1: Execution time of different parts of the algorithm running on the MicroBlaze.

Figure 5.2: Diagram showing how the processor is connected to the rest of the system.

#### Software

The software, implemented in C, must be fast due to its placement in the critical path. This is because the projection step of the algorithm described in Section 3.2 is executed for every image. The projection step can be executed in advance while the engines are handling the computation step. If the host parameters change however, the result will have to be recomputed. To determine the available time to run the code, consider the worst-case scenario where new parameters arrive just before the new frame is required. This means the processor and the engines have to complete their work within 16.5 ms in order to achieve the desired performance of 60 images per second. To provide the engines with a wide margin to complete their work, the processor should finish its part of the algorithm within 2 ms.

Execution begins with fetching parameters from the host. However, as host/FPGA communication has not yet been realized for this thesis, it is not discussed further. The execution times of the remaining operations for the projection step have been measured using simulation and are summarized in Table 5.1. Based on the total duration, completion within 2 ms is easily achieved. To ensure a fast execution time, the algorithm uses fixed point numbers for all computations. This speeds up the execution dramatically, since the processor does not have a Floating Point Unit (FPU) for the arithmetic. To determine the number of fractional bits required, the fixed point implementation was compared with a floating point implementation. The number of fractional bits was adjusted until the requirement of accuracy up to 1/16th the size of a projection pixel was met. In addition to the fixed point implementation, an approximation of the sine- and cosine function is also implemented in the software. The values are computed once and reused for each vector that needs to be rotated. The approximation was confirmed to meet the level of accuracy required.

#### 5.2. Ray generator

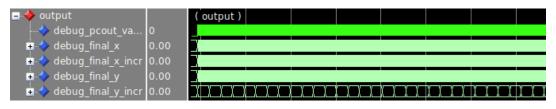

The ray generator component supplies the engines with data about the X-rays, including the x- and y-position within a model layer as well as their respective changes, known as the x- and y-increments.

To determine this for every ray, knowledge of the projected boundary as well as positional information from the processor is used.

It operates based on a state machine. When the reset signal drops, the ray generation component waits for the necessary parameters as mentioned in Section 5.1. It receives these parameters through an IO decoder attached to the IO bus of the processor. Once all parameters have been received, the IO status signal is asserted and rays can be generated.

#### X- and y-position

The rays are generated from the bottom-left to the top-right corner of the boundary. To compute the initial position of the ray, the  $x_{step}$  and  $y_{step}$  parameters are introduced. These parameters are equal to the width and height of a projection pixel respectively. They are computed by the processor and equal to the width or height of the boundary divided by the resolution in the same direction. The initial x- and y-position are calculated according to Equation (5.1), where  $x_{min}$  and  $y_{min}$  are the bottom-left corner of the boundary.

$$\begin{aligned} x &= x_{min} + 0.5 \cdot x_{step} \\ y &= y_{min} + 0.5 \cdot y_{step} \end{aligned} \tag{5.1}$$

For each additional ray the x-position is incremented by the  $x_{step}$  parameter as long as it is within the boundary. If the horizontal boundary is passed, the x-position is restored to the initial x-position and the y-position is incremented. If the vertical boundary is passed, all rays have been generated.

#### X- and y-increment

The x- and y-increment values, which describe how the x- and y-positions change as the rays move between layers, are calculated using a similar process. The initial increment values are however provided by the processor, since they require a division operation to calculate. All additional values are determined by adding an *increment\_step* value to the previous increment value. To proof that this is valid, consider two adjacent projection points on the xz-plane. The first x-increment value can trivially be calculated using Equation (5.2), where  $P_n$  and  $P_{n-1}$  are neighbouring projection points, S is the source, and  $D_{smd}$  is the source-model-distance.

$$P_{n-1}: x_{increment} = \frac{P_{n-1,x} - S_x}{D_{smd}}$$

(5.2)

If  $P_n$  is rewritten in terms of  $P_{n-1}$  it is shown that the increment value changes by a constant factor, which has previously been referred to as the *increment\_step*. This is shown in Equation (5.3). The same relation holds for the y-increment of a ray.

$$P_{n}: x_{increment} = \frac{P_{n,x} - S_{x}}{D_{smd}}$$

$$= \frac{P_{n-1,x} + x_{step} - S_{x}}{D_{smd}}$$

$$= \frac{P_{n-1,x} - S_{x}}{D_{smd}} + \frac{x_{step}}{D_{smd}}$$

(5.3)

#### 5.3. Engines

The compute engines, introduced in a different Master's thesis [19], are responsible for computing the path of X-rays through a model. An overview of the components within the engine can be seen in Figure 5.3. Most of the functional details of the compute engines will not be covered in this thesis. However, in the context of the entire system an understanding of its basic functionality is required. Figure 5.4 shows a diagram describing the simplified interface of a single engine.

Figure 5.3: Diagram showing the components which make up a compute engine [19]. The most important components are the URAM manager, which handles all control signals within the engine, and the DSP manager, which handles the control signals of the addition component.

Figure 5.4: Simplified diagram describing the interface of a compute engine.

#### 5.3.1. Computations

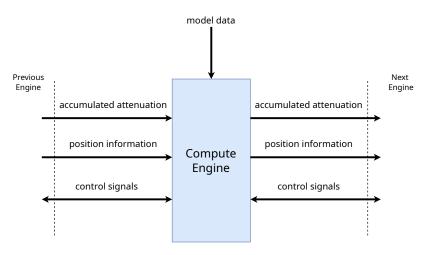

The compute engines are responsible for executing the computation step of the algorithm, as described in Section 3.2.2. The engines are connected in a chain, each responsible for calculating the path of a ray through eight model layers. The number of cascaded engines is therefore dependent on the depth of a model. A model with a depth of 256 layers requires 32 engines. The largest model supported has a depth of 1024 layers, which means 128 engines would be required. The three main pieces of information exchanged between engines are as follows:

- **Partial results:** Since the engines operate in a cascaded fashion, each engine takes the partial result of a previous engine and computes a new partial result which includes the eight layers it is responsible for.

- Position information: In order to determine the ray position within a layer, four values describing the position of a ray are shared between engines. These values include the x- and y-coordinate of a ray within a layer, as well as an x- and y-increment describing how the coordinate changes between layers. This logically means that the output position of a ray is equal to the sum of the input position and eight layer increments.

- **Control signals:** To facilitate the communication between engines some control signals are required. These signals describe when an engine is ready to receive data from the previous engine or to send it to the next one.

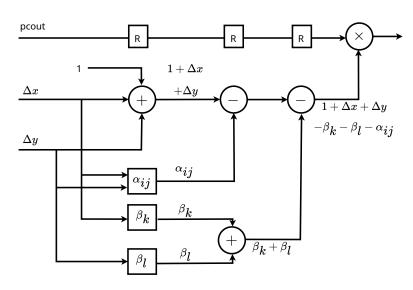

Figure 5.5: Implementation of the engine line buffers. The number in the boxes indicate the line numbers. The colour indicates the buffer a line is stored in.