# Thermal Management of High-Current Bidirectional Isolated DC-DC Converters

Yi Wang

# Thermal Management of High-Current Bidirectional Isolated DC-DC Converters

# **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. *ir. K.C.A.M Luyben,* voorzitter van het College voor Promoties, in het openbaar te verdedigen op 1 Mei, 2015 om 10:00 uur

door

# Yi WANG

Master of Science (Cum Laude), Delft University of Technology geboren te Xingtai, Hebei, China.

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. J. A. Ferreira

## Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. J. A. Ferreira Technische Universiteit Delft, promotor Ir. S. W. H. de Haan Technische Universiteit Delft, copromotor

## Independent Members:

Prof. dr. ir. R. W. De Doncker RWTH Aachen, Germany

Prof. dr. M. A. E. Andersen

Prof. dr. G. Q. Zhang

Assis. Prof. J. Popović-Gerber

Technical University of Denmark

EWI, Technische Universiteit Delft

EWI, Technische Universiteit Delft

Prof. dr. M. Zeman EWI, Technische Universiteit Delft, reservelid

This work was funded by the Quattro and Gen Power Box projects from Mastervolt company and SenterNovem, a research fund from Dutch Ministry of Economic Affairs.

ISBN: 978-94-6299-076-0

Printed by Ridderprint grafisch bedrijf, Ridderkerk, The Netherlands

Copyright © 2015 by Yi Wang All rights reserved

To my family

# ACKNOWLEDGMENTS

The research presented in this thesis was conducted at Delft University of Technology, the Netherlands, in the Electrical Power Processing (EPP) group headed by Professor Braham Ferreira. This is the place where I spent six memorable years towards my Master and Ph.D. degrees. Many people have been involved during this time and this thesis would not be completed without their valuable company, help, encouragement, and support. I would like to take this opportunity to thank those involved directly and indirectly.

First of all, I would like to thank my promoter Professor Ferreira, for giving me the opportunity to pursue both Master and Ph.D. degrees in his group and for his broad horizon, insightful guidance and brilliant ideas that inspire my Ph.D. work. After so many years I still remember clearly that it was to him that I made my first oral exam in English, and from that moment on, his support are always with me. I am deeply grateful to him. I would also like to express my sincere gratitude to Ir. Sjoerd W. H. de Haan, who is the weekly supervisor of my both Master and Ph.D. study. Thank him for so many interesting technical discussions and guidance, and for spending a large amount of precious time on editing and commenting my thesis. Only with his encouragement I could have made it this far.

The research presented in this thesis was sponsored by Quattro and Gen Power Box projects from Mastervolt company and SenterNovem, a research fund from Dutch Ministry of Economic Affairs. I would like to thank Mastervolt, especially its R&D manager Mr. Arno van Zwam, for giving the opportunity to do my master thesis in Mastervolt and for the numerous discussions during my Ph.D. work.

I would like to thank my Ph.D. committee members: Prof. R. De Doncker, Prof. M. Andersen, Prof. G. Q. Zhang, Assistant Prof. J. Popovic-Gerber and Prof. M. Zeman, for the time and effort they took to read my thesis and for their comments and suggestions.

In addition, I would like to thank my office roommate Dr. Bart Roodenburg, for your technical support in the first part of my Ph.D. work, and for so many helpful discussions about power electronics and the lifetime in Netherlands. Thanks for those years under the same roof.

Furthermore, I would like to acknowledge my colleagues in EPP groups. Thanks to Aleksander Borisavljevic, Anoop Jassal, Balazs Czech, Dalibor Cvoric, Doek-Je Bang, Dongsheng Zhao, Ghanshyam Shrestha, Gong Xun, Johan Wolmarans, Jianing Wang, Jinku Hu, Marcelo Gutierrez-Alcaraz, Milos Acanski, Ivan Josifovic, Hung Vu Xuan, Rodrigo

Teixeira Pinto, Samuel Ani, Wenbo Wang, Yi Zhou, Zhihui Yuan for so many enjoyable activities together.

I am also very grateful to my colleagues in Philips Lighting, Patrick Zijlstra, Waipang Chow, Marcel Beij and Luc Vogels, for translating the propositions into Dutch. Special thanks to my Master Shifu, Christiaan van Wijk, for translating the summary into Dutch and for so many insightful technical discussions about power electronics.

Last but most important, I would like to thank my family: my parents Zhimin Lin and Xilin Wang, my parents-in-law Bisheng Ren and Guibo Tang, for their unconditional love and encouragement. Most of all, I want to express my deepest and heartfelt gratitude to my beloved wife, Siyu Tang. Thank you for your understanding, support and sacrifice in so many weekends that I have to spend on my thesis. Without you, there is no color in my world. I love you!

# LIST OF SYMBOLS

| $\delta$                      | Vector angle between reactance and impedance of a capacitor                         | [rad]         |

|-------------------------------|-------------------------------------------------------------------------------------|---------------|

| $\delta$                      | Phase shift                                                                         | [rad]         |

| $\delta$                      | Skin depth                                                                          | [m]           |

| $\delta_{min}$                | Minimum phase shift                                                                 | [rad]         |

| $\delta_{max}$                | Maximum phase shift                                                                 | [rad]         |

| $\delta_{tri\_max}$           | Maximum phase shift in triangular modulation                                        | [rad]         |

| $\delta_{\textit{trap\_min}}$ | Minimum phase shift in trapezoidal modulation                                       | [rad]         |

| $\delta_{null}$               | Null time duration                                                                  | [rad]         |

| $\varepsilon$                 | Permittivity                                                                        | [F/m]         |

| η                             | System efficiency                                                                   | [%]           |

| $\sigma$                      | Electrical conductivity                                                             | [S/m]         |

| $\mu_n$                       | Electron mobility                                                                   | $[m^2/(V s)]$ |

| ho                            | Electrical resistivity                                                              | $[\Omega m]$  |

| $\Delta B$                    | Flux density peak-to-peak value                                                     | [T]           |

| $\Delta I$                    | Magnitude of current ripple                                                         | [A]           |

| a                             | Steinmetz constant                                                                  |               |

| $a_f$                         | Fill factor                                                                         |               |

| $A_c$                         | Core cross-section area                                                             | $[m^2]$       |

| $A_{cu}$                      | Copper area                                                                         | $[m^2]$       |

| $A_{drift}$                   | Area of the drift region in a semiconductor                                         | $[m^2]$       |

| $A_w$                         | Winding window area                                                                 | $[m^2]$       |

| b                             | Steinmetz constant                                                                  |               |

| $B_{pk}$                      | Peak flux density                                                                   | [T]           |

| $C_d$                         | Core depth                                                                          | [m]           |

| $C_{in}$                      | Input capacitors                                                                    | [F]           |

| $C_m$                         | Steinmetz constant                                                                  |               |

| $C_n$                         | Material-related constant of core hysteresis loss                                   |               |

| d                             | Ratio between the input voltage and referred output voltage $V_{\text{o}}^{\prime}$ |               |

|                               |                                                                                     |               |

| D                 | Duty Ratio                                                          |           |

|-------------------|---------------------------------------------------------------------|-----------|

| $D_c$             | Ratio between the conduction time and the switching period          |           |

| $D_o$             | Duty Ratio                                                          |           |

| $E_c$             | Field breakdown strength of a semiconductor material                | [V/m]     |

| $f_r$             | Resonant frequency                                                  | [Hz]      |

| $f_{sw}$          | Switching frequency                                                 | [Hz]      |

| $F_{prx}$         | Normalized skin-effect loss factor                                  |           |

| $F_{sk}$          | Normalized proximity-effect loss factor                             |           |

| h                 | Height of the secondary winding of transformer                      | [m]       |

| $I_{AVG}$         | Average Current                                                     | [A]       |

| $I_{eq\_35\mu m}$ | Equivalent current in 35μ m thick PCB trace                         | [A]       |

| $I_{rms}$         | Root-mean-square value of a current                                 | [A]       |

| $I_f$             | Forward flowing current                                             | [A]       |

| $i_{pri}$         | Current in the primary winding                                      | [A]       |

| $I_{rr}$          | Peak of the reverse recovery current                                | [A]       |

| J                 | Current density                                                     | $[A/m^2]$ |

| $k_{ce}$          | Material- and waveform-related constant of classical eddy current   |           |

| _                 | loss                                                                |           |

| $k_{ex}$          | Material- and waveform-related constant of excess eddy current loss |           |

| $k_h$             | Material-related constant of core hysteresis loss                   |           |

| $K_{rr}$          | Material-related constant of diode reverse recovery loss            |           |

| $L_{bst}$         | Inductor in a boost converter                                       | [H]       |

| $L_{lk}$          | Leakage inductance                                                  | [H]       |

| $L_r$             | Resonant inductor                                                   | [H]       |

| M                 | Number of winding layers                                            |           |

| M                 | Distance from trace left/right edge to board left/right edge        | [m]       |

| N                 | Number of turns per winding layer                                   |           |

| N                 | Transformer turns ratio                                             |           |

| $N_t$             | Number of winding turns                                             |           |

| $N_{sw}$          | Number of semiconductors in parallel                                |           |

| $N_u$             | Number of identical converter units in parallel                     |           |

| $P_b$               | Base power in the per-unit system                          | [W]        |

|---------------------|------------------------------------------------------------|------------|

| $P_{cap}$           | Capacitor loss                                             | [W]        |

| $P_{ce}$            | Classical eddy current loss                                | [W]        |

| $P_{cond}$          | Conduction loss                                            | [W]        |

| $P_{dr}$            | Loss in semiconductor driver                               | [W]        |

| $P_{ex}$            | Excess eddy current loss                                   | [W]        |

| $P_h$               | Hysteresis loss in magnetic cores                          | [W]        |

| $P_{layer}$         | Power loss in each layer                                   | [W]        |

| $P_{max}$           | Maximum power                                              | [W]        |

| $P_{mag}$           | Loss in magnetic components                                | [W]        |

| $P_o$               | Output power                                               | [W]        |

| $P_{on}$            | Turn-on loss                                               | [W]        |

| $P_{o\!f\!f}$       | Turn-off loss                                              | [W]        |

| $P_{rec\_max\_pu}$  | Maximum power of rectangular modulation in per-unit system | [W]        |

| $P_{rr}$            | Diode reverse recovery loss                                | [W]        |

| $P_{prx}$           | Winding loss due to proximity effect                       | [W]        |

| $P_{semi}$          | Semiconductor loss                                         | [W]        |

| $P_{sw}$            | Switching loss                                             | [W]        |

| $P_{sk}$            | Winding loss due to skin effect                            | [W]        |

| $P_{trap\_max}$     | Maximum power of trapezoidal modulation                    | [W]        |

| $P_{trap\_max\_pu}$ | Maximum power of trapezoidal modulation in per-unit system | [W]        |

| $P_{trap\_min}$     | Minimum power of trapezoidal modulation                    | [W]        |

| $P_{trap\_min\_pu}$ | Minimum power of trapezoidal modulation in per-unit system | [W]        |

| $P_{tri}$           | Power transferred by triangular modulation                 | [W]        |

| $P_{tri\_max}$      | Maximum power of triangular modulation                     | [W]        |

| $P_{tri\_max\_pu}$  | Maximum power of triangular modulation in per-unit system  | [W]        |

| $P_w$               | Winding loss                                               | [W]        |

| $Q_{g.tot}$         | Gate charge of a MOSFET                                    | [C]        |

| $Q_{rr}$            | Reverse recovery charge                                    | [C]        |

| $R_{ac}$            | AC resistance                                              | $[\Omega]$ |

| $R_c$               | Resistor representing the magnetic core loss               | $[\Omega]$ |

| $R_d$               | Diode on-state resistance                                  | $[\Omega]$ |

|                     |                                                            |            |

| $R_{dc}$        | DC resistance                                                    | $[\Omega]$ |

|-----------------|------------------------------------------------------------------|------------|

| $R_{ESR}$       | Equivalent series resistor                                       | $[\Omega]$ |

| $R_{fuse}$      | Fuse resistance                                                  | $[\Omega]$ |

| $R_g$           | Gate drive resistor                                              | $[\Omega]$ |

| $R_{lk}$        | Leakage resistance                                               | $[\Omega]$ |

| $R_{on}$        | On-state resistance                                              | $[\Omega]$ |

| $R_{on.sp}$     | Specific on-resistance                                           | $[\Omega]$ |

| $R_{rr}$        | Resistor representing the reverse recovery loss of power diodes  | $[\Omega]$ |

| $R_p$           | Winding resistance due to the proximity effect                   | $[\Omega]$ |

| $R_s$           | Winding resistance due to the skin effect                        | $[\Omega]$ |

| $R_{shunt}$     | Shunt resistance                                                 | $[\Omega]$ |

| $R_{sw}$        | Resistor representing the switching loss of power semiconductors | $[\Omega]$ |

| $R_{th.j\_PCB}$ | Thermal resistance from junction to PCB                          | [K/W]      |

| $R_{th\_jc}$    | Thermal resistance from junction to case                         | [K/W]      |

| $R_{th.j\_top}$ | Thermal resistance from junction to case top                     | [K/W]      |

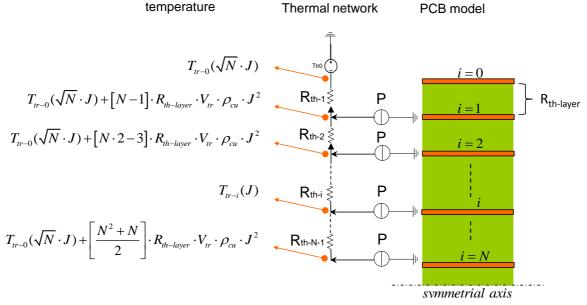

| $R_{th\_layer}$ | Thermal resistance of each lamination layer                      | [K/W]      |

| $S_{mod}$       | Modulation method                                                |            |

| $t_{null}$      | Null time duration                                               | [s]        |

| $t_{on}$        | Turning-on time interval                                         | [s]        |

| $t_{off}$       | Turning-off time interval                                        | [s]        |

| $T$ , $T_{sw}$  | Switching period                                                 | [s]        |

| $T_c$           | Case temperature                                                 | [°C]       |

| $T_{hs}$        | Heatsink temperature                                             | [°C]       |

| $t_{rr}$        | Reverse recovery time                                            | [s]        |

| $t_s$           | Excitation time                                                  | [s]        |

| $V_b$           | Base voltage in the per-unit system                              | [V]        |

| $V_{BD}$        | breakdown voltage                                                | [V]        |

| $V_c$           | Core volume                                                      | $[m^3]$    |

| $V_f$           | Diode forward voltage                                            | [V]        |

| $V_g$           | Drive voltage of a MOSFET                                        | [V]        |

| $V_{in}$        | Input voltage                                                    | [V]        |

| $V_i$           | Input voltage                                                    | [V]        |

|                 |                                                                  |            |

| $v_p$     | Voltage across the primary winding                             | [V]     |  |

|-----------|----------------------------------------------------------------|---------|--|

| $V_{RBD}$ | Diode reverse breakdown voltage                                | [V]     |  |

| $V_{tr}$  | Volume of each copper layer                                    | $[m^3]$ |  |

| $V_o$     | Output voltage                                                 | [V]     |  |

| $V_o{'}$  | Output voltage referred to the primary side of the transformer | [V]     |  |

| W         | Width of the secondary winding of transformer                  | [m]     |  |

| $W_W$     | Winding window width                                           | [m]     |  |

# **ACRONYMS**

1D One-Dimensional

2D Two-Dimensional

3D Three-Dimensional

AC Alternating current

CCC Current-carrying capacity

CCM Continuous conduction mode

DAB Dual active bridge

DAB-FB Dual active bridge - full bridge

DC Direct current

DCM Discontinuous conduction mode

DF Dissipation Factor

DFPR Die free package resistance

DHB-SC Dual half bridge with split capacitors

DSCC Double-sided collective cooling

EMI Electromagnetic interference

ESR Equivalent series resistance

GaN Gallium nitride

GSE Generalized Steinmetz equation

HC High current

HF High efficiency

HPD High power density

HV High voltage

iGSE Improved generalized Steinmetz equation

i<sup>2</sup>GSE Improved improved generalized Steinmetz equation

IGBT Insulated-gate bipolar transistor

KPI Key Performance Index

LV Low voltage

LQC Load resonant converter

MOSFET Metal oxide semiconductor field-effect transistor

MLCC Multi-layer ceramic capacitors

MLT Mean-length-per-turn

MSE Modified Steinmetz equation

PCB Printed circuit board

PCRC Parallel connected resonant converter

PD Power density

PE Power electronic(s)

PRC Partially Resonant Converter

PWM Pulse-wide-modulation

QRC Quasi-resonant converter

RMS Root mean square

SBD Schottky barrier diode

SE Steinmetz equation

SiC Silicon carbide

SCRC Series-connected resonant converter

TM Thermal management

VA Voltage-ampere

WBG Wide band gap

ZCS Zero-current switching

ZVS Zero-voltage switching

ZVZCS Zero-voltage and zero-current switching

# TABLE OF CONTENTS

| Chapte | r 1 Introduction                                          | 1  |  |

|--------|-----------------------------------------------------------|----|--|

| 1.1    | Development of Power Electronics (PE)                     | 1  |  |

| 1.2    | High-Current Isolated DC-DC Converters                    |    |  |

| 1.3    | Problem Description                                       | 5  |  |

| 1.4    | Objective and Approaches                                  | 7  |  |

| 1.5    | Thesis Layout                                             |    |  |

| 1.6    | References                                                | 9  |  |

| Chapte | r 2 Losses in PE Converters                               | 11 |  |

| 2.1    | Introduction                                              | 11 |  |

| 2.2    | Component Losses                                          | 12 |  |

| 2.2    | 2.1 Power Semiconductor Loss                              | 14 |  |

| 2.2    | 2.2 Power Diode Losses                                    | 16 |  |

| 2.2    | 2.3 Magnetic Components                                   | 17 |  |

| 2.2    | 2.4 Other Losses                                          | 22 |  |

| 2.3    | Loss Reduction Methods                                    | 23 |  |

| 2.3    | 3.1 Loss Reduction in Power Transistors                   | 23 |  |

| 2.3    | 3.2 Loss Reduction in Power Diodes                        | 30 |  |

| 2.3    | 3.3 Loss Reduction in Magnetic Components                 | 31 |  |

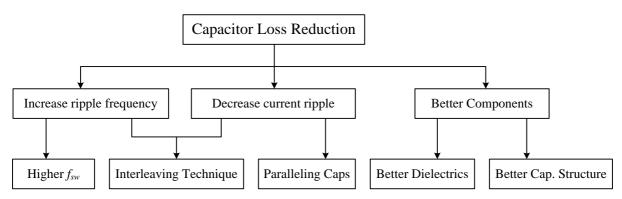

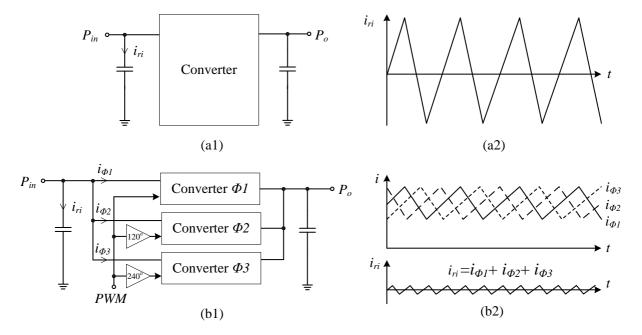

| 2.3    | 3.4 Loss Reduction in Capacitors                          | 32 |  |

| 2.4    | Conclusions                                               | 34 |  |

| 2.5    | References                                                | 35 |  |

| Chapte | er 3 High-Current Bidirectional Isolated DC-DC Topologies | 41 |  |

| 3.1    | Introduction                                              | 41 |  |

| 3.2    | Topology Review and Evaluation                            | 42 |  |

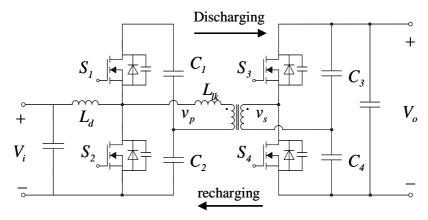

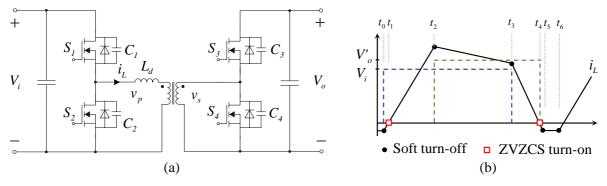

| 3.2    | 2.1 Flyback-Derived Converters                            | 42 |  |

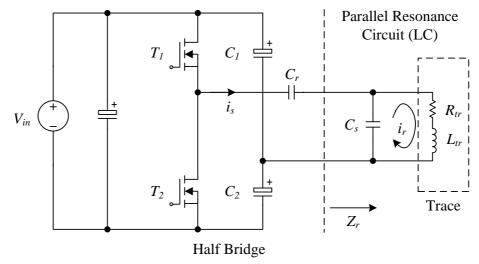

| 3.2    | 2.2 Half-bridge-based Converters                          | 43 |  |

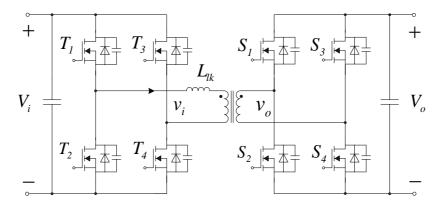

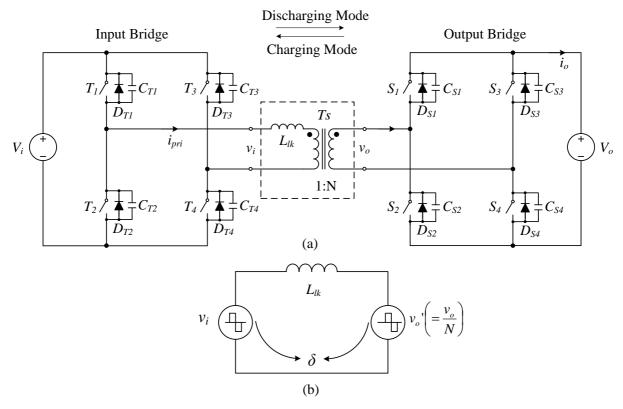

| 3.2    | 2.3 Full-bridge-based Converters                          | 45 |  |

| 3.2    | 2.4 Summary                                               | 46 |  |

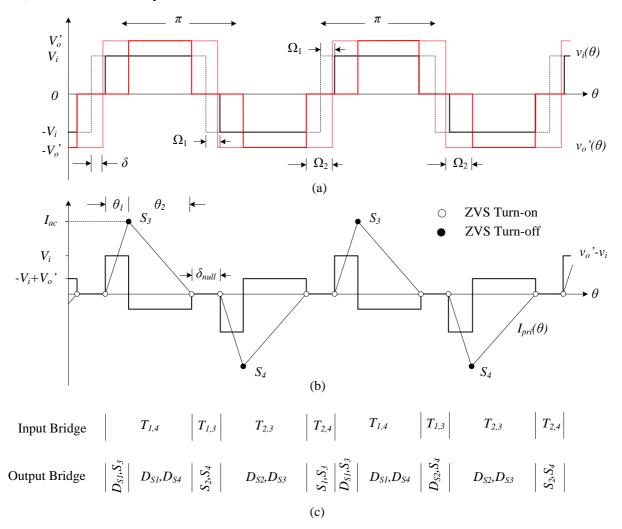

| 3.3    | Three Typical Modulations of Full-Bridge DAB              | 47 |  |

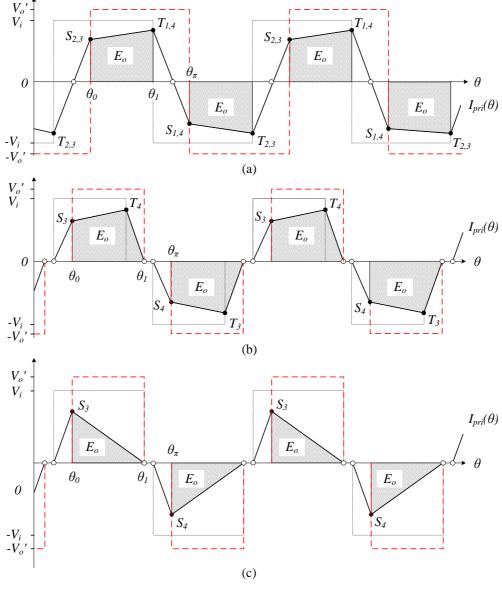

| 3.3    | Rectangular (Phase-shift) Modulation                      | 48 |  |

| 3.3    | 3.2 Trapezoidal Modulation                                | 52 |  |

| 3.3    | 3.3 Triangular Modulation                                 | 56 |  |

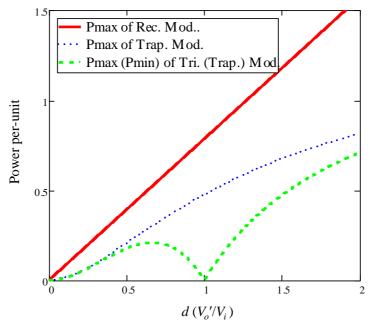

| 3.     | 3.4 Comparison of three DAB modulation methods             | 57     |

|--------|------------------------------------------------------------|--------|

| 3.4    | Conclusions                                                | 60     |

| 3.5    | References                                                 | 60     |

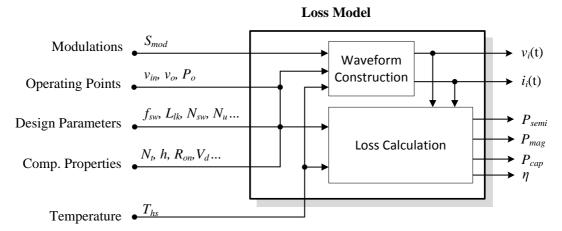

| Chapte | er 4 Loss Modeling of High-Current Converters              | 63     |

| 4.1    | Introduction                                               | 63     |

| 4.2    | Loss Modeling Approach                                     | 64     |

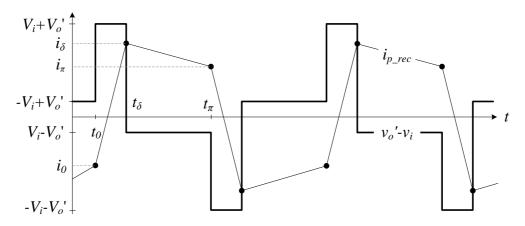

| 4.3    | Waveform Construction                                      | 66     |

| 4.     | 3.1 Ideal Waveform Construction                            | 66     |

| 4.     | 3.2 Inclusion of Non-Ideal Factors                         | 68     |

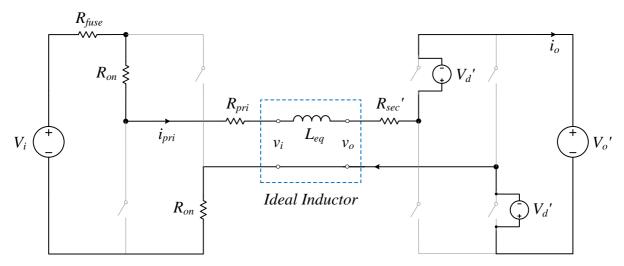

| 4.4    | Loss Calculation                                           | 69     |

| 4.     | 4.1 Modeling of Critical Resistances                       | 70     |

| 4.5    | Model Verification                                         | 75     |

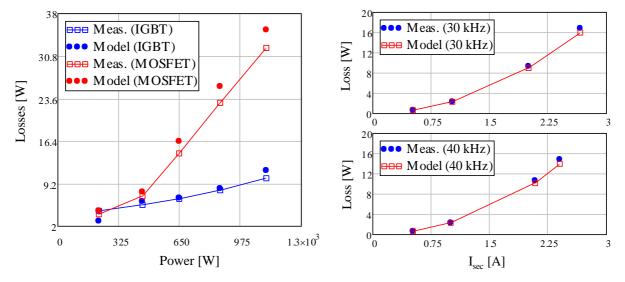

| 4.     | 5.1 Semiconductor Losses                                   | 75     |

| 4.     | 5.2 Transformer Losses                                     | 76     |

| 4.     | 5.3 Model Verification of a 1 kW DAB Converter             | 78     |

| 4.6    | Conclusions                                                | 81     |

| 4.7    | References                                                 | 81     |

| Chant  | er 5 High-Current Planar Transformer Design                | 92     |

| Спари  | er 3 mgn-current ranar Transformer Design                  |        |

| 5.1    | Introduction                                               | 83     |

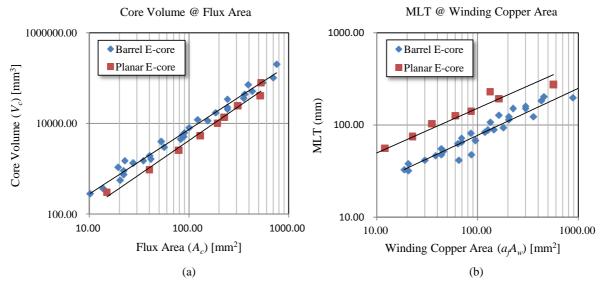

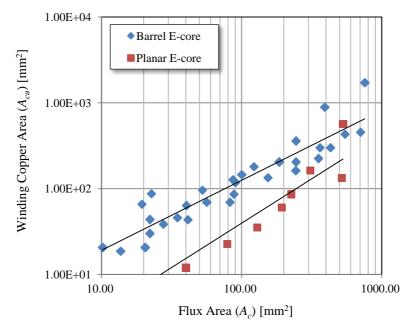

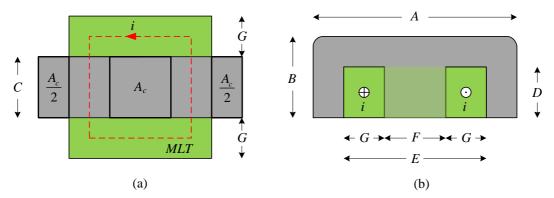

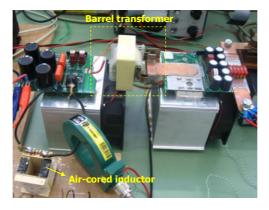

| 5.2    | Planar vs. Barrel Transformers                             | 85     |

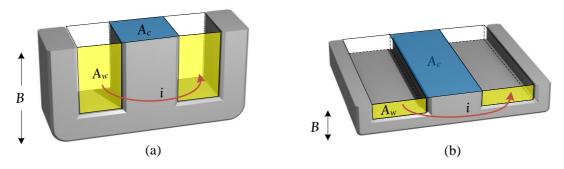

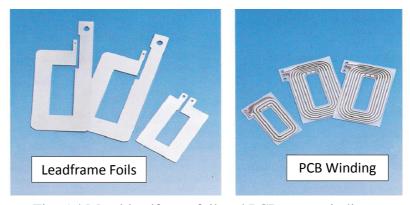

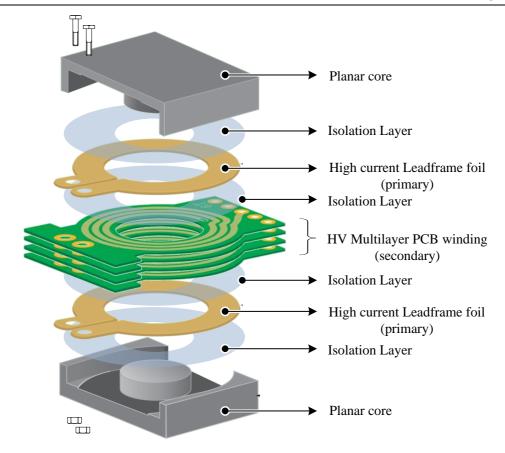

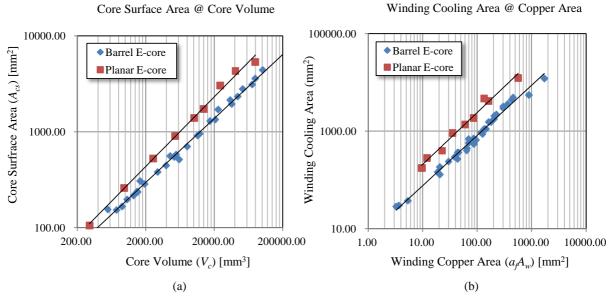

| 5.     | 2.1 Core and Winding Structures                            | 86     |

| 5.     | 2.2 Heat Generation                                        | 87     |

| 5.     | 2.3 Heat Removal                                           | 89     |

| 5.3    | Single-Turn Planar Transformer Design                      | 91     |

| 5.     | 3.1 Sing-Turn High-Current (HC) Winding                    | 91     |

| 5.     | 3.2 Single-Turn Interleaving Techniques                    | 93     |

| 5.     | 3.3 Evaluation of Three Single-Turn Transformers           | 95     |

| 5.     | 3.4 Leakage Inductance Tuning                              | 100    |

| 5.     | 3.5 Summary                                                | 102    |

| 5.4    | Nanocrystalline Planar Transformer Design Optimization     | 102    |

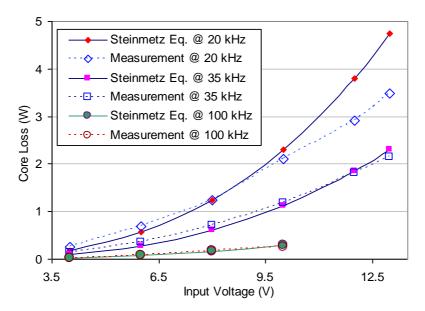

| 5.     | 4.1 Ferrite vs Nanocrystalline Cores                       | 103    |

| 5.     | 4.2 Key Transformer Parameters Selection                   | 104    |

| 5.     | 4.3 Optimal Core Dimension Design                          | 109    |

| 5.     | 4.4 Leakage Inductance Tuning                              | 111    |

| 5.     | 4.5 Nanocrystalline vs. Ferrite Transformer Comparisons    | 112    |

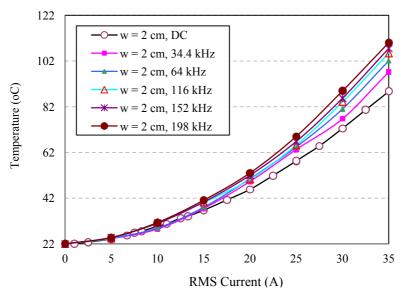

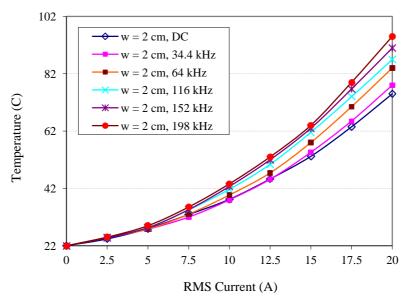

| 5.5    | Thermal Design Guideline of PCB traces under DC & AC Curre | ent115 |

| 5.5       | .1 Heat Conduction on Varied PCB Structures               | 116 |

|-----------|-----------------------------------------------------------|-----|

| 5.5       | .2 CCC of Wide PCB Traces                                 | 120 |

| 5.5       | .3 Discussions                                            | 129 |

| 5.6       | Conclusions                                               | 130 |

| 5.7       | References                                                | 130 |

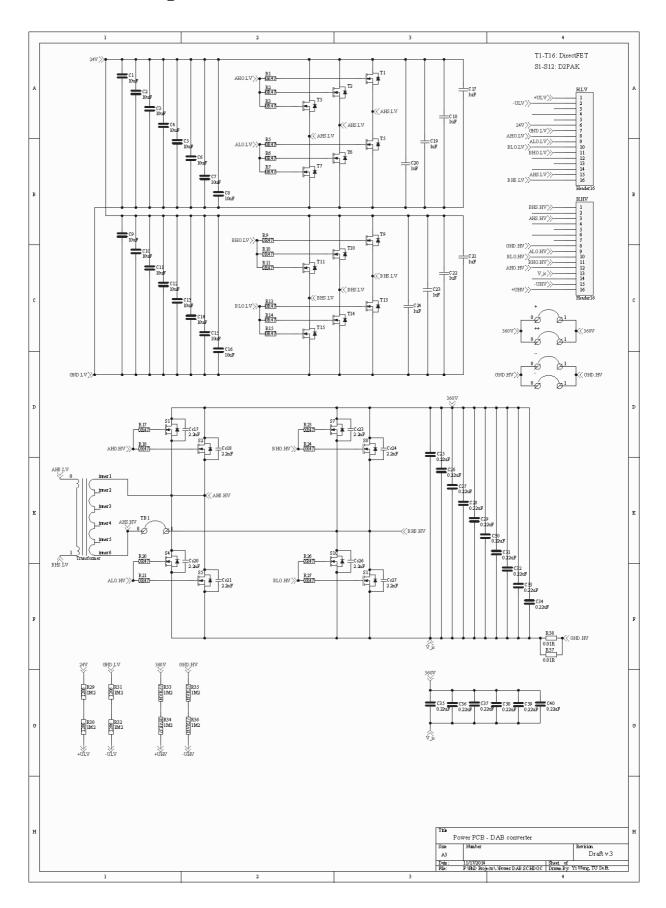

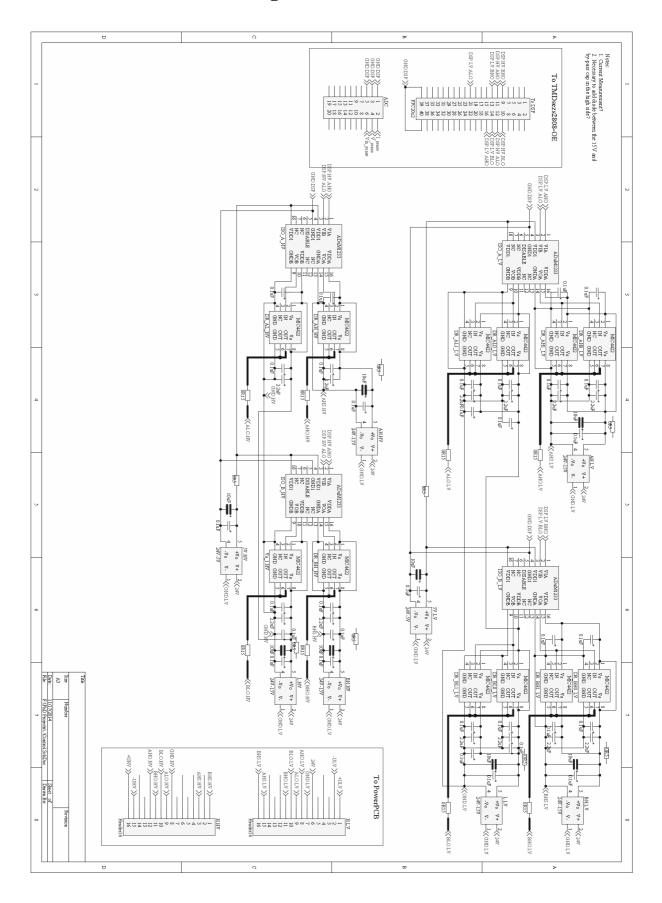

| Chapte    | r 6 Collective Cooling Strategy for Planar DAB Converters | 133 |

| 6.1       | Introduction                                              | 133 |

| 6.2       | Low-Profile Components and Their Heat Interface Design    | 136 |

| 6.2       | .1 Power Semiconductors                                   | 136 |

| 6.2       | .2 Magnetic Components                                    | 139 |

| 6.3       | Collective Cooling Strategy                               | 141 |

| 6.3       | .1 Concept                                                | 142 |

| 6.3       | .2 Experimental Demonstration                             | 143 |

| 6.4       | Double-Sided Collective Cooling (DSCC) Design             | 145 |

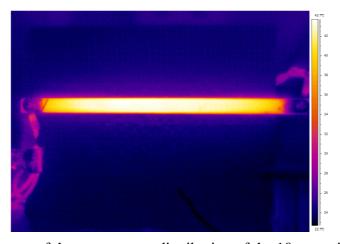

| 6.4       | .1 Heat Generation Management                             | 147 |

| 6.4       | .2 Heat Removal Management                                | 150 |

| 6.4       | .3 Thermal Simulation                                     | 155 |

| 6.4       | .4 Discussions                                            | 160 |

| 6.5       | Conclusions                                               | 161 |

| 6.6       | References                                                | 162 |

| Chapte    | r 7 Conclusions and Recommendations                       | 165 |

| 7.1       | Conclusions                                               | 165 |

| 7.2       | Recommendations                                           |     |

| Append    | lix A                                                     | 171 |

| Append    | lix B                                                     | 175 |

| Append    | lix C                                                     | 183 |

| Summa     | ry                                                        | 187 |

| Samenv    | vatting                                                   | 191 |

| List of 1 | Publications                                              | 195 |

|           | ılum Vitae                                                |     |

# Chapter 1

# Introduction

Onventional "Thermal Management" (TM) indicates various cooling techniques [1-1]. The goal of TM is to facilitate components operating at or below their maximum operating temperature while enhancing electronic designs that achieve all of the physical, electrical, thermal, and reliability requirements of the end products. In a power electronic converter with High-Power-Density (HPD), loss density in power components tends to increase due to a more compact component and system volume. The traditional thermal management approach would not be adequate for handling the thermal stress caused by the increased loss density within a limited space. The major contribution of this work is to investigate an extended thermal management approach to effectively managing heat generation and heat removal in PE converters in order to realize HPD. More specifically, this research will concentrate on the high-current bidirectional isolated DC-DC converters deployed in private marine vehicle applications where space is limited. To assist readers to better understand this work, this chapter introduces the related research background, problem statement, and thesis layout.

# 1.1 Development of Power Electronics (PE)

PE is an application of solid-state electronics for controlling and converting electrical power with assistance of electronic switching devices [1-2][1-3]. Until now, the development of PE has been driven by both technology push and application pull.

During the 1960s, breakthroughs in power semiconductor technology dramatically improved the voltage- and current- handling capabilities and switching speeds of electronic switching devices [1-4]. This allowed PE to flourish in a broad range of residential, industrial, and military applications such as traction and automotive, heating, lighting, information and telecommunication. Consequently, the continuous advance in technical fields of semiconductor wafer manufacturing, microprocessor design, packaging, and material has promoted PE to a more mature stage.

In addition to technology development, the needs in a wide range of applications have also significantly stimulated the advancement of PE. Some applications demand power supplies

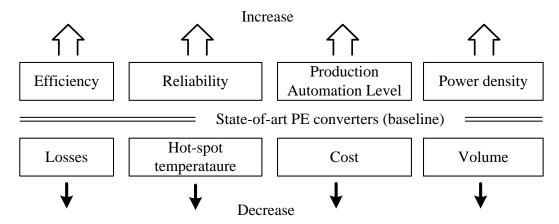

Fig. 1.1 Trends of PE converter requirements

with improved performance. Take power supplies for digital processors for example, the voltage level of microprocessors continuously decreases in response to the trend of smaller size, greater power, and higher transistor density [1-5]. Therefore, their power supplies must have increased stable output voltage and faster dynamic response. Some applications, such as the (hybrid) electric car [1-6] and solid-state lighting [1-7], require more efficient usage of energy where PE converters are employed to drive the loads and control the power flow. In recent decades, the utilization of renewable energy such as solar and wind power has been emphasized due to the depletion of fossil energy sources and the issues concerning the everdeteriorating environment. As an important technical approach to the conversion and delivery of renewable energy [1-8], PE plays a vital role in the energy harvest industry.

Generally speaking, advancements of PE systems are stimulated by following application requirements: higher energy efficiency, better reliability, higher production automation level, and larger power density (Fig. 1.1).

Higher energy efficiency is a direct result of the generation of lower losses which is not only a response to the energy-saving appeal but also influences whether other requirements such as reliability and power density can be successfully fulfilled. Greater reliability requires the hotspot temperature in the system to be lower since the temperature-dependent failure is the major cause of malfunction in electronic equipment [1-9]. Higher production automation level increases product yield and reliability, and reduces the end-product cost. The current PE practice has developed into a stage whereby it is difficult to reduce the system cost from a component perspective, but the packaging and assembly are quite costly due to the labor-intensive process [1-10]. Higher power density requires a reduced system volume with the same power processing capability, more power to be handled within the same volume, or more functionality to be integrated in the same space and more spatial design freedom [1-11]. HPD design is important for applications where space is limited such as in portable electronics and IT power supply as well as in automotive, marine and space vehicles. As achieving HPD design is the primary goal of this work, the status of state-of-the-art converters will be introduced briefly below from the power density point of view.

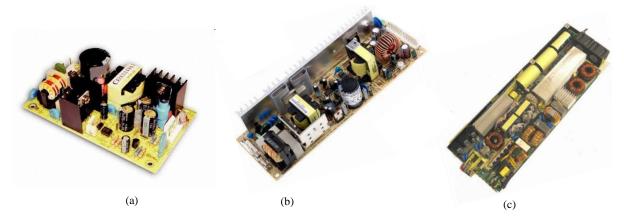

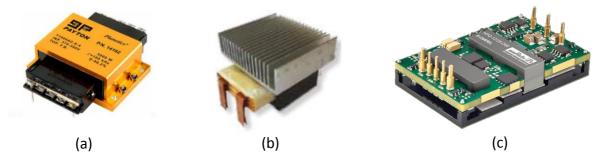

Fig. 1.2 (a) 25 W AC-DC UPS; (b) 150 W switching mode power supply (SMPS); (c) 3 kW AC/DC telecom power supply (forced air cooling)

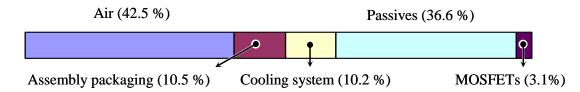

Fig. 1.3 Volume breakdown of an off-line laptop power supply built with the conventional technology [1-13]

The power density of state-of-the-art PE converters remains at a relatively low level. A survey performed on the primary power supply products of four Dutch PE developing companies [1-12] has indicated that the power density of several hundreds of W/L is still the mainstream. Many factors deteriorate the power density of current PE converters and main factors are introduced below.

#### Large amount of useless air filled in the system

Since component manufacturers employ varied packaging technologies and processes for the different components and even for the components with the same functions [1-13], the diversity and non-uniformity of component shapes and sizes are generated in current PE converters. This results in the fact that an extensive volume of waste air, which is not used for heat removing, fills a conventional PE system. This futile space can be observed in three typical switching-mode power supplies (open-frame) exhibited in Fig. 1.2. A volumetric breakdown of an off-line laptop power supply constructed with traditional technology is shown in Fig. 1.3 and indicates that the air occupies almost half (42.5%) of the system volume.

#### **Inefficient Operation**

The losses generated in a PE converter will be dissipated in the form of heat. An overabundance of heat generation increases the internal temperature of components to a level that shortens the component lifetime in the long run or immediately instigates catastrophic damage. To suppress heat generation, considerations can be given to a number of design aspects such as more efficient converter topologies, smarter semiconductor modulation methods, paralleled component units, better magnetic component structures, and more energy-efficient materials.

#### **Inefficient Heat Removal**

In PE converters, typical loss density ranges are 1~100 W/cm² for semiconductors, 0.1~1 W/cm² for magnetic components, and less than 0.1 W/cm² for capacitors [1-14]. Despite the minimal volume compared with passive components, high power semiconductors are always equipped with a cooling system much larger than themselves due to their outstanding loss density. If the thermal interface from semiconductors to the cooling system is not carefully designed, the volume of cooling system will be boosted considerably. Often, magnetic components and capacitors handle their heat through convection and radiation over their surfaces. This inefficient self-cooling pattern and their low energy density make the passive components cumbersome. In the case demonstrated in Fig. 1.3, the volume of passive components is the second largest contributor to the system volume.

To design a compact PE converter, this work investigates an effective heat generation management and heat removal management approach. More specifically, high-current bidirectional isolated DC-DC converters in marine vehicle applications will be our research carrier.

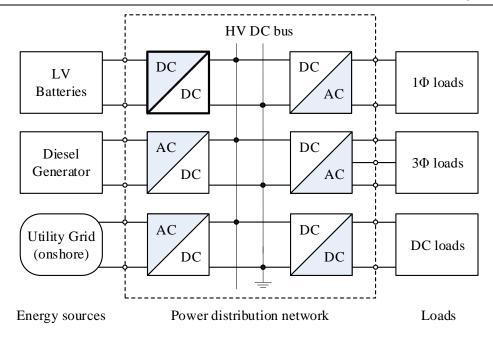

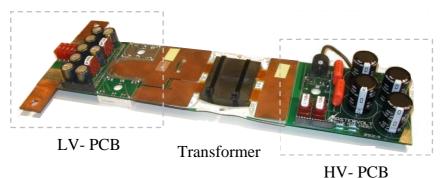

# 1.2 High-Current Isolated DC-DC Converters

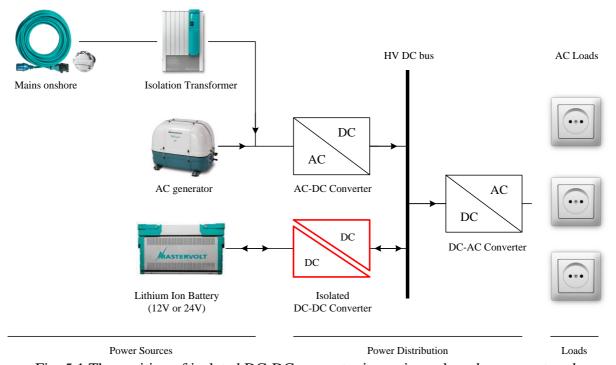

A DC-DC converter is a PE system that converts a source of direct current from one voltage level to another. A typical application of high-current isolated DC-DC converters is the interface of Low-Voltage (LV) storage batteries to the High-Voltage (HV) DC bus in vehicle power distribution systems such as yachts illustrated in Fig. 1.4. In this system, the diesel generator is the primary energy source that provides power to the loads and charges the batteries when sailing. As the alternative energy source, the storage batteries power a number of onboard loads when the generator ceases to perform, or provide the transient power to assist the start-up of engines and other electrical machines on board. It is the DC-DC converter (high-lighted in Fig. 1.4 with bold lines) that connects the storage batteries to the HV DC bus that distributes the power to loads. The major characteristics of this DC-DC converter are listed below:

- *High-Current*. Since the voltage level of the storage batteries remains at several tens of volts, and the normal continuous power is several kilowatts, the current can increase to several hundreds of amperes at the converter input.

- Galvanic isolation. Due to the large difference between batteries and a HV DC bus, a transformer with a substantial turns-ratio is normally employed to scale the voltage level.

- *High transient power*. Batteries power the start-up of engines and other electrical machines on board, so their cascaded DC-DC converters must electrically and thermally handle this large transient power.

- Bidirectional power flow. In addition to energy discharge, the batteries must also be charged when their voltage drops below a certain level. This is performed through the generators on-board or the grid plug on-shore when the marine vehicle is idle in har-

Fig. 1.4 Diagram of a typical power distribution network on a yacht

Fig. 1.5 An illustration of an air-cooling PE converter

bors. Therefore, it requires the DC-DC converter to be equipped with bidirectional power flow ability.

High power density. Due to the limited space on marine vehicles like yachts, a HPD design of this type of converters is always preferable.

# **1.3 Problem Description**

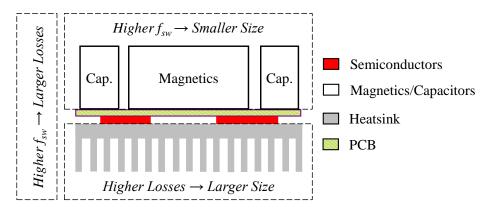

At the fixed power level, volume reduction increases the converter power density. In state-of-the-art PE converters, the passive components and cooling system dominate the system volume [1-15], which is conceptually illustrated in Fig. 1.5. Increased switching frequency of semiconductors is able to effectively reduce the volume of magnetics and capacitors [1-11], unless the capacitors are used for line frequency energy storage. However, higher frequency also raises the switching losses of semiconductors and core losses of magnetic components, which subsequently blows up the required volume of the cooling system to keep the temperature of components below a safe level. This undermines the effort of increasing frequency to

Fig. 1.6 Design dilemma in raising the power density of PE systems

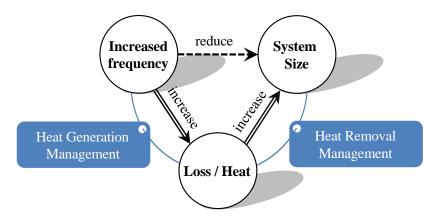

reduce the system volume. This design dilemma (illustrated in Fig. 1.6) is the primary obstacle to improving the power density of PE converters. Effective heat generation management to control the loss generated by the high switching frequency and heat removal management to control the temperature rise would be solutions to this design issue (Fig. 1.6)

The loss characteristics of a PE converter primarily originate in its circuit topology property. Different topologies vary in terms of component stresses, component counts, semiconductor modulation methods, power delivering pattern, and so on. The topology that can intrinsically generate less loss in a specified application facilitates heat generation management. In addition to operation efficiency, many other factors determine whether one topology is appropriate for a HPD design in a certain application. For instance, if capacitors are used to carry the power current, then this topology requires large capacitors to thermally manage the significant loss and is, therefore, inherently not a suitable candidate for high-current HPD design. Therefore, selecting the most suitable topology for given applications is the initial decision to make at the beginning of designing a PE converter.

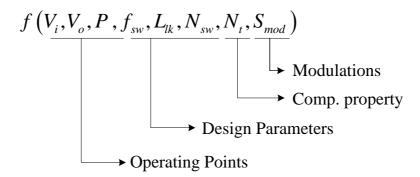

Once the converter topology has been confirmed and component types have been specified, a number of other design and component parameters must be optimized to obtain the optimal system performances. The design parameters include the switching frequency, inductance value and modulation methods, and so on. Key component parameters encompass the number of units connected in parallel (e.g. semiconductors, capacitors), number of winding turns, and the winding configuration of transformers. The optimal values of these parameters may also change with temperature and converter operating range. If the converter is to be optimized for efficiency, a loss model that can accurately and rapidly estimate the system and component losses with the abovementioned parameters will significantly facilitate the design.

The winding loss of a high-current transformer is extensive. To reduce it, the low-voltage winding must be with the minimum turn count to decrease winding resistance. However, less winding turns increase the flux density of the magnetic cores which tends to increase the tem-

perature of the cores. A larger core can be employed to restrain the flux density increase, but again, the volume of the transformer increases. Therefore, it is helpful to review the high-current transformer design in order to achieve the balance between the loss generation and transformer volume.

Besides heat generation, heat removal is the other aspect of HPD design. Without a careful cooling design, even a minimal loss can accumulate to burn components, not to mention the escalated loss density in the HPD design. Power semiconductors can be easily coupled to any flat cooling surface, however, the bulky passive components, which are considered as volume-heating components, are often decoupled from the cooling force that is engaged at semi-conductors. The heat within these passive components has to be released to ambient through their own surfaces. This results in a poor cooling efficiency. Integrating the active and passive components into the same cooling structure will improve the cooling efficiency. However, the bulky size, volume-heating property, and high internal thermal resistance of passive components remain as the challenge to cooling design.

# 1.4 Objective and Approaches

To solve the aforementioned issues, the primary objective of this thesis is to achieve a high power density design of high-current isolated DC-DC converters. To achieve this goal, a thermal management approach is proposed which extends the traditional thermal management concept to two parts: heat generation management and heat removal management.

#### **Heat generation management**

Heat generation management does not signify minimizing losses at any expense but, instead, minimize the losses within affordable cost and limited space such that the subsequent heat removal management is supplied with optimized loss inputs. This part covers three steps:

- Evaluate and select the isolated DC-DC topology that is the most appropriate for the high-current HPD design.

- Develop a loss modeling platform to analyze losses and optimize the converter and component parameters.

- Design optimization of high-current transformers.

## Heat removal management

The collective cooling strategy is proposed to limit the component temperature rise in a volumetrically efficient manner. It aims to collect heat from the main power components via different heat interface designs and conduct it to a common heat exchange surface where heat is dissipated in a centralized manner.

# 1.5 Thesis Layout

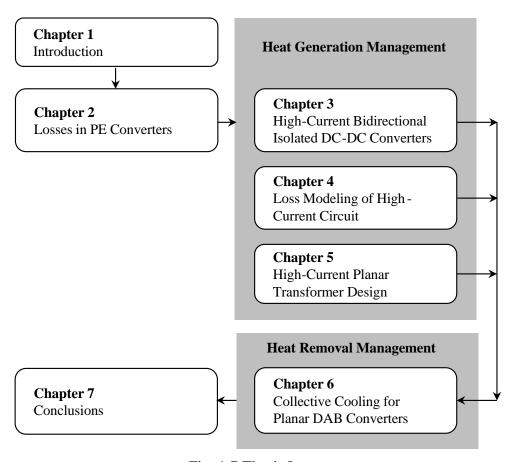

The body of this thesis consists of two parts, namely, heat generation management and heat removal management. The thesis layout is illustrated in Fig. 1.7.

Chapter 2 introduces the main loss sources in a PE converter. The loss mechanisms in different components and their calculation methods are presented as well as addressing the solutions to decrease these losses. This chapter provides background and input to the heat generation management chapters that follow.

### **Heat Generation Management**

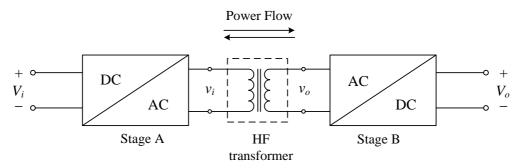

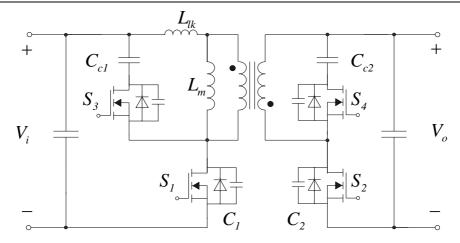

Chapter 3 evaluates and compares several mainstream isolated DC-DC topologies that are equipped with bidirectional power flow and soft-switching capability. These comparisons are based on the voltage and current stress on components, utilization of transformers, component counts, and whether passive components handle the power currents. Based on these comparisons, the topology that is most suitable for high-current and HPD design is concluded.

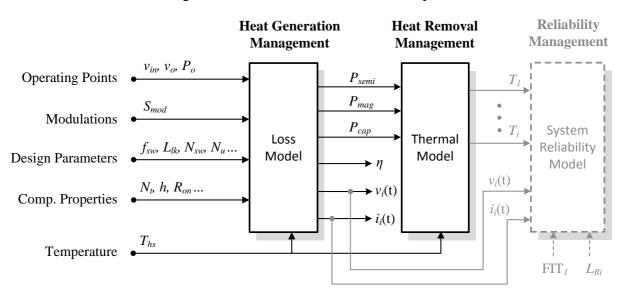

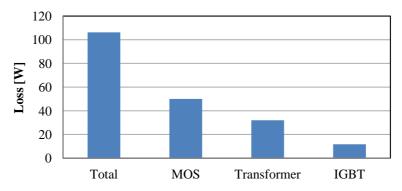

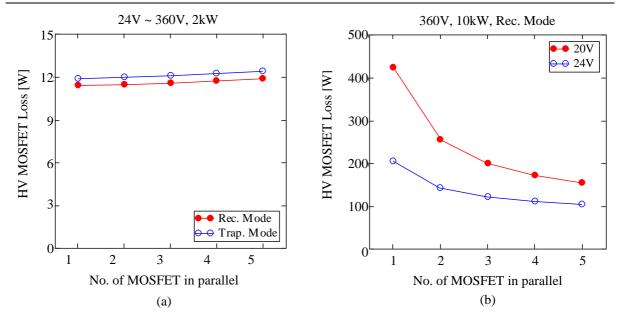

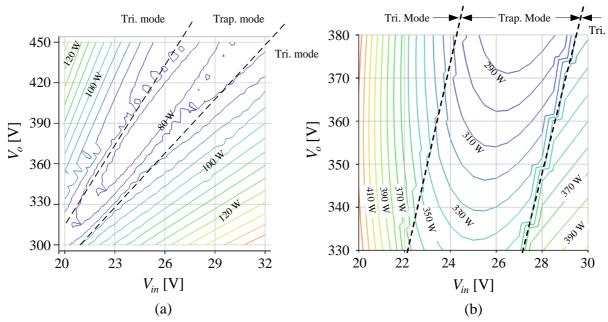

Chapter 4 proposes an analytical loss modeling platform which is specifically developed for high-current converters. Based on this loss model, losses in major power components can be calculated rapidly and accurately with various design and component parameters over the entire operating range. The effects of parasitic resistances and temperature are also included.

Fig. 1.7 Thesis Lavout

The verification methods of this loss model are also presented. This loss model is employed to optimize the converter according to the given specifications.

Chapter 5 reconsiders the design of the planar PCB transformers for high-current applications. The dimensions of the transformer core are optimized for minimum transformer losses, and the configuration of the cores is improved in response to the requirements for improved cooling and specific leakage inductance in dual active bridge topology. The transformers made of ferrite and nano-crystalline core materials are compared.

#### **Heat Removal Management**

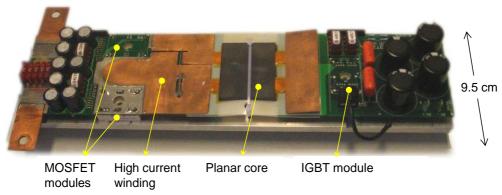

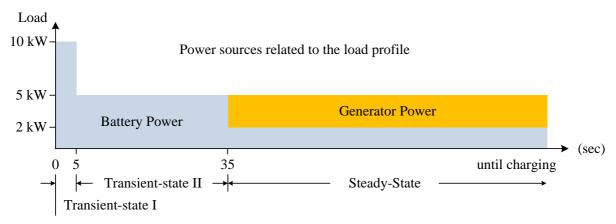

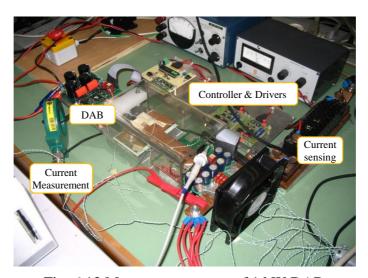

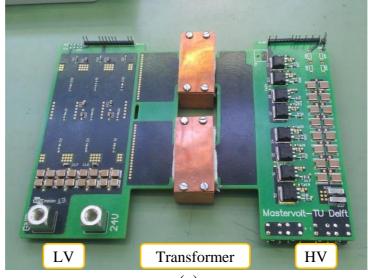

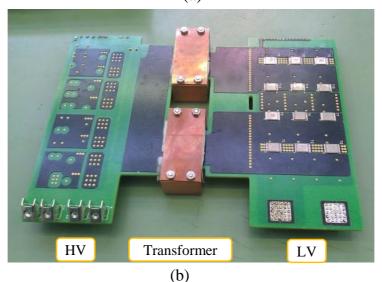

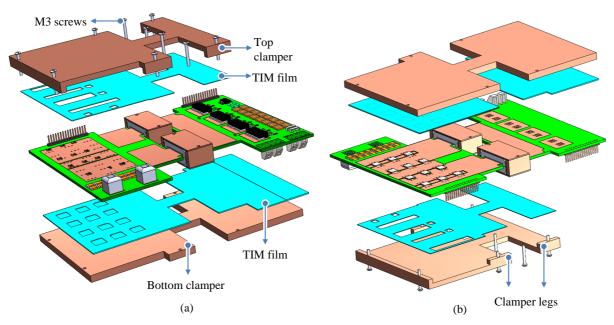

Chapter 6 proposes the collective cooling strategy for high-current isolated DC-DC converters. This strategy is engaged to obtain an effective and compact cooling system. The concept is demonstrated on a 1 kW dual active bridge converter. A double-sided collective cooling structure is also proposed to fully exploit the surface area of a low-profile converter. A dual active bridge converter with 2 kW nominal power and 10 kW peak power is designed to demonstrate this concept.

This thesis is concluded in Chapter 7 which summarizes the major contributions in this thesis. Re-commendations for future research are also suggested.

## 1.6 References

- [1-1] J. Sergent and A. Krum, "Thermal Management handbook: for electronic assemblies ", McGraw-Hill, 1998.

- [1-2] J. D. van Wyk, "Power electronics quo vadis?" *Power Electronics and Motion Control Conference (EPE/PEMC)*, 2012 15th International, Session 1-9, Novi Sad, Serbia, Sept. 2012.

- [1-3] J. D. van Wyk, F. C. Lee, "On a Future for Power Electronics," *Emerging and Selected Topics in Power Electronics, IEEE Journal of*, vol.1, no.2, pp.59-72, June 2013.

- [1-4] F. E. Gentry and R. A. York, "Scanning the issue: Special issue on high power semi-conductor devices," *Proceeding of the IEEE*, vol. 55, pp. 1247-1248, 1967.

- [1-5] L. Yao, H. Mao and I. E. Batarseh, "A Rectification Topology for High-Current Isolated DC-DC Converters," *IEEE Transactions on Power Electronics*, vol. 22, pp. 1522-1530, 2007.

- [1-6] A. Emadi, S. S. Williamson and A. Khaligh, "Power electronics intensive solutions for advanced electric, hybrid electric, and fuel cell vehicular power systems," *IEEE Transaction on Power Electronics*, vol. 21, pp. 567-577, 2006.

- [1-7] J. M. Alonso, "Foreword Special Issue on Lighting Applications," *IEEE Transactions on Power Electronics*, vol. 22, pp. 717 718, 2007.

- [1-8] J. Popović-Gerber; J.A. Ferreira; J. D. Wyk, "Quantifying the Value of Power Electronics in Sustainable Electrical Energy Systems," IEEE Transactions on Power Electronics, vol. 26, no. 12, pp.3534-3544, Dec. 2011.

- [1-9] H. Wang, K. Ma and F. Blaabjerg, "Design for reliability of power electronic systems," in *IECON 2012 38th Annual Conference on IEEE Industrial Electronics Society*, Montreal, Canada, 2012, pp. 33 44.

- [1-10] J. Popovic, "Improving packaging and increasing the level of integration in power electronics," PhD dissertation, Delft University of Technology, Delft, the Netherlands, 2005.

- [1-11] J. W. Kolar, U. Drofenik, J. Biela, M. L. Heldwein, H. Ertl, T. Friedli, and S. D. Round, "PWM converter power density barriers," in *Power Conversion Conference (PCC '07)*, Nagoya, Japan, 2007, pp. 9-29.

- [1-12] E. de Jong, "Three-dimensional integration of power electronic converters on printed circuit board," *PhD dissertation*, 2007, Technical University of Delft.

- [1-13] J. Popovic and J. A. Ferreira, "Concepts for high packaging and integration efficiency," in *35th IEEE Annual Power Electronics Specialists Conference*, *2004 (PESC'04)*, Aachen, Germany, 2004, pp. 4188 4194.

- [1-14] M. März and P. Nance, "Thermal modeling of Power-electronic systems," in *IEEE International Conference on Industrial Technology*, 2003, pp. 1196-1201.

- [1-15] Y. Wang, S. W. H. de Haan and J. A. Ferreira, "Potential of improving PWM converter power density with advanced components," in *Power Electronics and Applications*, 2009. *EPE '09. 13th European Conference on*, Barcelona, Spain, 2008.

# Chapter 2

# **Losses in Power Electronic Converters**

### 2.1 Introduction

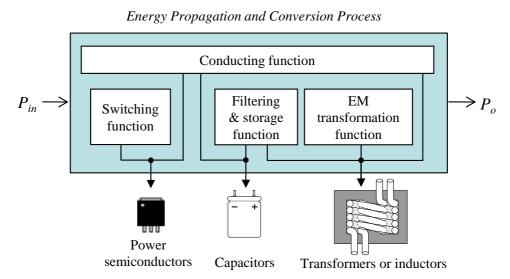

oss is generated in the form of heat during the electrical power processing and the loss generation is inevitable. With a PE converter, electrical energy is propagated and converted through several major functions [2-1]:

- Conduction

- Switching

- Electromagnetic (EM) transformation

- Filtering and storage

These functions are mainly executed by three categories of power components, including semiconductors, magnetic components (e.g. transformers, inductors) and capacitors. The functions that these components act are illustrated in Fig. 2.1. It can be found that all power components are involved in the conduction function. In the high-current applications, the conduction function will generate considerable loss in all power components. In applications where high switching frequency is required to reduce the size of passive components, high

Fig. 2.1 Loss generation by main functional components

loss will be induced in switching and EM transformation functions, which are conducted mainly by power switching semiconductors and magnetic components.

#### **Objectives**

The proposed thermal management approach, especially the heat generation management component, requires a thorough understanding of losses. The objectives of this chapter are

- To review loss generation mechanisms in power semiconductors, magnetic components and capacitors.

- To review the loss-related factors and loss calculation of different components.

- To evaluate loss reduction methods.

This chapter provides inputs to the chapters related to heat generation management and allows for 1) the evaluation of whether a topology is suitable for high-current bidirectional isolated DC-DC converters (Chapter 3), 2) the losses generated in different components to be quantified (Chapter 4); 3) Optimization of a high-current transformer design in terms of efficiency (Chapter 5).

In Section 2.2, the typical losses in a PE system based on a boost converter are outlined, and the loss generation mechanisms of key power components, loss-related factors and loss calculation methods are reviewed. The solutions to reduce losses in these components are introduced and evaluated in Section 2.3. Conclusions are presented in Section 2.4, with emphasis on high-current PE converters.

# 2.2 Component Losses

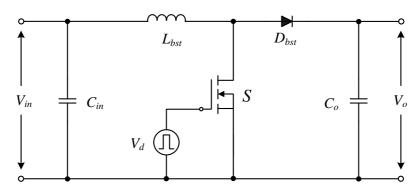

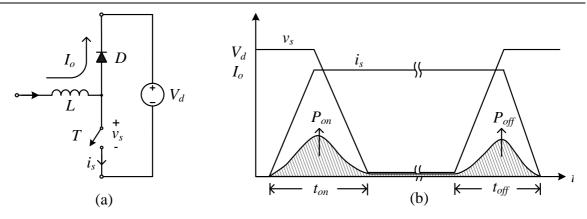

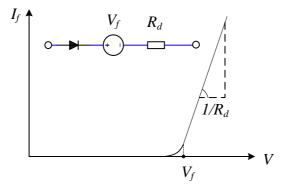

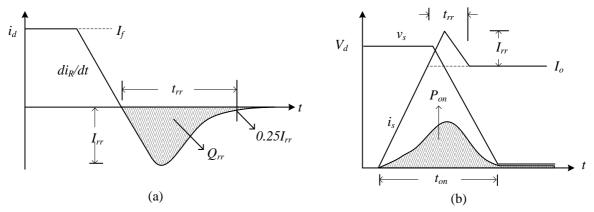

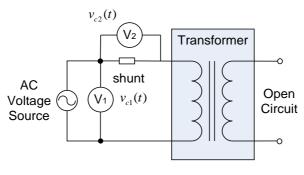

In this section, an overview of losses in PE converters is presented, with a boost converter (Fig. 2.2) as the carrier. The boost topology contains the basic power components of a PE system: power switching transistor (S, here MOSFET used) and its drive circuit, power diode ( $D_{bst}$ ), magnetic component (inductor,  $L_{bst}$ ) and capacitors ( $C_{in}$ ,  $C_o$ ). The losses in a boost converter are shown in Fig. 2.3, where all power components are assumed lossless, but their losses are represented by equivalent resistors or a voltage source (listed in TABLE 2.1). Most of losses are generated by the conduction functions, however three are generated by nonconduction functions:

Fig. 2.2 Circuit schematic of a boost converter

TABLE 2.1 LOSSY RESISTORS OR VOLTAGE SOURCE IN FIG. 2.3 AND THEIR REPRESENTED LOSSES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LOSSES                                |                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|

| Designators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Resistors                             | Loss Represented                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Power MOSFI                           | ET                                                     |

| $R_{on}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | On-state resistance                   | Conduction loss                                        |

| $R_{sw}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Equivalent dependent resistance       | Switching loss                                         |

| $R_g$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Gate drive resistor                   | Switching loss                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Diode                                 |                                                        |

| $R_d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Diode on-state resistance             | Conduction loss                                        |

| $V_f$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Diode forward voltage                 | Conduction loss                                        |

| $R_{rr}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Equivalent dependent resistance       | Switching loss (Reverse Recovery)                      |

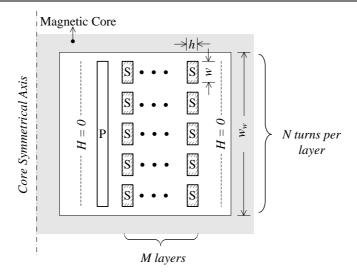

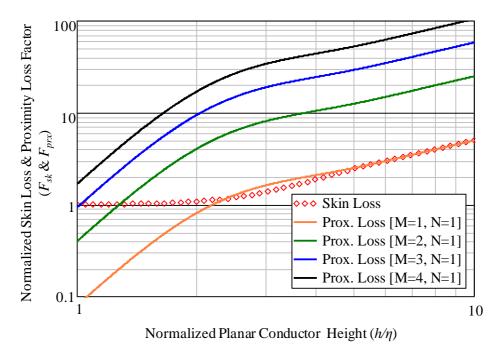

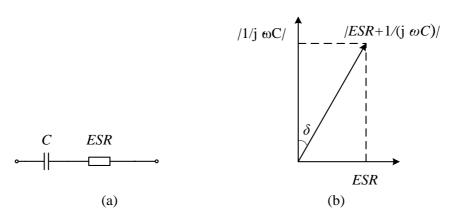

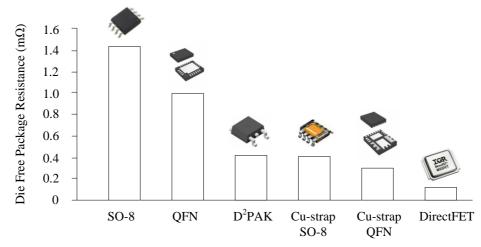

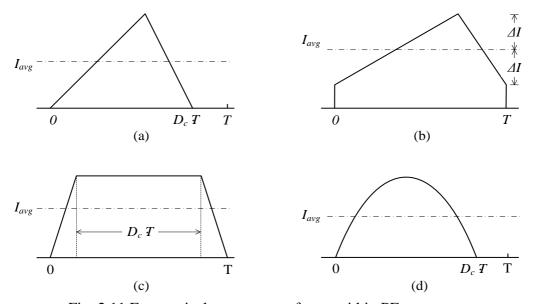

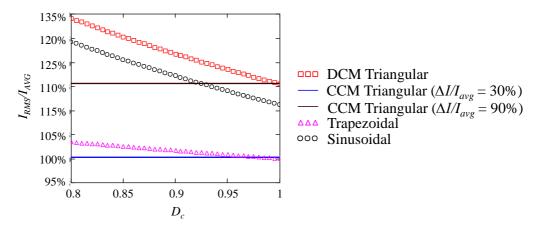

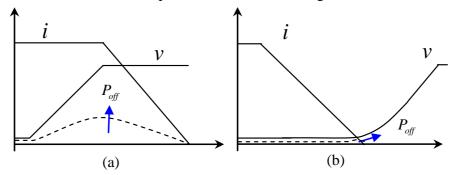

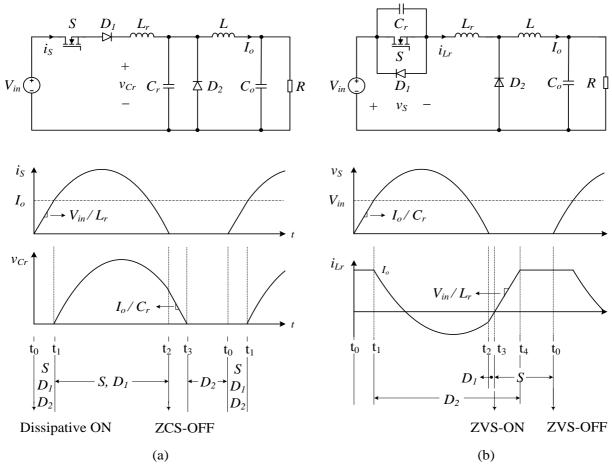

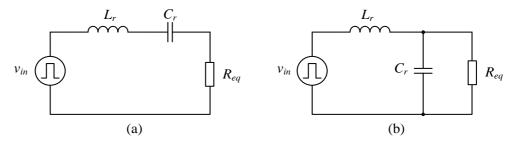

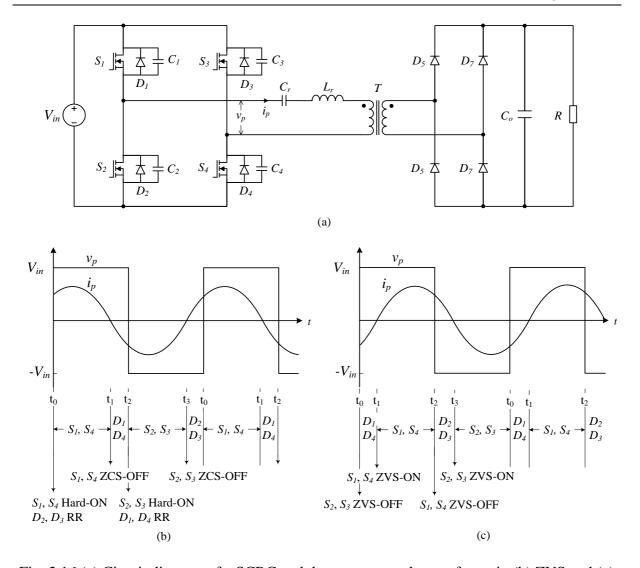

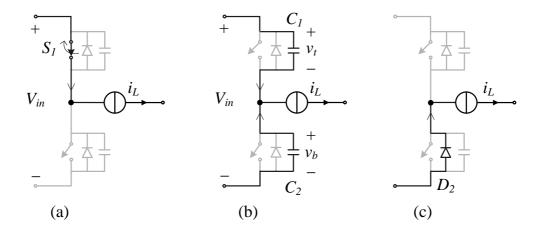

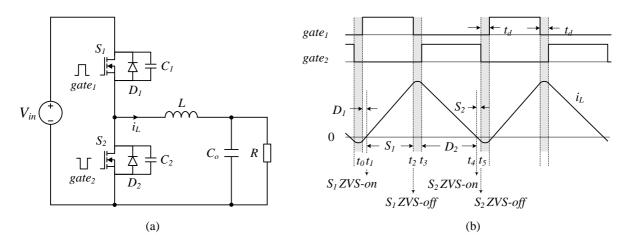

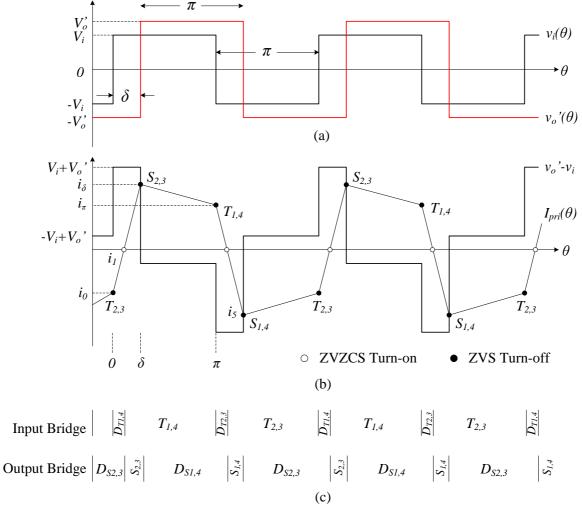

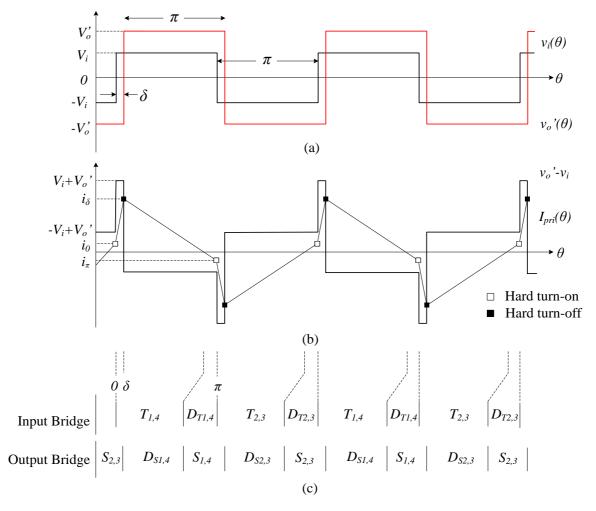

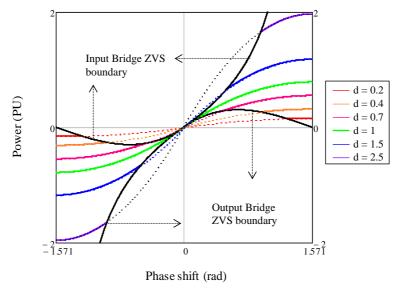

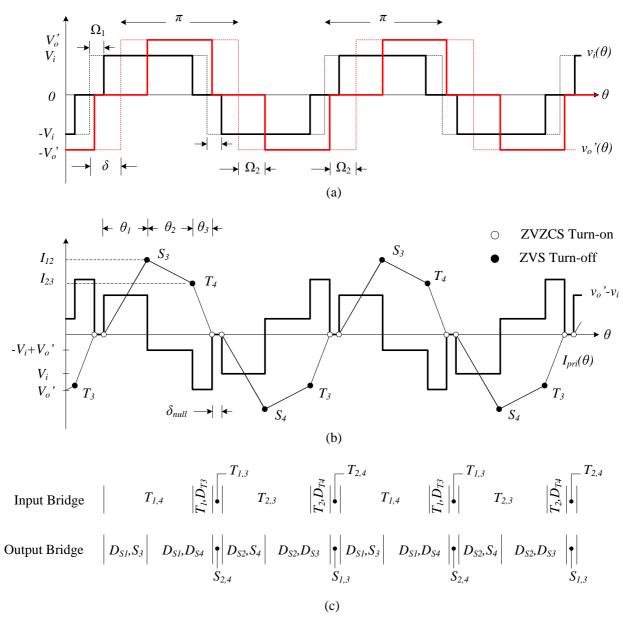

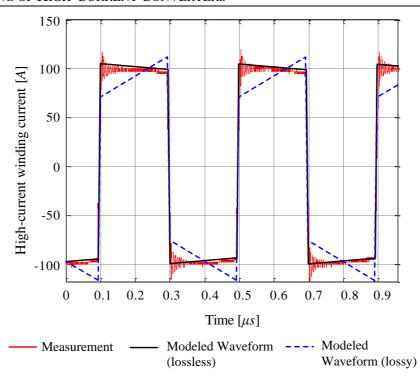

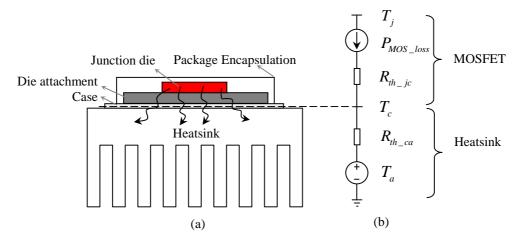

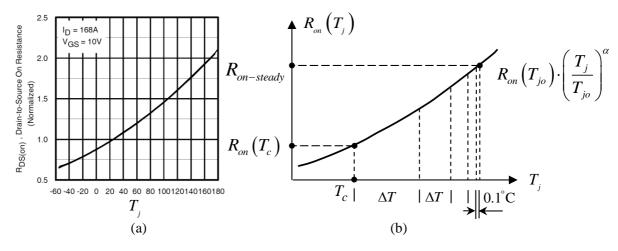

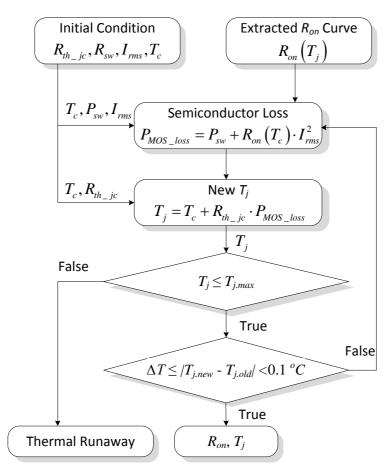

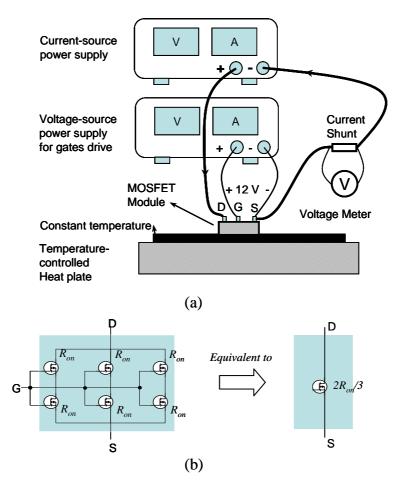

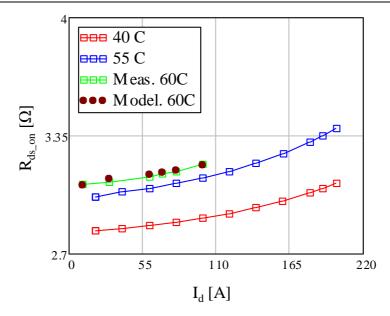

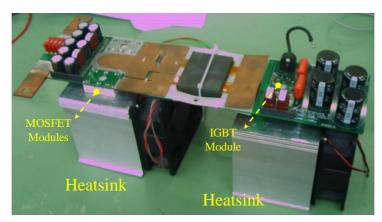

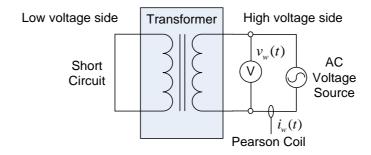

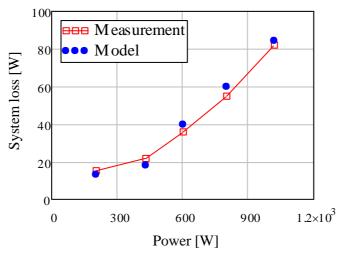

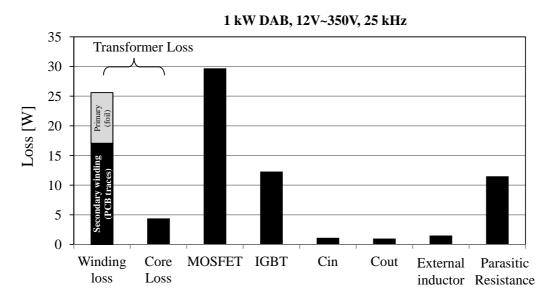

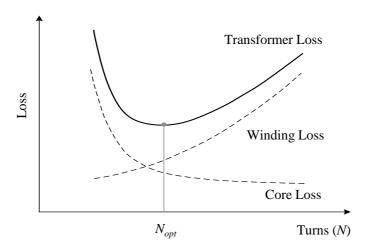

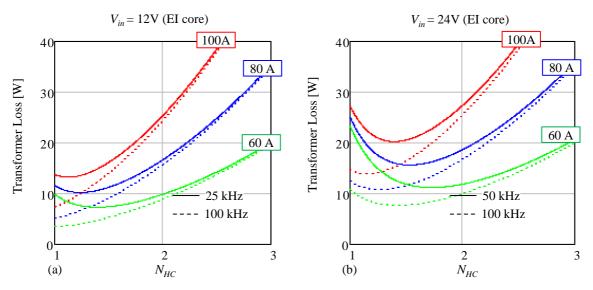

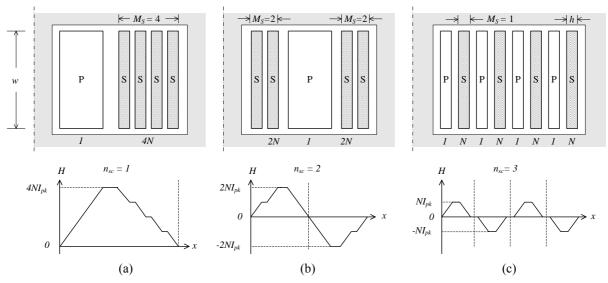

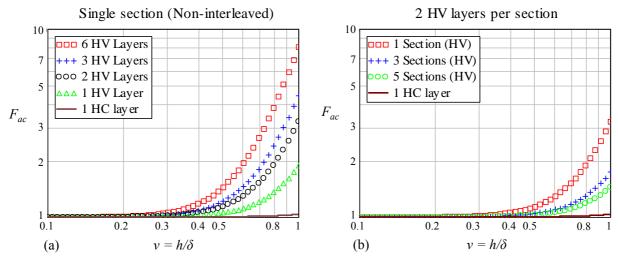

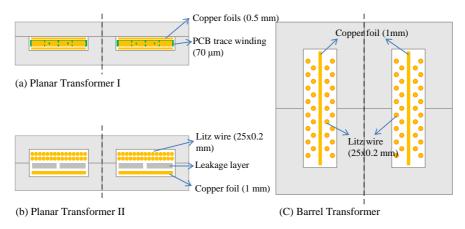

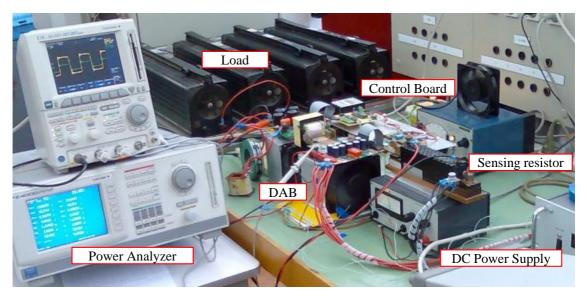

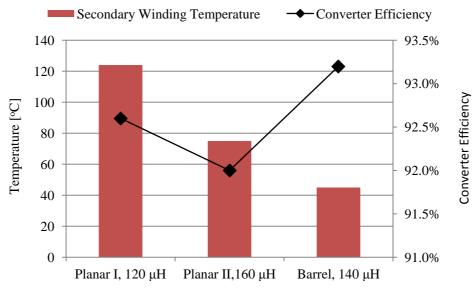

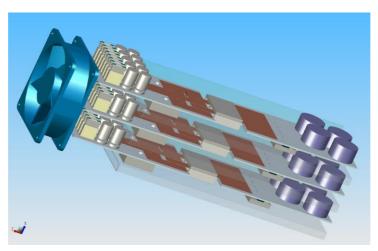

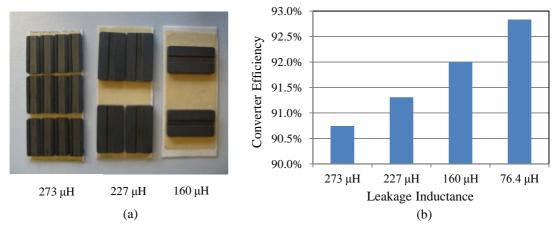

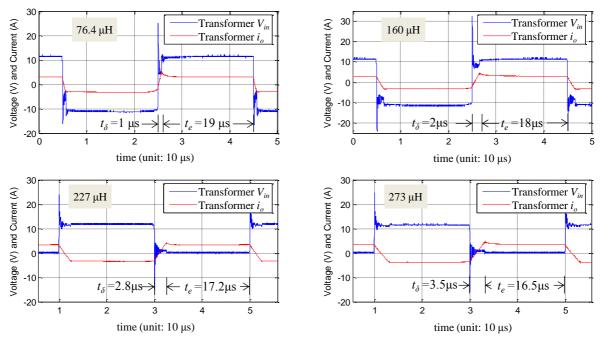

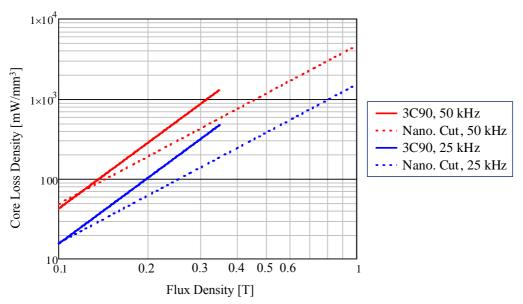

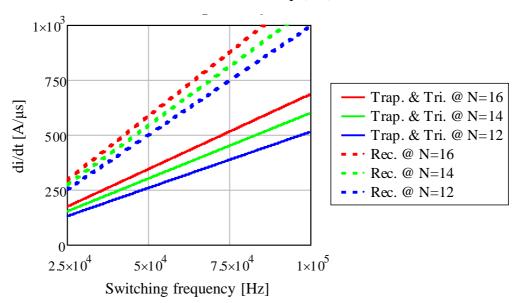

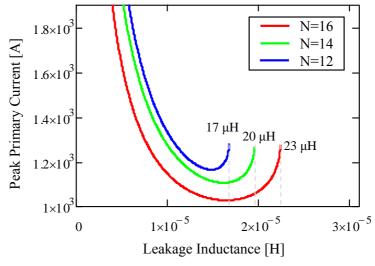

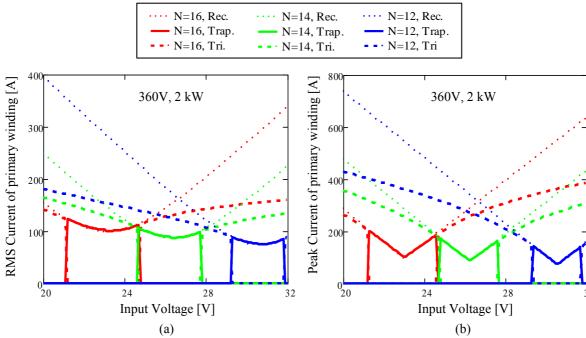

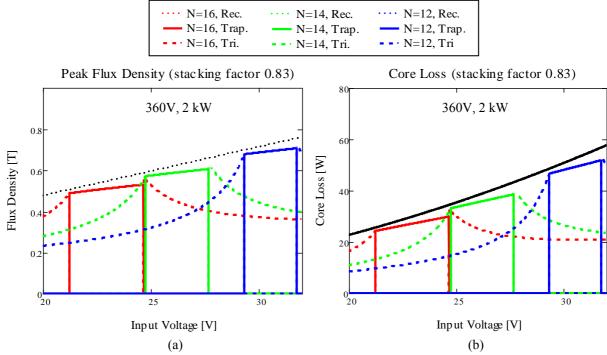

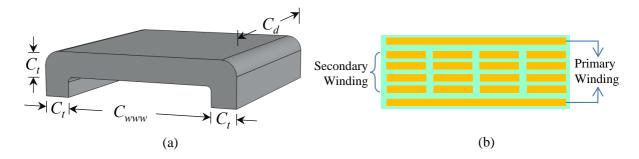

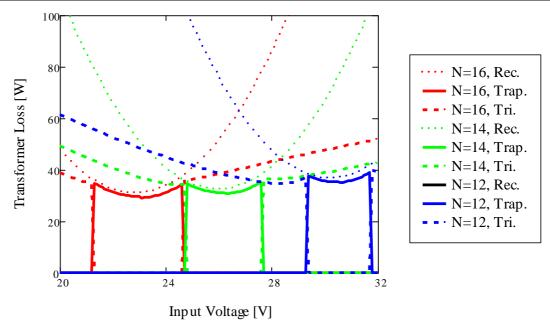

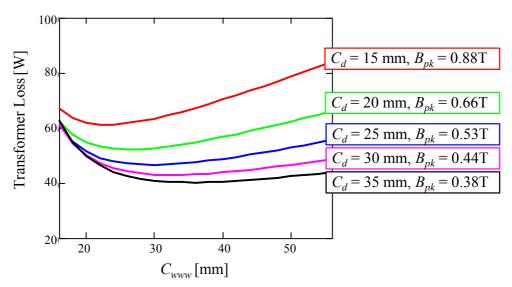

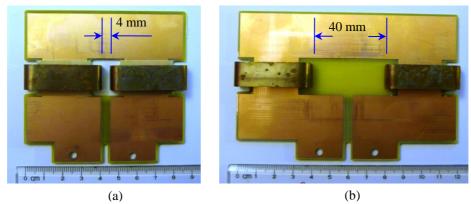

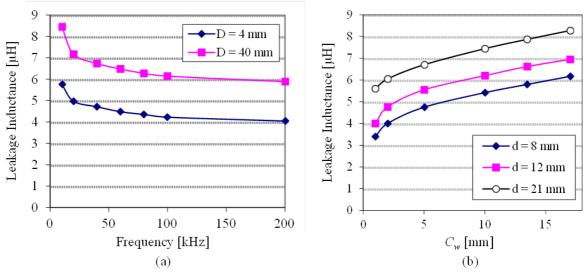

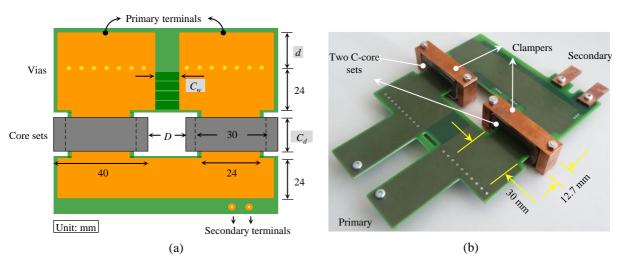

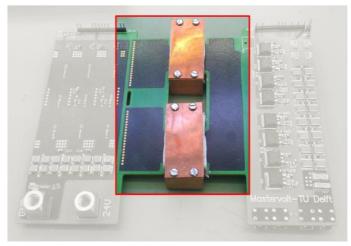

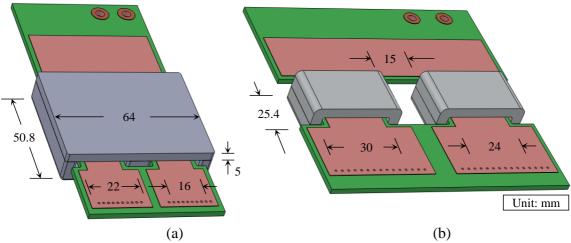

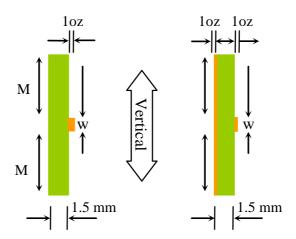

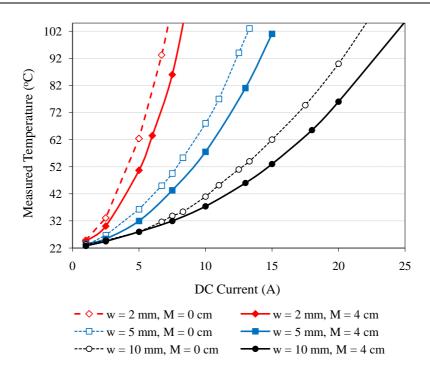

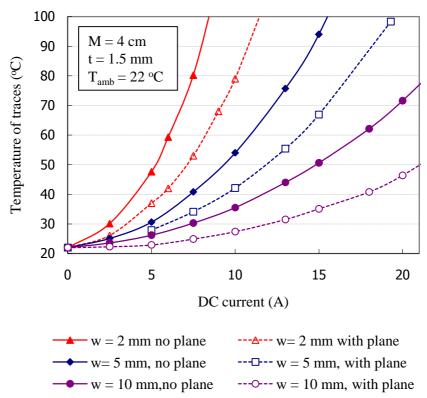

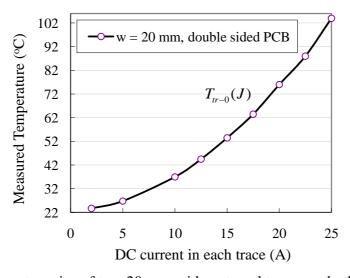

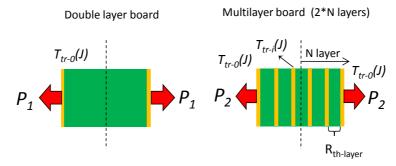

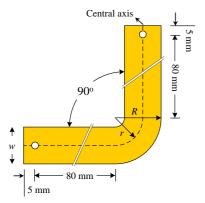

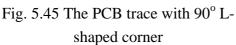

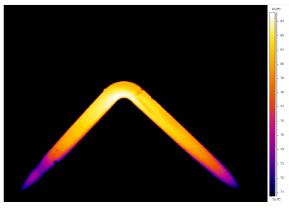

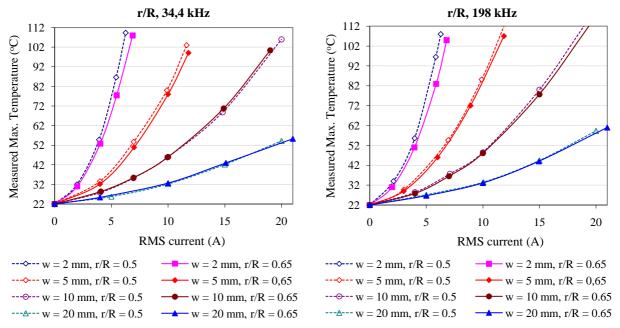

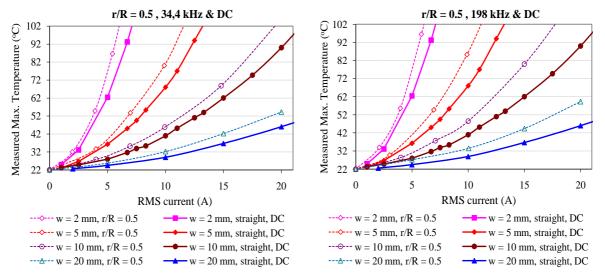

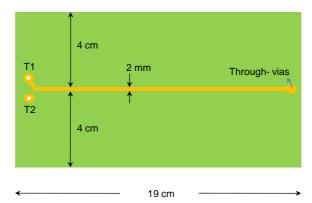

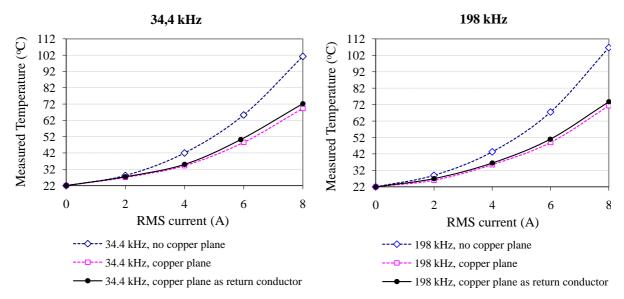

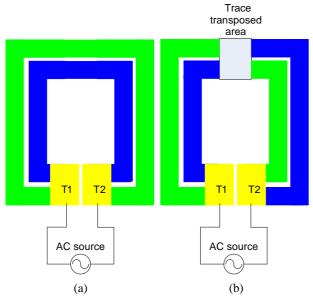

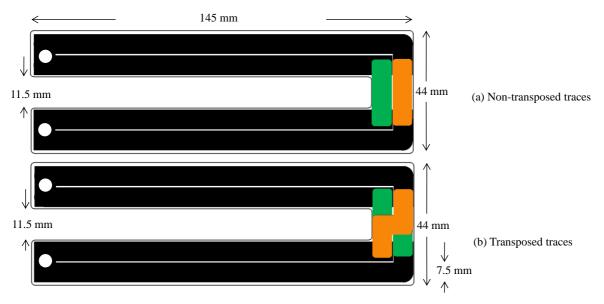

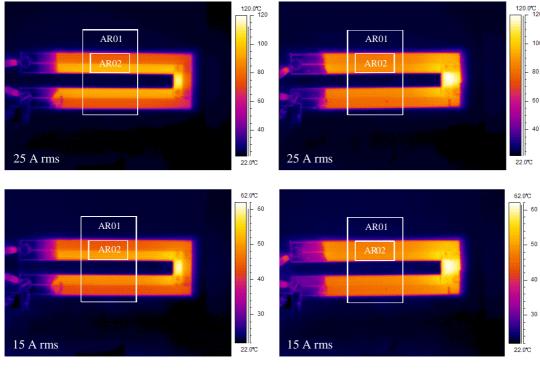

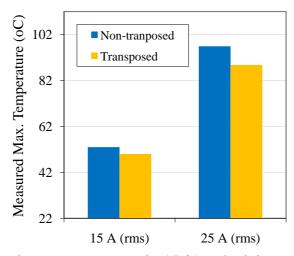

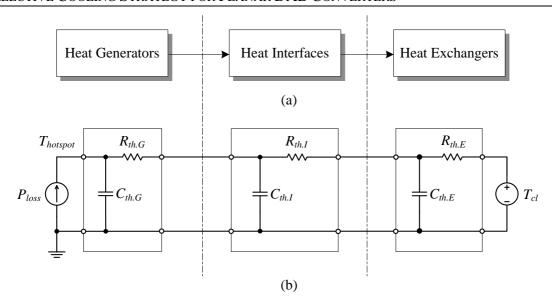

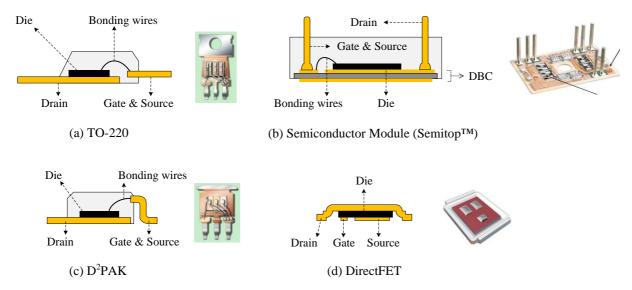

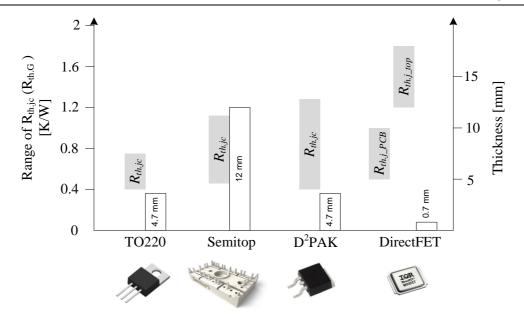

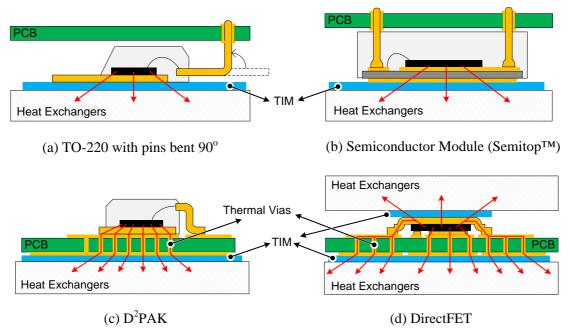

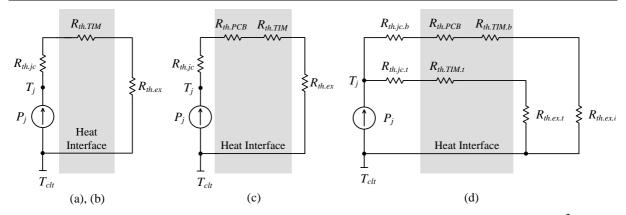

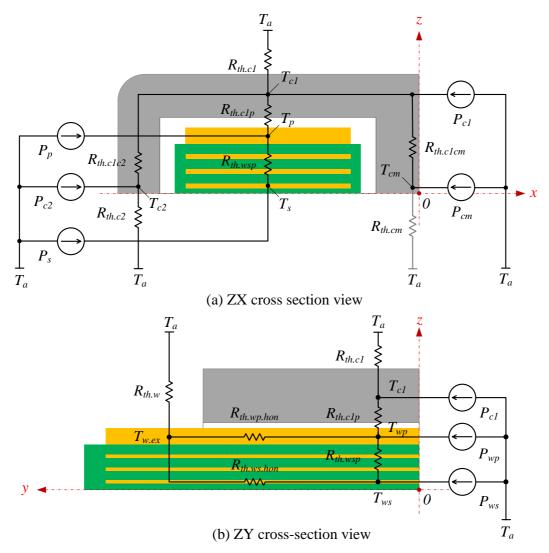

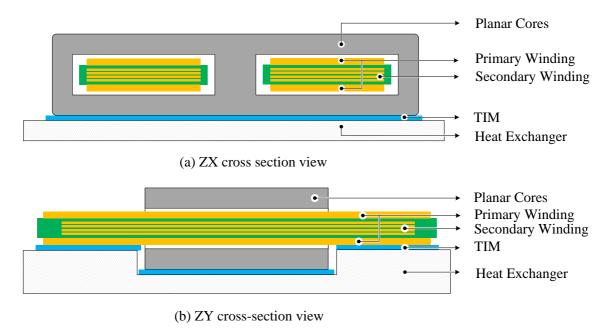

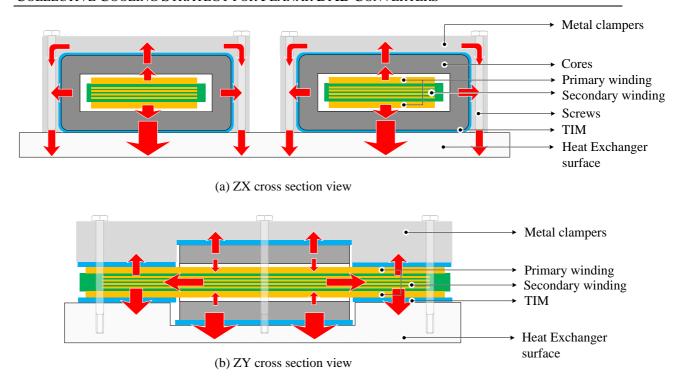

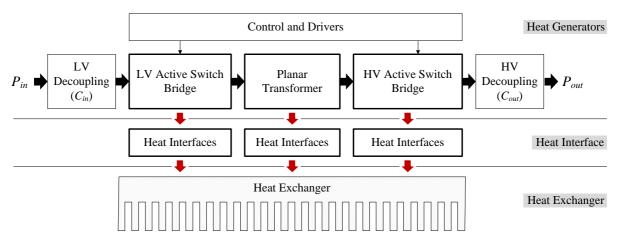

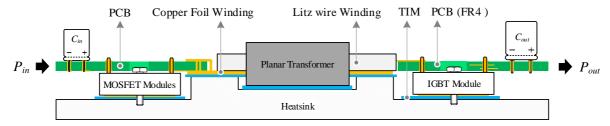

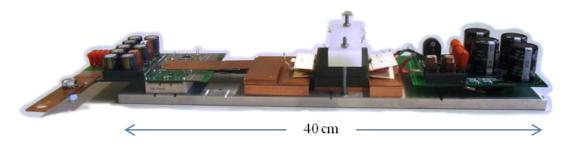

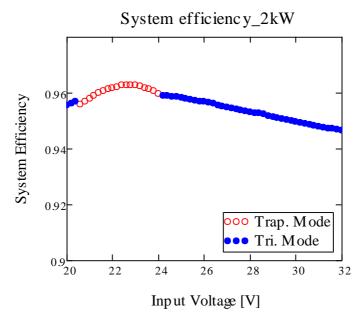

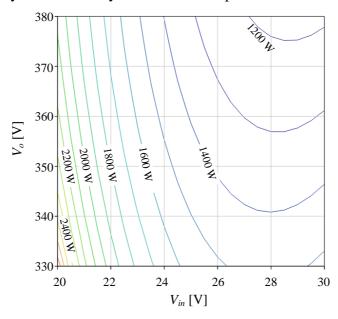

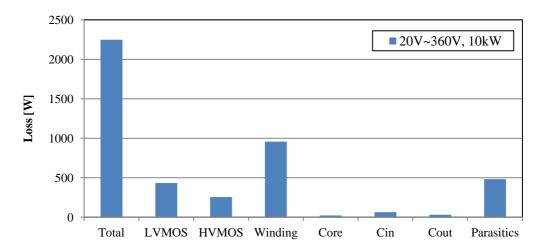

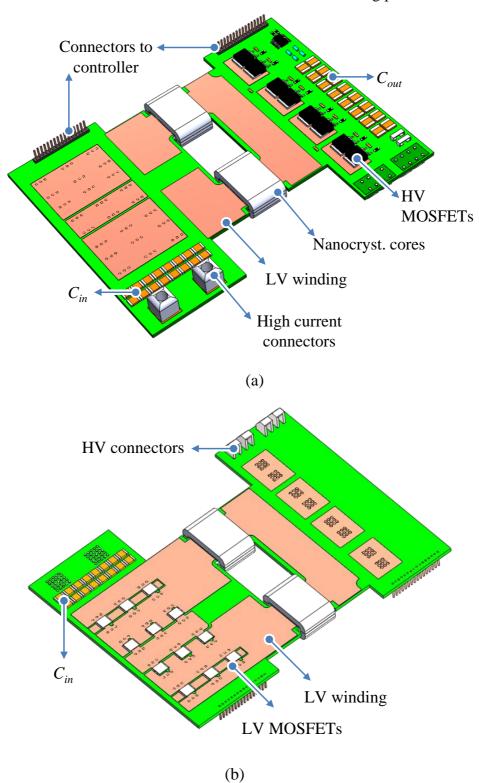

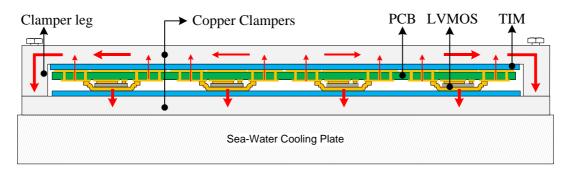

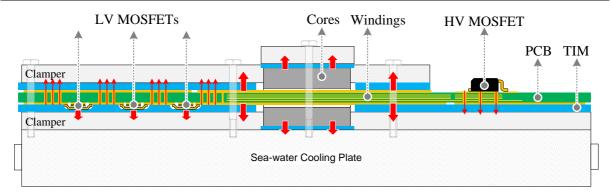

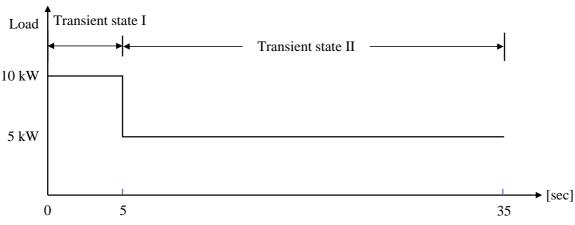

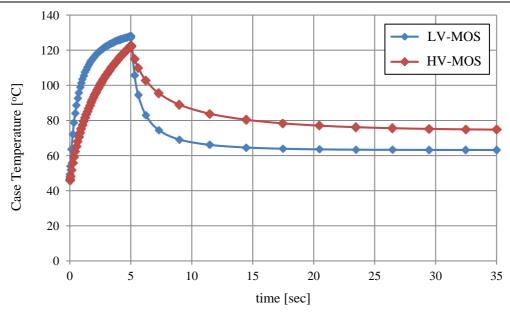

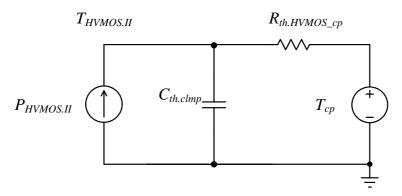

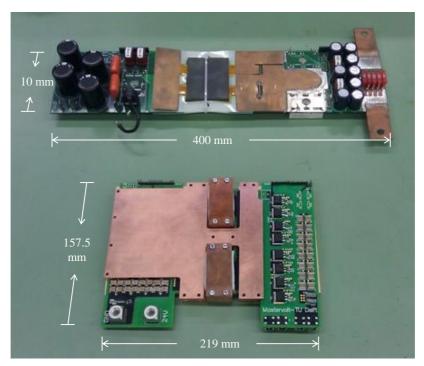

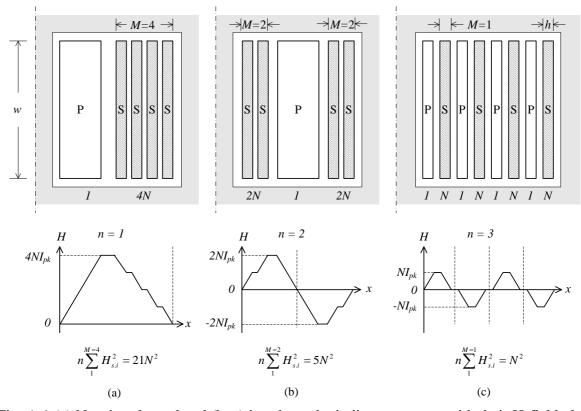

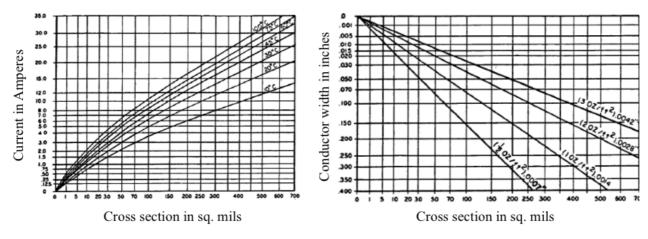

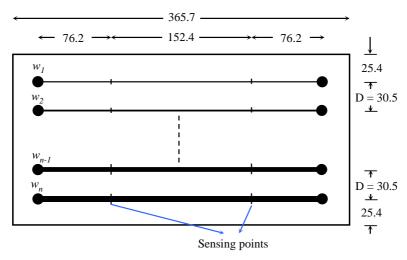

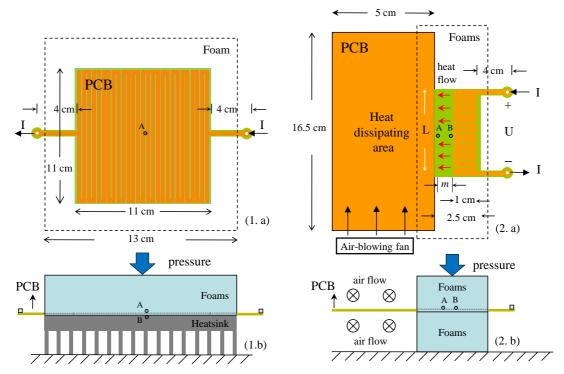

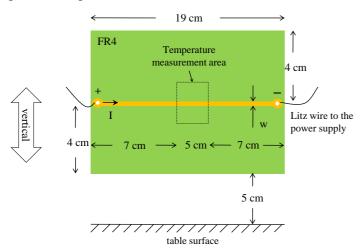

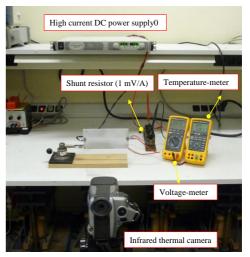

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Inductor                              |                                                        |