# Side-channel leakages from different target devices

0

# Vipul Arora

**Challenge the future**

# Side-channel leakages

## from different target devices

by

## Vipul Arora

in partial fulfillment of the requirements for the degree of

Master of Science in Embedded Systems

at the Delft University of Technology, to be defended publicly on Tuesday December 15, 2020 at 8:45 AM.

Student number:4770269Thesis committee:Prof. dr. ir. R.Ł. Lagendijk,<br/>Dr. ir. S. Picek,TU Delft, Chair<br/>TU Delft, Supervisor<br/>Radbound University<br/>TU DelftDr. ir. I. Buhan,<br/>Dr. ir. M. TaouilTU Delft

This thesis is confidential and cannot be made public until December 15, 2020.

An electronic version of this thesis is available at <a href="http://repository.tudelft.nl/">http://repository.tudelft.nl/</a>.

# Abstract

The advances in cryptography have enabled the features of confidentiality, security, and integrity in the digital space. The information about the working of the digital system is used to perform side-channel attacks. These attacks exploit the physics of the system rather than targeting the mathematical complexity of algorithms. Side-channel attacks measure the variations in the system's physical characteristics to obtain information about the operations being performed along with the operand data.

In this work, we evaluate how the choice of physical target device impacts the cryptographic implementation's security. A software implementation is flashed on devices from two different manufactures with the same instruction set, configured for identical execution. Power traces from different hardware devices are acquired and evaluated using leakage detection methodologies of TVLA, and KL-Divergence. Trace-sets are compared at the abstraction level of intra-board, inter-board, and inter-class to explore the information leaks. The performance of leakage detection methodologies in identifying leaks is evaluated using key-rank analysis and verified by profiling templates.

Results show two classes of devices belonging to different manufacturers vary significantly in terms of the power profile yet show similarities in data leakage. Based on the source of leaks; micro-architecture leaks have minor differences at the inter-board level within boards of the same class, though the results of micro-architecture leaks are not comparable across boards of different classes. Data-overwrite leaks are specific to the instruction set and pipeline implementation and are observed for both classes of devices. This work provides a methodology for evaluating software implementations across different hardware.

# Preface

Before you lies my thesis, which marks the completion of my masters at the TU Delft. I started the thesis in January 2020 while the world was still normal. However, switching to working from a room and meeting people over video calls did impact productivity. This year-long journey had its highs and lows with a lot of learning. There are many people who directly or indirectly contributed to this work, I would like to take this opportunity to thank them.

Firstly, I would like to thank my supervisor, Stjepan, for guiding me through a big part of my master's. You helped me out with the ever-changing situations and were accommodating for meetings, even at non-typical timings. Thank you for your support, which has enabled me to fulfill this achievement. I would also like to thank Ileana for her guidance in making sense of the story and proofreading. Thank you for spontaneous meetings and for mentoring me throughout the thesis.

I am thankful to Riscure for giving me the internship and allowing me to take the laboratory setup at home. I would like to thank Guilherme and Baris for taking an interest in my project and providing their feedback to direct the project.

Finally, I am thankful to Shruti, Fanis, Greg, and Jure for being able to distract me when I wanted to relax over breaks. I am grateful to my parents for supporting me through my studies, without whom this would not have had been possible.

Vipul Arora Delft, December 2020

# Contents

| 1      | Introduction                                                                                                                                                                                                                                                                                                                                  | 1                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 1<br>2 | Background         2.1 Microprocessor.         2.1.1 Instruction set.         2.1.2 Toolchain         2.1.3 Micro-architecture         2.1.4 Subsystem implementation         2.2 Cryptography         2.2.1 AES algorithm         2.2.2 Assembly S-box implementation         2.3 Side-channel analysis         2.3.1 Simple power analysis. | <b>1</b><br>5<br>5<br>6<br>7<br>8<br>9<br>9<br>10<br>11 |

|        | <ul> <li>2.4 Leakage detection methodologies</li></ul>                                                                                                                                                                                                                                                                                        | 13<br>13<br>14<br>15<br>15                              |

| 3      | <ul> <li>3.1 Leaks from Micro-architecture</li> <li>3.1.1 Pipeline leaks</li> <li>3.1.2 Variability in nanoscale devices</li> <li>3.2 Template attacks and machine learning</li> </ul>                                                                                                                                                        | 17<br>17<br>18<br>18<br>19                              |

| 4      | <ul> <li>4.1 Target devices</li></ul>                                                                                                                                                                                                                                                                                                         | <b>21</b> 22 22 23 24 25 26 27 27 27                    |

| 5      | 5.1 Methodology                                                                                                                                                                                                                                                                                                                               | <b>31</b><br>31<br>32<br>32                             |

|     | 5.2   | STM Intra-board comparison                 | 34 |

|-----|-------|--------------------------------------------|----|

|     |       | 5.2.1 STM inter-data comparison            | 34 |

|     |       | 5.2.2 STM inter-key comparison             | 37 |

|     | 5.3   | NRF intra-board comparison                 | 40 |

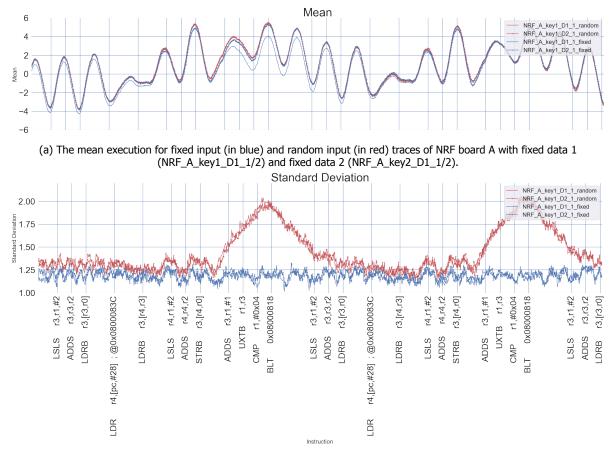

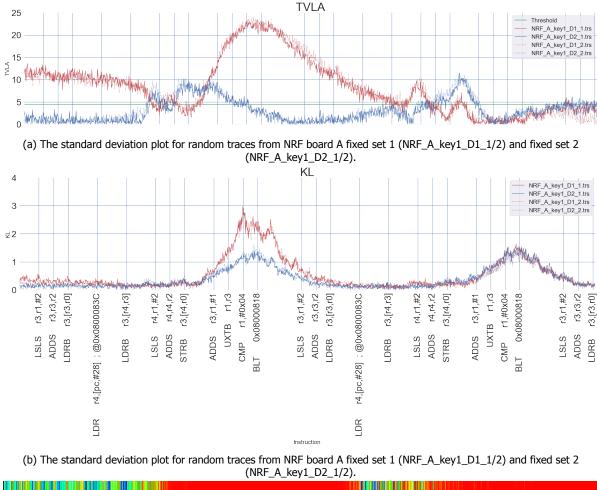

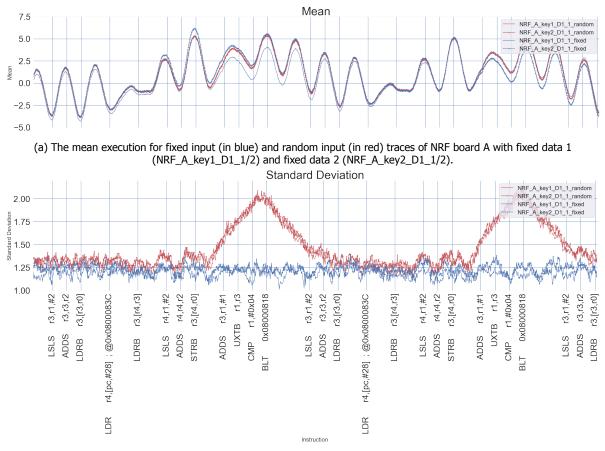

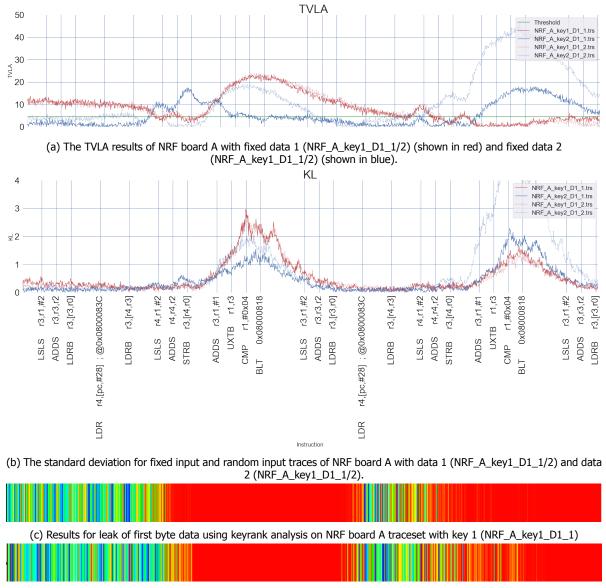

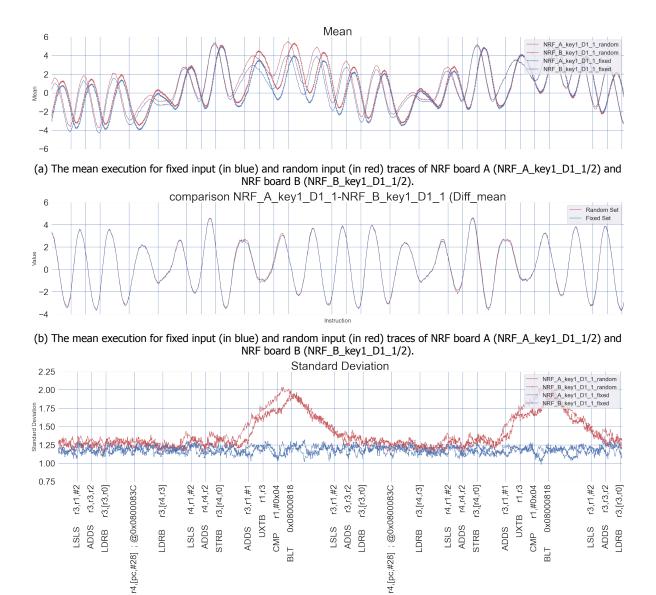

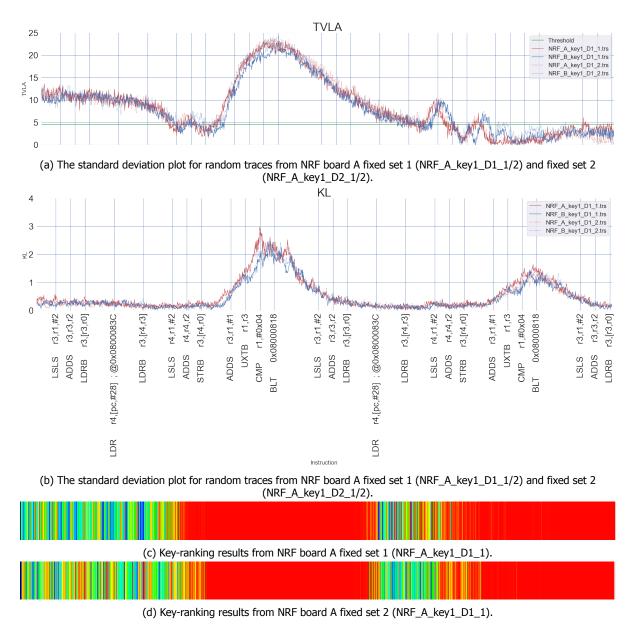

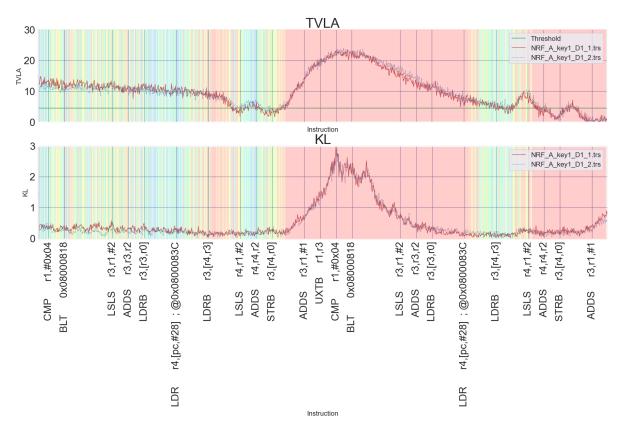

|     |       | 5.3.1 NRF inter-data comparison            | 40 |

|     |       | 5.3.2 NRF inter-key comparison             | 43 |

|     | 5.4   | Summarising chapter                        | 46 |

| 6   | Inte  | r-board comparison                         | 47 |

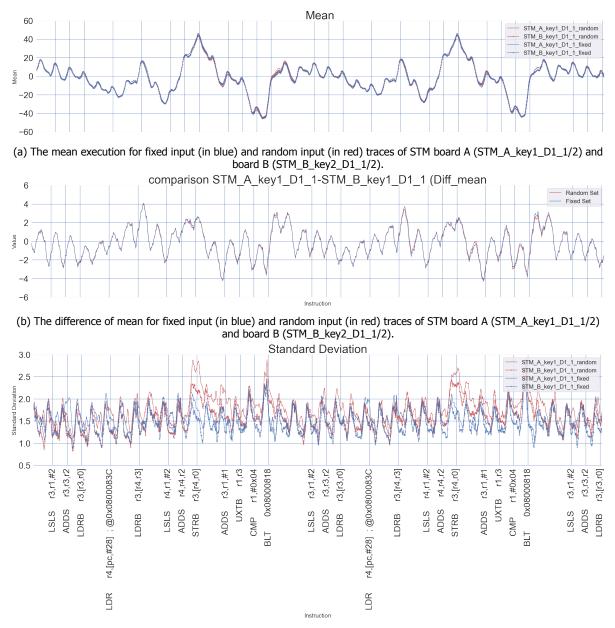

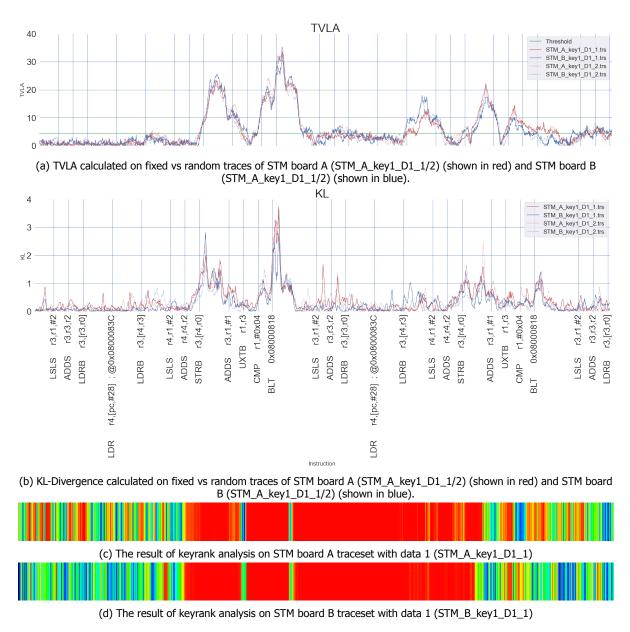

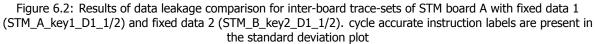

| •   |       | STM inter-board comparison.                | 48 |

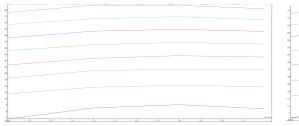

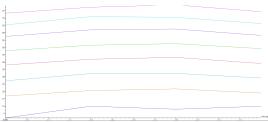

|     | 0.12  | 6.1.1 Power profile comparison.            | 48 |

|     |       | 6.1.2 Data leakage comparison.             | 48 |

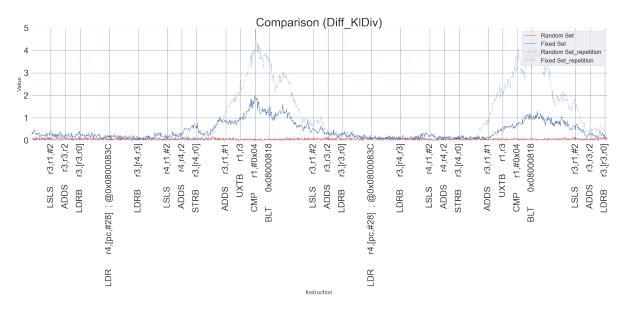

|     |       | 6.1.3 Comparing trace sets for differences | 50 |

|     | 6.2   | NRF inter-board comparison                 | 51 |

|     |       | 6.2.1 Power profile comparison.            | 51 |

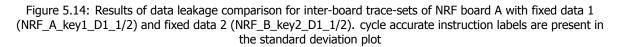

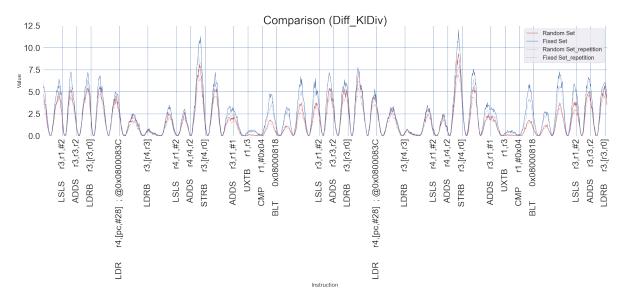

|     |       | 6.2.2 Data leakage comparison.             | 53 |

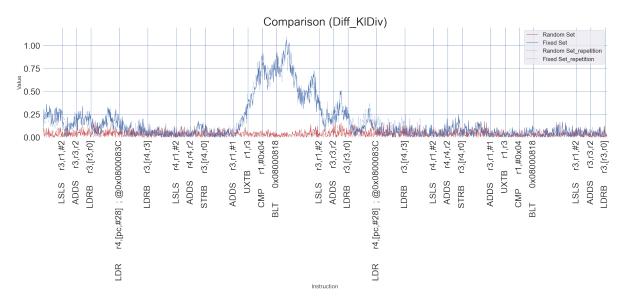

|     |       | 6.2.3 Comparing trace sets for differences | 53 |

|     | 6.3   | Profiling templates                        | 53 |

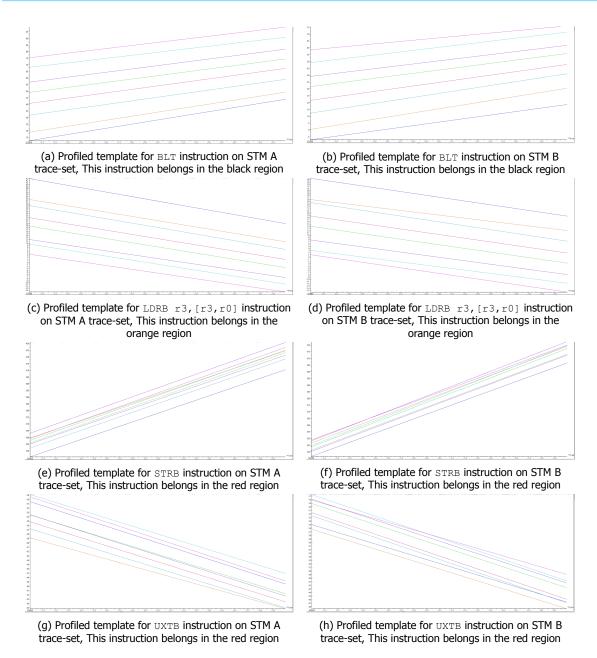

|     |       | 6.3.1 STM template profiling               | 54 |

|     |       | 6.3.2 NRF template profiling               | 57 |

|     | 6.4   | Summarising chapter                        | 58 |

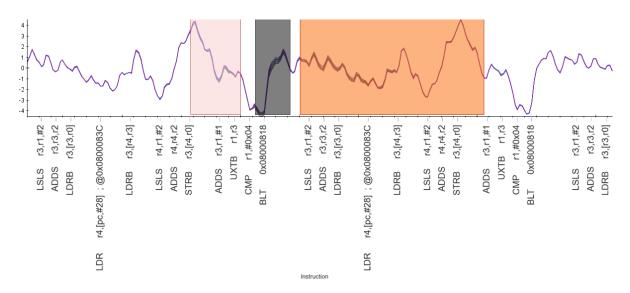

| 7   | Inte  | r-class comparison                         | 59 |

|     |       | Inter-class comparison.                    | 59 |

|     |       | 7.1.1 Inter-class power profile analysis   | 59 |

|     |       | 7.1.2 Data leakage comparison.             | 62 |

|     |       | 7.1.3 Key-rank analysis                    | 64 |

|     | 7.2   | Summarising chapter                        | 67 |

| 8   | Con   | clusion                                    | 69 |

|     | 8.1   | Research questions                         | 69 |

|     | 8.2   | Contributions                              | 70 |

|     | 8.3   | Limitations                                | 71 |

|     | 8.4   | Future work                                | 71 |

| Bil | bliog | raphy                                      | 73 |

|     | -     |                                            | -  |

1

# Introduction

In recent years growth in large scale semiconductor manufacturing has enabled the fast development of smart devices. An application developer does not need to bother with processors' hardware design to develop applications for most cases. These applications can be sensitive, though not all product development teams have resources for conducting security evaluations.

The advances in cryptography have enabled the features of confidentiality, security, and integrity in the digital space. The current widely used encryption algorithm AES (1998) has proven to be computationally complex for brute force attacks on the key, which can be assumed secure against classical adversaries with time and memory constraints [1]. Using crypto algorithms, developers design complex systems with confidence, assuming the secrecy of the key. In practice the hardware used for implementing the algorithm also needs to be considered as a part of the attack surface to be protected against adversaries with physical access.

Academic works have proven attacks on real-world devices such as the KeeLoq remote entry system [2], the bit-stream encryption in Xilinx FPGAs [3] and Mifare DESFire contactless payment cards [4]. These works utilize the information from the system's side-channel to expose the secret that can be employed for reverse-engineering the system, IP thefts, or injecting trojans.

The information obtained about the working of the underlying system is used to perform **side-channel attacks**. These attacks exploit the physics of the system rather than targeting the mathematical complexity of algorithms. Side-channel attacks measure the variations in the system's physical characteristics to obtain information about the operations being performed along with the operand data. Relating this information, an adversary can deduce the private key data of a cryptographic implementation and breach the system's security. It is common knowledge in security that a system is as strong as the weakest link. The security of a cryptographic system is likewise dependent on the processor's underlying implementation performing these operations [5]. If information about the sensitive data (i.e. password or key data) can be deduced by observing the physical characteristics of the system, the system is said to have **leaks**<sup>1</sup>.

Encryption/Decryption involves performing a sequence of mathematical operations on the input and output data, respectively, utilizing a secret-key. When coded in software and implemented using an **instruction set** of a general-purpose CPU, these mathematical operations are termed as **software implementation**. Some cores have dedicated logic circuitry for performing the cryptographic operation at a semiconductor level and is termed as a **hard-ware implementation**. Irrespective of the type of implementation, hardware or software,

<sup>&</sup>lt;sup>1</sup>The term leaks refers to leakage of information

an adversary can obtain knowledge about the key data while sensitive operations requiring manipulation with key data are performed. The observations can be recorded in the form of power or electromagnetic traces, referred to as **traces** in short. In side-channel analysis, these traces are used to make deductions on the sequence of the operations and the operand data used.

The early works in side-channel analysis treat the target device as black-box to extract information pertaining to **cryptographic primitives** [6]. To develop countermeasures the works have focused on adding randomness and masking the leaks [7–9]. It has been a cat and mouse game of developing new countermeasures and attacks for the last two decades. More recent works have been focused on generating complex power models [10] and employing deep learning techniques to predict the key from trace-sets [11]. The research direction detached away from leakage sources at the physical layer and focused more on attack methodologies. Our work takes a different direction and focuses on the effects of hardware choices on leakage.

An adversary collects multiple traces while repeating the target operation on varying input data. The power traces, labeled with the corresponding input and output, are recorded to create **trace-sets**. **Differential power analysis** is an advanced form of side-channel analysis, using statistical tools to compare the deviations between power-traces relating the input and output data for predicting the secret-key data. Differential power analysis has existed for about 20 years now, first presented by Kocher et al. [12].

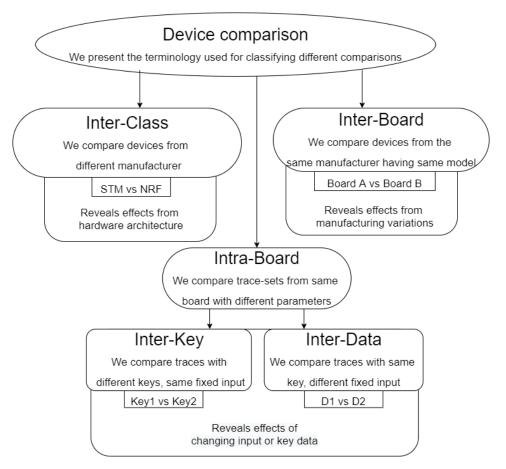

The research question we ask in this thesis is both simple and practically relevant for an embedded system developer assigned to implement an existing cryptographic algorithm (e.g tiny AES, Mbed TLS) on a micro-controller family (e.g ARM Cortex-M0, a popular choice in the IoT industry). The developer is free to choose a micro-controller meeting the project's specifications from the diverse SoC range offered by different manufacturers (ST, NXP, Nordic, etc.). The devices supporting a similar instruction set (e.g ARMv6), can vary in design; firstly based on the semiconductor technology used in manufacturing, which influences the physical characteristics of a device, and secondly, as a function of the changes in the HDL schematic of the micro-architecture to achieve the functional features desired for the specific device. The evaluation is done on hardware at different abstraction levels as shown in figure 1.1; devices from different manufacturers classified as **inter-class**; board iterations from same manufacturer are classified as **inter-board**; varying key and input data on the same physical board is classified as **intra-board**.

In this work, we evaluate how the choice of the physical target device impacts the security of the implementation of the cryptographic algorithm. Concretely, the questions relevant to our embedded system developers are:

- 1. How significant are the inter-key and inter-data variations?

- 2. How significant are inter-device manufacturing variations?

3. What is the impact of micro-architectural differences across manufacturers, on the SCA leakage for a given software implementation?

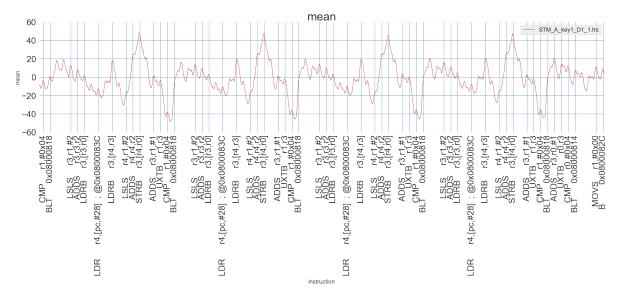

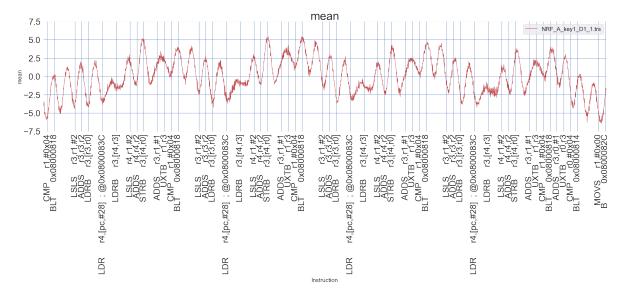

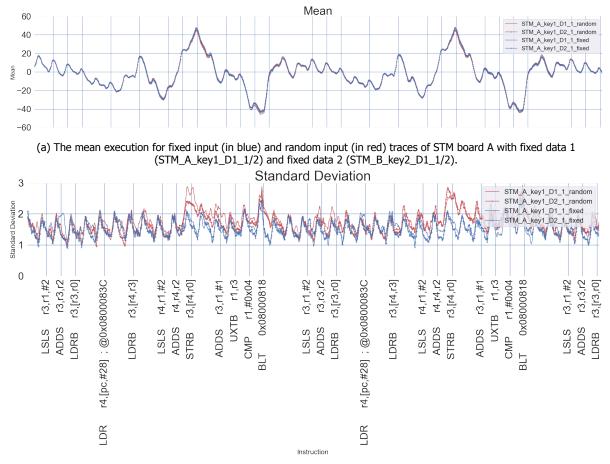

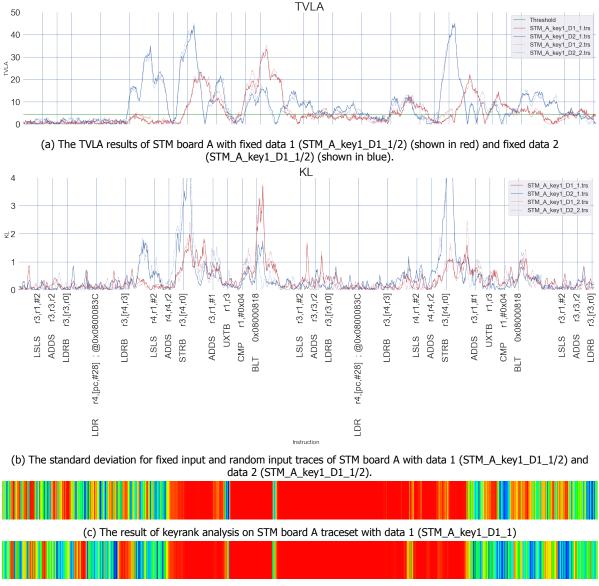

To answer these questions, we use **Statistical analysis** along with leakage detection methodologies to compare trace-sets at different levels. Statistical analysis is performed until the 3<sup>rd</sup> order, namely based on **mean**, **standard deviation** and **skew**, which gives us an idea about the probability distribution of the trace-set. **TVLA** methodology, **KL-Divergence** and **key-rank analysis**, are the statistical tools used to identify leaks in the trace-sets. Hamming weight model is used for profiling the trace-set to generate template models, which are used to comment on the source of leaks and portability of attacks. Doing so, this works

Figure 1.1: Different abstractions of device comparison over which the proposed methodology is used

provides a framework for extensive side-channel evaluation to compare software crypto implementations, highlighting the impact of micro-architecture on data leaks.

Devices belonging to the same family<sup>2</sup> have differences in data leaks. For a class of devices<sup>3</sup>, two board iterations differ from manufacturing process variations. The instruction traces<sup>4</sup> from devices of a class are of the same shape, though we observe each physical board to have its signature. The signature here is composed of the deviations in amplitude, specific to sections of instruction trace (ie-Board A has higher amplitude for the first half of the clock while executing ALU instruction compared to board B). Comparing two physical boards, we have consistency in how the difference of means varies along the instruction trace. The same behavior is observed for information leaks; the leakage results can be clustered based on the physical board from which trace-set is acquired (ie-board A shows higher amplitudes of leakage for a specific section of STR instruction); a board may be leakier for specific sections of instructions. The influence of key and input data on the results of leakage detection methodologies is presented to highlight the distinguishing features of these measures. Lastly, a methodology for selecting points of interest to profile templates for portability across devices with the same software crypto implementation is presented. This is the first known case of template attack across boards from different manufacturers, to the best of our knowledge, on an unsecured AES implementation.

The work done in this thesis has a wider application than the practical relevance for the

<sup>&</sup>lt;sup>2</sup>Devices with the same instruction set architecture, manufactured by different vendors

<sup>&</sup>lt;sup>3</sup>Devices from the same manufacturer with the same model number

<sup>&</sup>lt;sup>4</sup>trace acquired for the duration over which the instruction is being executed

above-mentioned embedded system engineer. First to the area of leakage simulators, which face the problem of portability across devices even with the same hardware architecture. ELMO [13] authors provide a leakage model for STM devices, though using ELMO on other Cortex M0 devices require profiling instruction triplets from the target device before use.

Secondly to the area of deep learning for SCA, as shown by X-DeepSCA [14] on the portability of template attacks across different physical boards. Unlike other works where profiling and attack traces are from the same target board, X-DeepSCA successfully create a DNN trained over multiple boards' traces to have a Cross-board SCA attack. The work done in this project takes one step further and can be used as input to the problem of creating an NN capable of attacking implementations from the same family of devices.

The remainder of this report is structured as follows: Chapter 2 provides an overview of hardware architecture, assembly AES implementation, side-channel leaks with discussion on leakage detection methodologies. In Chapter 3, the state of art research relating the leaks from devices to their hardware architecture is presented. The work done as a part of this project is presented from Chapter 4, where the procedure followed for acquisition and verification of data is presented. The effect of the chosen key and input data on the results of leakage detection methodologies is presented in chapter 5, the boards level variations and profiling templates is discussed in chapter 6. The properties of boards from both classes are compared in chapter 7, This report summarises the work and concludes in chapter 8.

# 2

# Background

This chapter presents the background information forming the basis of the work conducted in this thesis. To explain data leaks, the implementation of a processor is discussed in section 2.1. Followed by discussion on cryptography in section 2.2 and present assembly implementation of an unsecured AES algorithm in section 2.2.2. Section 2.3 explains the link between assembly code execution by the processor and data leaks in power traces used for side-channel analysis. The chapter ends by discussing techniques for identifying leaks in section 2.4.

## 2.1. Microprocessor

Instruction set architecture (ISA) or hardware architecture refers to register transfer level (RTL) micro-architecture of core elements to provide the instruction set capabilities. We will be focusing on the ARMv6-M Thumb instruction set implemented on the Cortex-M0 core for our work.

The Cortex-M0 is a 32-bit RISC processor developed by ARM that implements version v6-M of the ARM instruction set [15]. It is one of the most widely used embedded devices due to an efficient instruction set, affordable development costs with comprehensive development tools and support. The Cortex-M0 has a Harvard architecture with both 16-bit (THUMB) and 32-bit instructions and a 32-bit data path. It does not include a data cache or memory management unit (MMU) but instead comes with a pre-fetch buffer. The ARM6 has 37 registers; consisting of thirty-one 32-bit general-purpose registers and six additional status registers.

#### **2.1.1.** Instruction set

The instruction set determines the functional capabilities of a processor by specifying the list of all instructions that can be performed. The basic instructions that can be supported by Cortex-M0 core are presented below with a brief description of it's implementation.

- 1. **Data processing instructions** provide the functionality of manipulating with data, can be further divided into-

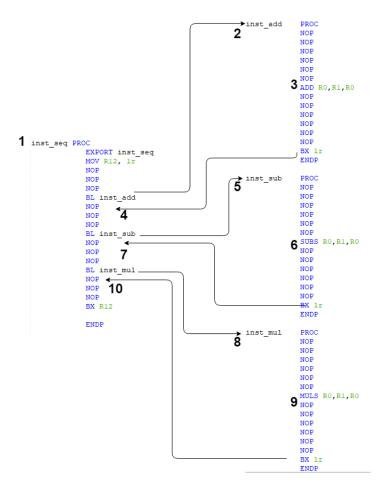

- (a) **Arithmetic instructions** basic mathematical operations of addition, subtraction and comparisons along with logical operations (EOR, AND). These instructions are implemented on the ALU represented with green color in figure 2.2. The first operand is read from the register file using the A bus; the second operand can be sourced from either register file or memory using data-in register via B bus.

- (b) **Shift instructions** Bit shift operations on data, logical and arithmetic. These are implemented using the barrel shifter represented with yellow color in figure 2.2.

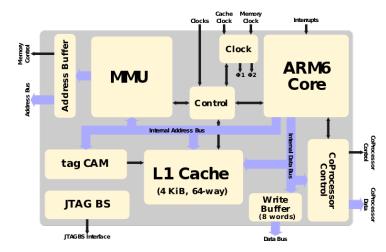

Figure 2.1: ARM6 hardware architecture [16]. The data busses are presented in purple and the control signals are presented in black. The micro-architecture of ARM6 Core has been presented in 2.2. It presents the different peripherals of an SoC and their interconnections.

(c) **Move instructions**-To move data between the register file represented with red in figure 2.2. Data moved across registers passes through ALU using A bus and is stored in the destination register from the ALU output bus.

Most implementations can compute the result of arithmetic and logical instructions in a clock cycle. Multiplication instruction is more complex to implement; the designers can decide between execution cycles needed to compute the result compromising area and power consumption. In Cortex-M0, the designers can choose the multiplier implementation amongst a 1 or 32 clock cycle implementation.

- 2. **Memory access instructions** implement the read/write of data between registers and memory. Since these instructions access the memory, which takes time, it is normal for these instructions to take more than one clock cycle to execute. These instructions consume considerably more power in comparison to the arithmetic instruction.

- (a) Load instruction- Can read data from memory to register

- (b) Store instructions- Can write data from registers to memory

Data loaded to the bus generated current in wires proportional to the hamming weight. Overwriting register values involves bit flips, which consume power relative to the old value on the bus. Hamming distance and hamming weight are the two widely used power models to profile the power consumption for predicting data.

Branch and control instructions- these instructions are used to control the execution flow of the program, enable code re-use and conditional execution. These instructions do not relate to data directly but rather allow controlling the address in the program counter, which determines the next instruction to be executed.

#### 2.1.2. Toolchain

For executing code on a processor, the compiler and the assembler convert the code from a high-level language to a machine-readable form called **machine code**. The compiler performs the function of understanding the program flow for all different code sections and optimizes it for size and speed by removing redundant operations. The assembler breaks down the high-level code to perform the required operations by a combination of assembly instructions taken

from the instruction set of the architecture. The assembly code is translated to a machine code by replacing the assembly instruction with their respective **opcodes**; and a **binary** file is generated that can be decoded and executed by the processor.

The machine code is composed of sequential instructions that are executed by the processor core. Each instruction of the machine code is decoded by the processor to determine the operation to be performed. The instruction can also contain the source of operands and destination for returning the result based on the instruction functionality. The opcodes are used by the processor to select the corresponding micro architecture peripheral based on the instruction type, and it also configures the peripheral for executing the specific instruction by the generation of respective control signals.

The compiled and linked machine code is called a binary file because it consists of 1s and 0s, directly written to the program memory when the board is flashed. On booting, the system starts fetching the instructions and executing them from memory.

#### 2.1.3. Micro-architecture

Figure 2.2: This figure shows the micro-architecture components needed for implementing arithmetic and memory instructions. The purple arrows depict the flow of data between the components. When an instruction uses secret-key data, it is loaded on the data bus to be used by the component performing the operation. internal control logic has not been represented in this figure; the black arrows represent the control signals applied to the core. Sourced from [16] and added color code with instruction labels

Micro-architecture refers to the specification and interconnection of different semiconductor peripherals, including registers(r0-r15), Arithmetic logical unit (ALU), multiply and accumulate (MAC) that provide the functionality to the core instruction set. Each micro-architecture peripheral is implemented by combinational logic gates to provide the operational functionality and routing circuits to transfer the data. One peripheral can support the execution of multiple instructions; when an instruction is executed, the decoded opcode is used to select the respective micro-architecture element and activate it in the configuration required for performing the requested instruction.

There have been constant optimizations in design at the micro-architecture level for speed and utilizing the silicon area effectively; these optimizations can be in the form of multistage pipelines and resource sharing. The design specifications are mostly confidential as they are trade secrets. The device's functional specifications are provided to enable the developers to design applications without the need to know design specifications.

The arithmetic and logical instructions operate solely on registers. A barrel shifter located between the register file and the Arithmetic-Logic Unit (ALU) allows one to combine an ALU operation with a shift or rotation of the second operand. Most ALU instructions execute in one cycle; the only exceptions are MUL(multiply), DIV (divide), and operations targeting the program counter.

The core functionality of combinational logic gates and routing circuits is implemented by switching transistors. The switching of transistors gives rise to leakage current (the usage of term leakage here is in electronics terms) and electromagnetic emissions, which are recorded to perform side-channel analysis.

#### 2.1.4. Subsystem implementation

This section will link how the instruction set and the micro-architecture implementation work to execute the machine code.

| Fetch       | Decode      | Select   | Read     | Shift | alu | Write    |

|-------------|-------------|----------|----------|-------|-----|----------|

| Instruction | Instruction | Register | Register |       |     | Register |

Figure 2.3: This figure shows the implementation of 3 stage pipline in ARM V6 core.

Cortex M0 has a three-stage pipeline, which implies three different instructions are being implemented in fetch, decode, and execute stages of the pipeline. To optimize the execution for speed, the memory operations are assigned to sub-peripherals to perform reads and writes, while the processor core can be executing other operations. Branch prediction is implemented where one of the alternative instructions is speculatively executed and eventually discarded if it turns out that the speculation was wrong. Store to memory instructions (e.g., str) are buffered and executed in one cycle, whereas load from memory instructions (e.g., LDR) introduce a wait-state.

Power trace shows the cumulative effect from all pipeline stages of the processor. Relating effects in power traces to instructions is problematic because the instruction being executed does not need to be the cause for leaks.

The memory location of instructions also plays a role because instruction pre-fetch works on preset word lengths. More than the requested data is cached to optimize for speed if the next instruction requires data in the current memory address's spatial vicinity.

Due to the reasons above, the methodology of side-channel analysis treats the target device as a black/grey-box and focuses on hiding/extracting sensitive data.

### **2.2.** Cryptography

Cryptography has enabled the transfer of sensitive information while keeping it hidden from snooping third parties. Cryptography is the field of studying encryption/decryption protocols to implement secure communication by hiding the real content of data by using a secret-key. Though the secrecy of the message is dependent on the secrecy of the key.

Cryptography provides us with multiple cipher protocols for different use cases; the two broad classifications can be made as symmetric and asymmetric based on the nature of keys. Symmetric ciphers use the same secret key for encryption and decryption of data; AES is the current widely used block cipher introduced in 1998.

Our work focuses on recording power traces while the processor was executing AES encryption on 16-byte data. We discuss the methodology of AES in detail in the next section.

#### 2.2.1. AES algorithm

AES stands for Advances encryption standard announced by National institute of standards and technology in 1998 [17]. AES is a block cipher whose key size can be amongst the three options of 128, 192, or 256. The applied key size determines the number of transformation rounds applied to the input data. AES encryption computes the cipher text from plain text and the secret key by using four significant operations on the 16-byte data represented in a 4x4 matrix.

- 1. **Key expansion** The secret key is expanded in length from which sub-keys are of 128 bit are selected for each round following the key schedule

- 2. **Add round key** 16 bytes of data are XORed with the 16 byte round key obtained from crucial expansion.

- 3. **Intermediate rounds** In each of the intermediate rounds, the listed operations are performed. *Based on the chosen key size, the following operations are repeated 9, 11, or 13 times for key lengths of 128, 192, and 256 bits, respectively.*

- (a) **Substitute Byte** The input bytes from the plain text are substituted based on a fixed table or s-box, and we have a 4x4 matrix with substituted values.

- (b) **Shift Rows** The 4x4 matrix rows are shifted.

- (c) **Mix Columns** This operation applies a mathematical transformation on a column of 4x4 matrix (4bytes) and outputs 4 bytes of data to replace the column.

- (d) **Add round key** 16 bytes of data are XORed with the 16 byte round key obtained from key expansion.

- 4. **Final round** Operations are the same as other rounds except for Mix Columns, we get the ciphertext as output from Add round key operation.

- (a) Substitute Byte

- (b) Shift Rows

- (c) Add round key

There can be multiple ways of implementing a specific function; for example, using lookup tables is the simplest means of S-box implementation, though it is unprotected from sidechannel attacks. We discuss an unprotected AES implementation in the next section.

#### 2.2.2. Assembly S-box implementation

In this section, the assembly code implementing the S-box operation used in our implementation is presented. This assembly code is generated by compiling Tiny-AES-C<sup>1</sup> library using Keil  $\mu$ 5 compiler. This is an unprotected AES implementation that is used to acquire power traces for our experiment. The background color of assembly instructions determines the type

<sup>&</sup>lt;sup>1</sup>https://github.com/kokke/tiny-AES-c

of instruction as discussed in 2.1.1 and relates to the micro-architecture peripheral of similar color in figure 2.2.

The S-box implementation is unmasked and uses a look-up table stored in memory for performing substitutions. the relative addressing for the byte in operation is loaded in R3 with instruction LDRB r3, [r3, r0] address of look-up table is loaded in R4 with the instruction LDR4, [pc, #28]; @0x0800083C, and finally the substituted S-box value is loaded to R3 with the instruction LDRB r3, [r4, r3]. The intermediate instructions of LSLS and ADDS are used to calculate the memory address where the result of the substituted byte will be saved by instruction STRB r3, [r4, r0].

| SubBytes                                       | •                             |

|------------------------------------------------|-------------------------------|

|                                                | LSLS r3,r1,#2                 |

| (*state)[j][i] = getSBoxValue((*state)[j][i]); | ADDS r3,r3,r2                 |

|                                                | LDRB r3,[r3,r0]               |

|                                                | LDR r4,[pc,#28] ; @0x0800083C |

|                                                | LDRB r3,[r4,r3]               |

|                                                | LSLS r4,r1,#2                 |

|                                                | ADDS r4,r4,r2                 |

|                                                | STRB r3,[r4,r0]               |

Figure 2.4: c code implementing substitute byte operation (left); Assembly instructions sequence to implement the c code (right); **Colour code**: Yellow-Barrel shifter; Green-ALU; data-in/out registers-orange

To evaluate an application for security, we need to identify code sections that involve manipulation with sensitive data. This reduces the code section to be evaluated significantly; care should be taken to ensure the best coverage of the attack surface, which requires system knowledge. There have been attempts to remove this burden of security evaluation from the developer by designing leakage simulators to identify data leaks.

### **2.3.** Side-channel analysis

Deducting information about the internal working of a system without interacting with it directly, rather observing on its interactions with the external environment is a side-channel. The side-channel signals are generated as a result of operating the device; they can be of different types such as power [5], electromagnetic emissions [18], or even sound [19]. Sidechannel analysis involves processing these signals to deduct useful information that can be used to attack them.

As discussed in section 2.1, a processor provides its functionality by the combinational logic gates implemented at a micro-architecture level. Logic gates provide their functionality by switching transistors in the physical layer, which is done by generating a depletion region in the semiconductor gate. These processes at the semiconductor level occur due to electrons' movement in the circuit, which gives rise to leakage current and electromagnetic emissions.

We can record these side-channel signals from a device while it is performing operations by using a probe to convert the signal to a voltage domain that can be measured by an oscilloscope. The EM traces are recorded by positioning an EM probe over the silicon chip, which measures the EM field passing through the probe's aperture. To record power traces, we can add a tap on the device's power line in the form of a current probe or by measuring the voltage across a register. In power traces, we can observe the collective effect of all the micro-architectural components of the processor. In contrast, in EM analysis, it can be possible to perform localized measurements by selectively positioning the probe over the core. The work done in this thesis is has been applied to power traces; from here on, when we refer to trace, we mean power traces.

Side-channel can be distinguished into two sub-categories depending on the type of analysis performed. In **Simple power analysis (SPA)** the timing differences are used to make deductions about the operations being performed, while in case of **Differential power analysis (DPA)** a amplitude deviations are compared from a collection of traces to comment on the operand data [12]. The power consumption of a device can be classified in terms of static power and dynamic power consumption. Static power refers to the constant power consumed by the chip circuitry, while the dynamic power consummation originates from the working of logic circuitry in the chip. DPA side-channel attacks focus on the dynamic power component because it has a strong input-dependency to accumulate information about a secret value manipulated by a device. Trace-sets with varying input data (IE-Fixed vs. Random) can be compared to distinguish between the static and dynamic power traces.

#### **2.3.1.** Simple power analysis

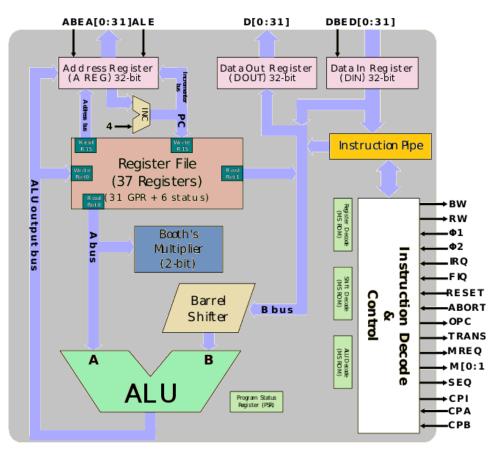

When a visual comparison of power traces is used to deduct information about the executed operation or branch, it is termed simple power analysis (SPA) [12]. We present a code snippet in figure 2.5 that executes *Addition* (ADD), *Subtraction* (SUB) and *Multiplication* (MUL) instruction padded between NOP instructions to keep the processor processor and pipeline stages to be in idle state.

Figure 2.5: This figure shows a basic assembly code template that was created in order to to perform a visual inspection of how corresponding assembly instructions will be perceived in power traces. The label numbers in bold can be used to correlate the executed instruction to sections in power traces

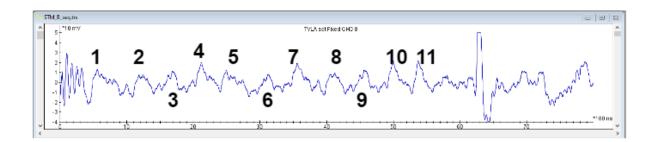

A labeled power trace for executing a basic assemble code (shown in figure 2.5) on a STM32 is presented in figure 2.6. The control flow of program shown with arrows can be linked to different sections of power traces with the numbered labels. A the steep increases

Figure 2.6: This figure the acquired power trace on executing the code snippet in figure 2.5 on a STM320f051 board. 1 marks the point where control jumps into inst\_sec procedure

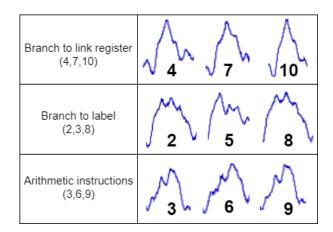

in current consumption on executing branching operations labeled by 1, 2, 4, 5, 7, 8 & 10. It is possible to distinct between *Branch to label* (BL label) instruction marked with 2, 5 & 8 and *Branch to link register* (BX lr) instruction marked with 4, 7 & 10 by the power traces of the instructions. In the same manner, it is possible to profile different instructions; the similarities in trace of arithmetic instructions labeled by 3, 6 & 9 can be observed, pointing towards the use of same micro-architecture subsystems for executing the instructions. For easier comparison, we have extracted the sections of the power trace and presented it in figure 2.7.

Figure 2.7: Signature of individual instructions shown in figure 2.6

By identifying the executed instructions from the power trace, an adversary can deduct information about the underlying implementation and use that knowledge to attack. Timings attacks are a subset of simple power analysis; they identify non-time constant executions and use them as a guessing oracle to observe how the execution changes with input [5].

Tanking an example of a password verification implementation that checks if the provided input is valid by iterating over input bytes sequentially. The number of iterations taken to compute the result needs to be balanced, or else an adversary can use the device as a guessing oracle. By providing different inputs for the first key byte, an attacker can compare traces to find the input that leads to the execution of a different code branch, implying the first byte passed the check. The above process can be applied iteratively for each password's byte.

Timing attacks are the most simple form of side-channel attacks; they can be mitigated by having constant time executions and balanced branches. We will now go over Differential power analysis, which can be applied in cases where simple power analysis cannot be used because of counter-measures used in the implementation.

#### **2.3.2.** Differential power analysis

When the branches are balanced and the intensity of leakage relative to noise is less, statistical tools are used on a large number of samples to deduct leaked information performing by Differential power analysis [12].

As discussed in the simple power analysis section, the instructions can be identified based on their power trace. We observe minor deviations in these power traces that originate from the instruction's data. These deviations are observed because reading and writing data from the data bus involves overwriting the old data with new data by toggling bits. These toggling of bits gives rise to leakage current whose effects we observe in instruction traces as small deviations. It is possible to profile the data from multiple traces with known data to create a profiling model that can be used to identify the underlying data from a power trace. By profiling trace-sets with mathematical and deep learning tools, we can accurately predict the secret-key data used to perform operations.

Due to various hardware cores available and the differences in the execution of software, it imparts too many variables to obtain a generic profiling methodology. The profiling has to be done specifically to the target device and software implementation for the reasons mentioned earlier. Moreover, two identical devices can significantly differ during manufacturing in the silicon layer, which induces significant differences between the two devices' power traces. Hence, for most cases, profiling has to be done on the same device, which is also the target. This has been a widely discussed topic in side-channel research to create machine learning networks capable of generating portable profiling models.

## **2.4.** Leakage detection methodologies

Using input/output correlation is the most basic way to check for data leaks [20]. Over the years more advanced differential power analysis attacks have been developed exploiting different sources of information from the power trace. So statistical tools are used to find aberrations in the probability distribution function of trace-sets; the variation in probability distribution implies the source processes are different in some form and can provide information about the system.

The statistical tools can be used for different types of tests [21] The test can be classified as non-specific or specific, depending on the set of traces being compared. In the case of a non-specific test, a set of traces with a random inputs are compared against a set of traces with fixed input. In case of specific test, two sets of traces with the same fixed key but different fixed inputs are compared for differences in probability distribution function. If the probability distribution for the two sets, differs significantly the time samples can be classified as leaky [22].

The statistical tools of TVLA and KL divergence have been used in this work to check for leaks, are discussed in the sections ahead.

#### 2.4.1. Test vector leakage assessment

TVLA methodology is a set of guidelines using Welch's T-test to check for a significant difference in the data set's true means [23].

#### T-test

A T-test is a statistical tool that tests if the null hypothesis specifying that the true mean of two distributions is zero. If the null hypothesis is proven false, it implies that the two distributions result from two distinct processes.

We calculate the **t-statistic** for two distribution *P* and *Q*, as follows

$$t = (mean(P) - mean(Q)) / \sqrt{(variance(P)/N_P) + (variance(Q)/N_Q)}$$

where  $N_x$  is the number of samples in the set x.

This *t* value is compared with the threshold value, which is computed using the confidence level (denoted by  $\alpha$ ) of the test. If the t-statistic value is higher than the threshold, we reject the null hypothesis, implying the true mean of underlying distributions is not the same. Though the t-statistic is less than the threshold, we cannot say that the underlying distributions have the same true mean.

#### Confidence level and effect size

The confidence level is used to control the type-1 (false positives) and type-2 (true negative) error rates for rejecting the null hypothesis. It tells us if the difference of means between the two sets is big enough to suggest the true difference for the two data sets is non-zero. The threshold value for the T-test is based on the determined significance level  $\alpha$ . When following the TVLA methodology, this threshold is set to 4.5 for a confidence level  $\alpha = 0.00001$  [24].

Two sample populations are created at index locations being tested for leaks. If the result of the t-statistic is higher than the value of 4.5, we determine the index location be leaky. TVLA methodology emphasizes verifying the results by performing a repetition with second set of traces since it is a statistical tool.

#### **2.4.2.** Kullback–Leibler Divergence

Kullback–Leibler Divergence is an information theory metric that quantifies the difference between two probability distributions. It has traditionally been used in classifying the similarity in two sets. In the field of side-channel it has been used by J Park et al. for creating a side-channel instruction-level disassembler [25], which can generate assemble code from a single power trace. In our work we use it to quantify the level of dissimilarity in trace sets and contrast it with the sections of trace with leaks.

Let P and Q represent two probability distributions defined on the same probability space X, then KL Divergence of set P with respect to Q is calculated as

$$KL_{(P||Q)} = \sum_{x \in X} P(x) \lg(P(x)/Q(x))$$

KL divergence has a shortcoming that it is an asymmetric measure and cannot be used to measure the distance between two probability distributions.

$$KL_{(P||Q)} \neq KL_{(Q}||P)$$

The lowest value of KL-Divergence between two sets can be zero, which would imply both the distributions are identical.

$$KL_{(P||Q)} \ge 0$$

By using KL divergence to compare trace sets we quantify the differences in probability distribution function of trace-sets, to observe the behaviour for different instructions. By comparing the results of KL-divergence with leaks observed at that time sample, we comment on the viability of using KL-Divergence as a metric to test for leakages.

## **2.5.** Key-rank analysis

To compare two implementations for security a unified methodology for the analysis of sidechannel key recovery attacks is presented by FX-Standaert et al. [26]. Key-rank denotes the position of the correct key in the key guessing vector. Key guessing vector is a vector of all possible keys sorted from the most likely to the least likely. In our implementation operations are performed on each byte of data, so the key guessing vector consists of all 256 values of one byte. GE states the average number of key candidates an adversary needs to test to reveal the secret key after conducting a side-channel analysis.

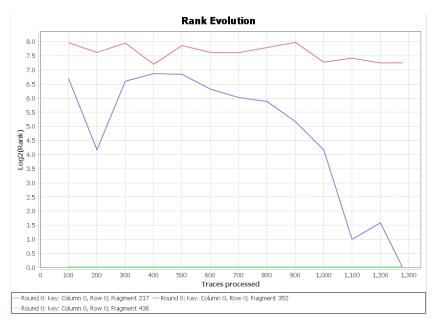

Key-rank analysis is effected by the number of traces used for analysis. Key-rank evolves as more traces are added, if the correct key value is found to be leaking the key-rank converges towards 1. The key-rank evolution for 3 time sample from STM trace is shown in figure 2.8. The time sample plotted in red can be classified to have no leaks as the log(keyrank) does not converges to 0. The time sample plotted in blue converges to 0 after 1000 traces, so the correct key does leaks. The time sample plotted in green shows high intensity of leaks as the correct key was found in less that 100 traces and it always stays at 0.

Figure 2.8: Rank evolution on STM device; plot for LDRB r3, [r3,r0] (red) with no leaks; LDRB r3, [r4,r3] (blue) with low intensity leaks, the correct key is found after 1k traces and LSLS r4,r1, #2 (green) with high intensity of leaks, the correct key is found in less than 100 traces

## 2.6. Template attacks

Template attacks are a subset of differential power analysis as described in section 2.3.2, first works were performed by Chari et al. dating back to 2003 [27]. The principle of template attacks is to classify traces according to the leakage model and using Bayes's theorem to estimate the key data being used. The most widely used leakage models are hamming distance on 1 byte data which classifies into 9 classes or directly into 256 classes based on the byte value. Template consist of two phases, being profile phase and attack phase.

Profile phase involves classifying the traces data at the selected points of interest (POIs) to generate a leakage model. By using a known key value for the profiling phase, the intermediate value of operation can be computed and used to classify the traces. The number of POIs selection as well their location in time determines the quality of profiled template [28]. The

template is generated using probability distribution of different sample classes based on the leakage model. The closer the leakage model is to the actual power consumption the more effective is the attack.

During the attack phase the acquired power trace is compared against the template to characterize the intermediate value being computed upon. Sample from the attack traces are compared with the temple to determine the most probable key value. For a good attack it is necessary to build a template that has enough samples for each class of leakage model. Selection of leakage model influences the strength of attack, implying it will influence the number of traces needed to attack successfully [29].

# 3

# **Related Work**

This chapter discusses the existing works, in the domain of side-channel analysis relating the effects of hardware to leaks. First, the works presenting micro-architecture sources of leaks are presented. Followed by a discussion on the portability of works preventing micro-architecture leaks.

## **3.1.** Leaks from Micro-architecture

To attack a cryptographic implementation on a digital system, a good understanding of the system's underlying physics can provide an adversary with essential clues. At the same time, this knowledge is essential for a developer to assure the system's security. Hardware designers implement optimizations which can have unintended consequences leading to leaks from branch prediction [30] and instruction cache [31]. Data leaks can be classified based on their source as follows-

- Direct value leaks- Operand value leaks because of current consumed by bus to transfer data

- 2. **Data-overwrite leaks-** Overwriting of data in register consumes power relating to the hamming distance of old and new value

- 3. Circuit level leaks- Originate due to coupling effects induced by current-carrying wires

**Direct value leaks** where the operand value leaks can be prevented by masking, though the system can still be exposed to data-overwrite and circuit-level leaks [32]. Y. Le Corre et al. discuss leaks due to pipeline stages [33] which is discussed in section 3.1.1; M. Renauld et al. investigates the significance of interconnects and coupling [34] discussed in section 3.1.2.

#### 3.1.1. Pipeline leaks

Y. Le Corre et al. have presented A HDL level analysis of Cortex M3 core to explain the concepts used for building a Micro-Architecture power simulator (MAPS) [33]. Cortex M3 implements the ARM7 micro-architecture, the successor of the ARM6 micro-architecture used by Cortex M0. Thumb instructions used in crypto implementation use the basic functionality of micro-architecture peripherals, which is expected to be similar for ARMv6 and ARMv7; hence we use their findings to support our observations.

Y. Le Corre et al. analyzed the 3 stage pipeline implementation in ARM architecture and revealed the sources of leaks. They determine the presence of ra and rb register, located

between the register file and the ALU, being used to isolate the decode stage from the execution stage. For an instruction in the decode stage, the operand data is loaded into the co-responding registers; in the subsequent cycle to execute the instruction, the peripheral sources operand data from the intermediate ra and rb register. These intermediate registers combine the data from subsequent instructions, which is the source of data leakage. Loading of data to a register consumes power corresponding to the hamming distance <sup>1</sup> between the old value and new value, which leads to leaks on pipeline registers and register-reuse.

Operations at the hardware level involving the writing of a value to a register are a potential source of data-overwrite leaks. Y. Le Corre et al. determine the intermediate registers used as a boundary for the pipeline stages to be a source of data-overwrite leaks over subsequent instructions. They back their findings in the paper from experimental results on ALU and STR instructions.

#### 3.1.2. Variability in nanoscale devices

M. Renauld et al., in their work [34] investigate the significance of variability in sub-micron technologies for cryptographic implementations. As the CMOS technology is scaled down, the static power consumption increases (energy consumed, even when no computation is performed), reducing dynamic power contribution. Device variability is becoming more significant due to manufacturing process variations making it challenging to determine a leakage model valid across physical board iterations. The tight integration of microelectronic circuits to minimize the area footprint increases the coupling between their interconnected parts; current-carrying wire can induce capacitance effects in its surroundings, leading to variations in path-delays. These path-delays are observed as **glitches** and leaks are termed **circuit-level leaks**.

To conclude devices have leaks from multiple micro-architecture sources; with the increase in process variability, different micro-architecture sources' contribution can vary across physical device iterations. Due to device-specific variations, the sample locations (from power trace) for generation/application of leakage models can vary. We test out the effects of device variability by generating and testing validity of template across different physical devices.

## **3.2.** Template attacks and machine learning

Template attacks were first introduced by Chari et al. in 2002 [27], and since then these attacks have been recreated for breaking various hardware and software implementations [35, 36]. Template based DPA attacks have been considered one of the most powerful attacks from information theoretic point of view and have shown success in breaking masked implementations also [37]. Earlier works in template attacks used the same physical device for profiling phase and attack phase, now there is a move towards working on portability of these attacks.

The major problems in porting template attacks arises from the fact that side-channel traces have noise, being influenced by environmental factors (temperate, power source) during acquisition which effect the acquired traces. The second more prominent problem arises from the presence of inter-device variations, which make it difficult to have a standard leakage model for a class of target device. The problem of portability has been approached from different directions, by using algorithms to normalise the drift in acquisitions [38]. The work done by X-DeepSCA: Cross-Device Deep Learning Side-Channel Attack [39] has been successful in creating a model that can be ported across devices, by using traces from multiple devices. Work done by S. Bhasin et al. has evaluated the portability for profiled side channel attacks and has shown the advantage of using multiple device models for portability of attacks [40].

<sup>&</sup>lt;sup>1</sup>number of positions at which the corresponding bits are different

The strength of attack is greatly influenced by the quality of profiled template; the number of features (POIs) used for creating template, and the time samples selected as POI and the leakage model used have a big impact in the quality of template. The work done by S. Picek et al. has investigated the use of machine learning with different tuning parameters and have compared it with the conventional template attacks [41]. Their work shows machine learning can outperform the conventional template attacks when applied properly.

#### **3.3.** Portability of works preventing micro-architecture leaks

Developing a secure software implementation involves determining the cause of leakage and fixing it until no more leaks are found. Advanced tools for simulating and detecting leaks from hardware are presented in this section. These tools provide a good means to test for data leaks, though their limitation which have prevented these their wide use are also presented.

Clearing the registers before loading the subsequent value can prevent data-overwrite leaks; this applies to both register and intermediate registers [42]. M. Renauld et al. have developed Micro-Architectural Power Simulator (MAPS) [34], which takes the generated binary and simulates the data flow through all the registers in the pipeline to predict data-overwrite leaks. To add support for another target, analysis of HDL schematic is required, this information is not always available.

There is no easy way to predict circuit-level leaks as the circuit delays influence them at the gate level and induced capacitance effects from wires. The effects of circuit delays can be simulated on the RTL schematic but are computationally complex, and RTL schematic is not always available. It will still not include the leaks due to capacitance effects. D. Mccann et al. have developed ELMO by creating leakage models of instruction triplets (Cortex M0 has 3 stage pipeline) for basic crypto instructions [13]. Their methodology encapsulates detection of circuit-level and data-overwrite leaks, but adding support for new targets is labour intensive. The complexity of modeling increases with the number of pipeline stages in the target processor. There are further works that replace leaky assembly instructions with a sequence of assembly instructions providing the same functionality at the cost of executing additional instructions [43, 44].

Based on the type of leaks, appropriate remedial action can be applied. Understanding the data-flow at the micro-architecture level and clearing the register value before subsequent writes may prevent data-over write leaks. Circuit level leaks are more difficult to prevent as specific requirements need to be laid down at the RTL design stage to prevent data leaks through glitches or be mitigated at the software level using alternate instruction sequences. Solutions have been proposed at the hardware level to develop augmented instruction set architecture (aISA) specific to secure operations. However, it needs to be incorporated into the manufacturer's design and it costs area and design overheads [45].

RISC hardware architecture provides a separation between the instruction set and its microarchitecture implementation, providing manufacturers' flexibility for designing cores optimized for specific requirements. Having the same instruction set allows portability of application across devices, though differences in micro-architecture can impact the implementation's security. This presents the problem in the portability of crypto-implementations across devices with the same instruction set since the hardware implementation of instructions at RTL level vary; so the countermeasures used have to be evaluated specific to the device.

# 4

# **Experimental Setup**

In this chapter, we go over the two classes of boards use for our experiments in section 4.1, followed by the acquisition setup used for collecting power traces from the target boards in section 4.2, We discuss how to check if the raw traces are suitable for performing comparisons in section 4.4 and end the chapter by explaining the procedure for making the traces from two different classes of board comparable in section 4.5.

## 4.1. Target devices

Two devices designed on Cortex MO core were selected for this study because comprehensive literature is available and Cortex MO is the most basic 32-bit processor core, with a wide application in embedded and IoT devices, making it the right candidate for our work. The future generations of ARM cores have been designed around the Cortex MO.

Embedded devices are designed around a processor core by semiconductor manufacturers to create application-specific systems on chip (SoC). The distinction between a processor core and an embedded device is essential. When the term device is used, it implies the specific implementation of a processor core, the features of the device are dependent on the manufacturer's design choices.

Our work explores the impact of hardware architecture on leaks observed from power traces. The target devices devices from different manufactures have different design specifications but are built around the same hardware architecture (processor core). Such comparison can provide us with information for relating data leakages to the micro-architecture effects in physical layer.

The target devices chosen by us for our experiments are-

- 1. STM32F051: We used two STM32 boards for our experiments, we refer to them as  ${\tt STM}\_{\tt A}$  and  ${\tt STM}\_{\tt B}.$

- 2. NRf51: We used two NRF boards for our experiments, we refer to them as NRF\_A and NRF\_B.

Signal to noise ratio in the acquired traces significantly impact the results of side-channel analysis. Leakage detection methodologies are discussed in 2.4 are dependent on the probability distribution function of the leaks. The power traces should have a high signal to noise ratio to get good results from the leakage detection methodologies.

Based on the target device and the acquired traces, getting a high signal to noise ratio might require reduction of interference from the board circuit circuitry. Hardware modification

can be done on the board circuitry after studying the schematic for the same. Care has to be taken when performing physical modifications, not to impact the performance or execution of the processor core.

In the following section, we present the specifications devices from STM class (4.1.1) and NRF class (4.1.2) along with the hardware modifications made before moving on to acquiring traces.

#### **4.1.1.** STM32F0 Discovery

Figure 4.1: This figure shows the STM32F051 development board along with the hardware modifications, used to collect traces on AES encryption. The coupling capacitors C18, C19, C20 and C21, highlighted by a red circle in the image, were removed. To isolate the target MCU from the effects of interface MCU, it was powered from the current measurement port by the pin highlighted by the yellow circle. The target is powered by a 3.3V supply with the current probe attached in series. The interface MCU is powered by the USB.

STM32 Discovery is a development board by ST Microelectronics for the STM320f051 device, which consists of an interface MCU on-board that enables easy flashing and debugging using ST-Link over USB. The development board also offers a PPI port that connects a current probe in series to measure the current consumption. The hardware modifications made on the device will now be discussed.

On inspection of the STM board's schematic, we observe that interface MCU and the target device share the same power source. Even though the PPI port is used to measure the target MCU's current, by sharing the same power source for both MCUs, the power line becomes unstable, resulting in more noise in the acquired signal. The target MCU is powered by an external 3V3 supply from the current measurement port while having a current probe in series, while the interface MCU is powered using the USB port. This way, we isolate the target MCU on the power feed from the effects of interface MCU, which is now powered by USB.

The coupling capacitors attached to the power pins of target MCU are removed; they act as a low pass filter on the input power supply to target MCU. Filtering can lead to loss of information in the power traces at the cost of low-frequency noise in the signal. The coupling C18, C19, C20 and C21 are removed, as shown in figure 4.1 without affecting the device's performance.

#### 4.1.2. NRf51 Development kit

NRf is a SoC designed for Bluetooth low energy application based on Cortex M0 running at 16MHz. We choose this device to have a comparison for STM device since NRf51 is a low power device using a fraction of the power of the STM board even though both the devices are

Figure 4.2: This figure shows the NRF51 Development kit 1 board on which AES implementation was run. The board was powered from the external power supply port highlighted with a yellow circle by a 3.3V supply. We did not have to make hardware modifications for this board as the interface MCU is isolated by default on powering the board from an external supply. The current probe was attached to the current measurement port highlighted by a red circle in the image

designed on the Cortex MO. NRF51 development kit also offers a current measurement port that can be enabled by cutting solder bridge SB9. No coupling capacitors were found on the power-line circuitry. The target MCU is already isolated from the interface MCU when the board is powered externally using 3v3, so we do not need to make any hardware modifications.

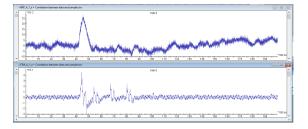

Since NRF51 is a low power electronic device, Picoscope 3000 has the lowest resolution of 39 µAAmps, but it cannot record good traces due to quantization noise. The current measurement signal is passed via a signal amplifier to improve signal gain, as presented in figure 4.4.

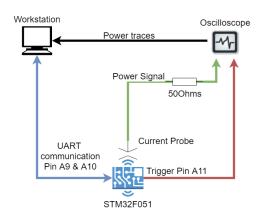

## 4.2. Acquisition Setup

The prepared boards are now ready to acquire the traces. We connect the current probe to the PPI port on the board. The PPI port is in series to the target MCU's power line and can be used for taping into the current consumption of the same. Using a current probe induces a phase shift; hence we add an inductance of 50 OHMs before the signal is recorded from the oscilloscope. Riscure Inspector <sup>1</sup> is used to acquire the power traces; the acquisition setup used are presented in the image. The trigger pin on the board is connected to the channel B on the oscilloscope, which starts recording measurements from channel A on detecting trigger signal. We use a USB UART cable for connecting to the UART pins on the board from USB, the serial communication to the device happens over this cable.

The specific pins used for STM32 and NRf are shown in figures 4.3 and 4.4 respectively. The specifications of the tools used have been presented below.

#### Acquisition software

**Riscure Inspector Version:** 2019.2.1 Riscure inspector is a side-channel analysis tool that enables acquiring traces from target, while combining it with input (plain text) and the output (cipher text) from target device. It incorporates a signal processing toolkit to apply preprocessing on the acquired traces along with modules specific to SCA (i.e. TVLA, key-rank analysis, template attacks).

<sup>&</sup>lt;sup>1</sup>https://www.riscure.com/security-tools/inspector-sca/

Figure 4.3: Acquisition setup used for STM board. Pin A9 and A10 are used for UART Rx and Tx respectively, pin A11 is used for connecting the trigger signal. Current probe is attached to the oscilloscope though a 50  $\Omega$  impedance

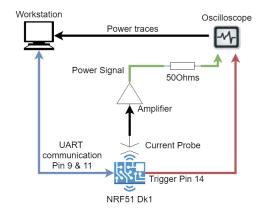

Figure 4.4: Acquisition setup used for NRF board. Acquisition setup used for STM board. Pin 9 and 11 are used for UART Rx and Tx respectively, pin 14 is used for connecting the trigger signal. A signal from the current probe is passed through a signal amplifier because NRF51 is a LPE device, in order to increase the gain of the signal. The power signal is fed to the oscilloscope via 50  $\Omega$  impedance

#### Oscilloscope

Model: Picoscope 3000 Sampling rate: 500MHz Range:  $\pm 50mV$  Resolution: 8 bit

#### **Current Probe**

Model: Risc-CP189

### **4.3.** Preparing portable software implementation

Our work is focused on comparing power traces across different target boards, so both the boards must be executing the same instructions in sync. Since the boards from different manufacturers will have a different project for configuring and running the startup script, we have to make sure the region of code between the triggers is identical for both targets. The same compiler was used to generate the binary files, and the disassembly of code was compared to ensure that the execution would be the same.

An unmasked implementation of AES128 was flashed on both target boards. The execution sequence is explained below.

- 1. On boot/reset, a startup code runs on both target devices, which sets the system and peripheral clocks. This step differs for two boards as follows

- NRf51: works at a fixed clock speed of 16Mhz.

- STM: device supports operation over a wide clock frequency. The startup code sets the clock frequency to 16MHz.

- 2. Core and UART drivers are initialised

- 3. System tick interrupt is disabled

- 4. Control enters main () and an AES object is initialised with a preset key

- 5. Enter infinite loop, repeat the steps below

- (a) Receive 16 bytes of data over UART.

- (b) Set trigger pin low. this signals the oscilloscope to start recording the measurement.

- (c) 16 bytes of data is encrypted using an unmasked implementation of MBED-AES

- (d) Encrypted ciphertext is sent back over UART

By setting the clock frequency of both the board to 16MHz, both the target devices can be configured for identical execution. Identical execution timings are achieved at the clock cycle level for the uploaded code, which is an important criterion for comparing power traces across different target devices. Only the required peripheral drivers of UART were initialized to keep the effects from core peripherals at a minimum in the recorded power traces. The system tick interrupt was disabled to prevent switching of program control in the middle of AES encryption operation since it would lead to inconsistencies in execution traces.

On successfully receiving 16-bytes of data, the trigger pin is set to high, which signals the oscilloscope to start recording the power measurements. After setting the trigger pin high, program control enters the <code>AES\_ECB\_encrypt</code> function, which computes and returns the ciphertext as output, which is sent back to the workstation over UART. The software projects for both the devices were created and compiled using Kiel  $\mu$ Vision5 to have a consistent development tool-chain.

The AES library used is an insecure implementation from MBEDtls.

## **4.4.** Acquired traces

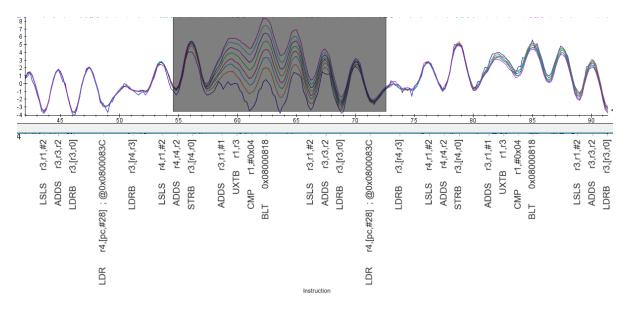

(c) Legend for the colour overlays to represent the operation being executed.

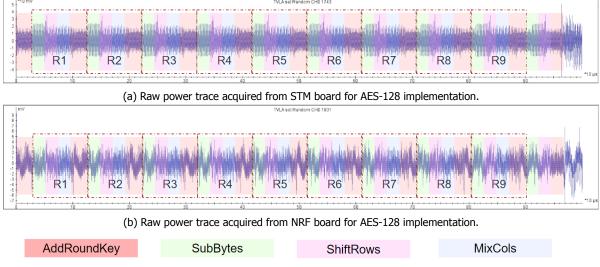

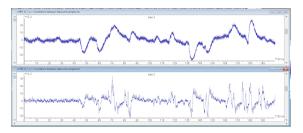

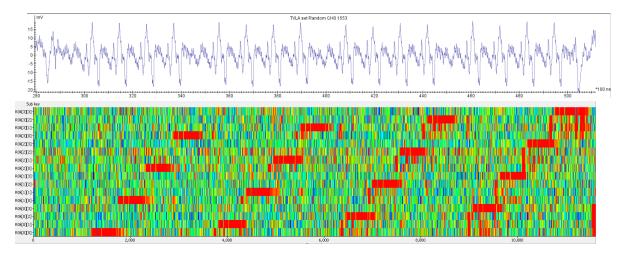

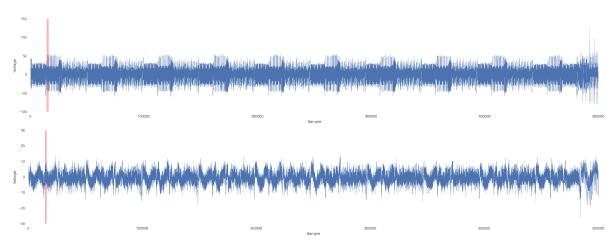

The raw traces acquired from STM and NRf board using Riscure Inspector are presented in figure 4.5. From a visual comparison, it is evident that the power consumption across the target devices differs significantly. It was expected since different manufacturers make devices with different specifications. Moreover, NRf51 is an LPE device, and the power traces were acquired using an amplifier.

The different operations being performed based on repetitive patterns can be distinctly identified across both the target devices. The raw traces have a color overlay depicting the AES operations being performed at the trace sections, corresponding to the sequence of operations

discussed in section 2.2.1. The operation execution across both the devices is synchronized in time, which is in line with our expectations to ensured identical execution of code across both devices.

#### 4.4.1. Organisation of datasets

The power traces coming from different devices of the same Cortex-M0 family differ significantly visually. Detailed analysis is performed on trace-sets consisting of multiple traces. Each trace-set consists of 2.5k encryption traces using the same secret key. Half of the tracesets are provided with a 16 byte fixed plain-text and the collection of these traces is termed as fixed-set. The other half is provided a 16-byte random plain-text; the collection of these traces is termed as random-set. A 2.5k trace trace-set is a union of 1.25k trace random-set and 1.25k trace fixed-set. Each trace has the input plain-text and output ciphertext information embedded in them.

We collected multiple traces-sets from the target boards executing AES encryption varying the parameters given below-

- 1. **Board family**: The label STM or NRF determines the family of board from which traceset was acquired.

- 2. Board iteration: We have two development boards from each family labeled as A  $\,$  or  $_B$

- 3. Encryption key: The secret key used for encryption labeled by key1 or key2.

- 4. Fixed plain-text: Determines the 16 byte fixed input provided to half of the traces represented by D1 or D2.

- 5. **Repetition**: TVLA methodology specifies performing a repetition in order to verify results, trace-sets are labeled by 1 or 2 representing two repetitions

We choose a naming convention for easier identification of trace-set parameters postacquisition. The nomenclature followed is <code>class\_board\_key\_data\_repetition</code>, for example a trace-set with the name <code>NRF\_B\_2\_a</code> means it was collected from <code>NRF</code> board <code>B</code> with <code>key 2</code> and provided fixed input <code>a</code>. In total, we collected 32 traces sets with different permutations of parameters, all of which have been listed in figure 4.6. We will be referencing these trace labels to identify the trace-sets and their parameters while discussing data analysis.

|         | STM Board       |                 |       | NRF Board       |                 |  |

|---------|-----------------|-----------------|-------|-----------------|-----------------|--|

|         | Fixed set-1     | Fixed set-2     |       | Fixed set-1     | Fixed set-2     |  |

|         | STM_A_key1_D1_1 | STM_A_key1_D2_1 | Key 1 | NRF_A_key1_D1_1 | NRF_A_key1_D2_1 |  |

| Desired | STM_A_key1_D1_2 | STM_A_key1_D2_2 |       | NRF_A_key1_D1_2 | NRF_A_key1_D2_2 |  |

| Board A | STM_A_key2_D1_1 | STM_A_key2_D2_1 |       | NRF_A_key2_D1_1 | NRF_A_key2_D2_1 |  |

|         | STM_A_key2_D1_2 | STM_A_key2_D2_2 | Key 2 | NRF_A_key2_D1_2 | NRF_A_key2_D2_2 |  |

|         | STM_B_key1_D1_1 | STM_B_key1_D2_1 |       | NRF_B_key1_D1_1 | NRF_A_key1_D2_1 |  |

|         | STM_B_key1_D1_2 | STM_B_key1_D2_2 | Key 1 | NRF_B_key1_D1_2 | NRF_A_key1_D2_2 |  |

| Board B | STM_B_key2_D1_1 | STM_B_key2_D2_1 | Kau 0 | NRF_B_key2_D1_1 | NRF_B_key2_D2_1 |  |

|         | STM_B_key2_D1_2 | STM_B_key2_D2_2 | Key 2 | NRF_B_key2_D1_2 | NRF_B_key2_D2_2 |  |

Figure 4.6: Created a data set with 32 trace-sets following the defined nomenclature showing set parameters.

In the next section, we will be discussing the methodology used for the synchronization of traces and the addition of instruction labels to the traces.

# 4.5. Preparing traces for comparison

Even though the boards execute the same instructions, the traces must be synchronized after the trigger finely align the clocks. To perform an instruction level analysis of traces, cycleaccurate instruction labels are added in the time axis. We will now discuss how these problems were solved.

#### **4.5.1.** Synchronisation of traces

Having the trace-sets aligned finely in time along clock cycles is necessary to provide an accurate analysis of the observed effects. The accuracy of the trigger signal determines the level of drift that is observed between the acquired traces. We compared the accuracy of the trigger signal from the oscilloscope to the recorded traces to find the level of drift.

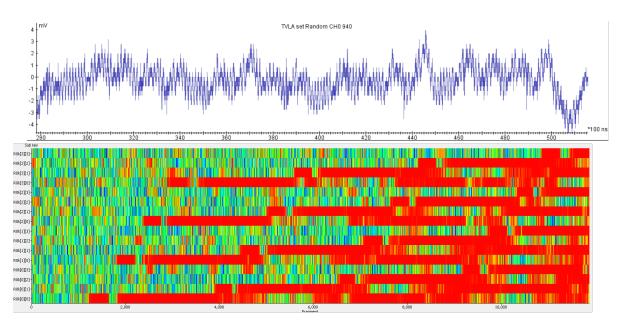

Using the disassembly of C code, the assembly code line that sets the trigger pin low is found to have exact timings. The number of cycles the program flow takes to enter the AES\_Encrypt function is noted, which is used as an offset to identify the start of AES\_Encrypt in recorded traces. The resulting offset from above was applied to the boards' traces to get them synchronized.