# Address decoders with FeFET-based Content-Addressable Memories

Master Thesis

Thomas I. Makryniotis

# Address decoders with FeFET-based Content-Addressable **Memories**

by

# Thomas I. Makryniotis

to obtain the degree of Master of Science at the Delft University of Technology, to be defended publicly on Tuesday, 27th of August 2024 at 14:00 PM.

Student number: 4625501

Project duration: July 2023 – August 2024

Thesis committee: Prof. dr. ir. G. Gaydadjiev, TU Delft, supervisor

Prof. dr. ir. M. Taouil, TU Delft, co-supervisor Prof. dr. ir. M. Babaie, TU Delft

Cover: 300 mm test wafer under magnification (2.5 mm side size of the

chip) lightened with visible light. Creative Commons CC0 1.0

TU Delft Report Style, with modifications by Daan Zwaneveld Style:

An electronic version of this thesis is available at http://repository.tudelft.nl/.

# Acknowledgements

It is been a long time since I started this journey; definitely not an easy one, but not a difficult one, either. It was a proper adventure, with all the necessary ingredients an adventure has: excitement, success, failure, commitment, trouble and eventually, relief. As with every journey, in the end, what worth remembering is the people that helped you go through it.

So, this is a public "thank you" to everyone who stood by me during this journey.

First of all, I would like to express my deepest gratitude to my supervisor Georgi and my co-supervisor Motta, for all the valuable help and guidance they provided, often regardless of the time or the day of the week. Without them it would not be possible to complete this project.

A big "thank you" also goes to the members of the Q&CE group who generously shared their expertise, answered my questions and provided their ideas.

Then, I would like to thank all my friends, old and new, who were tolerating my tantrums and celebrating my successes. Every cup of coffee, every beer, every walk and every conversation we had, was one more little push towards the finish line.

Finally, I would like to thank my family; my parents Giannis and Georgia and my brother Konstantinos for all their unconditional love, support and motivation throughout the years.

Thomas I. Makryniotis Delft, August 2024

# Summary

Emerging, non-volatile memories are promising solutions to contemporary computing problems. These include In-Memory Computing, Neuromorphic Computing, and Machine Learning. We believe that these are not the only possible applications of non-volatile emerging memory devices and that these can be used effectively for tackling several challenges of the "conventional" computer architecture.

For instance, address decoders are an integral part of random access memories. They are typically implemented using fast logic optimised for low latency. They are, however, difficult to test, while their repair is considered to be impossible. In this thesis we research the possibility of a highly scalable and testable address decoder solution, based on Content-Addressable Memories build with ferroelectric transistors (FeFET).

This solution can offer numerous advantages including transistor count close to state of the art designs, while outperforming them in terms of latency. In addition, a key advantage could emerge during the testing of this decoder; due to its regular 2D structure, it's testability is comparable to that of conventional memory arrays. Moreover, it can enable higher production yields, considering that adding a few spare rows will enable end-of-production repair, in the presence of manufacturing defects.

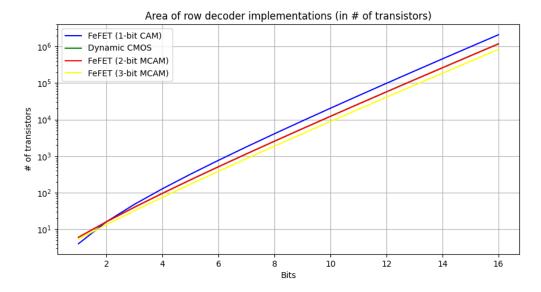

By additionally increasing the number of address bits stored in a single FeFET CAM cell, further potential area reductions of 30% - compared to the traditional dynamic NAND decoders - can be achieved.

# Contents

| Ac | Acknowledgements                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |  |  |  |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| Su | ımmary                                                                                                                                                                                                                                                                                                                                                                                               | ii                                                                    |  |  |  |  |

| No | omenclature                                                                                                                                                                                                                                                                                                                                                                                          | viii                                                                  |  |  |  |  |

| 1  | Introduction  1.1 Motivation and Research Questions  1.2 FeFET-based Address Decoders  1.3 Contribution  1.4 Thesis Organisation                                                                                                                                                                                                                                                                     | 1<br>1<br>2<br>2<br>2                                                 |  |  |  |  |

| 2  | Introduction to FeFETs  2.1 Ferroelectricity and Ferroelectric Materials  2.2 An overview on FeFETs  2.3 FeFET Advancements and Materials  2.4 Challenges of HfO <sub>2</sub> Integration  2.4.1 Depolarization Field  2.4.2 Retention  2.4.3 Wake-up  2.4.4 Endurance  2.4.5 Fatigue  2.5 Structures and Applications  2.5.1 Memories  2.5.2 Neurons  2.5.3 Miscellaneous  2.6 Simulation of FeFETs | 4<br>4<br>6<br>8<br>9<br>10<br>10<br>10<br>11<br>11<br>11<br>12<br>14 |  |  |  |  |

| 3  | Overview of Memory Decoders  3.1 Row Decoders  3.1.1 Static Decoders  3.1.2 Dynamic Decoders  3.2 Column Decoders  3.3 Address Decoder Faults                                                                                                                                                                                                                                                        | 15<br>16<br>18<br>18<br>19                                            |  |  |  |  |

| 4  | Content-Addressable Memories  4.1 CMOS-based Content-Addressable Memories  4.1.1 A special case: TCAMs  4.1.2 Matching Line Sensing Schemes  4.2 CAMs based on Emerging Memory Technologies  4.2.1 Resistive CAM cells  4.2.2 FeFET-based CAM cells  4.3 Analog and Multi-level CAMs                                                                                                                 | 20<br>21<br>23<br>24<br>25<br>26<br>27                                |  |  |  |  |

| 5  | The FCAM Row Decoder  5.1 Concept and motivation                                                                                                                                                                                                                                                                                                                                                     | 29<br>29<br>32<br>32                                                  |  |  |  |  |

| 6  | Simulation and Results 6.1 Experimental Methodology                                                                                                                                                                                                                                                                                                                                                  | <b>33</b>                                                             |  |  |  |  |

Contents

|    | 6.2<br>6.3<br>6.4<br>6.5 | 6.5.1 Evaluating the single-cell simulation results 6.5.2 Evaluating the array simulation results 6.5.3 Match line open faults 6.5.4 Source line open faults 6.5.5 Array bridge defects 6.5.6 Testing for defects | 35<br>44<br>44<br>45<br>46<br>47 |

|----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 7  | 7.1                      | clusion<br>Summary                                                                                                                                                                                                | <b>50</b><br>50<br>51            |

| Re | ferer                    | nces                                                                                                                                                                                                              | 52                               |

| Α  | Pub                      | lication: FeFET-based CAM Address Decoders                                                                                                                                                                        | 58                               |

| В  | B.1<br>B.2               | Partial-open single cell defects                                                                                                                                                                                  | <b>65</b><br>65<br>67<br>69      |

# List of Figures

| 2.1  | The ferroelectric hysteresis loop                                                             | 4  |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.2  | The two phases of lead titanate and of similar materials                                      | 5  |

| 2.3  | Domain polarizations before and after the application of an external field                    | 5  |

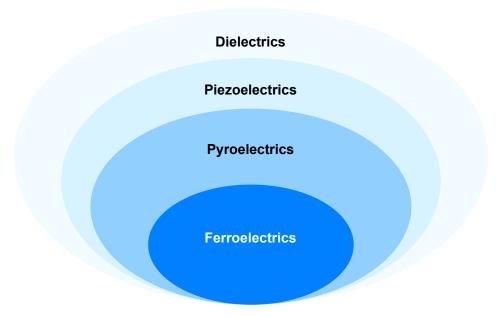

| 2.4  | Relationship between dielectric, piezoelectric, pyroelectric and ferroelectric materials      | 6  |

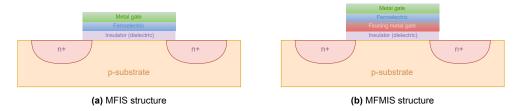

| 2.5  | The two different gate stack structures for FeFETs                                            | 7  |

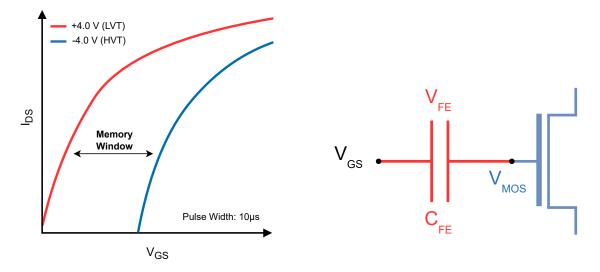

| 2.6  | The I-V characteristics for the two FeFET states                                              | 7  |

| 2.7  | Circuit equivalent of FeFET device                                                            | 7  |

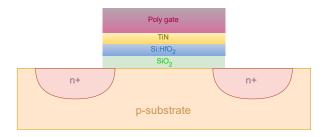

| 2.8  | FeFET structure with silicon-doped hafnia as a FE layer.                                      | 9  |

| 2.9  | ·                                                                                             | 12 |

|      | FeFET-based spiking neuron                                                                    |    |

|      | FeFET crossbar for IMC operations                                                             | 12 |

|      | Two FeFET-based FPGA LUTs                                                                     | 13 |

|      | Routing elements with FeFETs                                                                  | 13 |

| 2.13 | FeFET-based non-volatile flip-flop                                                            | 14 |

| 3.1  | An SRAM array with decoders                                                                   | 15 |

| 3.2  | 8-input NAND gate. Each gate can drive a wordline                                             | 16 |

| 3.3  | Decoders with different number of stages                                                      | 17 |

| 3.4  | Comparison of predecoder architectures                                                        | 17 |

| 3.5  | 2-input dynamic decoders                                                                      | 18 |

| 3.6  | 2-input dynamic decoders                                                                      | 19 |

| 5.0  | 2-input dynamic decoders                                                                      | 13 |

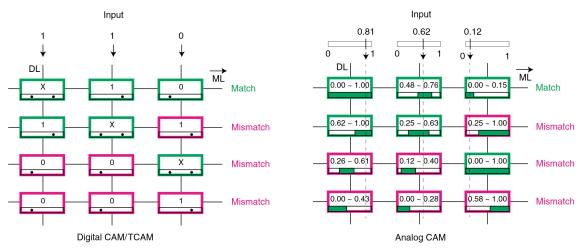

| 4.1  |                                                                                               | 20 |

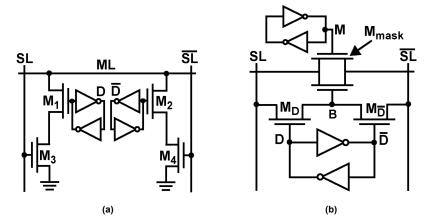

| 4.2  | Binary CAM cells                                                                              | 21 |

| 4.3  | TCAM cells - (a) NOR-type, (b) NAND-type                                                      | 22 |

| 4.4  |                                                                                               | 23 |

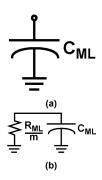

| 4.5  | The equivalent models for match and mismatch for the precharge-high sensing scheme.           | 23 |

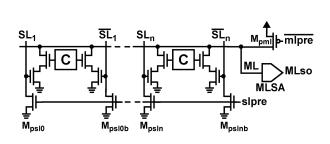

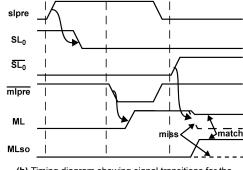

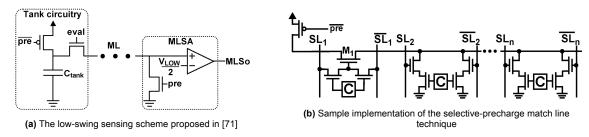

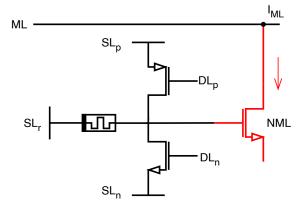

| 4.6  | Examples of the two sensing schemes discussed                                                 | 24 |

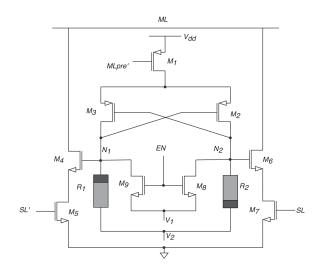

| 4.7  | A 9T-2R memristive CAM cell                                                                   | 25 |

| 4.8  | A 3T1R memristive CAM cell                                                                    | 26 |

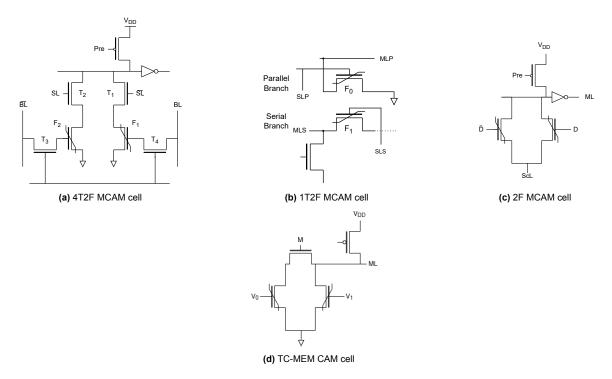

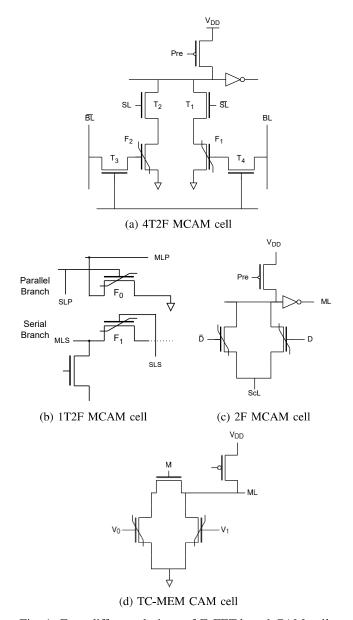

| 4.9  | Four different designs of FeFET-based CAM cells                                               | 27 |

| 4.10 |                                                                                               | 28 |

| 4.10 |                                                                                               | 20 |

| 5.1  | Area consumed by different implementations of decoders, compared to the decoded               |    |

|      | address width                                                                                 | 30 |

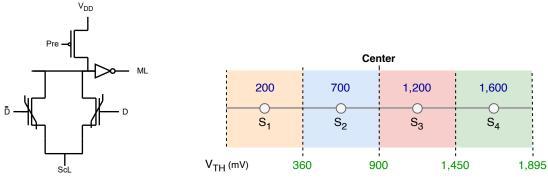

| 5.2  |                                                                                               | 31 |

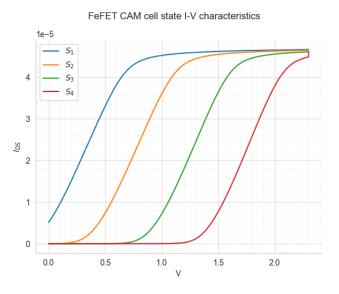

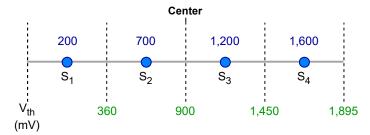

| 5.3  | The I-V characteristics of the FeFET for the four $Vth$ used to define the four CAM states.   | 31 |

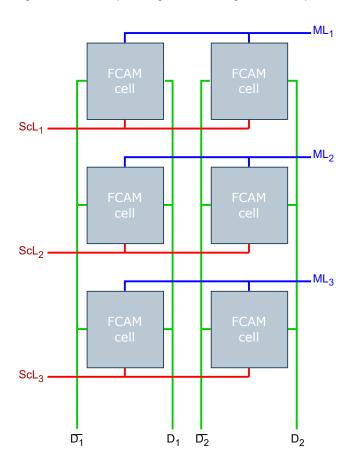

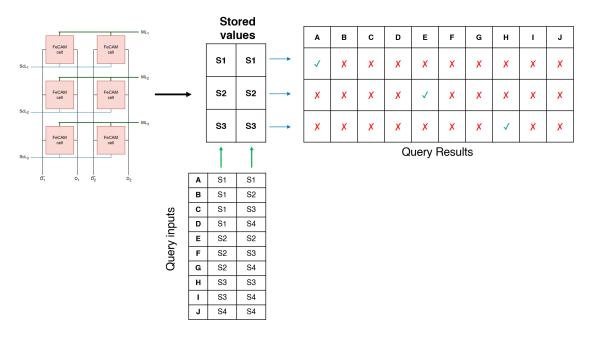

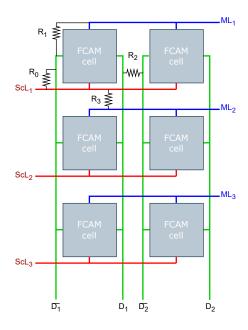

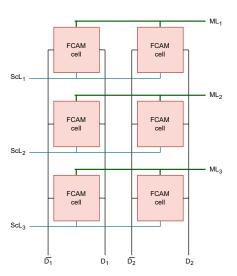

| 5.4  | The high-level architecture of the $2 \times 3$ FCAM array                                    | 32 |

|      |                                                                                               |    |

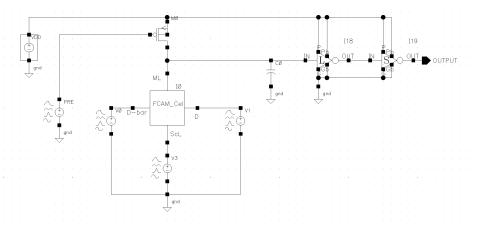

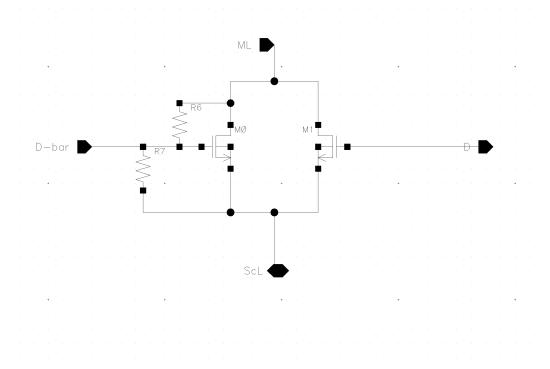

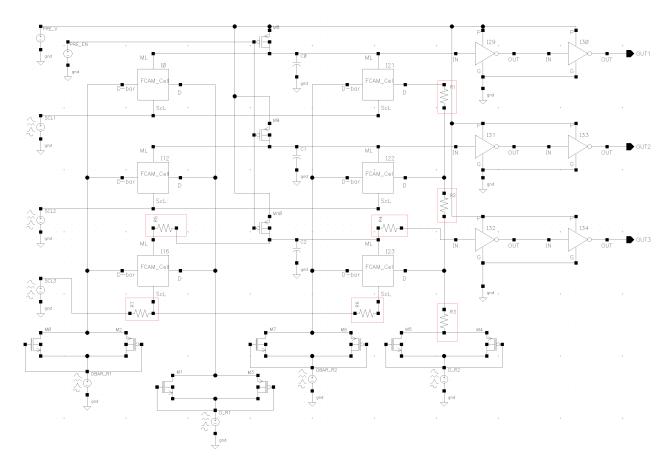

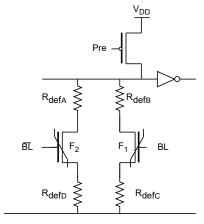

|      | Schematic of a single FCAM cell with the sense amplifier (SA)                                 | 34 |

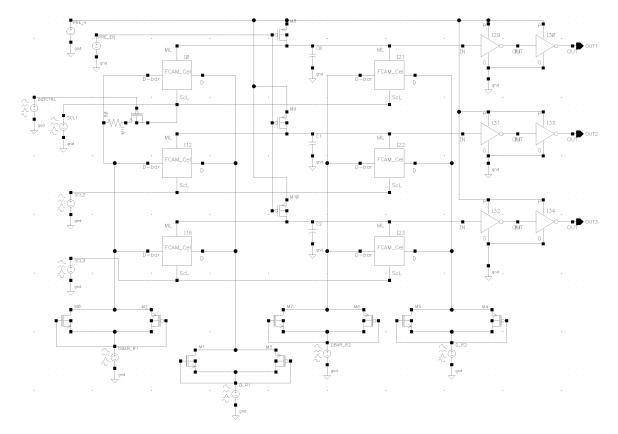

| 6.2  | The circuit schematic of the $2 \times 3$ FeFET decoder. The 2-inverter SA could also be seen |    |

|      | as well as one of the simulated resistive defects                                             | 35 |

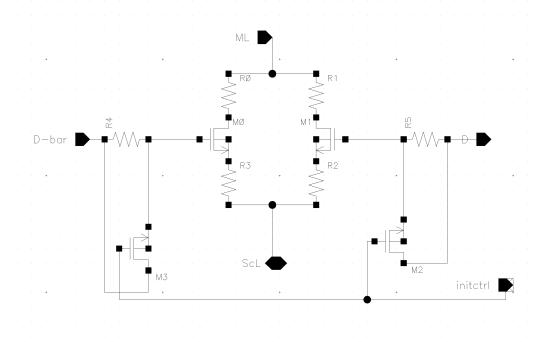

| 6.3  | Schematic of a single, defective FCAM cell. Each resistor simulates one possible open         |    |

|      | defect                                                                                        | 36 |

| 6.4  | Schematic of another defective FCAM cell. Each resistor simulates one possible bridge         |    |

|      | defect                                                                                        | 36 |

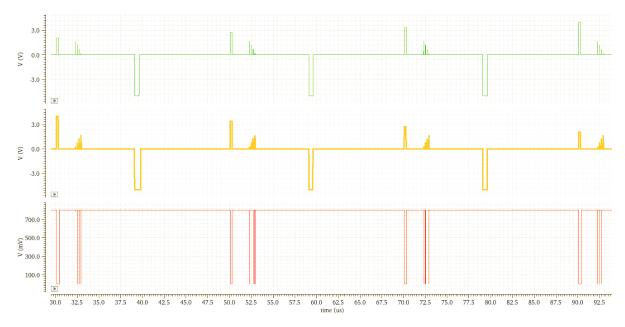

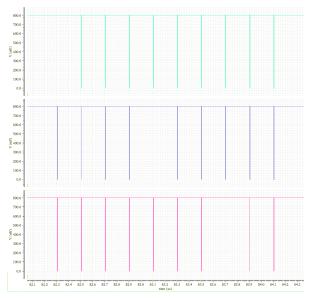

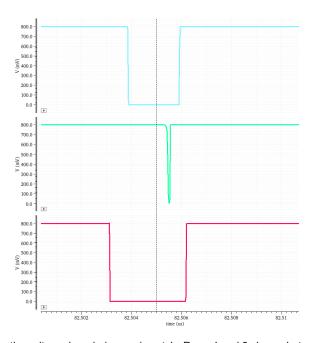

| 6.5  | Pulse plot during simulation. The first two plots are the write/read pulses, while the last   |    |

|      | one is the output from the SA. The negative pulses are erase operations, followed by a        |    |

|      | relatively high positive pulse which programs the cell. The subsequent short pulses are       |    |

|      | the read operations. Notice the differential signals between the input terminals              | 37 |

List of Figures vi

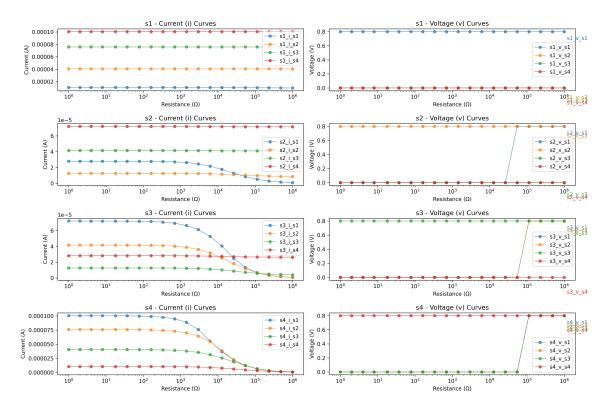

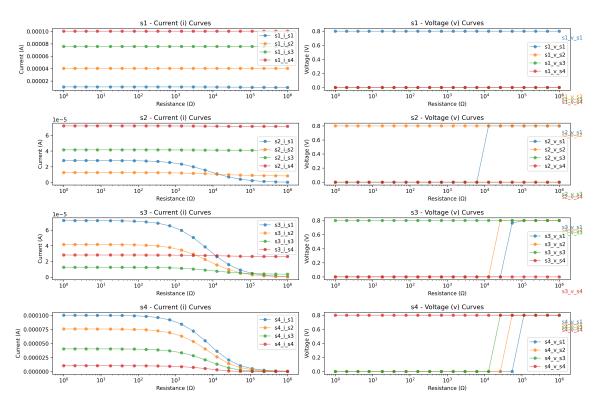

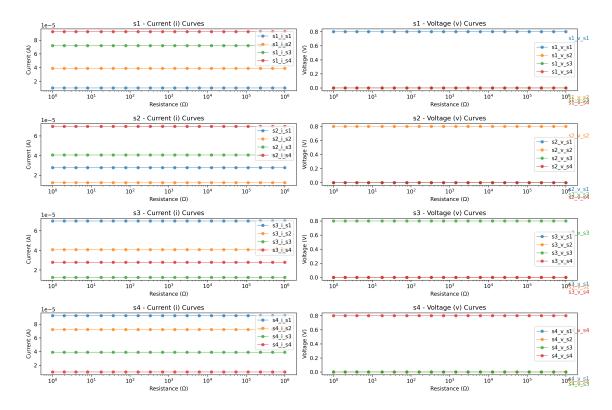

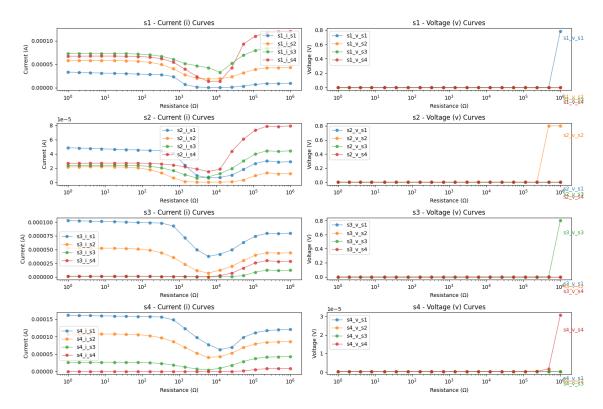

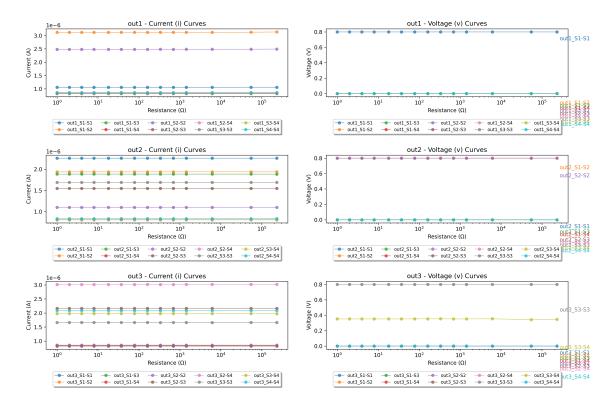

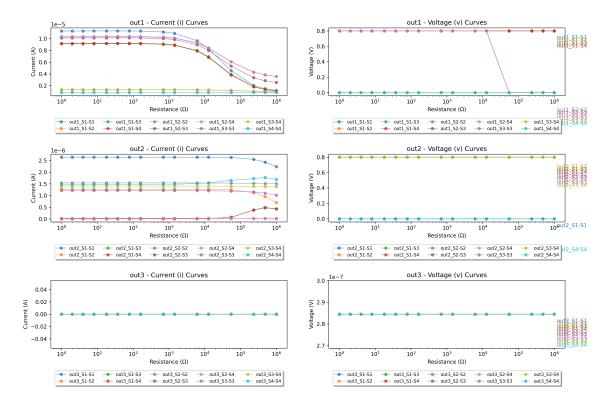

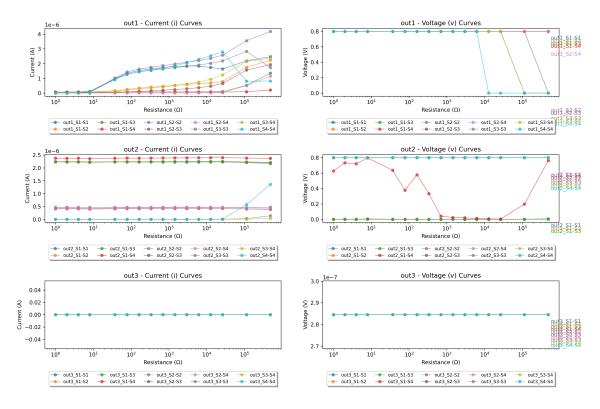

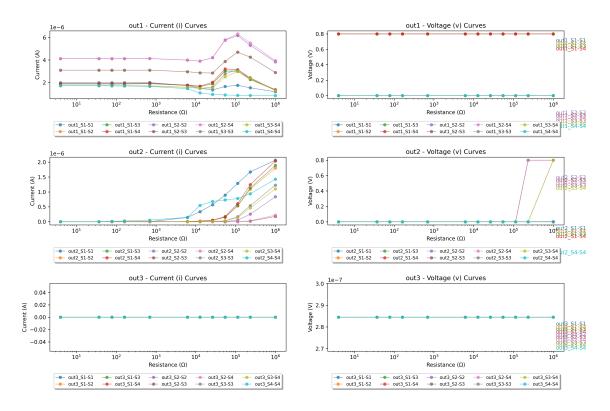

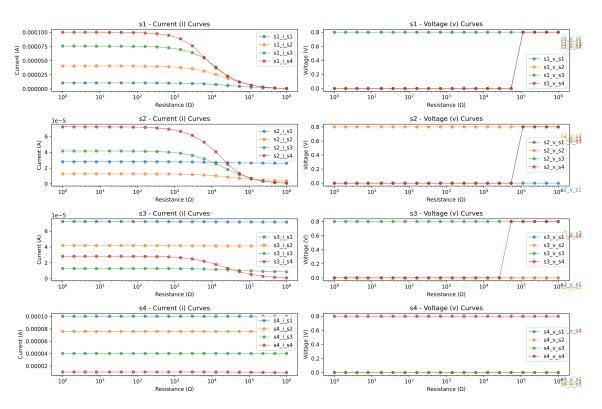

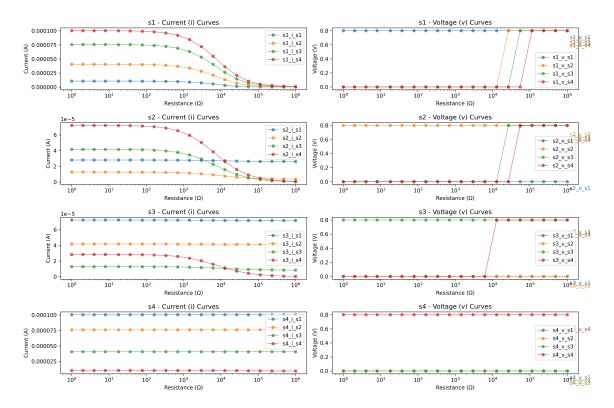

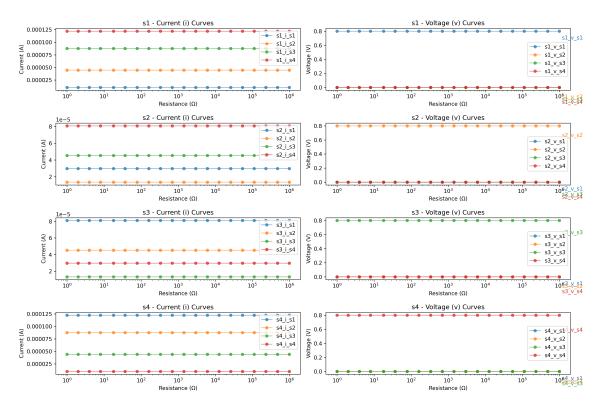

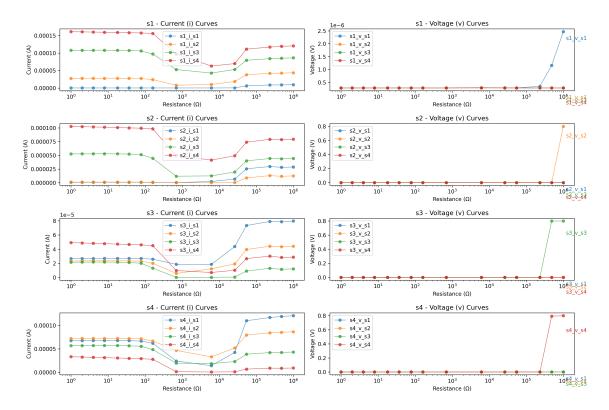

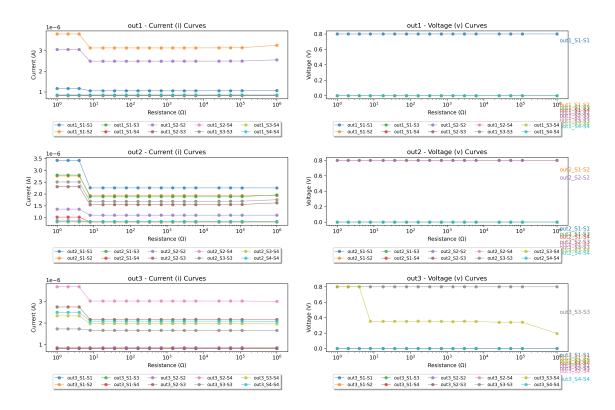

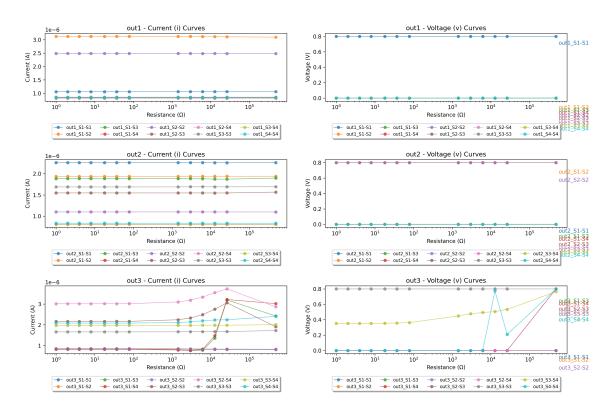

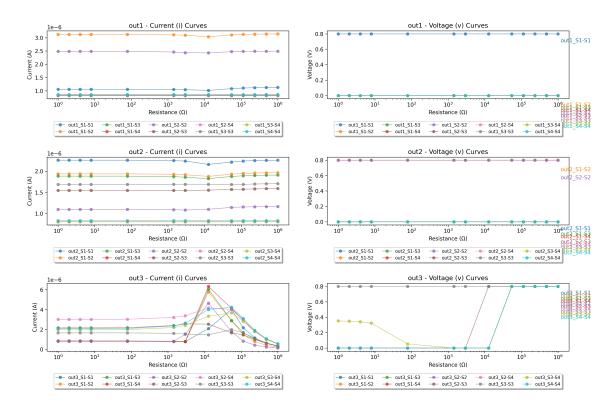

|      | Voltage and current plots for the defect point on R0                                                                                                                                                                                                                                                                                                          | 38<br>39<br>39<br>40 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | query $(S_2-S_2)$ and the third row for the eighth query $(S_3-S_3)$                                                                                                                                                                                                                                                                                          | 40                   |

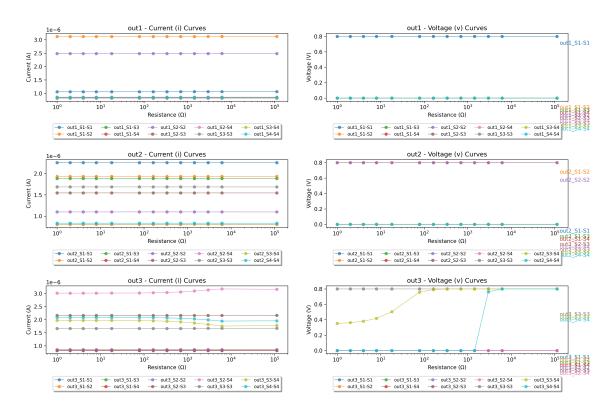

|      | Voltage and current plots for the partial-open array defect point on $R_1$                                                                                                                                                                                                                                                                                    | 41                   |

|      | Voltage and current plots for the partial-open array defect point on $R_4$ (match line)                                                                                                                                                                                                                                                                       | 41                   |

|      | Voltage and current plots for the partial-open array defect point on $R_6$ (source line)                                                                                                                                                                                                                                                                      | 42                   |

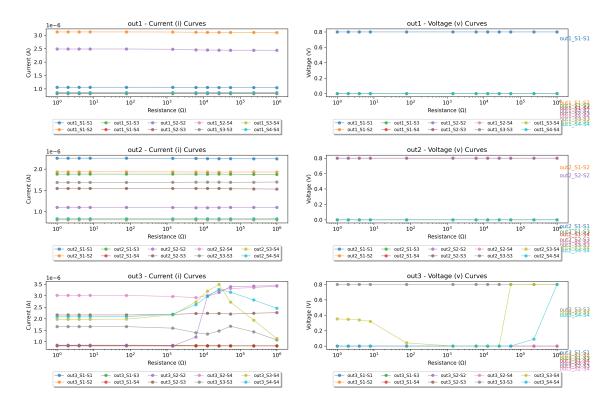

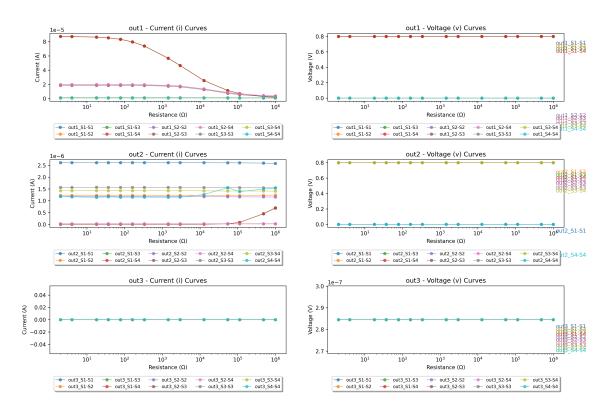

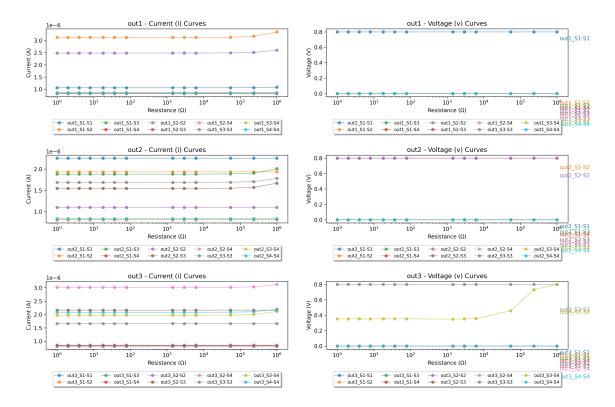

| 6.15 | Voltage and current plots for the array bridge defect shown in 6.2 (between bitline - source                                                                                                                                                                                                                                                                  | 40                   |

| 6 16 | line)                                                                                                                                                                                                                                                                                                                                                         | 42<br>43             |

|      | Voltage and current plots for the array bridge defect between bitline - hitline                                                                                                                                                                                                                                                                               | 43                   |

|      | Voltage and current plots for the array bridge defect between bitline - source line                                                                                                                                                                                                                                                                           | 44                   |

|      | The array structure, showing the partial-open, resistive defects (marked with red squares)                                                                                                                                                                                                                                                                    |                      |

|      | The plot shows the voltage drop during a mismatch. Rows 1 and 3 show what would be considered, normal, discharge pulse, following the duration of the input. The discharge pulse of the row 2 is much shorter and delayed, which created issues during the sampling of the signals. The marker (dashed vertical line), shows exactly where the sampling point | 10                   |

|      | is                                                                                                                                                                                                                                                                                                                                                            | 46                   |

|      | An overview of the sites of the bridge defects we simulated on the array                                                                                                                                                                                                                                                                                      | 47                   |

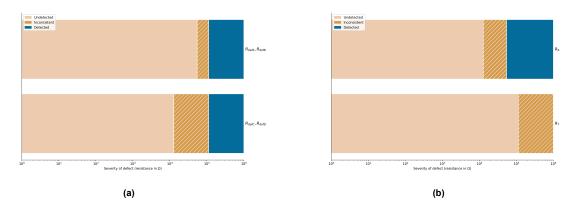

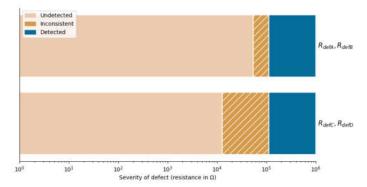

|      | Detectability ranges for cell and array faults                                                                                                                                                                                                                                                                                                                | 48                   |

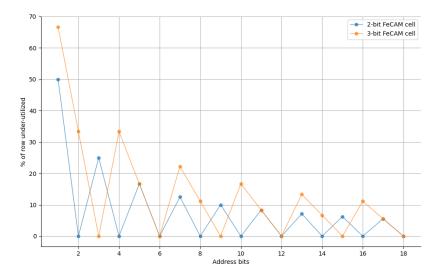

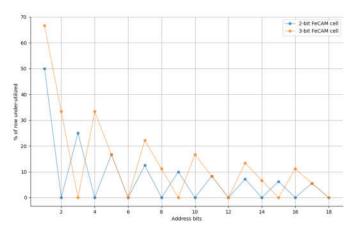

| 6.23 | Under-utilization of 2- and 3-bit FCAM cells with regards to the address length                                                                                                                                                                                                                                                                               | 49                   |

| B.1  | Voltage and current plots for the single cell, partial-open defect point on $R_1$                                                                                                                                                                                                                                                                             | 65                   |

| B.2  | Voltage and current plots for the single cell, partial-open defect point on $R_2$                                                                                                                                                                                                                                                                             | 66                   |

| B.3  | Voltage and current plots for the single cell, partial-open defect point on $R_4$                                                                                                                                                                                                                                                                             | 66                   |

| B.4  | Voltage and current plots for the single cell, bridge defect point on $R_7$                                                                                                                                                                                                                                                                                   | 67                   |

| B.5  | Voltage and current plots for the partial-open array defect point on $R_2$                                                                                                                                                                                                                                                                                    | 67                   |

| B.6  | Voltage and current plots for the partial-open array defect point on $R_3$                                                                                                                                                                                                                                                                                    | 68                   |

| B.7  | Voltage and current plots for the partial-open array defect point on $R_5$ (match line)                                                                                                                                                                                                                                                                       | 68                   |

| B.8  | Voltage and current plots for the partial-open array defect point on $R_7$ (source line)                                                                                                                                                                                                                                                                      | 69                   |

# **List of Tables**

|     | Truth table with representing voltages for a 1FeFET AND gate                                                                                                                                                                          |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | The NOR CAM values for storing and reading data. Note that, even though D and $\bar{D}$ are not complementary, the complementary notation is preserved for consistency with the previous description of the binary cell architecture. | 22 |

| 4.2 | The NAND CAM values for storing and reading data                                                                                                                                                                                      |    |

|     | Comparison summary of CAM cell designs                                                                                                                                                                                                |    |

| 6.1 | An example of a march test used to detect faults in FCAM single cells                                                                                                                                                                 | 48 |

| 6.2 | Comparison of the transistor count and delay of different implementations                                                                                                                                                             | 49 |

| B.1 | An example of a March test to detect single-cell bridge defects                                                                                                                                                                       | 69 |

| B.2 | An example of a March test used to detect partial-open faults in FCAM arrays                                                                                                                                                          | 69 |

| B.3 | An example of a March test used to detect bridge faults in FCAM arrays                                                                                                                                                                | 69 |

# Nomenclature

If a nomenclature is required, a simple template can be found below for convenience. Feel free to use, adapt or completely remove.

### **Abbreviations**

| Abbreviation | Definition                                        |

|--------------|---------------------------------------------------|

| ISA          | International Standard Atmosphere                 |

| ACAM         | Analog Content-Adressable Memory                  |

| Al           | Artificial Intelligence                           |

| BCAM         | Binary Content-Addressable Memory                 |

| CAM          | Content-Addressable Memory                        |

| CMOS         | Complementary Metal-Oxide Semiconductor           |

| CNTFET       | Carbon NanoTube Field-Effect Transistor           |

| DRAM         | Dynamic Random Access Memory                      |

| FCAM         | Ferroelecric Content-Addressable Memory           |

| FPGA         | Field-Programmable Gate Array                     |

| FRAM         | Ferroelectric Random Access Memory                |

| FeFET        | Ferroelectric Field-Effect Transistor             |

| HKMG         | High-K Metal Gate                                 |

| HVT          | High $V_{TH}$ (Threshold Voltage)                 |

| HZO          | Hafnium Zirconate                                 |

| LUT          | Look-Up Table                                     |

| LVT          | Low $V_{TH}$ (Threshold Voltage)                  |

| MCAM         | Multi-level Content Addressable Memory            |

| MFIS         | Metal-Ferroelectric-Insulator-Semiconductor       |

| MFMIS        | Metal-Ferroelectric-Metal-Insulator-Semiconductor |

| MLSA         | Match Line Sense Amplifier                        |

| MOSFET       | Metal-Oxide Semiconductor Field-Effect Transistor |

| NVFF         | Non-Volatile Flip-Flop                            |

| PCM          | Phase-Change Memory                               |

| PZT          | Lead Zirconate Titanate                           |

| PTM          | Predictive Technology Model                       |

| RAM          | Random Access Memory                              |

| ReRAM        | Resistive Random Access Memory                    |

| SNN          | Spiking Neural Network                            |

| SRAM         | Static Random Access Memory                       |

| SSD          | Solid-State Disk                                  |

| ScL          | Source Line                                       |

| TCAM         | Ternary Content-Addressable Memory                |

| TLB          | Translation Lookaside Buffer                      |

1

# Introduction

### 1.1. Motivation and Research Questions

Computer engineering is one of the youngest fields of engineering and arguably, the one with the greatest impact in the modern world. The advancements in the field are so rapid and groundbreaking that within 70 years, computers went on from being enormous, power-hungry, unreliable machines that only a few institutes could afford experimenting with, to tiny, elegant and powerful gadgets that play a vital role in our day-to-day lives.

Several times over the years, the computing paradigms have shifted: from a central processing unit responsible for everything, to separate accelerators that communicate over fast buses, to the most recent advancements of Near- and In-Memory Computing. Undoubtedly, these advancements would not be possible without the constant research and development in the microelectronics field. Vacuum tubes gave their place to several different types of transistors, like Metal-Oxide Semiconductor Field-Effect Transistors (MOSFET), which then became the building blocks for Integrated Circuits (IC). Complementary Metal-Oxide Semiconductor (CMOS) technology dominates the IC industry the last decades and it seems that it will keep on doing so for the foreseeable future.

Despite the success of CMOS, novel, emerging technologies are gaining traction, fueled by the increased demand for data processing, and the applications in the fields of Machine Learning (ML), Neural Networks (NN) and Artificial Intelligence (Al). These technologies include among others Memristors, Ferroelectric FET (FeFET), Phase-Change Memory (PCM), Spintronics and Carbon Nanotube FET (CNTFET). A big part of the recent research on these devices is devoted in their storage capabilities and their potential to be used in building memory arrays that could also perform logic operations. Despite the significant potential of these novel, non-von Neumann architectures, we believe that emerging devices can give solutions to many more problems in the field of Computer Engineering.

Address decoders, for instance, are an integral part of Random Access Memories (RAM) and low latency address decoding remains a challenge in high-performance memory designs ranging from cache memories up to large main memory arrays. This typically results in highly customised logic implementations for the targeted memory array that are fast, but difficult to test. Detecting address decoder faults is challenging since the tests have to "recover" the effects from the expected values obtained from different locations in the memory array [1], [2]. Moreover, detecting linked address decoder faults requires long March tests [3]. Implementing testable and ideally, repairable address decoders will not only help reducing end of production test times but it will also improve the overall yield.

In this thesis we research the feasibility of a highly scalable and testable address decoder solution, based on Content-Addressable Memories (CAM) build with FeFET. During the course of our research

we tried to answer the following two key questions:

- Is it feasible to leverage the FeFET device to create a CAM array, which then can be used to decode a memory address?

- If yes, how is it possible to test the functionality of this structure in a simple and effective way?

### 1.2. FeFET-based Address Decoders

Hardwired dynamic NAND address decoders are widely used in random access memories to decode parts of the address. The function of a dynamic NAND decoder is quite simple: each row of the decoder corresponds to a row of the decoder's truth table and a certain number of transistors are hardwired to either the address signals, or their inverted ones. Based on which transistors are ON or OFF, the appropriate line of the address decoder is activated.

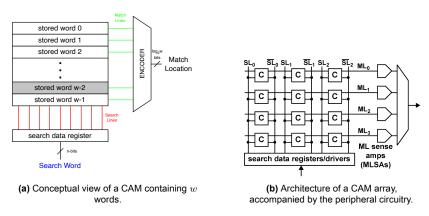

Practically, the same can be achieved by using a content-addressable memory which has all the available addresses stored: an input address is used as a query and if a CAM row contains it, it signals a Match Line (ML) which then activates a row in the memory array. An implementation was suggested for the first time in [4] where the proposed CAM array was based on a ReRAM array. This design was discussed in a more elaborate way in [5] where a few applications were also proposed such as fully associative TLBs and virtually addressable memory.

FeFET-based address decoders constitute a special category of CAM-based decoders, where the CAM cell is built with FeFETs. Compared to cells built with other technologies, FCAM cells demonstrate lower search energy, significantly reduced area (especially for multi-level cells) and switching times similar to those of a "traditional" MOSFET. In addition, FeFET manufacturing is fully compatible with the existing manufacturing processes, with only minor changes being deemed necessary. This leads to a much easier integration with "conventional" CMOS circuits and a rapid design-prototype-manufacturing cycle, compared with other technologies like ReRAM or PCM.

### 1.3. Contribution

In this paper we propose a novel, low latency address decoder built using an array of two-FeFET Content Adressable Memory (CAM) cells. Each FeFET CAM cell stores at least two bits in order to reduce the overall array size. Our address decoder was simulated in PTM14nm CMOS technology and outperforms the state of the art in latency, by at least a factor of 1.7x. At the same time, its area stays on par with the baseline solutions. When more than two bits per CAM cell are used, additional area gains can be achieved. Moreover, due to its memory-like regular organization, our decoder is easy to test and by adding few spare rows end-of-production-line repair can be facilitated.

The main contributions of this paper are:

- a fast FeFET CAM based address decoder design;

- a careful investigation of the possible partial-open and bridge defects in the proposed two-transistor CAM cells;

- · a set of march tests able to detect the above defects.

### 1.4. Thesis Organisation

The remainder of the dissertation is organised as follows:

Chapter 2 provides the necessary background on FeFETs. In this chapter we discuss the physics, the materials and the applications of FeFETs. Key concepts are explained, as well as a general introduction to the possibilities of this emerging technology.

Chapter 3 provides an overview of address decoders. Several different types are being discussed, including static, dynamic and column decoders. Also, key concepts are introduced, like decoder stages and predecoding.

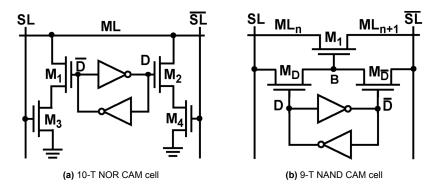

Chapter 4 is an extensive overview of Content-Addressable memories. Starting from established designs and technology (like CMOS), we discuss designs and applications, as well as past and present advancements, pitfalls and edge cases. The chapter also introduced the new generation of CAM cells built with emerging memory technologies, showcasing their advantages over previous designs.

Chapter 5 introduces and discusses the FCAM row decoder. Combining the insight from the previous chapters, we present the idea of a memory address decoder based on CAMs built with FeFET devices.

Chapter 6 presents the experimental platform and the simulation results. In this chapter we also discuss the results and the challenges of the project and we provide our solution for testing this new type of decoder based on simple march tests. We also compare certain metrics of the design with other state-of-the-art conventional decoder designs.

In the appendices, extra information can be found with regards to this research. *Appendix A* includes a conference paper to be published in VLSI-SoC 24' which constitutes a "condensed" version of this thesis, while *Appendix B* includes additional material from the simulations, such as plots and figures of measurements on different defect sites.

# Introduction to FeFETs

### 2.1. Ferroelectricity and Ferroelectric Materials

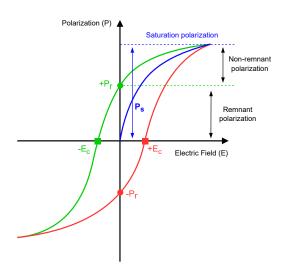

Ferroelectricity is the property of certain materials (crystals) to demonstrate a spontaneous, yet reversible, electric polarization. We call these materials ferroelectrics and their outstanding feature is that, this polarization reversal can occur by applying a strong electric field in the opposite direction. Therefore, the polarization is dependent not only on the current electric field but also on its history, effectively yielding hysteresis loops (Figure 2.1). This phenomenon was discovered and reported for the first time in 1920 in Rochelle salt by J. Valasek [6]. The observed similarities with ferromagnetism lead to the use of the prefix ferro-, meaning iron, despite the fact that most ferroelectric materials do not contain iron.

Figure 2.1: The ferroelectric hysteresis loop

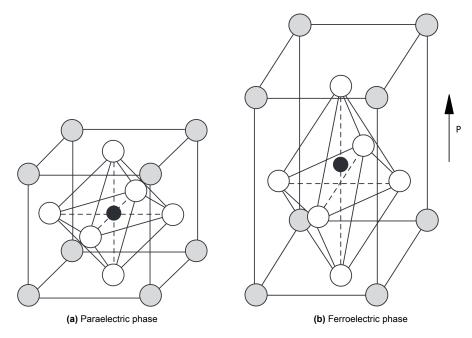

In a way similar to ferromagnetism, this spontaneous polarization is the consequence of a specific arrangement within the crystal lattice of the material. A good example of a characteristic ferroelectric material is lead titanate ( $PbTiO_3$ ); its ferroelectric properties arise from the displacement of titanium atom in the center of the  $TiO_6$ octahedron. In general, the spontaneous polarization present in these materials stems from the breaking of symmetry in the crystal structure along a unique axis, specifically, a noncentrosymmetric lattice. Figure 2.2 shows the perovskite structure of the lead titanate, in two different phases the paraelectric and the ferroelectric. Similarly structured materials demonstrate similar ferroelectric properties like lead zirconate titanate and barium titanate. Despite all of them sharing the same pervskite structure, it is important to note that most perovskites do not show any ferroelectric properties.

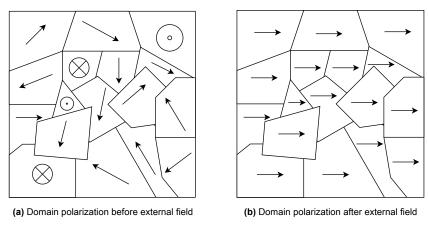

Macroscopically, ferroelectric materials are not homogeneous and have an incoherent structure with small areas of local homogeneity. These areas are called *domains* and they have discrete boundaries called *domain walls*. The size of the domains can vary between a few nanometers, up to one micron, and the most important property is that each domain has its own ferroelectric orientation. Although each domain has its own spontaneous polarization, eventually the cumulative polarization of all the domains cancels out and the material, as a whole, is neutral. Figure 2.3 shows the difference between

Figure 2.2: The two phases of lead titanate and of similar materials.

Figure 2.3: Domain polarizations before and after the application of an external field

a material without ferroelectric homogeneity, against one where ferroelectric polarization is observable.

Having described the domain structure and behaviour, it is easier to understand the phases of the hysteresis loop as shown in Figure 2.1. Starting with a pristine piece of ferroelectric material, no electric polarization is observable, hence both the polarization and the applied electric field are zero. By increasing the intensity of the externally applied electric field, the polarization of the material starts to rise, in the opposite direction of the applied electric field. Once all the domains have been re-oriented, the material has reached the *saturation polarization*; regardless of the intensity of the external electric field, there are no domains left to be re-oriented. At this point, if the electric field is completely removed, the polarization of the material will drop since some of the domains will not be able to retain their polarization. However, the majority of them will do so, and the material will keep its overall net polarization. This is called *remnant polarization* ( $P_r$ ), while the polarization "lost" due to the fallback of the domains, is called *non-remnant polarization*. At this point, if a reverse external field is applied, the polarization of the material will start to drop again, until it reaches a negative "peak" value, ie. a negative saturation polarization. The behaviour is exactly the same as the one we described, but since the orientation of the electric field is reversed, the polarization of the material is also reversed. The polarization shows a reaction delay (or hysteresis) with regards to the electric field, hence the name hysteresis loop.

Figure 2.4: Relationship between dielectric, piezoelectric, pyroelectric and ferroelectric materials.

Ferroelectrics are a subset of the broader family of materials called *pyroelectrics*, which in turn are a subset of the *piezoelectric* family of materials. Figure 2.4 shows this relationship.

Until recently, the use of ferroelectric materials was limited in applications like FRAM, due to its significant advantages over Flash and EEPROM memories. FRAM technology employed a ferroelectric capacitor utilizing lead zirconate titanate (PZT) in the back-end-of-the-line (BEOL) configuration, which was linked to the drain of a front-end metal-oxide-semiconductor field-effect transistor (MOSFET). However, wide-scale adoption of ferroelectric technologies remained unrealized due to the difficulties associated with incorporating perovskite oxides into front-end semiconductor manufacturing processes. These challenges primarily encompassed issues related to perovskite etching, sensitivity to hydrogen, as well as limitations in thickness and cell size scaling beyond the 130 nm technology node [7].

The resurgence of research in ferroelectric devices was ignited by the discovery of ferroelectricity in binary oxides like silicon doped hafnia (Si:HfO<sub>2</sub>) in 2011 [8]. Hafnia has played a pivotal role as a key facilitator of *high-K-metal-gate* (HKMG) technology for advanced logic transistors since the mid-2000s. Its compatibility with modern complementary metal-oxide-semiconductor (CMOS) technology, along with its scalability, holds the potential to unlock the promise of ferroelectric memories in high-volume semiconductor manufacturing, opening up opportunities for a wide array of commercial products [9]. Ferroelectric memories offer numerous prospects across various levels of the memory hierarchy, including embedded memory, main memory, storage-class memory, and long-term storage. In addition, many proposals are out for using ferroelectric devices for alternative computing paradigms such as non-von Neumann and neuromorphic computing [10], [11], [12].

### 2.2. An overview on FeFETs

The main concept of a FeFET refers to using a layer of ferroelectric material that is deposited on a semiconductor, in order to tune its surface conductivity. While this idea was discussed for the first time in 1957 [13, 14], as a device it was realized for the first time in 1974 by We et al., at the Westinghouse Research Laboratory [15]. This first prototype was an n-type MOSFET using a Bismuth Titanate film  $(Bi_4Ti_3O_{12})$  as a ferroelectric material. In practice, the structure of a FeFET is straightforward; an additional ferroelectric (FE) layer is used in the gate stack, forcing the MOSFET to showcase two different threshold voltages, under two different polarization states. The two architectures used in the gate stack are the *Metal-Ferroelectric-Insulator-Semiconductor* (MFIS) and the *Metal-Ferroelectric-Metal-Insulator-Semiconductor* (MFMIS). Figure 2.5 shows these structures.

Figure 2.5: The two different gate stack structures for FeFETs

FeFETs demonstrate negative capacitance (NC) and hysteresis in their I-V curves [16]. As we already mentioned, a switching of the ferroelectric polarization results in the shifting of the FeFET's  $V_{th}$  and this is the key characteristic we aim to exploit. Apart from this fact, the FeFET effectively behaves identically to any other conventional MOSFET. The implications of such a structure are obvious; by controlling the polarization of the ferroelectric layer (and as a consequence, the  $V_{th}$  of the transistor), it is possible to store binary values in a FeFET which then can be read afterwards.

The polarization of the ferroelectric layer can be controlled by applying appropriate pulses on the gate terminal. Two characteristics of these pulses can be controlled: amplitude and duration. The designer is responsible for deciding the values of these factors and tune them according to the application. FeFETs demonstrate two states, the first one called HVT (High  $V_{th}$ ) and the other LVT (Low  $V_{th}$ ). The circuit equivalent of a FeFET is shown in Figure 2.7 and it is essentially a ferroelectric capacitor in series with the gate of a conventional MOSFET. The  $V_{GS}$  equivalent would be derived by the equation:

$$V_{GS} = (V_{FE} + V_{MOS}) (2.2.1)$$

When a strong positive  $V_{GS}$  is applied, it causes the ferroelectric layer to switch its polarity in such a way that it now manifests a positive voltage towards the MOSFET structure (Figure 2.7). This attracts electrons towards the gate and thus lowers the voltage needed to fully create the conductive channel (Low  $V_{th}$ ). On the contrary, if a strong negative pulse is applied, the ferroelectric layer will be polarized in such way that a negative voltage will be manifested towards the MOSFET structure, hence, a repulsion of electrons will occur and the  $V_{th}$  will be raised (High  $V_{th}$ ).

Figure 2.6: The I-V characteristics for the two FeFET states

Figure 2.7: Circuit equivalent of FeFET device

Figure 2.6 shows the different I-V characteristic curves between the LVT and HVT states. The voltage window between these two is also called *memory window* and it is the voltage range within which a non-destructive read can take place. FeFET is a voltage-driven device, but current sensing is used

to retrieve the value stored. As with regular MOSFETs, FeFETs' drain-source current is given by the following equation:

$$I_D = \frac{1}{2} \cdot \mu \cdot C_{OX} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(2.2.2)

FeFETs have demonstrated several advantages such as high density, low power, non-volatility, high read/write speeds, random access, high endurance and non-destructive readout. However, relatively short retention times is the major disadvantage of FeFETs which happens due to gate leakage current, depolarization field and carrier trapping in the gate-dielectric stack [17, 18].

### 2.3. FeFET Advancements and Materials

The previous section was an overview of the basic FeFET functional principles. However, factors like memory window, retention time and endurance, are defined by the materials used and the unique properties associated with them. As we already mentioned, in 1974, the first n-channel FeFET on silicon wafer with  $(Bi_4Ti_3O_{12})$  as FE-material was reported. After one year, K. Sugibuchi et al., [19] reported the first p-channel FeFET on silicon wafer with same FE-material and structure. Both of them used a Metal-Ferroelectric-Semiconductor (MFS) structure.

Coercive field  $(\varepsilon_c)$  and remnant polarization  $(P_r)$  are the critical factors of FE-film used in FeFETs; both of them can be modulated with a capping layer, annealing conditions and doping concentration [20]. Dielectric breakdown and gate leakage are the serious issues associated with MFIS-structure based FeFETs, therefore, the gate stack must be carefully designed so that the program/erase voltage can be effectively distributed between the FE and insulator layers. Both gate leakage current and depolarization field  $(E_{dp})$  degrade the retention time of FeFETs; the  $E_{dp}$  reduces the polarization in the FE- layer which then leads to the reduction in memory retention time [21].  $E_{dp}$  can be calculated by the following formula:

$$E_{dp} = \frac{PC_{FE}}{\varepsilon (C_{IS} + C_{FE})} \tag{2.3.1}$$

P,  $C_{FE}$ ,  $\varepsilon$  and  $C_{IS}$  represent polarization, FE-capacitance, permittivity of FE-film and semiconductor capacitance respectively.

Quite often, an insulating layer will be used to prevent the chemical reaction between Si-wafer and the FE-material. However, this will also create a depolarization field in the gate stack which reduces the memory retention time. In general, FeFETs with an MFIS structure demonstrate poor memory window and retention time. The MFMIS-structure has emerged as an excellent solution to mitigate the limitations of MFIS-structure based FeFETs [22]. FeFETs with MFMIS structure can be operated with lower voltages compared with FeFETs having MFIS structure due to the enhancement of FE capacitance.

The introduction of insulating layer leads to the increase of writing voltage due to the voltage drop across it. In order to reduce this voltage drop, a high-k material is usually preferred, however, usage of high-k dielectrics (e.g. HfO<sub>2</sub>) creates a poor interface between Si-wafer and the high-k material that severely degrades the memory performance of FeFETs. These problems can be effectively mitigated by employing an intermediate electrode in between insulating and FE-layers, which leads to the MFMIS structure [23]. That is, FeFETs with MFMIS structure showcase perfect non-destructive readout and disturb free write operation compared with FeFETs with MFIS structure.

The memory performance of FeFETs is highly sensitive to temperature; it is reported that an increase in temperature leads to the increase of leakage current and the decrease of  $I_{ON}/I_{OFF}$  and memory window [24], [25], [26], [27]. In 2011, Tang et al., [25] experimentally demonstrated an MFIS-FeFET using HfTaO buffer layer and SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> FE-film that showcased a memory window,  $I_{ON}/I_{OFF}$  and endurance of 0.9 V,  $10^7$  and  $2 \times 10^{11}$  cycles respectively. In the same year, Böscke et al., [24], [26] discovered ferroelectricity in HfO<sub>2</sub>, a major breakthrough in the development of FeFETs due to the fact that HfO<sub>2</sub> provides better scalability compared with strontium-bismuth titanate FE-material. In 2013, Mueller et al., [28] experimentally demonstrated a FeFET using Si-doped HfO<sub>2</sub> (Si:HfO<sub>2</sub>) FE-film.

Figure 2.8: FeFET structure with silicon-doped hafnia as a FE layer.

In 2017, Chatterjee et al., [20] successfully fabricated a FD-SOI FeFET using gate last, self aligned process featuring  $Hf_{0.8}Zr_{0.2}O_2$  FE-film that showcased a memory window, ION/IOFF, retention time and endurance of 0.5 V,  $10^6$ , 10 years and  $10^7$  cycles respectively.

FeFETs are a field of active research and new structures and proposals are constantly published. A few indicative examples of their promising future can be found in the research by Zeng et al., [29] a FeFET was successfully fabricated, featuring HfN top electrode and Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> (HZO) FE-film that showcased a MW and endurance of 0.92 V and  $10^4$  cycles, respectively. In 2019, Huan Liu et al., [30] were the first to demonstrate a p-channel FeFET on Ge wafer featuring Ge-channel, TaN gate electrode and  $ZrO_2$  FE-film that exhibited a memory window and endurance of 0.78 V and  $10^7$  cycles respectively. S. Ohmi et al., [31] reported a FeFET having metal-FE-semiconductor architecture that exhibited a memory window and endurance of 1.2 V and  $10^{10}$  cycles, respectively. It was also reported that forming HfO<sub>2</sub> FE-film with Kr/O2-plasma sputtering, offers superior polarization, reduced leakage current, improved ferroelectric capacitance, improved the drain current and provided superior memory window and endurance characteristics compared with HfO<sub>2</sub> formed by using Ar/O<sub>2</sub>-plasma sputtering. Finally, in 2022, Dutta et al., [32] successfully fabricated a interfacial layer-free FeFET featuring Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> FE-film and indium tungsten oxide (IWO) semiconductor channel that offers high speed, low voltage memory operation and exhibited a MW and endurance of 1.6 V and  $10^{11}$  cycles, respectively. The elimination of interfacial layer efficiently minimizes the charge traps which in turn lead to the reduction in write voltage and improvement in endurance.

Large write voltage remains a serious issue in FeFETs, mainly due to the voltage drop across the interfacial layer. To reduce write voltage, the electric field across the interfacial layer should be reduced, however, it has been shown that this causes a severe degradation of the memory window. Reducing write voltage without degrading memory window is a ongoing challenge in the development of FeFETs [33].

For this thesis, the experiments took place using a FeFET model calibrated with data from fabricated FeFETs. The FeFETs were build based on an MFMIS structure and using an (HZO)  $Hf_{0.4}Zr_{0.}O_2$  ferroelectric layer with 10nm thickness [34].

### 2.4. Challenges of HfO<sub>2</sub> Integration

Despite significant progress since its discovery in 2011, the implementation of ferroelectric  $HfO_2$  still presents certain key non-ideal properties that affect its observed behavior. This section addresses some of the most commonly discussed challenges, according to [35].

### 2.4.1. Depolarization Field

The polar nature of ferroelectrics inevitably leads to the generation of a depolarization field, which significantly impacts the characteristics of thin films. This depolarization field is caused by uncompensated charges at the interfaces. From device fabrication, the presence of a dielectric layer at the ferroelectric/metal interface, often referred to as a dead layer, is commonly present [36]. This dielectric layer hinders the screening of surface charges, as the counter charges in the metal electrode are spatially separated from the surface charge. The unscreened charges create a depolarization field across the ferroelectric, reducing the effective polarization and limiting thickness scaling, with its impact becoming

more pronounced in thinner films [37–39]. Even in the case of having no dielectric interface layer, a depolarization field will still be present, since even metal electrodes will have a non-zero screening length. However, the larger coercive field in  $HfO_2$ -based ferroelectrics, compared to the traditional perovskite ferroelectrics, should enable  $HfO_2$  to withstand higher depolarization fields [36, 40]. The depolarization field is the cause of reduced memory state retention for FeFETs. The understanding and control of depolarization fields in ferroelectrics is of key importance for their use in technological applications.

### 2.4.2. Retention

In ferroelectric devices, *retention* refers to the ability of a ferroelectric material to maintain its polarization over time, in the absence of an external electric field. Retention is an important characteristic because it determines how long the ferroelectric state can be maintained, once the external electric field is removed. Retention performance is influenced by various factors, including material properties, device architecture, and operating conditions [35, 41]. It is of great importance to design FeFETs in a way that ensures the reliability and longevity of the device, especially when it comes to applications where stored information needs to be preserved for extended periods.

### 2.4.3. Wake-up

It is common in  $HfO_2$ -based ferroelectrics to observe what is called a "wake-up" effect, which is a gradual increase of the  $P_r$ , during voltage cycling. It is typical that the wake-up effect is especially strong during the first, approximately, 1000 cycles. Initially, it was believed that the wake-up effect only stemmed from the redistribution of oxygen vacancies [35, 42–44], causing domains in the film to de-pin which results in an elevated  $P_r$ . However, recent evidence suggests that the main contribution is a phase transition from the t- to the o-phase, or even m-phase to o-phase during voltage cycling, offering an alternative explanation for the observed increase in  $P_r$ . Currently, substantial efforts are underway to mitigate the presence of the wake-up effect in  $HfO_2$ -based ferroelectrics by engineering the thermal treatment [35, 45], introducing La dopants [46], and optimizing the deposition conditions.

### 2.4.4. Endurance

The ability of a ferroelectric material to undergo repeated cycles of polarization switching without significant degradation, is called endurance. However,  $HfO_2$ -based ferroelectrics, often experience hard breakdown before any significant degradation of the polarization occurs. For this reason, the "cycles until breakdown" is typically what is reported in the literature. Reported endurance values for  $HfO_2$  ferroelectrics span a range from  $10^4$  to  $10^{11}$  cycles. Comparison of different devices with regards to endurance should be done carefully, since endurance is dependent on both frequency and field magnitude. A better metric could be the time until break down, which, as demonstrated in the work by Toprasertpong et al., is constant, independently of the cycling frequency used [47]. Additionally, thinner films are expected to have improved endurance compared to thicker films, since the breakdown field decreases with thickness [35, 47].

### 2.4.5. Fatigue

A ferroelectric material that goes over repeated switching of its polarization under the influence of an external electric field, it can experience *fatigue*. These phenomenon is manifested as the reduction of the material's ability to maintain a stable and well-defined polarization state. Several mechanisms contribute to fatigue in ferroelectrics, with one common factor being the accumulation of defects in the material, during the polarization-switching process. Over time, these defects can impede the movement of domain walls (pinning) and eventually hinder the ability of the material to maintain a stable polarization state. As a result, fatigue can play a major role in the material's reliability and performance.

### 2.5. Structures and Applications

Ferroelectric FET technology is emerging in many application domains ranging from non-volatile storage, to reconfigurable hardware. Some examples of promising FeFET based applications are emulating atomic neuromorphic operations [48], hyper-dimensional encoding [49], multiply-accumulate operation crossbars [50] and energy/area efficient FPGA fabrics [51]. Clearly, both Academia and Industry consider using FeFET devices in promising solutions for various limitations faced by contemporary computing technology.

### 2.5.1. Memories

FeFETs are by definition a very promising candidate for new types of memories.

### **FeRAM**

Ferroelectric random-access memory (FeRAM) aims to replace dynamic random-access memory (DRAM) that constitutes the main memory of today's devices. The FeRAM architecture, resembles DRAM, but with one key difference, that the insulator in the capacitor is now a ferroelectric film, allowing for non-volatile charge storage. The read and write procedures are similar to DRAM and as the access transistor is opened, a voltage is applied across the ferroelectric capacitor. Then, if polarization reversal occurs, the sensed current will be significantly larger than a non-switched one. The non-volatile nature of FeRAM removes the need for refresh, which makes it significantly more power efficient. Recently a non-destructive read process for FeRAM was demonstrated, focusing on the difference in capacitance between the two polarization states, allowing for read endurance beyond  $10^11$  cycles [52]. Moreover, the charge density offered by ferroelectrics enables the integration of smaller capacitors. Despite these advantages, challenges such as limited endurance, and high write voltage still require further improvements before consumer products can be realized [53].

### **FeFET Crossbar Memories**

As already mentioned above, FeRAM aims to replace DRAM [35] and with regards to non-volatile storage, similar arguments can be made for the case of FeFETs aiming to be used as a replacement for Flash memory. Flash memory is a non-volatile semiconductor storage technology widely used in electronic devices such as USB drives, solid-state drives (SSDs), and memory cards. Its operation is based on a threshold voltage shift to realize two different memory states. It achieves this through the principle of storing charge on a floating gate buried between the gate electrode and transistor channel. As charges are trapped in the floating gate, the electric field of the gate electrode is screened. This increases the threshold voltage of the transistor. Although flash memory is well established, it suffers from limited endurance (typically < 10<sup>5</sup>) and very high write energy consumption (~1 nJ/bit) [35]. FeFETs, offers improved endurance, significantly improved energy efficiency and have the potential to replace flash memory in non-volatile applications. Using their two-level threshold voltages, they can act in a similar fashion to Flash, for memory applications. Another concept has been introduced where instead of integrating the ferroelectric directly in the gate stack of the transistor, a ferroelectric capacitor which shares one of its electrodes with the transistor gate, is connected in series with a traditional non-ferroelectric transistor. This device approach is called a ferroelectric-metal-field-effecttransistor (FeMFET) and allows for reduced programming voltages and generally better reliability when compared to the standard FeFETs[54].

### **2.5.2.** Neurons

Neuromorphic computing (like *spiking neural networks* - (SNNs)) is a relatively novel computing paradigm which attempts to mimic the human brain in the way computations are done. However, it is fundamentally different that the more popular, computer science driven, *machine learning* and its variants (such as *deep learning*) [55]. This attempt to capture brain-like features such as computation using spikes, holds the promise of improving the energy efficiency of computing platforms. In order to achieve an energy efficiency significantly better than the current CMOS-based neuronal circuits, researchers have turned to the emerging NVM devices.

The general working principle of a SNN can be described as follows: when a synapse receives a spike (i.e. an action potential), from its pre-synaptic neuron, it emits a post-synaptic potential (PSP). The PSP in turn stimulates the membrane potential of the post-synaptic neuron and the neuronal membrane potential exhibits temporal evolution where it integrates the PSPs. When the membrane potential crosses a threshold, the post-synaptic neuron fires, emitting an output spike.

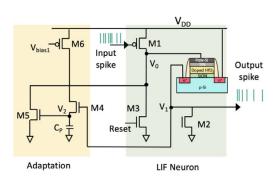

FeFETs are an excellent candidate for implementing a hardware spiking neuron, due to their partial polarization characteristics. This feature enables the polarization change of the FeFET layer through a sequence of smaller potentiation pulses, instead of a single longer pulse. It is evident that, the inherent ferroelectric polarization switching dynamics, closely resemble the neuronal membrane dynamics of the spiking neuron and can be used to emulate one. Figure 2.9 shows the proposal of spiking neuron based on a FeFET and three conventions transistors [56].

Figure 2.9: FeFET-based spiking neuron

### 2.5.3. Miscellaneous

### Multiply-accumulate operation crossbar

In-Memory Computing is a computational paradigm that uses memory cells organized in crossbar arrays to perform parallel, in-situ execution of operations such as Matrix-Vector Multiplications. While SRAM and DRAM cells could be used, challenges like static leakage, continuous refreshing and complex peripheral circuitry, are significant drawbacks. Emerging devices, such as ReRAM and FeFETs have reduced size and improved data retention, and can thus be attractive alternatives. ReRAMs, which were among the first devices used for building IMC crossbars. Despite having significantly smaller memory footprint compared to SRAMs and DRAMs, they come with some drawbacks too; sneak path effects and crossbar parasitics can significantly complicate their use. FeFET-based crossbars, can be used as an alternative due to their minimal leakage currents, compactness, compatibility with CMOS technology, and the elimination of selector devices, enabling the creation of larger and more efficient crossbar arrays.

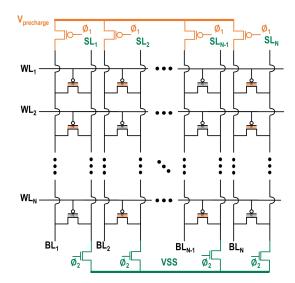

Figure 2.10 shows such a FeFET crossbar, used for IMC operations. The method proposed by [57] occurs in two phases. During the first phase, the BLs are precharged to a potential denoted as  $V_{precharge}$ . In the second phase, the WLs representing the input activations are enabled simultaneously. At the same time, the source lines (ScLs) are connected to a lower potential ( $V_{SS}$ ). This configuration allows the BLs to discharge linearly based on the stored data (programmed FeFET state) and input activations. Consequently, this arrangement facilitates a MAC operation through integration along the BL.

### **FPGAs**

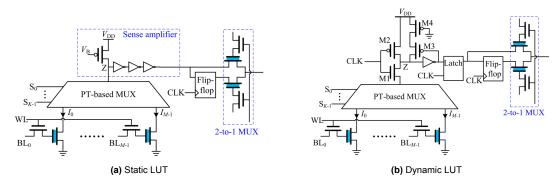

Since ferroelectric field-effect transistors (Fe-FETs) have the potential to reduce the power and area by integrating non-volatile storage elements with logic, this fact can be exploited to design lookup tables (LUTs) and routing switches. These elements have obvious utility in Field-

Figure 2.10: FeFET crossbar for IMC operations

Programmable Gate Arrays (FPGAs). It has been proposed in [51] that basic building blocks for FPGAs

Figure 2.11: Two FeFET-based FPGA LUTs

Figure 2.12: Routing elements with FeFETs

like lookup tables (LUTs) and routing elements can be beneficial in terms of area, energy, or both. Figure 2.11 shows two FeFET-based FPGA LUT structures.

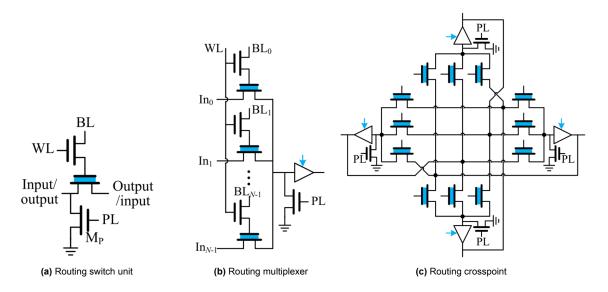

It is also proposed that FPGA routing units can be built using FeFETs. Figure 2.12 shows the routing elements built with FeFETs, from a simple routing switch unit, up to a routing crosspoint. The research towards this direction is very promising: despite the fact that programming the FeFETs consumes about  $35\times$  more energy and is over four orders of magnitude slower than programming an SRAM cell, much faster programming times (<50 ns) have been reported [48] with some reports as low as 10ns [58]. However, FeFET-based LUTs are reported to have a advantage over many aspects against competing technologies, when it comes to reading/accessing them. In the same work, the authors reported a 55% reduction in the number of transistors needed for a LUT, when compared to traditional CMOS, while the power-delay product (PDP) was reduced up to  $16\times$ .

### Gates, Latches, Flip-Flops

Considering the gate of a FeFET as one input and the stored value as the second, a FeFET can be used as a 1-transistor, 2-input AND gate, which will produce the result in two phases. In the first phase, the input 'B' will have to be stored in it, while in the second, the input 'A' will be asserted on the gate pin. Considering a  $V_r=0.6V$ , an LVT (logic 1) value of 0,4V and an HVT (logic 0) value of 0.8V the following truth table can be realized:

Batteryless devices leveraging energy-harvesting methods (such as solar panels, vibrations, and radio frequency (RF)) can frequently lose their computing progress in case of abrupt power outages. In these cases, the devices can be benefited by a mechanism that stores their current computing state, which

| Α | В | OUT | VG   | Vth  | IDS |

|---|---|-----|------|------|-----|

| 0 | 0 | 0   | 0V   | 0.8V | -   |

| 1 | 0 | 0   | 0.6V | V8.0 | -   |

| 0 | 1 | 0   | 0V   | 0.4V | -   |

| 1 | 1 | 1   | 0.6V | 0.4V | YES |

**Table 2.1:** Truth table with representing voltages for a 1FeFET AND gate

**Table 2.2:** Truth table with representing voltages for a 1FeFET AND gate

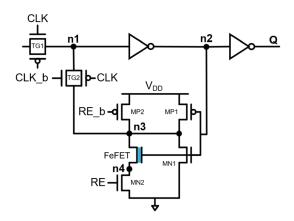

Figure 2.13: FeFET-based non-volatile flip-flop

can then be resumed after the device receives enough power again. In this, "intermittent computing" paradigm, FeFETs can play a crucial role by being used in a new type of non-volatile latches and flip-flops (NVFFs). Several researchers have worked towards this direction and promising results have been reported. An indicative example is the NVFF designs reported by Kim et al [59], where it offers a per-cycle backup operation while it requires only 19% more area compared to a conventional flip-flop. Figure 2.13 shows the slave latch which is build around a FeFET device.

### 2.6. Simulation of FeFETs

FeFET devices are modelled using two main approaches: the Landau-Khalatnikoff (L-K) model which is based on time-dependent equations that describe the relationship between the polarization (P) and the electric field (E) [60] and the Preisach model, built upon the fact that a FE thin-film consists of multiple independent domains, with a distribution of coercive fields [61], [34]. While L-K model is useful in specific cases, it also has a few drawbacks. The first being that it assumes a single domain FE material, while in practice it is usually poly-crystalline with multiple domains. The second limitation is that the  $V_{GS}$  applied to the FeFET can either keep the device polarization or switch it, as reported in [62]. It is impossible to turn the transistor completely off and maintain polarization, which means that the model cannot reproduce the basic non-volatile operation of FeFET [62]. There are several models that have been proposed for both approaches, both compact and physical [34, 63–65].

# **Overview of Memory Decoders**

In this chapter we will discuss about memory decoders and we will give the necessary background in order to understand the concepts described later. Memory decoders are an integral part of almost any type of memory, regardless of the level, type or the use case for it. Since memories are built in an array fashion, having a system that enables locating a specific area within that matrix, is needed. Depending on the usage of the decoders, they can be classified into two large categories, row decoders and column decoders. In this chapter we will focus on decoders for random-access memories (RAM) like SRAM or DRAM.

### 3.1. Row Decoders

A decoder is a circuit with many inputs and many outputs. Its job is to reduce the number of select signals by  $log_2$ , so if the number of inputs is N, then the number of outputs is  $2^N$ .

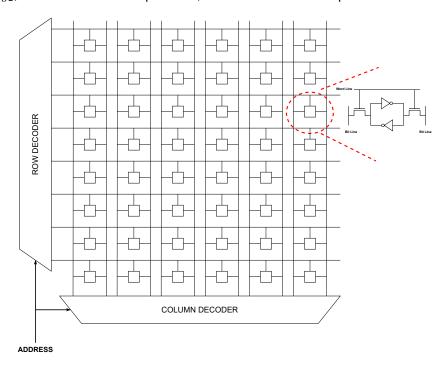

Figure 3.1: An SRAM array with decoders

Before we describe the specifics of row decoders it is important to review how exactly a memory array is built and how the decoders fit into the peripheral circuitry. Figure 3.1 depicts an SRAM array together

3.1. Row Decoders

with the row and the column decoder. The address signal is split into two parts, and being fed to the decoders. The row decoder is responsible for activating the correct word line, while the column decoder should activate the correct bitlines.

As a standard decoder design we can consider the use of multiple AND gates, one for every word line (WL). Each one of these AND gates has a unique combination of address inputs, or their inverted values. This means, that if we want to decode an 8-bit address (for a hypothetical  $256 \times 256$  SRAM array), this would effectively lead to a total of 256 lines and consequently, to 256 8-input AND gates. Eventually the logic function for activating the word lines would be like this:

$$WL_0 = \bar{A}_7 \bar{A}_6 \bar{A}_5 \bar{A}_4 \bar{A}_3 \bar{A}_2 \bar{A}_1 \bar{A}_0 \tag{3.1.1}$$

$$WL_{255} = A_7 A_6 A_5 A_4 A_3 A_2 A_1 A_0 (3.1.2)$$

Of course it is possible to use NOR logic:

$$WL_{255} = \overline{A_7 + A_6 + A_5 + A_4 + A_3 + A_2 + A_1 + A_0}$$

(3.1.3)

### 3.1.1. Static Decoders

The first way to implement an address decoder is by using static logic. This means that regular combinational logic is used without any clock signals or precharge phases. There are many ways to implement a static decoder and the most obvious is by using a sequence of AND (or NAND) gates, so that each one of them activates only with a specific combination of the input (address) signals. We have already shown this possibility

Figure 3.2: 8-input NAND gate. Each gate can drive a wordline.

in the equations 3.1.1 and 3.1.2. Figure 3.2 shows this NAND gate.

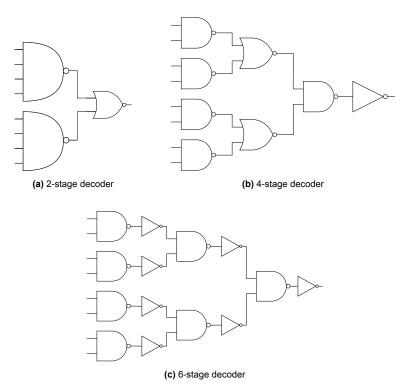

Of course, the problem with a gate like this is the large fanout, 256 bit cells, which can be prohibitive in terms of gate size and/or delay. Another approach could involve splitting the inputs into two smaller NAND gates and then wire them in a 2-input NOR, effectively having two stages. Splitting them to even more stages is also feasible and a few of these designs are shown in Figure 3.3. At this point the design with the best logical effort should be considered, which happens to be the 6-stage decoder. The implementation of such a decoder however, doesn't come without problems: each of the addresses is essentially driving 128 gates which is an enormous fanout, using long wires with overall high capacitance. On top of that, there will be problems with the bitcell pitch, essentially not having enough pitch space to fit all the signal wires.

### **Predecoding**

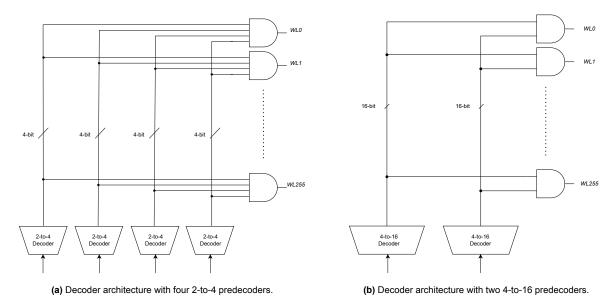

A solution to the aforementioned problems is implementing a predecoder in the architecture. The idea of a predecoder comes from the fact that neighbouring addresses differ only by one bit, hence a lot of the decoding hardware can be shared and reused. By grouping together inputs from the boolean expression, smaller decoders can be created; their outputs can be ANDed producing the final output. An alternative predecoding architecture for the example we already mentioned could be using 2 4:16 predecoders (depicted in figure 3.6). This architecture allows us to decode the 4 LSBs separately from the 4 MSBs and then AND the output of the predecoder circuits effectively producing the word line signal. This requires 256 AND gates, however, these AND gates are now smaller since they are having only two inputs, in addition, each address driver is driving only 8 gates which is far less than with the naive approach (128 gates) and thus the capacitance is significantly reduced. This architecture leads also to enormous area reductions, since less gates are needed (due to sharing) and the final stage 2-input AND gates are easily placed in the tight bit cell pitch.

3.1. Row Decoders

Using small predecoders as opposed to bigger ones does not produce better results in terms of area or performace. Figure 3.6 depicts a rough schematic comparison between two different approaches, the one using two 4:16 predecoders and the second using four 2:4 predecoders. The consequences of choosing the one over the other can be of great impact; the design using the smaller predecoders suffers from inefficiencies such as pitch fitting issues (due to the large AND gates that drive the word lines), switching higher capacitances due to the length/number of wires and demonstrating worse logical effort for the predecoder stages. Hence, it is important to remember that predecoding should be done with as large predecoders as possible.

Figure 3.3: Decoders with different number of stages.

Figure 3.4: Comparison of predecoder architectures.

3.2. Column Decoders 18

### 3.1.2. Dynamic Decoders

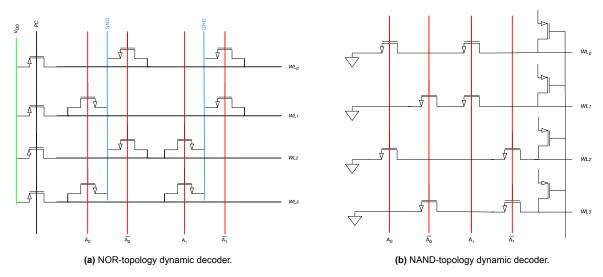

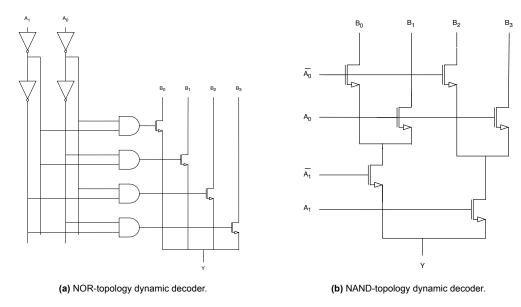

An alternative to the static decoder approach we described earlier would be the use of dynamic logic. Decoders designed with dynamic logic could have either a NOR or a NAND structure and their main advantage is speed, due to the limited usage of pMOS transistors and the lower capacitances being driven. However, the static power dissipation is higher and the circuit is more complex to design. For these reasons dynamic decoders are preferred in high speed designs and are considered as the state-of-the-art of the industry. Figure 3.5 shows the 2 different architectures of dynamic decoders. The advantage of a NOR topology is that it is faster, since only one transistor is required to open for the line to be discharged, however, this also requires that each transistor is connected to the ground as shown in Figure 3.5a. Even though the use of ground lines to each transistor looks trivial for small decoders, for larger ones it imposes significant complexity. On the other hand, NAND decoders are slower due to the fact that all transistors on the line need to open for the discharge to occur; their manufacturing is much simpler though, since each one of the transistors is just diffusion connected to their neighbour.

Figure 3.5: 2-input dynamic decoders