# **Adaptive RF Front-End Circuits**

Proefschrift

ter verkrijgen van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. J. T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 25 april 2005 om 13:00

door

Aleksandar TASIĆ

Electrical Engineer van Universiteit van Niš, Servie, geboren te Niš, Servie.

Dit proefschrift is goedgekeurd door de promotor: Prof. dr. J. R. Long

Samenstelling promotiecommissie:

|               | Rector Magnificus   | Voorzitter                                         |

|---------------|---------------------|----------------------------------------------------|

| Prof. dr.     | J.R. Long           | Technische Universiteit Delft, promotor            |

| Dr. ir.       | W.A. Serdijn        | Technische Universiteit Delft, toegevoegd promotor |

| Prof. dr.     | J.N. Burghartz      | Technische Universiteit Delft                      |

| Prof. dr. ir. | A.H.M. van Roermund | Technische Universiteit Eindhoven                  |

| Prof. dr. ir. | B. Nauta            | Universiteit Twente                                |

| Prof. dr.     | L. Larson           | University California San Diego                    |

| Dr. ir.       | M. Sanduleanu       | Philips Eindhoven                                  |

| Prof. dr. ir. | J.H. Huijsing       | Technische Universiteit Delft, reservelid          |

Cover: Adaptive Multi-Standard Image-Reject Downconverter: chip and printed circuit board photographs by A. Tasić.

ISBN 90-9019348-0

Copyright © 2005 by A. Tasić

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without prior written permission from the author.

Printed in the Netherlands by Print Partners IPSkamp.

to the missed opportunities, to the missed moments of joy, to the sleepless nights, to you, I owe most.

Аца

# CONTENTS

| С | ONTI  | ENTS                                       | I   |

|---|-------|--------------------------------------------|-----|

| L | IST O | <b>DF ABBREVIATIONS</b>                    | VII |

| 1 | INT   | RODUCTION                                  | 1   |

|   | 1.1   | Why Silicon?                               | 1   |

|   | 1.2   | Why Wireless And RF?                       | 2   |

|   | 1.3   | Why Low-Power And Adaptive RF?             | 4   |

|   | 1.4   | Why Multi-Standard And Adaptive RF?        | 7   |

|   | 1.5   | Thesis Objectives                          | 8   |

|   | 1.6   | Thesis Outline                             | 8   |

|   |       | References                                 | 10  |

| 2 | PER   | RFORMANCE PARAMETERS OF RF CIRCUITS        |     |

|   | 2.1   | Gain Parameters                            | 13  |

|   | 2     | .1.1 Stability                             | 15  |

|   | 2     | .1.2 Matched Gain Parameters               | 16  |

|   | 2.2   | Nonlinearity Parameters                    | 18  |

|   | 2     | .2.1 Intermodulation                       | 20  |

|   |       | 2.2.1.1 Third-order intercept point        | 21  |

|   |       | 2.2.1.2 Second-order intercept point       | 23  |

|   | 2.3   | Noise Figure                               | 23  |

|   | 2.4   | Phase Noise                                | 26  |

|   | 2.5   | Dynamic Range                              | 28  |

|   | 2.6   | <b>RF Front-End Performance Parameters</b> | 30  |

| <u>Adaptiv</u> | ve RF Front-End Circuits | II |

|----------------|--------------------------|----|

| 2.7            | Conclusions              | 33 |

|                | References               | 33 |

| 3 | 3 SPECTRUM-SIGNAL TRANSFORMATION |     |                                               |    |

|---|----------------------------------|-----|-----------------------------------------------|----|

|   | 3.1                              | Tr  | ansceiver Architectures                       | 40 |

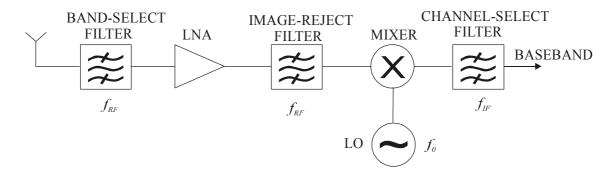

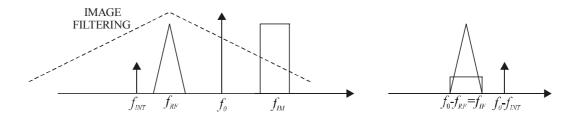

|   | 3.                               | 1.1 | Heterodyne Architectures                      | 40 |

|   | 3.                               | 1.2 | Homodyne Architectures                        | 42 |

|   |                                  | 3.1 | .2.1 Image-reject zero-IF architectures       | 43 |

|   |                                  | 3.1 | .2.2 Drawbacks of zero-IF architectures       | 45 |

|   | 3.                               | 1.3 | Low-IF Architectures                          | 45 |

|   | 3.                               | 1.4 | Wireless Standards and Employed Architectures | 46 |

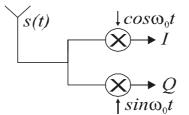

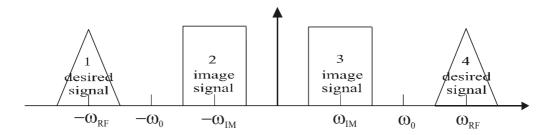

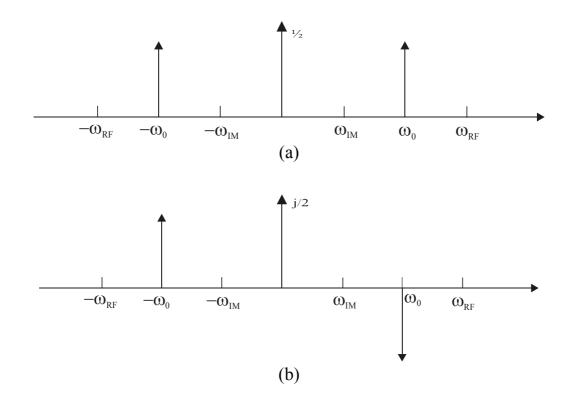

|   | 3.2                              | Sig | nal and Spectral Transformations              | 47 |

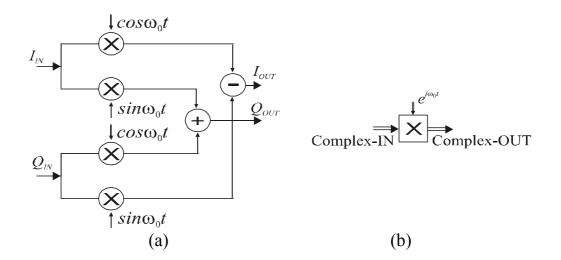

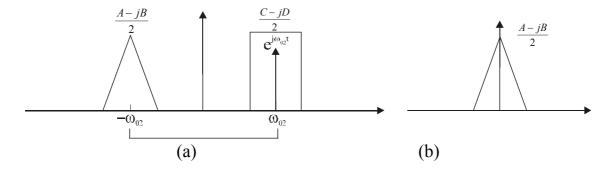

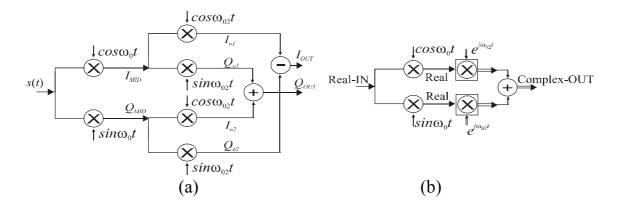

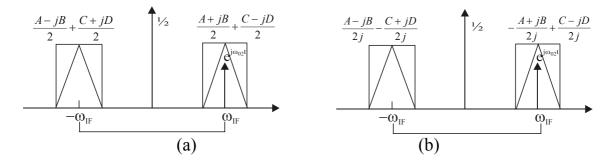

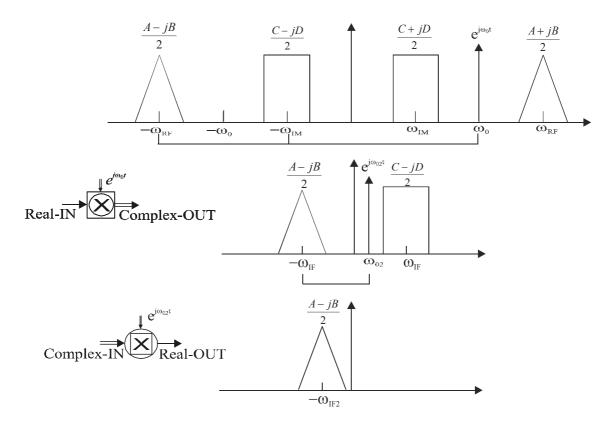

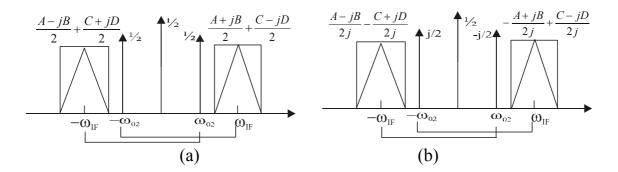

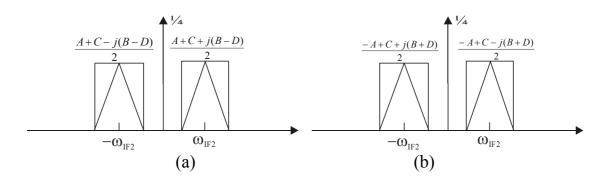

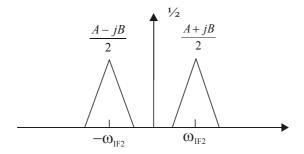

|   | 3.3                              | Mi  | xer-Oscillator Models                         | 52 |

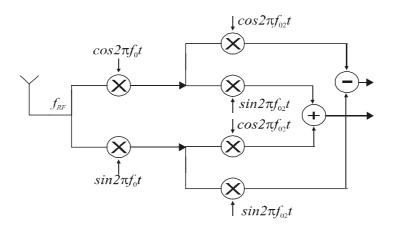

|   | 3.                               | 3.1 | Double-Real Mixer-Oscillator Model            | 53 |

|   | 3.                               | 3.2 | Single-Complex Mixer-Oscillator Model         | 55 |

|   |                                  | 3.3 | .2.1 Real-to-complex transformation           | 55 |

|   |                                  | 3.3 | .2.2 Complex-to-real transformation           | 57 |

|   | 3.                               | 3.3 | Double-Complex Mixer-Oscillator Model         | 58 |

|   | 3.4                              | Im  | age-Rejection Ratio Model                     | 62 |

|   | 3.5                              | IR  | R Model of Double-Quadrature Downconverters   | 64 |

|   | 3.6                              | Co  | nclusions                                     | 67 |

|   |                                  | Re  | ferences                                      | 68 |

| 4 | S   | ELECTION OF PERFORMANCE PARAMETERS FOR                     | RF |

|---|-----|------------------------------------------------------------|----|

|   | F   | RONT-END CIRCUITS                                          | 77 |

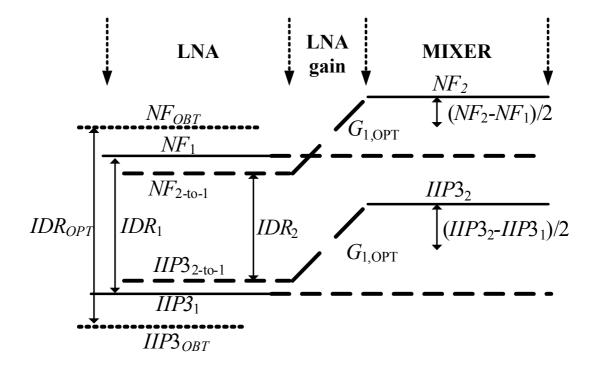

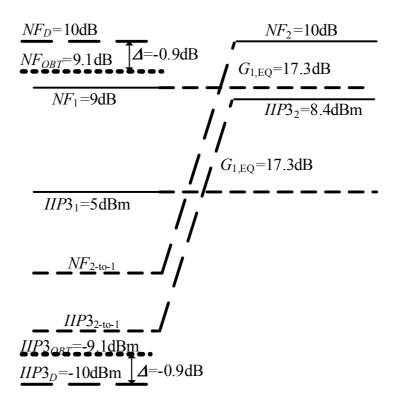

|   | 4.1 | System Considerations                                      | 78 |

|   | 4.2 | Independent Selection of NF And IIP3 Specifications        | 80 |

|   | 4.3 | Mutually Dependent Selection of NF And IIP3 Specifications | 85 |

|   | 4.  | 3.1 The Optimality Criterion                               | 85 |

| 3.2                                                       | The Equality Criterion                      | 88                                                                                                         |  |

|-----------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| 3.3                                                       | Optimality vs. Equality                     | 91                                                                                                         |  |

| Eq                                                        | uilibrium, Optimality and Equality Criteria | 92                                                                                                         |  |

| No                                                        | tes on Power Consumption                    | 94                                                                                                         |  |

| 6 <b>Performance Trade-offs in a Single RF Circuit</b> 95 |                                             |                                                                                                            |  |

| Co                                                        | nclusions                                   | 97                                                                                                         |  |

| Ret                                                       | ferences                                    | 98                                                                                                         |  |

|                                                           | 3.3<br>Eq<br>No<br>Per<br>Co                | 3.3 Optimality vs. Equality<br>Equilibrium, Optimality and Equality Criteria<br>Notes on Power Consumption |  |

| ADAPTIVITY OF LOW-NOISE AMPLIFIERS |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1                                | Adaptivity Phenomena of Amplifiers            | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.2                                | Performance Parameters of Inductively-Degener | rated Low-Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                    | Amplifiers                                    | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

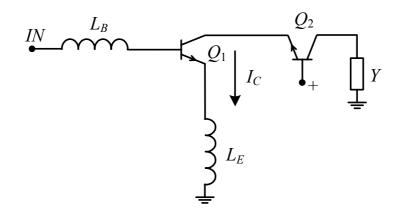

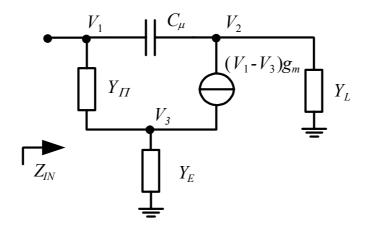

| 5.                                 | .2.1 Input-Impedance Model                    | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.                                 | .2.2 Gain Model                               | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

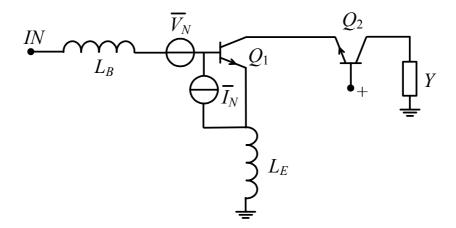

| 5.                                 | .2.3 Noise Model                              | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 5.2.3.1 Noise factor                          | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 5.2.3.2 Minimum noise factor                  | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 5.2.3.3 Optimum-minimum noise factor          | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.                                 | .2.4 Linearity Model                          | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.3                                | Adaptivity Models for Low-Noise Amplifiers    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.4                                | Conclusions                                   | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | References                                    | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                    | 5.1<br>5.2<br>5<br>5<br>5<br>5<br>5.3         | <ul> <li>5.1 Adaptivity Phenomena of Amplifiers</li> <li>5.2 Performance Parameters of Inductively-Degener<br/>Amplifiers</li> <li>5.2.1 Input-Impedance Model</li> <li>5.2.2 Gain Model</li> <li>5.2.3 Noise Model</li> <li>5.2.3.1 Noise factor</li> <li>5.2.3.2 Minimum noise factor</li> <li>5.2.3 Optimum-minimum noise factor</li> <li>5.2.4 Linearity Model</li> <li>5.3 Adaptivity Models for Low-Noise Amplifiers</li> <li>5.4 Conclusions</li> </ul> |

| 6 | ADAP   | TIVE VOLTAGE-CONTROLLED OSCILLATORS                 | 119   |

|---|--------|-----------------------------------------------------|-------|

|   | 6.1 Ad | aptivity Phenomena of Oscillators                   | 120   |

|   | 6.1.1  | Phase-Noise Tuning                                  | 120   |

|   | 6.1.2  | Frequency-Transconductance Tuning                   | 120   |

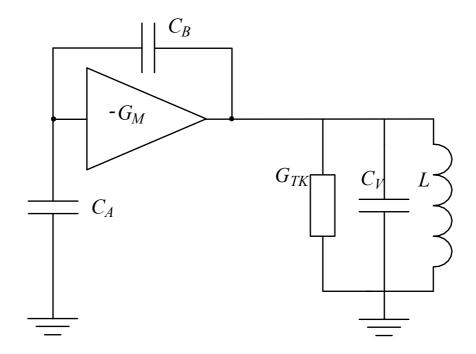

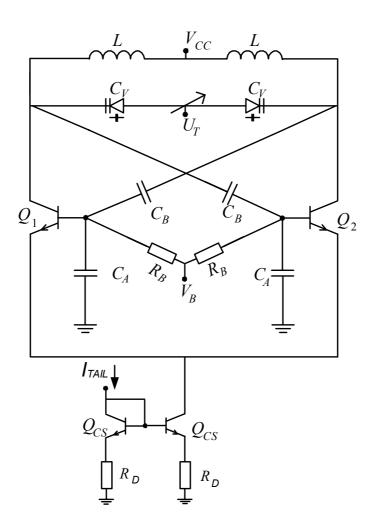

|   | 6.2 An | Adaptive Quasi-Tapped Voltage-Controlled Oscillator | · 121 |

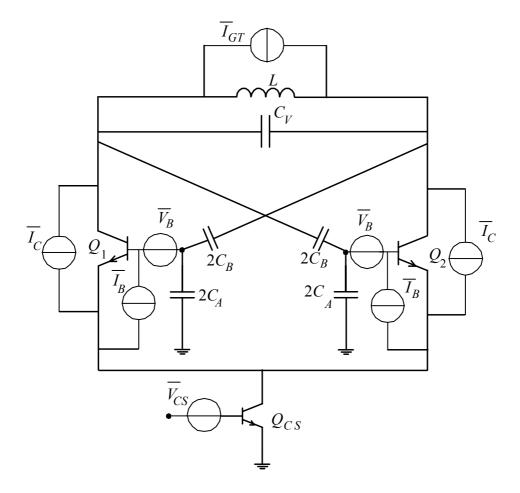

| 6.3 | Phase-Noise  | Model        | of      | Quasi-Tapped        | <b>Voltage</b> | -Controlled   |

|-----|--------------|--------------|---------|---------------------|----------------|---------------|

|     | Oscillators  |              |         |                     |                | 124           |

| 6.3 | .1 Time-V    | arying Trar  | nsfer I | Function            |                | 126           |

| 6.3 | .2 Base-Re   | esistance No | oise    |                     |                | 127           |

| 6.3 | .3 Transco   | onductor Sh  | ot No   | ise                 |                | 129           |

| 6.3 | .4 Tail-Cu   | rrent Noise  |         |                     |                | 129           |

| 6.3 | .5 Total O   | scillator No | oise    |                     |                | 131           |

| 6.3 | .6 Resonat   | nt-Inductive | e Dege  | eneration of Tail-  | Current So     | ource 132     |

|     | 6.3.6.1 Base | resistance   | e noi   | se transformation   | on of the      | e resonant-   |

|     | indu         | ctive degen  | erated  | l tail-current sour | ce             | 133           |

|     | 6.3.6.2 Base | - and colled | ctor-c  | urrent shot noise   | transforma     | ations of the |

|     | reso         | nant-inducti | ive de  | generated tail-cu   | rrent sourc    | e 134         |

|     | 6.3.6.3 Tota | l output no  | oise d  | of the resonant-    | inductive      | degenerated   |

|     | tail-o       | current sour | ce      |                     |                | 136           |

| 6.3 | .7 Resistiv  | e Degenera   | tion c  | of Tail-Current So  | ource          | 136           |

| 6.3 | .8 Adaptiv   | e Phase-No   | oise M  | lodel               |                | 138           |

|     | 6.3.8.1 Line | ar Phase-No  | oise N  | Iodel               |                | 138           |

| 6.4 | Phase-Noise  | e Performa   | nce o   | of Quasi-Tapped     | l Voltage-     | -Controlled   |

|     | Oscillators  |              |         |                     |                | 141           |

| 6.5 | Adaptivity   | Figures of   | Mer     | it of Voltage-C     | ontrolled      | Oscillators   |

|     |              |              |         |                     |                | 143           |

| 6.5 | .1 Phase-N   | loise Tunin  | g Ran   | ige                 |                | 143           |

| 6.5 | .2 Frequer   | icy-Transco  | onduct  | ance Sensitivity    |                | 144           |

| 6.6 | K-rail I     | Diagrams     | _       | Comprehens          | sive P         | erformance    |

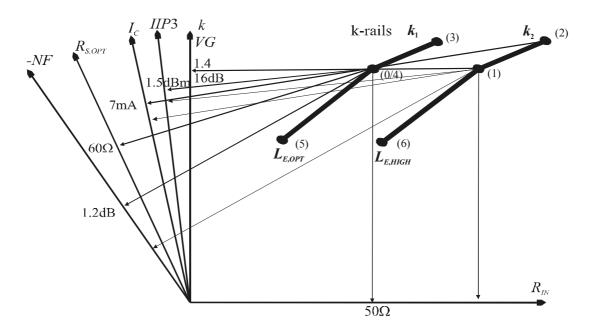

|     | Characteriz  | ation of Vo  | oltage  | -Controlled Osc     | illators       | 147           |

| 6.6 | .1 K-Rail    | Diagram      |         |                     |                | 148           |

| 6.6 | .2 K-Rails   | Diagram      |         |                     |                | 149           |

| 6.6 | .3 K-Loop    | Diagram      |         |                     |                | 151           |

| 6.6 | .4 An All-   | Round Exa    | mple    |                     |                | 153           |

| 6.7 | Conclusions  | 5            |         |                     |                | 155           |

|     | References   |              |         |                     |                | 156           |

| 7 | DESIC         | GN OF ADAPTIVE VOLTAGE-CONTROLLE                                    | D        |

|---|---------------|---------------------------------------------------------------------|----------|

|   | OSCI          | LLATORS AND ADAPTIVE RF FRONT-ENDS 15                               | 59       |

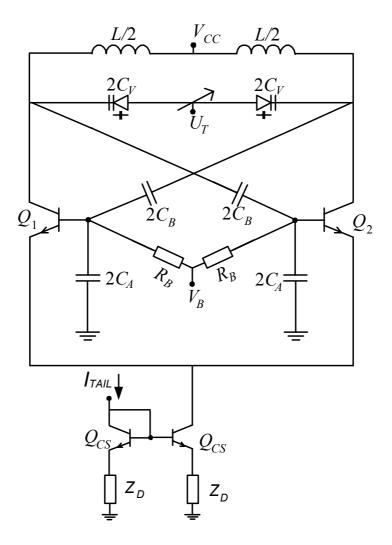

|   | 7.1 <b>An</b> | Adaptive Low-Power Voltage-Controlled Oscillator                    | 60       |

|   | 7.1.1         | Design for Adaptivity of Voltage-Controlled Oscillators             | 60       |

|   | 7.1.2         | Circuit Parameters of the Adaptive Voltage-Controlle                | ed       |

|   |               | Oscillator 10                                                       | 61       |

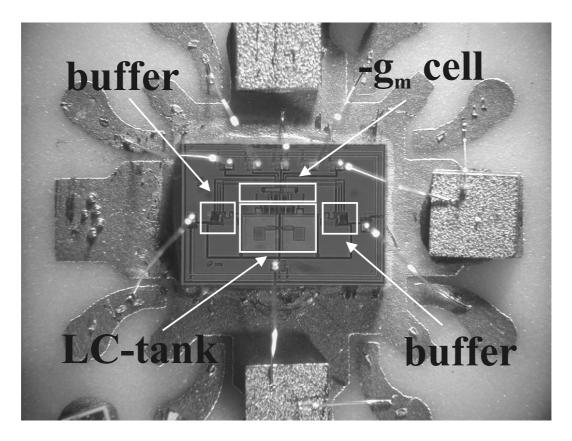

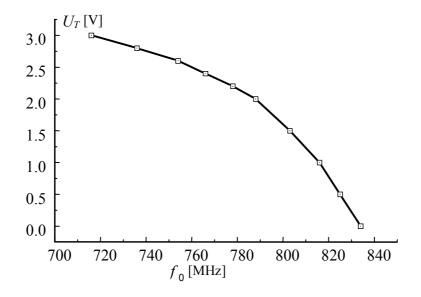

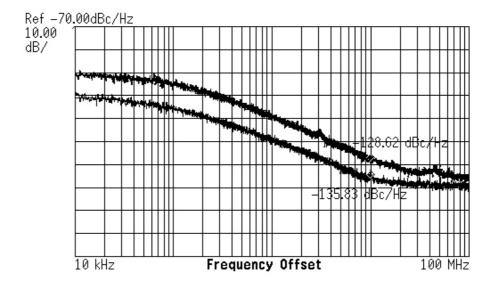

|   | 7.1.3         | Measurement Results for the Adaptive Voltage-Controlle              | ed       |

|   |               | Oscillator 10                                                       | 62       |

|   | 7.2 A N       | Multi-Standard Adaptive Voltage-Controlled Oscillator         10    | 66       |

|   | 7.2.1         | Designing for Adaptivity of Multi-Standard Voltage-Controlle        |          |

|   |               |                                                                     | 67       |

|   | 7.2.2         | Circuit Parameters of the Multi-Standard Adaptive Voltag            |          |

|   |               |                                                                     | 69       |

|   | 7.2.3         | Measurement Results for the Multi-Standard Adaptive Voltag          | •        |

|   |               |                                                                     | 70       |

|   |               | 1                                                                   | 74       |

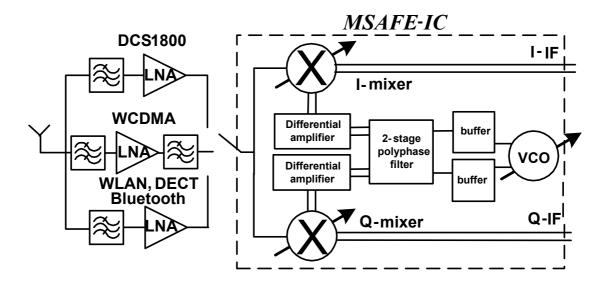

|   | 7.3.1         | System Considerations for Multi-Standard Adaptive RF From           |          |

|   | = 0           |                                                                     | 75       |

|   |               |                                                                     | 76       |

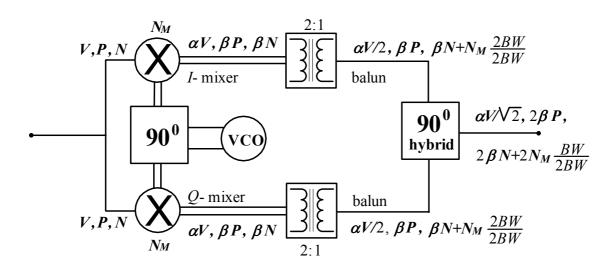

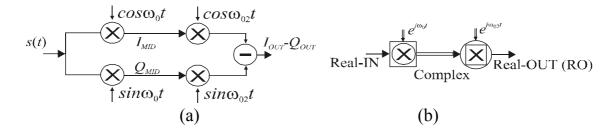

|   | 7.3.2         |                                                                     | 78       |

|   | 7.3.3         | 1                                                                   | 79       |

|   |               | 1                                                                   | 82<br>NE |

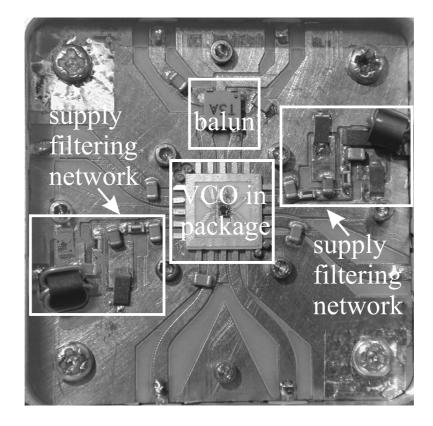

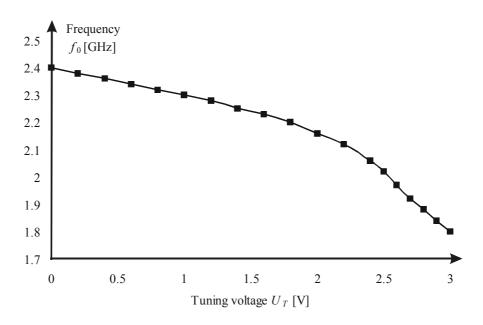

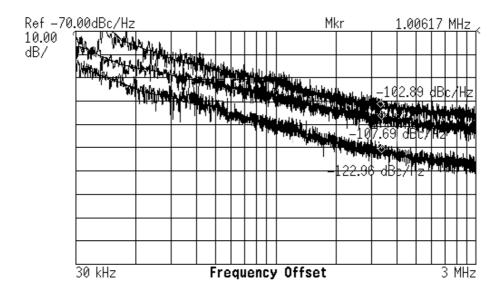

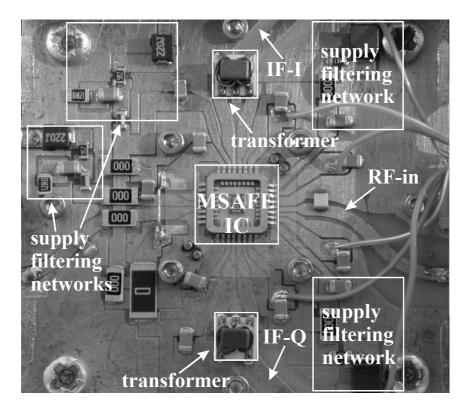

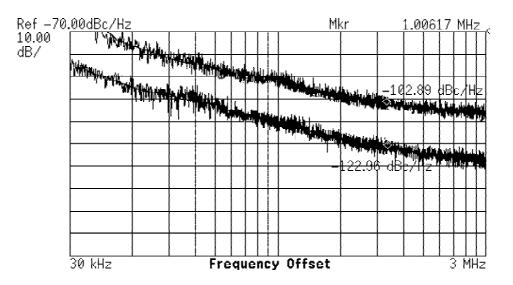

|   | 7.3.4         | Experimental Results for the Multi-Standard Adaptive F<br>Front-End |          |

|   | 7.4 Co        |                                                                     | 83<br>88 |

|   |               |                                                                     |          |

|   | Kel           | ferences 18                                                         | 89       |

|   |               |                                                                     |          |

| 8 | CONC          | CLUDING REMARKS 19                                                  | )3       |

|   | 8.1 Sur       | mmary 19                                                            | 93       |

| A    | Real-to-Complex-to-Real          | <b>Fransformation</b> | ••••• |     |

|------|----------------------------------|-----------------------|-------|-----|

|      | Transformed-Feedback<br>olifiers | -                     |       |     |

| List | of Publications                  |                       | ••••  | 209 |

| Con  | clusies                          |                       | ••••  |     |

| Ack  | nowledgements                    |                       | ••••  |     |

| Biog | raphy                            |                       | ••••  |     |

# **LIST OF ABBREVIATIONS**

| ADC                  | Analog to Digital Converter                                        |

|----------------------|--------------------------------------------------------------------|

| AFOM                 | Adaptivity Figure of Merit                                         |

| BB                   | Baseband                                                           |

| CAD                  | Computer-Aided Design                                              |

| CGM                  | Frequency-Transconductance Tuning                                  |

| CMOS                 | Complementary Metal-Oxide Semiconductor                            |

| CPU                  | Central Processor Unit                                             |

| <b>D</b> (subscript) | Desired                                                            |

| DC-MO                | Double-Complex Mixer-Oscillator                                    |

| DCS1800              | Digital Cellular Communications                                    |

| DECT                 | Digital Enhanced Cordless Telecommunications                       |

| DR                   | Dynamic Range                                                      |

| DR-MO                | Double-Real Mixer-Oscillator                                       |

| DSB                  | Double-Side Band                                                   |

| E (subscript)        | Equilibrium                                                        |

| EQ (subscript)       | Equivalent                                                         |

| F                    | Noise Factor                                                       |

| FDD                  | Frequency-Division Duplex                                          |

| <b>G</b> (g)         | Gain                                                               |

| GMSK                 | Gaussian Minimum-Shift Keying                                      |

| GPRS                 | General Packet Radio Service                                       |

| GSM                  | Global System for Mobile Communications                            |

| IC                   | Integrated Circuit                                                 |

| ID                   | Inductive Degeneration                                             |

| IDR                  | Inverse Dynamic Range                                              |

| IF                   | Intermediate Frequency                                             |

| IM2                  | 2 <sup>nd</sup> -Order Intermodulation                             |

| IM3                  | 3 <sup>rd</sup> -Order Intermodulation                             |

| IIP3TR               | Input-Referred 3 <sup>rd</sup> -Order Intercept Point Tuning Range |

| IITR                 | Imaginary-Impedance Tuning Range                                   |

| IP2                  | 2 <sup>nd</sup> -Order Intercept Point                             |

| IP3                  | 3 <sup>rd</sup> -Order Intercept Point                             |

| IRR                  | Image-Rejection Ratio                                              |

| LC                   | Inductance-Capacitance                                             |

| LNA                  | Low-Noise Amplifier                                                |

|                      |                                                                    |

| LO                     | Local Oscillator                            |  |  |  |

|------------------------|---------------------------------------------|--|--|--|

| MB                     | Multi-Band                                  |  |  |  |

| MMS                    | Multimedia Message Service                  |  |  |  |

| ΜΟ                     | Mixer-Oscillator                            |  |  |  |

| MP3                    | Moving Pictures Experts Group Audio Layer 3 |  |  |  |

| MS                     | Multi-Standard                              |  |  |  |

| MSAFE                  | Multi-Standard Adaptive Front-End           |  |  |  |

| MSK                    | Minimum Shift Keying                        |  |  |  |

| MSM                    | Multi-Standard Module                       |  |  |  |

| NF                     | Noise Figure                                |  |  |  |

| NFTR                   | Noise-Figure Tuning Range                   |  |  |  |

| NI                     | Noise/Linearity                             |  |  |  |

| NT                     | Non-Tapped                                  |  |  |  |

| <b>OBT</b> (subscript) | Obtained                                    |  |  |  |

| <b>OPT</b> (subscript) | Optimum                                     |  |  |  |

| <b>OPT-MIN</b>         | Optimum-Minimum                             |  |  |  |

| PCB                    | Printed-Circuit Board                       |  |  |  |

| PN                     | Phase Noise                                 |  |  |  |

| PND                    | Phase-Noise Difference                      |  |  |  |

| PN-D                   | Phase-Noise Demanding                       |  |  |  |

| PN-M                   | Phase-Noise Moderate                        |  |  |  |

| PNR                    | Phase-Noise Ratio                           |  |  |  |

| PN-R                   | Phase-Noise Relaxed                         |  |  |  |

| PNTR                   | Phase-Noise Tuning Range                    |  |  |  |

| QPSK                   | Quadrature-Phase Shift Keying               |  |  |  |

| QT                     | Quasi-Tapped                                |  |  |  |

| RF                     | Radio Frequency                             |  |  |  |

| RD                     | Resistive Degeneration                      |  |  |  |

| RID                    | Resonant-Inductive Degeneration             |  |  |  |

| RITR                   | Real-Impedance Tuning Range                 |  |  |  |

| RSTR                   | Source-Impedance Tuning Range               |  |  |  |

| SFDR                   | Spurious-Free Dynamic Range                 |  |  |  |

| SIGE                   | Silicon-Germanium                           |  |  |  |

| SMS                    | Short Messaging System                      |  |  |  |

| SNR                    | Signal to Noise Ratio                       |  |  |  |

| SS                     | Spectrum Signal                             |  |  |  |

| SSB                    | Single-Side Band                            |  |  |  |

| S-UP (subscript)       | Start-Up<br>Safaty Start Up                 |  |  |  |

| S_S-UP (subscript)     | Safety Start-Up<br>Tail-Current Noise       |  |  |  |

| TCN<br>TCS             |                                             |  |  |  |

| TCS                    | Tail-Current Source                         |  |  |  |

| TFD        | Transformed-Feedback Degeneration         |

|------------|-------------------------------------------|

| TDD        | Time-Division Duplex                      |

| VCO        | Voltage-Controlled Oscillator             |

| VG         | Voltage Gain                              |

| VGTR       | Voltage-Gain Tuning Range                 |

| WCDMA      | Wideband Code Division Multiple Access    |

| WLAN       | Wireless Local Area Network               |

| 16QAM      | 16 Symbol Quadrature Amplitude Modulation |

| 2G         | 2 <sup>nd</sup> -Generation               |

| <b>3</b> G | 3 <sup>rd</sup> -Generation               |

One emerging worldwide vision of communication is that wireless communications and ambient intelligence will be highly advantageous in satisfying our yearning for information at any time and anywhere. Electronics that is sensitive to people's needs, personalized to their requirements, anticipatory of their behavior and responsive to their presence is one visionary conception of ambient intelligence [1]. Ambient intelligence technologies are expected to combine concepts of computing and intelligent ubiquitous systems. Technological breakthroughs will allow people to integrate electronics into more friendly environments: roll-up displays [2], intelligent mobiles [3], internet-enabled furniture [4]. People will relate to electronics in a more natural and comfortable way than they do now.

## 1.1 WHY SILICON?

The Greek messenger Phidippides set off for 42km with news of his nation's victory over the invading Persian army at the battle of Marathon in 490 BC, uttering the words "be joyful, we win" on arrival, before promptly dropping dead of exhaustion [5]. Since then, it took humanity some 2400 years to find a harmless way to send a spoken message over a distance.

The technique of using radio waves to send information, exercised by Heinrich Hertz in 1888, and later by Nikola Tesla [6], was demonstrated in 1895 by Guglielmo Marconi [7], who successfully established the first transatlantic radio contact. This event is often referred to as the beginning of wireless communications [8].

At the beginning of the 20<sup>th</sup> century, Lee De Forest developed a triode vacuum tube that allowed for the amplification of an applied signal [9]. Around his amplifier vacuum tube, he developed the first radio- and audio-frequency amplifiers [8]. In the 1930s, scientists at Bell Labs, seeking improved RF demodulation, resorted to the antiquated crystal detector, paving the way to a reliable semiconductor material, *silicon*.

The unreliability, heat dissipation problems and relatively large power consumption of vacuum tubes initiated a search for new means of amplification. In 1947, Walter Brattain and John Bardeen observed that a germanium crystal in touch with wires 0.002 inches apart could amplify an applied signal [10,11]. The point-contact transistor was born. Somewhat later, the junction (sandwich) transistor and field-effect transistor were implemented by William Shockley [12,13]. This trio was awarded the Nobel Prize for the invention of the transistor in 1956. The first commercial use of the transistor was in telephone equipment in the early 1950s [8].

The first transistorized radio appeared in 1954, and was the fastest selling retail object of that time. Using discrete components in those days, transistor circuits occupied a number of printed circuit boards the size of postcards. The idea of integrating a complete circuit on a single slice of silicon was implemented independently in 1958 by Jack Kilby [14] and Robert Noyce [15].

Thanks to techniques such as photolithography and computer-aided design, millions of transistors and other electronic components can be compactly integrated onto a silicon die smaller in size than a cornflake. Integrated circuits (IC) have paved the way to low-cost mass production of electronic equipment. A continuous reduction of the minimum feature sizes, i.e., scaling of microelectronic devices, reduces the cost per function by 25% per year and promotes IC market growth with 17% per year. Doubling of the number of components per chip every 18 months (Moore's Law) [16] has led to improved productivity and improved quality of human life through the proliferation of consumer and industrial electronics.

## **1.2 WHY WIRELESS AND RF?**

Progress in silicon IC technology and innovations in IC design have enabled mobility of wireless consumer products and services.

Having started out with limited performance capabilities beyond simple telephony, mobile communications technologies are now entering all aspects of our lives. Mobile equipment today is shaped by user and *application* demands on the one hand and enabling semiconductor process *technologies* as well as radio frequency microelectronics on the other. Main drivers for mobile wireless devices are related to:

• **cost**, which depends on volume of production, size of mobile units, power consumption, and performance.

- **power consumption**, which depends on available frequency spectrum, functionality, and performance.

- **performance**, which depends on applications, standards and protocols.

The factors that make an integrated piece of silicon a desirable item are: mobility, high performance (voice, text and video transfer), low cost (advances in IC processing technology) and long lifetime (low power consumption).

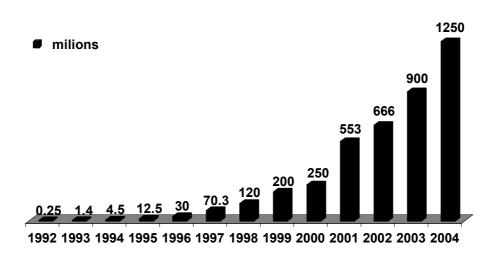

An example of the enormous expansion of the wireless market is shown in Fig. 1.1. At this moment (late 2004), the total number of global mobile users amounts to 1.52 billion, whereas the number of GSM (Global System for Mobile communications) users is estimated at 1.25 billion (82% of the total) [17]. By 2007, the worldwide wireless telephone market is projected to grow to more than 2 billion subscribers [18].

Figure 1.1: GSM growth for the period 1992-2004.

Global handset sales will grow 14% in 2004 to 596 million units, and 11% to 662 million units in 2005, as demand continues in mature markets and surges in developing markets [19]. GSM sales are projected to grow at a Compound Annual Growth Rate of 11% through 2009, as color-, MMS-(Multimedia Messages Service), camera- and Java-enabled devices become widely available, and the cost of wireless services declines [19].

Despite the expansive sales growth of wireless devices, the use of wireless services generates even greater profit for telecom companies. For example, more than 15 billion SMS (Short Messaging System) messages were sent per month across Europe in 2004 [17]. Furthermore, even larger growth requires many new services provided by mobile equipment: MMS, web access, and e-mail. The use of cellular phones for web access is forecast to exceed the use of personal computers as terminals by 2006 [20].

By introducing third-generation (3G) systems [21], more spectrum for voice services has become available, whilst enabling a wider variety of data and multimedia services. 3G handset sales account for 21% of total global sales in 2004. 98% of handsets sold worldwide in 2009 will be 3G devices, with the remainder being primarily GSM handsets sold into emerging markets and very cost sensitive segments of the mature markets [17].

Aside from the mobile phone market [16,21], there are many other wireless applications. Wireless connections to wired computer networks have become feasible. Wireless systems allow for cost-effective installation and deployment of electronics equipment by obviating the need for wires and cables. Wireless RF systems will undoubtedly spawn telemedicine, that is, remote, wireless medical monitoring. An intelligent transportation system that allow for communication and traffic control on the highway is yet another example of a mass market for wireless technology in future. Finally, to support all these applications, more sophisticated RF devices are required.

### **1.3 WHY LOW-POWER AND ADAPTIVE RF?**

The communication devices of today and the future will not only have to support applications ranging from text, telephony, audio, and graphics to video, but they will also have to maintain connections with many other devices in a variety of environments (and not only with a single base station). Moreover, they should be position aware, and perhaps wearable rather than just portable.

Both the lifetime and size of mobile equipment critically depends on the battery. Low-power circuits (e.g., an order of mW for analog front-end circuits [22]) prolong battery lifetime while meeting the performance requirements [22,23]. However, for wearable devices that require the use of the highest-volume and highest-weight density batteries [24], even a low-power design strategy can offer only limited savings.

A combination of multiple functional requirements and a small energy supply is an argument for the design of both adaptive low-power (i.e., poweraware) hardware and adaptive low-power software. Simply stated, as consumer demands outstrip the cost benefits achieved by Moore's Law and low-power circuit design, a new design direction is found in *adaptivity*. This eventually leads to smaller physical size, longer standby and active times, and enhanced functionality of mobile wearable devices.

The quality of service of mobile devices changes with the position and speed of mobile users. It also depends on the application, the number of users in a cell as well as their activity. A mobile device must handle the variable context efficiently due to scarce resources, especially limited battery power.

A power-aware (i.e., adaptive) RF design approach poses unique challenges: from hardware design to application software, throughout all layers of the underlying communication protocol (i.e., the processing technology, device level, circuit level, system level, as well as protocol level, software and application levels).

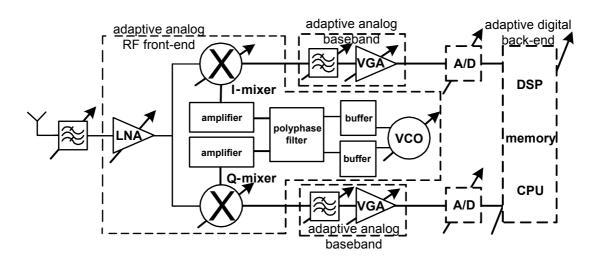

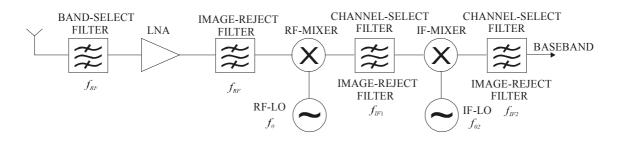

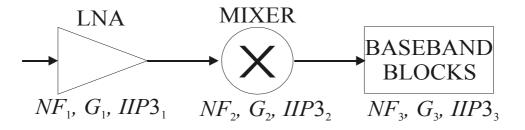

A block diagram of the receive part of a typical mobile device is shown in Fig. 1.2. This receiver consists of an analogue RF front-end, an analog baseband (analogue processing of the received signal), and a digital back-end consisting of a dedicated central processing unit (CPU) and a memory.

Whereas the transceiver circuits determine instantaneous power consumption, the average consumption depends on the power management of the complete system [25]. This implies that not only local, but also global (in all layers and at all time) power optimization and awareness are important for extending "lifetime" of mobile devices (time between battery recharges).

Figure 1.2: Block diagram of an adaptive receiver.

RF and power management have become the fastest growing segments in wireless IC revenue, due to the integration and increasingly complex power requirements, which are driven by advancing functionality (e.g., video, text) and transmission speeds in wireless devices [26]. The RF portion is estimated at \$3.8 billion or 19% of the wireless IC market [26].

Setting the performance parameters of an RF front-end by means of adaptive RF front-end circuitry [27] is a way to manage power consumption in the RF path of a receiver. Adaptive RF front-end circuits (shown in Fig. 1.2), viz., an adaptive low-noise amplifier, an adaptive voltage-controlled oscillator and an adaptive mixer, allow efficient use of scarce battery resources, thereby extending the lifetime of a mobile device. Furthermore, power-conscious adaptive analogue baseband circuits and digital back-end circuits enable complete hardware adaptivity. The theory and design of adaptive RF front-end circuits and adaptive RF front-ends is elaborated in detail in this thesis.

RF front-end robustness can be further improved by control of symbol rates, antenna beam patterns, transmitter power levels, and by control of circuit noise and linearity levels. For example, adaptive modulation and adaptive coding strategies [28], where the system can choose an optimal modulation and coding technique based on the temporal circumstances, can ameliorate the effects of multi-path fading, shadow fading, and path loss.

Graphical interaction with our direct environment combined with mobility is another intriguing concept in which low-power RF circuit design plays an important role [29]. If a lightweight video camera is attached to a mobile display for position tracking and recording of video, the hardware complexity must be reduced in order to keep the power consumption low. Since the RF front-end cannot operate with scarce resources, the power consumption can be reduced by limiting the processing and memory capabilities of the headset unit. In turn, this requires "clever" (power-aware) processing of received and transmitted data.

At an even higher hierarchical level, an example of a power-aware software implementation is the efficiency of a compiled code [30]. An example of application-level adaptivity is scaling the operating power and clock frequency in a general-purpose CPU under the control of power-aware applications, such as video and audio decoding software. Here, dynamic adjustment of the supply voltage can be traded for processor speed, allowing considerable power savings in the digital circuitry [31].

A framework for the exchange of performance and power consumption information between RF receiver, hard disk, CPU, operating system and the application has been developed within the Ubiquitous Communications project [25]. It is an example of a fully adaptive low-power mobile system.

## **1.4 WHY MULTI-STANDARD AND ADAPTIVE RF?**

Trends such as the provision of various services (text, audio, video) using different standards and smooth migration towards higher data rates and higher capacities for multimedia applications require designs that work across multiple standards, can easily be reused, and consume the minimum required power.

The increase of the performance per price ratio of radio-frequency integrated circuits (Moore's Law) drives the rapid development of wireless communication systems. The minimum required performance of a certain wireless system is determined by the standard that it implements. By enhancing performance of a system to cover multiple standards, its functionality increases as well. However, more performance for the same price can be achieved if the system hardware can be shared among different standards and adapted to different conditions and requirements [27].

The coexistence of numerous cellular systems requires multi-mode, multiband, and multi-standard mobile terminals [27]. To prolong talk time, it is desirable to share and/or switch transceiver building blocks in these handsets, without degrading the performance compared to that of single-standard transceivers.

Multi-standard front-ends typically use duplicate circuit blocks, or even entire radio front-ends for each standard. Although this approach is simpler to implement, it is neither optimal in cost nor in power consumption [32]. When different standards do not operate simultaneously, circuit blocks of a multi-standard handset can be shared. By using circuits that are able to trade off power consumption for performance on the fly, i.e., *adaptive multi-standard circuits*, considerable power can be saved. There is currently an apparent migration in RF IC design towards multi-mode multi-band integrated modules for low-noise amplifiers [33], oscillators [34], power amplifiers [12] and transceivers [27]. Design of multi-standard oscillators and multi-standard front-ends is discussed in detail in this thesis.

In addition to multimode capability at radio frequencies, adaptivity should be implemented at baseband frequencies as well. After a signal is downconverted to the baseband, it must be filtered, amplified and digitized. In order to accommodate multiple radio standards with different bandwidths and modulation schemes, such receivers require different channel, and imagereject filter bandwidths and different analogue-to-digital converter (ADC) resolutions. For example, a variable-bandwidth baseband filter and variableresolution ADC can be used to alternate between different modes of operation [35]. Finally, because adaptive multi-standard low-power RF front-ends are able to share building blocks across different standards, they have advantages over their predecessors: they use a smaller chip area, and most importantly, have a potential for lower overall cost.

## **1.5 THESIS OBJECTIVES**

The overall goal of this thesis is to develop design methodologies and a proofof-concept for analog RF front-end circuits that trade performance for power consumption in an *adaptive* way. This results in a transceiver front-end that either consumes less average power for a given performance or offers better performance for a given average power compared to a conventional transceiver front-end. For low-noise amplifiers and mixers, this comes down to trading off dynamic range for power consumption, whereas for oscillators a trade-off between phase noise or even oscillation frequency and power consumption is possible.

When exploring the fundamental and practical limits of an adaptive radio frequency implementation for multiple communication standards, we have examined basic aspects of the physical mechanisms underlying the operation of *adaptive* RF front-end circuits, and have developed design methodologies for their *structured synthesis*.

The techniques and methodologies developed in this project [36] have been validated by specifying requirements and implementing adaptive wireless receiver circuits and an adaptive wireless receiver front-end for multiple communication standards.

### **1.6 THESIS OUTLINE**

After this introductory chapter, basic *definitions* of RF performance parameters are reviewed in Chapter 2, viz., gain, linearity and noise parameters.

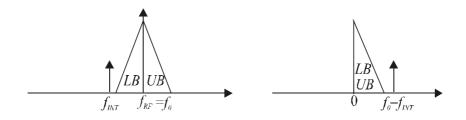

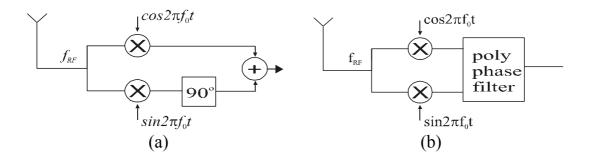

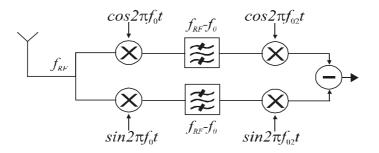

Chapter 3 discusses *spectrum* and *signal* (SS) *transformation* in various downconverter topologies. Classification of *mixer-oscillator* (MO) models is then introduced. Using the introduced SS presentation and the MO models, an all-encompassing analysis of a number of RF front-end architectures and RF front-end phenomena is performed.

A procedure to *select* noise and linearity specifications for RF system blocks is described in Chapter 4. Furthermore, an outline is given for the

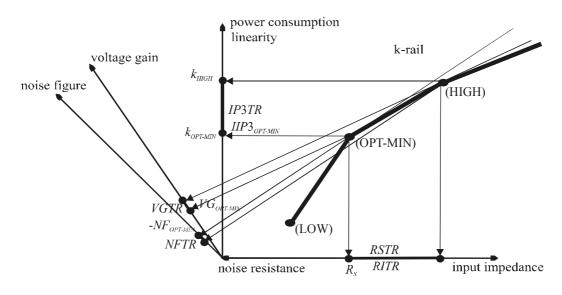

assigning of the mutually dependent noise and linearity performance parameters to RF front-end circuits. In addition, we derive conditions for the *optimal* dynamic range of a receiver, and for the *equal* noise and linearity improvements with respect to the required performance. Finally, some design trade-offs between performance parameters in a single RF circuit are described by means of a K-rail diagram: this diagram describes graphically the relationships between performance parameters of RF circuits.

Chapter 5 introduces amplifier adaptivity models (i.e., adaptivity figures of merit). They give insight into how low-noise amplifiers can trade performance (noise figure, gain, and linearity) for power consumption in an adaptive way. The performance trade-offs in adaptive low-noise amplifiers are discussed using amplifier K-rail diagrams.

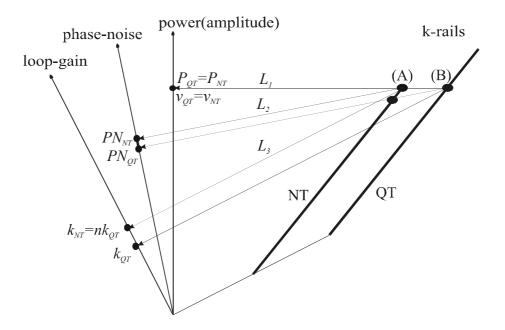

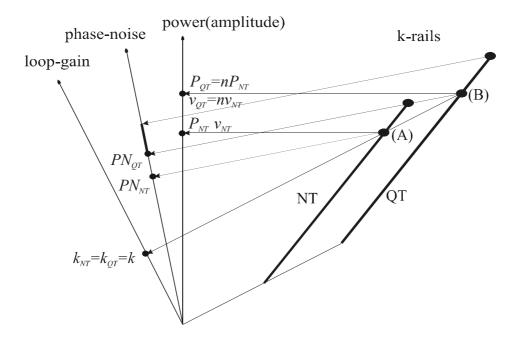

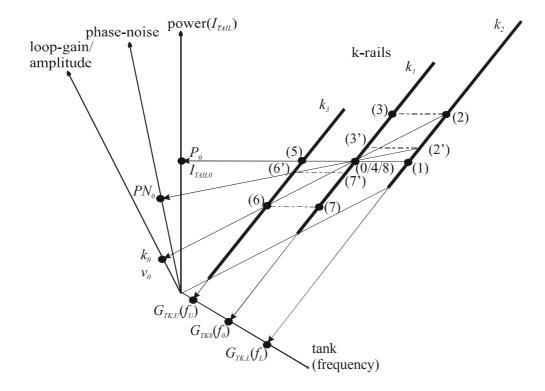

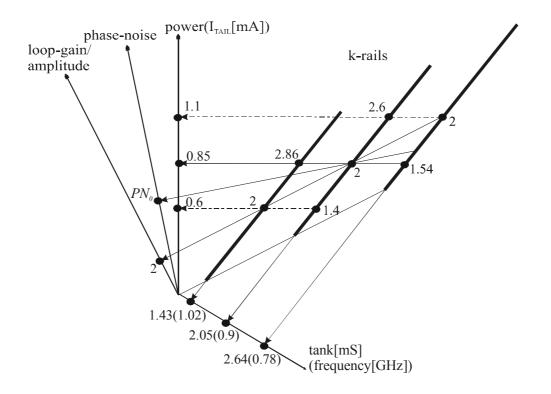

The application of *adaptivity* concepts to voltage-controlled oscillators is discussed in Chapter 6. The concepts of phase-noise tuning and frequencytransconductance tuning are first introduced. An adaptive oscillator and an adaptive phase-noise model are then presented. The adaptivity figures of merit viz.. phase-noise tuning range and are derived. the frequencytransconductance sensitivity. The subject of last section is a comprehensive performance characterization of voltage-controlled oscillators by means of Krail diagrams. Numerous relationships and trade-offs between oscillator performance parameters, such as voltage swing, tank conductance, power consumption, phase noise, and loop gain, are qualitatively and quantitatively described. Furthermore, the oscillator adaptivity figures of merit are captured using K-rail diagrams.

*Adaptivity* proofs-of-concept are discussed in Chapter 7. An 800MHz voltage-controlled oscillator design is presented with a phase-noise tuning range of 7dB and a factor 3.3 saving in power consumption. In addition, the chapter discusses an *adaptive, multi-standard*, second/third-generation (2G/3G) voltage-controlled oscillator design that satisfies the requirements of DCS1800, WCDMA, WLAN, Bluetooth and DECT standards. Finally, the results of an exploratory circuit design for a multi-standard, adaptive RF receiver front-end (MSAFE) are described. The multi-standard adaptive RF front-end (oscillator and mixers) satisfies the requirements of both 2<sup>nd</sup> and 3<sup>rd</sup> generation standards. This design allows adaptation between different standards by trading RF performance for current consumption. A supply current range from 9.9mA in the relaxed mode (2.4GHz DECT) to 20.2mA in the highest performance mode of operation (1.8GHz DCS1800) is realized.

Chapter 8 concludes and summarizes the thesis.

## REFERENCES

[1] Philips Research, Ambient Intelligence, http://www.research.philips.com/ technologies/syst\_softw/ami.

[2] http://www.research.philips.com/technologies/syst\_softw/ami/display.html

[3] Intelligent mobiles: context awareness and Bluetooth, http://www.research .philips.com/profile/people/researchers/intelligentmobiles.html

[4] http://www.research.philips.com/technologies/syst\_softw/ami/planet.html.

[5] http://encyclopedia.thefreedictionary.com/Phidippides.

[6] N. Tesla, Patent No. 645576, 1897.

[7] G. Marconi, Patent No. 763772, 1904.

[8] Bell Labs, http://www.belllabs.com.

[9] L. de Forest, "The Audion – Detector and Amplifier", *Proceedings IRE*, vol. 2, pp. 15-36, March 1914.

[10] J. Bardeen and W. H. Brattain, "The Transistor, a Semiconductor Triode", *Physical Review Letters*, 74:230, 1949.

[11] J. Bardeen and W. H. Brattain, "Conductivity of Germanium", *Physical Review Letters*, 75:1216, 1949.

[12] W. Shockley, "The Theory of P-N Junctions in Semiconductors and P-N Junction Transistors", *Bell System Technology Journal.*, 29:435, 1949.

[13] W. Shockley, "A Unipolar Field-Effect Transistor", *Proceedings IRE*, vol. 40, pp. 1365-1376, November, 1952.

[14] U.S. patent number 3138743.

[15] U.S. patent number 2981887.

[16] ITRS roadmap, 2003 edition, "Radio Frequency and Analog/Mixed-Signal Technologies for Wireless Communications" (a section of the Process Integration Chapter), http://www.itrs.com.

[17] Latest Mobile, GSM, Global, Handset, Base Station, & Regional Cellular Statistics, http://www.cellular.co.za/stats/stats-main.htm.

[18] K. Hyers, Service: Mobile Consumer Markets, Report Number IN0301117GW, Reed Electronics Group, August 2003, http://www.instat.com.

[19] N. Mawston, *Global Handset Sales Forecasts* 2004 – 2009, March 2004, http://www.strategyanalytics.com.

[20] NEMI Technology Roadmap, 2002 Edition, http://www.nemi.com.

[21] 3GPP, http://www.3gpp.org.

[22] A. Abidi et al., "Power-Conscious Design of Wireless Circuits and Systems", *Proceedings IEEE*, vol. 88, no. 10, pp. 1528-1545, October 2000.

[23] M. Pedram and J. Rabaey, *Power Aware Design Methodologies*, Kluwer Academic Publishers, 2002.

[24] L. Holguin et al., "Battery Technology for Mobile Computers", March 2002, http://www.dongkang.com.cn/BasicKnowledge/whitepaper/Battery TechnologyWhitePaper.pdf

[25] R. L. Lagendijk, Ubiquitous Communications Research Program, Final Program Report, http://www.ubicom.tudelft.nl, January 2002.

[26] Electronics Industry Market Research and Knowledge Network, Market Research Report Number DB375, July 2003, http://www.electronics.ca/reports/ic/rf\_ics.html#toc.

[27] A. Tasić, "Design of Adaptive Voltage-Controlled Oscillators and Adaptive RF Front-Ends", PhD thesis, Chapter 7.

[28] T. Keller and L. Hanzo, "Adaptive Multicarrier Modulation: a Convenient Framework for Time-Frequency Processing in Wireless Communications", *Proceedings IEEE*, vol. 88, no. 5, pp. 611-640, May 2000.

[29] W. Pasman et al., "Low-Latency Rendering for Mobile Augmented Reality", *Computers and Graphics*, vol. 23., no. 6, pp. 875-881, 1999.

[30] A. van der Schaaf et al., "Design of an Adaptive Interface between Video Compression and Transmission Protocols for Mobile Communications", *Proceedings of PV-2001*, pp. 395-404, April 2001.

[31] J. Pouwelse et al., "Dynamic Voltage Scaling on a Low-Power Microprocessor", *Proceedings Mobicom*, pp. 251-259, July 2001.

[32] J. Ryynanen, K. Kivekas, J. Jussila, A. Parssinen, K. Halonen, "A dualband RF front-end for WCDMA and GSM applications", *Proceedings CICC*, pp. 175-178, May 2000.

[33] H. Hashemi et al., "Concurrent Dual-Band LNAs and Receiver Architectures", *Proceedings VLSI*, pp. 247-250, June 2001.

[34] A. Tasić, W. A. Serdijn and J. R. Long, "Design of Multi-Standard Adaptive Voltage Controlled Oscillators", *IEEE Transactions on Microwave Theory and Technique*, vol. 53, no. 2, February 2005.

[35] X. Li and M. Ismail, "Architectures and Specs Help Analysis of Multi-Standard Receivers", http://www.planetanalog.com/story/OEG200303 12S0038.

[36] R. L. Lagendijk, Ubiquitous Communications – Updated Technical Annex 2000, P1.4: Low-Power Adaptive Front-End Circuits, STW, January 2000, http://www.ubicom.tudelft.nl.

# PERFORMANCE PARAMETERS OF RF CIRCUITS

Interdisciplinarity is essential to RF circuit design. An RF designer is a system designer, an analogue circuit designer, a microwave circuit designer, and a passive and active component designer.

Gain, noise figure, phase noise, distortion, and dynamic range are only a few of the parameters of interest to an RF IC designer, which are reviewed in this chapter. The determination of RF front-end performance parameters closes this chapter.

## 2.1 GAIN PARAMETERS

Current, voltage and power are fundamental circuit design quantities. The choice of the input and output quantities determines the transfer function of a network [1]: power two-port gain, voltage gain, current gain, transconductance gain and transimpedance gain. Usually, signal power is taken as a design variable when maximum power transfer (i.e., conjugate impedance match) is desired [2]. This is required at input of a receiver, because of the impedance match to the receive antenna (in order to avoid signal reflection), between RF front-end circuits in heterodyne receivers, and also when interconnect dimensions are on the order of the signal wavelength (microwave circuit design). On the other hand, voltage and/or current quantities can be the preferable design choice for RF front-end circuits in homodyne receivers where stages reside on-chip and power matching is not required (e.g., the interface between very large and very small impedances).

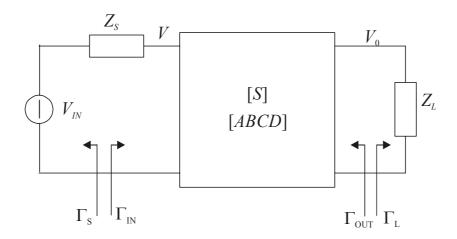

For a two-port network connected to load impedance  $Z_L$ , source impedance  $Z_S$ , and characterized by a scattering matrix [S] [3-10] and/or chain matrix [ABCD] (see Fig. 2.1), a number of gain definitions are in use [11-15].

The *transducer* power gain  $(g_T)$  stands for the ratio of the power delivered to the load  $(P_L)$  and the power available from the source  $(P_{AVS})$ . If  $\Gamma_{IN}$  and  $\Gamma_{OUT}$  are the input and the output reflection coefficients (which characterize quality of input and output two-port impedance matching) and  $\Gamma_S$  and  $\Gamma_L$  the reflection coefficients of the source and the load respectively, this gain definition becomes [12]:

$$g_{T} = \frac{P_{L}}{P_{AVS}} = \frac{\left|S_{21}\right|^{2} (1 - \left|\Gamma_{L}\right|^{2})(1 - \left|\Gamma_{S}\right|^{2})}{\left|1 - \Gamma_{IN}\Gamma_{S}\right|^{2} \left|1 - S_{22}\Gamma_{L}\right|^{2}},$$

(2.1)

where  $S_{11}$ - $S_{22}$  are the parameters of the two-port scattering matrix [S]. The Sparameters can be directly measured with a vector network analyzer, and are especially useful at high frequencies (e.g., order of GHz) where it is difficult to measure currents and voltages.

*Figure* 2.1: A two-port network.

From the relationship between the S-parameters and chain-matrix parameters (A,B,C,D) [13,14], the transducer power gain can also be expressed as:

$$g_{T} = \frac{4R_{L}R_{S}}{\left|AZ_{L} + B + CZ_{S}Z_{L} + DZ_{S}\right|^{2}},$$

(2.2)

where  $R_S$  and  $R_L$  are the real parts of the source and load impedances, respectively, and *A*, *B*, *C* and *D* are the parameters of the chain matrix. This matrix is especially useful for characterization of a cascade connection of two-port networks (e.g., a receiver) by multiplying the individual *ABCD* matrices of the individual two-ports. In a similar manner, the impedance *Z*parameters and the admittance *Y*-parameters can be used to describe the relationship between total voltages and currents at network ports. Whereas analogue circuit designers are more familiar with voltages and currents (i.e., *Z-, Y-, ABCD*-parameters), microwave circuit designers prefer *S*-parameters.

The transducer power gain depends on both the source and the load impedances (i.e., mismatches  $\Gamma_s$  and  $\Gamma_L$ ). This gain parameter can be easily extracted from measurements (required impedance match with signal generator only). Moreover, a maximum operation frequency ( $f_{MAX}$ ) of a device can be directly estimated from the measured unilateral ( $S_{12}$ =0) transducer power gain.

In the case of matched input and output impedances for a two-port network, the *available* power gain  $(g_A)$  can be defined. It stands for the ratio of the power available from the two-port network and the power available from the source  $(P_{AVS})$ . The transducers power gain equals the available power gain when the input and output are power matched simultaneously.

Throughout the thesis we refer to the transducer power gain if only the input power match condition is satisfied. For a simultaneous input and output power match, we refer to the available power gain (that in this case only equals the transducers power gain).

If  $V_s$  is the signal voltage swing at the source and  $V_0$  is the output voltage swing (at the load; see Fig. 2.1), the relationship between the transducer power gain and the voltage gain (vg, from the source) can be determined:

$$vg^{2} = \frac{V_{0}^{2}}{V_{S}^{2}} = \frac{V_{0}^{2} / R_{L}}{V_{S}^{2} / 4R_{S}} \frac{R_{L}}{4R_{S}} = g_{T} \frac{R_{L}}{4R_{S}}, \qquad (2.3)$$

where the input power match, and real source and load impedances ( $R_S$  and  $R_L$ ) are assumed. When we consider the voltage gain from the input of the two-port network (i.e., not with respect to  $V_S$ ), voltage and power gain definitions are equal when expressed in decibels for  $R_L = R_S$ .

#### 2.1.1 STABILITY

Two types of stability are distinguished: unconditional and conditional stability [12,16-18]. If  $\Gamma_{IN}$  and  $\Gamma_{OUT}$  are less than one only for a range of source and load impedances, then the two-port network is conditionally stable, because impedances outside of this range may cause oscillations (i.e., the real part of either the input or output two-port impedance has a negative real part). If  $\Gamma_{IN}$  and  $\Gamma_{OUT}$  are always below one, the two-port is unconditionally stable.

The conditional stability criterion can be expressed as [4]:

$$\left|\Gamma_{IN}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1$$

(2.4)

$$\left|\Gamma_{OUT}\right| = \left|S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S}\right| < 1.$$

(2.5)

A device is unconditionally stable if *Rollet's* condition [19] (Eq. (2.6)) is satisfied.

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |\Delta|^2}{2|S_{21}S_{12}|} > 1 \qquad \Delta = S_{11}S_{22} - S_{12}S_{21} < 1.$$

(2.6)

As this condition involves constraints on two different parameters, it is difficult to compare the stability of different devices. However, the  $\mu$  test [20,21] for the unconditional stability can be used for both testing and comparison, and is given by Eq. (2.7).

$$\mu = \frac{1 - |S_{11}|^2}{|S_{22} - S_{11}^* \Delta| + |S_{12} S_{21}|} > 1.$$

(2.7)

This condition reads as: the larger the  $\mu$ , the better the stability. Generally, figures expressed with *S*-parameters can be conveniently mapped and followed using Smith charts [10].

If there is feedback in a circuit, the stability criteria can be related to loop gain and loop phase shift [15].

#### 2.1.2 MATCHED GAIN PARAMETERS

Referring to Eq. (2.1), we can distinguish between the gain factors of the source matching network  $g_S$ , Eq. (2.8), of the designed two-port network (Fig. 2.1)  $g_0$ , Eq. (2.9), and of the load matching network  $g_L$ , Eq. (2.10) [11,12].

$$g_{S} = \frac{1 - |\Gamma_{S}|^{2}}{\left|1 - \Gamma_{IN}\Gamma_{S}\right|^{2}}$$

(2.8)

$$g_0 = \left| S_{21} \right|^2 \tag{2.9}$$

$$g_L = \frac{1 - |\Gamma_L|^2}{\left|1 - S_{22}\Gamma_L\right|^2}.$$

(2.10)

For the maximum power transfer, the input impedance of the two-port network must be conjugate matched to the impedance of the source-matching network, and the output impedance of the two-port network must be conjugate matched to the impedance of the load-matching network [12]. This condition is satisfied if:

$$\Gamma_{IN} = \Gamma_S^* \qquad \Gamma_{OUT} = \Gamma_L^* \,. \tag{2.11}$$

Input and output power match design practice is common to circuits of a heterodyne receiver. If the matching conditions are violated at either the input or the output of an external (usually 50 $\Omega$  terminated) image-reject or channel-select filter, the passband and stopband characteristics of the filter will exhibit loss and ripples [2].

However, for an ideal voltage or current amplification, different requirements result, as shown in Table 2.1. For example, infinite impedance at the input of the two-port is expected for the maximum voltage gain ( $\Gamma_{IN}$ =1), whereas zero impedance enables the maximum current gain ( $\Gamma_{IN}$ =-1). This design practice is common to circuits where power matching is not required (e.g., homodyne receiver circuits).

*Table* 2.1: Reflection coefficients for ideal current ( $Z_{IN}=0$ ) and voltage ( $Z_{IN}-\infty$ ) quantities;  $Z_{IN}$  is the input impedance of a two-port network.

| input voltage                                | input current              |  |

|----------------------------------------------|----------------------------|--|

| $Z_{IN} \rightarrow \infty, \Gamma_{IN} = 1$ | $Z_{IN}=0, \Gamma_{IN}=-1$ |  |

## 2.2 NONLINEARITY PARAMETERS

As a minimal detectable signal at the input of wireless receivers can be an order of microvolt large, it must be heavily amplified (without distortion) for further processing.

If a system is linear and memoryless, then its output can be presented as:

$$y(t) = ax(t), \qquad (2.12)$$

where x(t) is an input signal and y(t) is the output signal.

For memoryless nonlinear systems, the input-output relationship has the form

$$y(t) = a_0 + a_1 x(t) + a_2 x(t)^2 + \dots$$

(2.13)

The parameters  $a_i$  are time dependent for time-varying systems.

Whereas a linear model can approximate an RF circuit for small input signals (e.g., -100dBm), for large input signals (e.g., -10dBm) or for heavily amplified signals, an RF circuit is characterized by a nonlinear model.

By inspecting the response to a sinusoidal excitation  $(x(t)=A\cos\omega t)$  using the nonlinear model (Eq. (2.13)), we can describe numerous nonlinearity phenomena (from Eq. (2.14)).

$$y(t) = \frac{a_2 A^2}{2} + (a_1 A + \frac{3}{4} a_3 A^3) \cos \omega t + \frac{a_2 A^2}{2} \cos 2\omega t + \frac{1}{4} a_3 A^3 \cos 3\omega t + \dots$$

(2.14)

In the remainder of this section we will comment on gain compression, desensitization, cross modulation and intermodulation [22-39].

In a symmetric system (odd-order terms eliminated) dominated by the  $3^{rd}$ -order term [22,23] (i.e., higher-order terms neglected as they are small compared to lower-order terms), from Eq. (2.14), the gain g of the nonlinearly modeled system is:

$$g = a_1 + \frac{3}{4}a_3A^2 \,. \tag{2.15}$$

If  $a_3 < 0$ , the gain is a decreasing function of amplitude A. The 1-dB *compression point* quantifies this gain reduction effect [2]. It is defined as the input signal level at which the gain g is reduced by 1dB compared to the

linear gain term  $(a_1)$ . From Eq. (2.15), this point is:

$$A_{\rm 1dB} = \sqrt{0.145 \left| \frac{a_1}{a_3} \right|} \,. \tag{2.16}$$

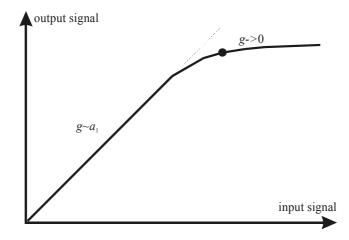

Note that the signal at the output of an analogue circuit is a result of the combination of the factors: nonlinear model (2.13) as well as bias conditions. Therefore, for very large input signals, the gain can even become zero, because either the output signal is limited by the bias supply quantity (see Fig. 2.2), or  $a_3 < 0$  (see Eq. (2.15)).

*Figure* 2.2: A relationship between the input and output signal amplitudes under the constraint of bias (supply) conditions in a nonlinear system.

In the presence of a strong interferer, the desired signal may experience a very small gain. If the signal applied at the input of a nonlinear system has the form (a desired signal at an angular frequency  $\omega_1$  and an interferer at  $\omega_2$ ):

$$x(t) = A_1 \cos \omega_1 t + A_2 \cos \omega_2 t , \qquad (2.17)$$

the gain of the desired signal can be calculated after combining Eqs. (2.13) and (2.17). The term representing the content of the output signal around the angular frequency  $\omega_1$  becomes:

$$y(t) \cong (a_1 + \frac{3}{2}a_3 A_2^2) A_1 \cos \omega_1 t$$

(2.18)

For sufficiently large  $A_2$ , the gain term may also drop to zero. This effect is referred to as *blocking* [2]. The interferer leading to this effect is called the blocking signal.

If the amplitude of a strong interferer is modulated and applied to the input of a nonlinear system along with a desired signal, then at the output the desired signal experiences the effect of a modulated interferer. This phenomenon is called *cross modulation* [2,24,25].

#### 2.2.1 INTERMODULATION

When signals of different frequencies are applied to the input of a nonlinear system, not only does the output exhibit components that are harmonics of the input signals, but also of their combinations. This phenomenon is referred to as *intermodulation* [2,26,27]. If the input signal is given by Eq. (2.17), the following terms are generated at the output of the system (2.13):

desired component:

$$(a_1 + \frac{3}{4}a_3A_1^2 + \frac{3}{2}a_3A_2^2)A_1\cos\omega_1 t$$

(2.19)

2<sup>nd</sup>-order distortion component:  $a_2 A_1 A_2 \cos(\omega_1 - \omega_2) t$  (2.20)

3<sup>rd</sup>-order distortion component:

$$\frac{3}{4}a_3A_1^2A_2\cos(2\omega_1-\omega_2)t$$

(2.21)

These are the fundamental component, Eq. (2.19), the second-order intermodulation component, Eq. (2.20), and the third-order intermodulation component, Eq. (2.21).

Due to mismatches in real designs, the distortion that originates from the second-order nonlinearities must be taken into account, even in differential circuits (even components fractional matching below 1% can be critical [28]). Especially, circuits that transform a high-frequency input spectrum to the baseband would suffer from this type of the distortion (e.g., homodyne receivers). This phenomenon is referred to as *second-order intermodulation distortion* [29].

As third-order intermodulation products are located near the desired signal, it is often difficult to filter them out without affecting the information content. It is therefore expected that such in-band products will distort the output signal. The associated phenomenon is referred to as *third-order intermodulation distortion* [2,26,27].

Second- and third-order intercept points characterize the introduced intermodulation distortion phenomena. They are derived in the remainder of this section.

### 2.2.1.1 Third-Order Intercept Point

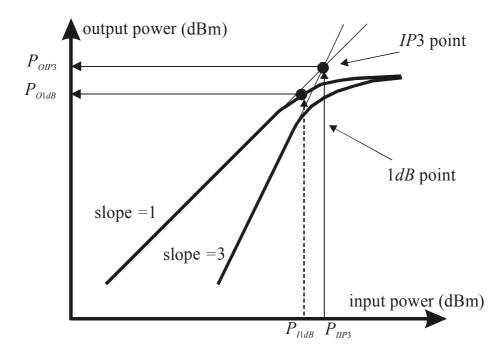

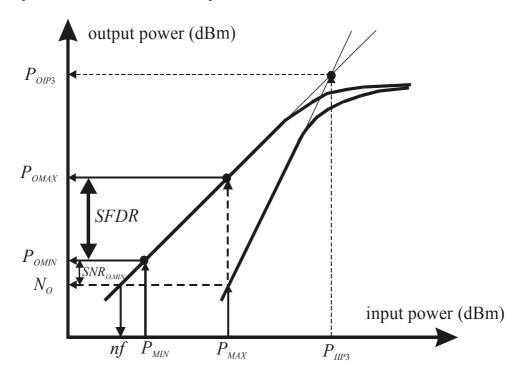

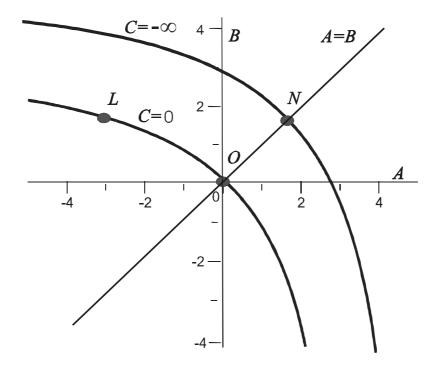

Referring to Eqs. (2.19) and (2.21), and assuming  $A_1=A_2=A$ , it can be seen that the output power of the third-order products increases with the cube of the input power, whereas the fundamental output power is proportional to the input power [23]. This effect is shown in Fig. 2.3.

A hypothetical intersection point where the first-order power product ( $P_o$ ) and the third-order power product ( $P_{OIM3}$ ) are equal is called *third-order intercept point* (IP3). Table 2.2 describes the notation that is used throughout this thesis.

Figure 2.3: Input-output power relationship of a nonlinear device.

If the corresponding power definitions are given by Eq. (2.22),

$$P_O = \frac{1}{2}a_1^2 A^2 \qquad P_{OIM3} = \frac{1}{2}(\frac{3}{4}a_3 A^2 A)^2 = \frac{9}{32}a_3^2 A^6, \qquad (2.22)$$

the amplitude of the input-referred  $3^{rd}$ -order intercept point ( $A_{IIP3}$ ) becomes

$$A_{IIP3} = \sqrt{\frac{4a_1}{3a_3}} \,. \tag{2.23}$$

Once the parameters  $a_0, a_1, \ldots$  of the corresponding circuit are determined, the intercept point can be calculated. What is more, the effects of distortion can be fully encompassed only by analysis at the circuit level, after all circuit nonlinearity contributors are taken into account [30-37]. For example,  $A_{IIP3}$  for a single bipolar transistor, as derived from Eq. (2.23) using the simplified exponential characteristic [38], is  $A_{IIP3} = \sqrt{8}V_T$  ( $V_T$  is the thermal voltage).

Table 2.2: Amplitude-power-dB scale notation.

| parameter\presentation                              | amplitude  | power      | dB scale      |

|-----------------------------------------------------|------------|------------|---------------|

| 3 <sup>rd</sup> -order input-intercept point        | $A_{IIP3}$ | $P_{IIP3}$ | IIP3          |

| 3 <sup>rd</sup> -order output-intercept point       | $A_{OIP3}$ | $P_{OIP3}$ | OIP3          |

| 3 <sup>rd</sup> -order input-intermodulation point  | $A_{IIM3}$ | $P_{IIM3}$ | IIM3          |

| 3 <sup>rd</sup> -order output-intermodulation point | $A_{OIM3}$ | $P_{OIM3}$ | OIM3          |

| input desired signal                                | A          | Р          | <i>P</i> [dB] |

| output desired signal                               | $A_O$      | $P_O$      | $P_O$ [dB]    |

The equivalent IIP3 of, most generally, an n-stage cascaded network equals [2,39,40]

$$\frac{1}{A_{IIP3}^{2}} = \frac{1}{A_{IIP3,1}^{2}} + \frac{a_{1}^{2}}{A_{IIP3,2}^{2}} + \frac{a_{1}^{2}b_{1}^{2}}{A_{IIP3,3}^{2}} + \dots, \qquad (2.24)$$

where  $A_{IIP3,1}$ ,  $A_{IIP3,2}$ , ... are the third-order input-intercept amplitudes and  $a_1$ ,  $b_1$ , ... are the linear gain coefficients of the corresponding blocks in a receive chain (similar to Eq. (2.13)).

An important conclusion that can be derived from the above result is the inverse proportionality of the first-stage linear gain  $a_1$  and the overall IIP3. Namely, a larger gain of the first stage results in a larger intermodulation product that is responsible for an even larger distortion at the output of the second stage.

Note that IIP3 cannot be obtained directly from measurements, but as an intersection between the extrapolated linear and third-order intermodulation responses (Fig. 2.3), which are, however, obtained for small input signals. The reason for this is that IIP3 is often far beyond the maximal signal range of the system.

#### 2.2.1.2 Second-Order Intercept Point

A hypothetical intersection point of the first-order product  $(a_1A)$  and the second order product  $(a_2A^2)$  is *second-order intercept point* (IP2) [29]. The amplitude of the input-referred IP2 is defined as:

$$A_{IIP2} = \frac{a_1}{a_2}$$

(2.25)

Similar to the derivation of the cascaded IIP3, the cascaded IIP2 can be expressed as:

$$\frac{1}{A_{IIP2}} = \frac{1}{A_{IIP2,1}} + \frac{a_1}{A_{IIP2,2}} + \frac{a_1b_1}{A_{IIP2,3}} + \dots, \qquad (2.26)$$

where  $A_{IIP2,i}$  are the input-referred second-order intercept amplitudes of the corresponding cascaded stages.

### **2.3 NOISE FIGURE**

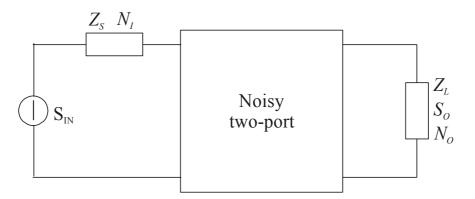

The reduction in signal-to-noise ratio (SNR) throughout a two-port network is characterized by the *noise factor* [41].

$$F = \frac{SNR_I}{SNR_O} = \frac{S_I / N_I}{S_O / N_O}$$

(2.27)

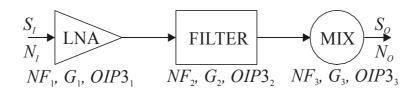

Here,  $SNR_I$  and  $SNR_O$  are the input and output signal-to-noise ratios, respectively.  $S_I$  and  $N_I$  are the input signal power and the input noise power, and  $S_O$  and  $N_O$  are the output signal and noise power (see Fig. 2.4). When expressed in decibels (dB), this ratio is called the *noise figure*.

The general expression for noise factor is given below [42-47],

$$F = F_{MIN} + \frac{R_N}{G_S} \Big[ (G_S - G_{OPT})^2 + (B_S - B_{OPT})^2 \Big], \qquad (2.28)$$

where  $F_{MIN}$  is the minimum noise factor,  $R_N$  the equivalent noise resistance,  $G_S$  and  $B_S$  the source conductance and susceptance, and  $G_{OPT}$  and  $B_{OPT}$  the optimum source admittance parameters corresponding to the minimum noise factor. The source admittances that minimize noise factor and maximize power transfer (impedance match) of a two-port network are usually not the same. Therefore, orthogonal optimization for noise figure and power transfer is required if one wants to enjoy simultaneous noise and power match (if possible). Whereas  $F_{MIN}$  stands for the noise factor achieved under noise matched conditions, noise resistance  $R_N$  characterizes the sensitivity of the minimum noise figure to changes in the source impedance.

*Figure* 2.4: A noisy two-port network.

On the other hand, microwave designers are more familiar with the noisefactor definition that is related to reflection coefficients of a two-port network, Eq. (2.29) [4],

$$F = F_{MIN} + 4 \frac{R_N}{Z_0} \frac{\left|\Gamma_S - \Gamma_{OPT}\right|^2}{(1 - \left|\Gamma_S\right|^2)\left|1 + \Gamma_{OPT}\right|^2},$$

(2.29)

where  $\Gamma_{OPT}$  is the optimum reflection coefficient corresponding to the optimum source admittance that provides the minimum noise factor, and  $\Gamma_S$  is the source reflection coefficient.

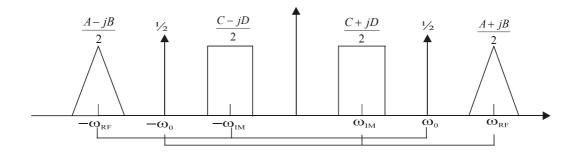

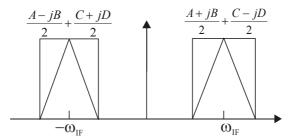

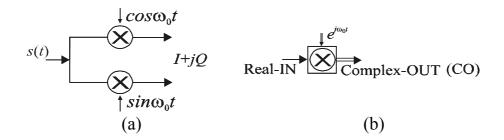

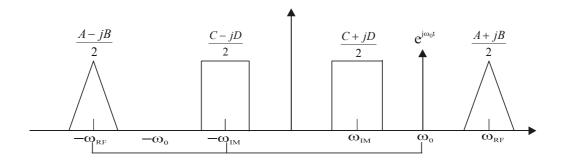

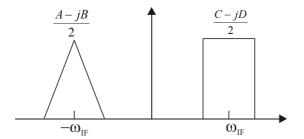

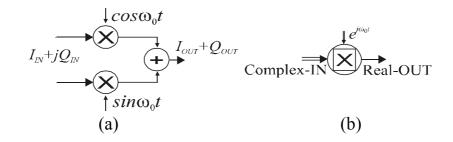

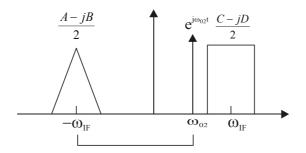

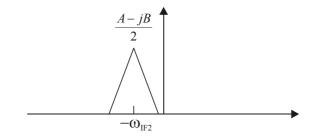

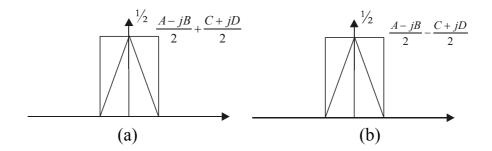

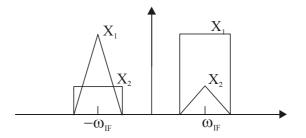

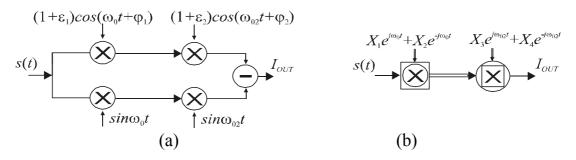

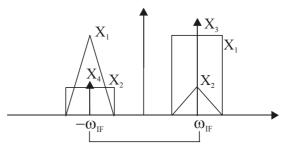

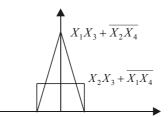

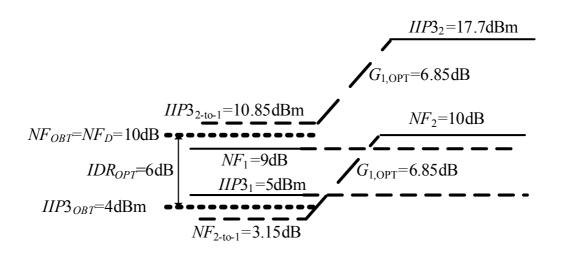

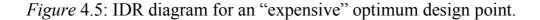

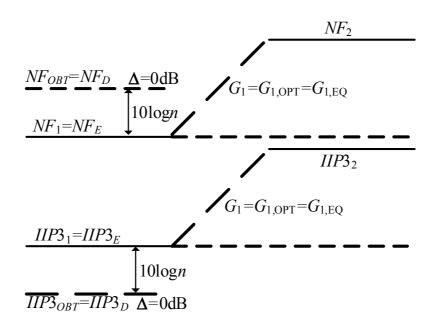

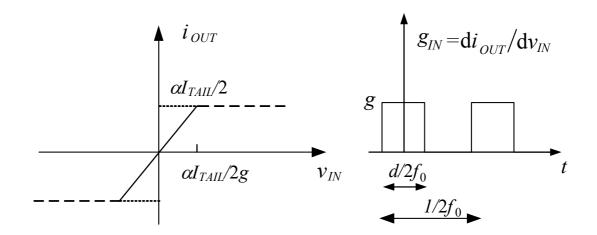

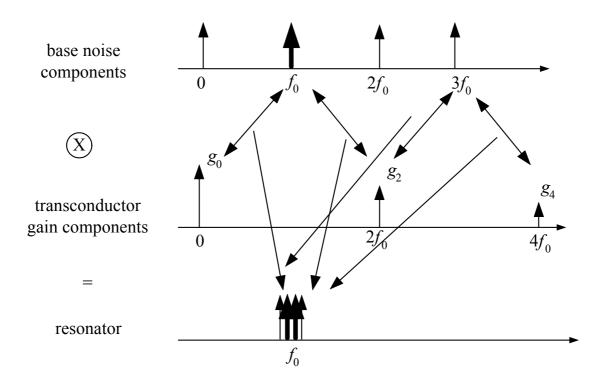

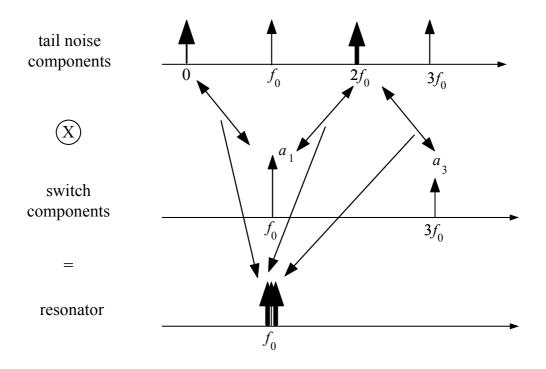

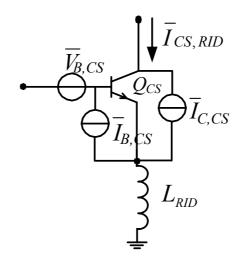

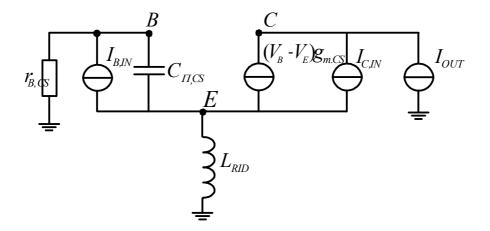

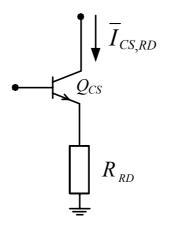

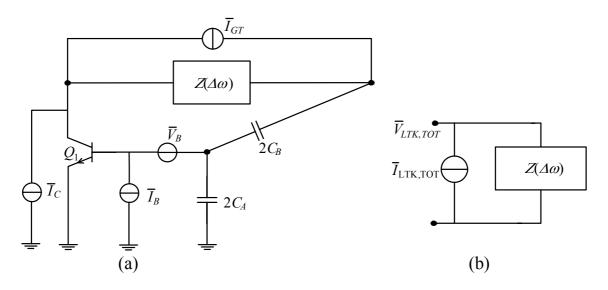

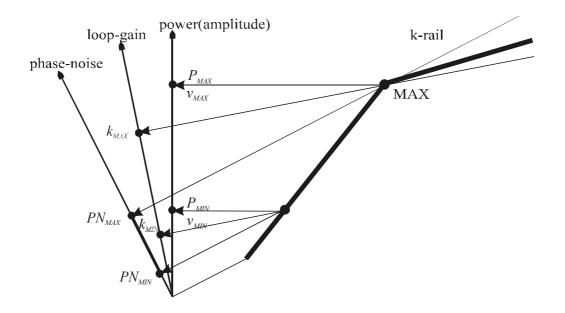

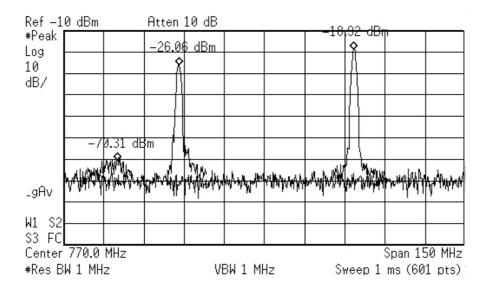

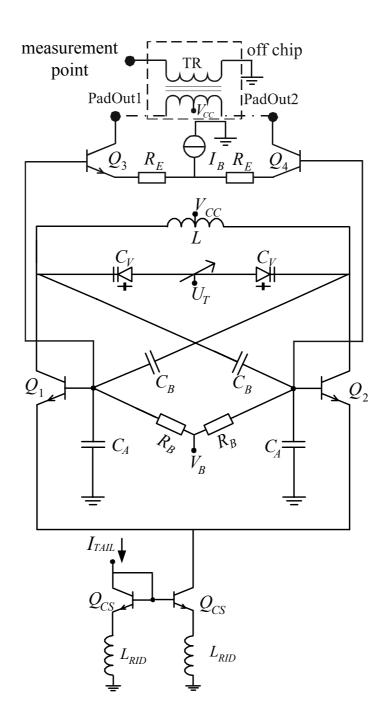

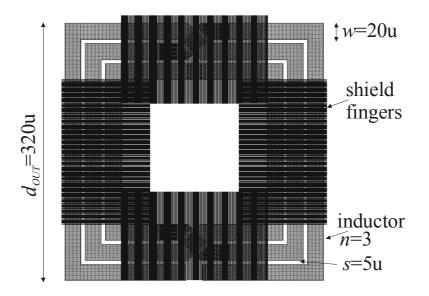

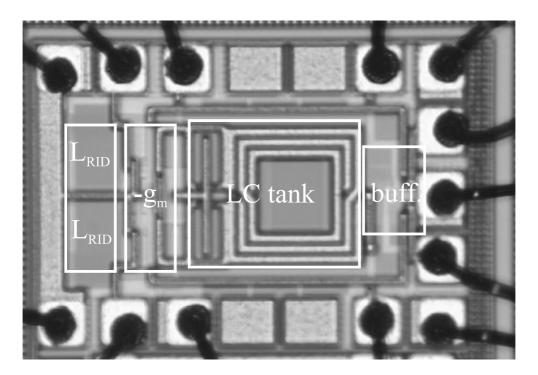

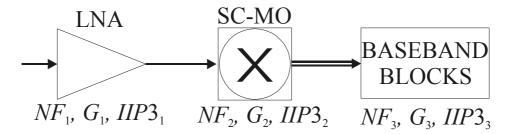

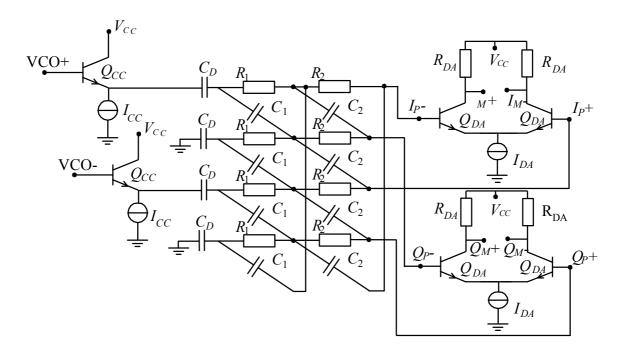

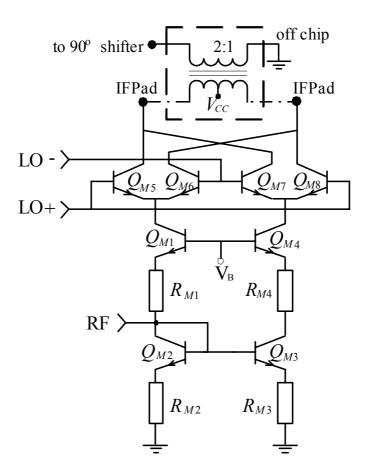

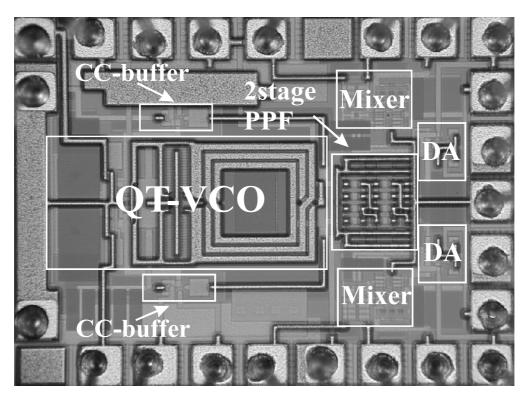

The noise parameters,  $F_{MIN}$ ,  $R_N$ , and  $\Gamma_{OPT}$ , are characteristics of the device,