**Delft University of Technology**

## Design of a High Voltage Arbitrary Wave Shape Generator for Dielectric Testing

Ganeshpure, D.A.

DOI 10.4233/uuid:0a34b7ef-d18b-4f86-be16-62128a52dd7c

Publication date 2024

**Document Version** Final published version

#### Citation (APA)

Ganeshpure, D. A. (2024). Design of a High Voltage Arbitrary Wave Shape Generator for Dielectric Testing. [Dissertation (TU Delft), Delft University of Technology]. https://doi.org/10.4233/uuid:0a34b7ef-d18b-4f86be16-62128a52dd7c

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

#### Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

This work is downloaded from Delft University of Technology. For technical reasons the number of authors shown on this cover page is limited to a maximum of 10.

## **Design of a High Voltage Arbitrary Wave Shape Generator for Dielectric Testing**

\_ I

\_ I

## **DESIGN OF A HIGH VOLTAGE ARBITRARY WAVE SHAPE GENERATOR FOR DIELECTRIC TESTING**

## Dissertation

for the purpose of obtaining the degree of doctor at Delft University of Technology by the authority of the Rector Magnificus Prof.dr.ir. T.H.J.J. van der Hagen, chair of the Board for Doctorates to be defended publicly on Wednesday, 10 January 2024 at 15:00 o'clock

by

## **Dhanashree Ashok GANESHPURE**

Master of Science in Electrical Engineering, Delft University of Technology, The Netherlands. Born in Akola, India This Dissertation has been approved by the promotors.

\_ I

| Composition of the Doctoral Committee: |                                                |  |

|----------------------------------------|------------------------------------------------|--|

| Rector Magnificus                      | Chairperson                                    |  |

| Prof. ir. P.T.M. Vaessen               | Delft University of Technology, promotor       |  |

| Prof. dr. ir. P. Bauer                 | Delft University of Technology, promotor       |  |

| Dr. M. Ghaffarian Niasar               | Delft University of Technology, copromotor     |  |

|                                        |                                                |  |

| Independent members:                   |                                                |  |

| Prof. dr. ir. M. Popov                 | Delft University of Technology                 |  |

| Prof. dr. ir. G. Rietveld              | University of Twente                           |  |

| Prof. dr. G. Burt                      | University of Strathclyde, UK                  |  |

| Dr. C.A. Plet                          | DNV, Canada                                    |  |

| Prof. dr. ir. A.H.M. Smets             | Delft University of Technology, reserve member |  |

|                                        |                                                |  |

This research work is sponsored by KEMA Laboratories, Arnhem, The Netherlands.

Printed by:

\_ I

Copyright © 2024 by D. Ganeshpure

ISBN 000-00-0000-000-0

An electronic version of this dissertation is available at http://repository.tudelft.nl/.

माझ्यावर निरपेक्ष प्रेम करण्यारा आणि मला सदैव पाठिंबा देणाऱ्या, माझ्या प्रिय आई आणि बाबांना हा प्रबंध समर्पित!! Ι\_\_

\_ I

\_ I

# **CONTENTS**

۱\_\_

| Li | stof                      | Abbreviations                                                                                                                                                                                                                                                                          | xi                                                                                         |

|----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Li | st of S                   | Symbols                                                                                                                                                                                                                                                                                | xiii                                                                                       |

| Li | List of Figures xvi       |                                                                                                                                                                                                                                                                                        | xvii                                                                                       |

| Li | st of '                   | Tables                                                                                                                                                                                                                                                                                 | xxiii                                                                                      |

| Sı | ımma                      | ary                                                                                                                                                                                                                                                                                    | xxv                                                                                        |

| Sa | ımen                      | vatting                                                                                                                                                                                                                                                                                | xxvii                                                                                      |

| 1  | <b>Intr</b><br>1.1<br>1.2 | oduction         Motivation         Scope, Objective and Research Questions                                                                                                                                                                                                            |                                                                                            |

|    | 1.3<br>1.4                | Contributions                                                                                                                                                                                                                                                                          |                                                                                            |

| 2  | 2.1                       | Test Requirements         Introduction                                                                                                                                                                                                                                                 | 8<br>8<br>10<br>10<br>11<br>11<br>11<br>13<br>13<br>13<br>14<br>16<br>16<br>16<br>17<br>18 |

| 3  |                           | mising HV AWG solution and its design trade-offs         Comparison of Promising Solutions.         Schematic of MMC as HV AWG         Design Trade-offs in the Chosen Solution         3.3.1         Modulation Techniques         3.3.2         Arm Inductance and Series Resistance | <b>21</b><br>21<br>24<br>26<br>26                                                          |

|   |      | 3.3.3 Number of Submodules and Switches                          | 31  |

|---|------|------------------------------------------------------------------|-----|

|   |      | 3.3.4 Submodule Capacitance and its Voltage Balancing            | 32  |

|   | 2.4  | 3.3.5 Control System.                                            | 34  |

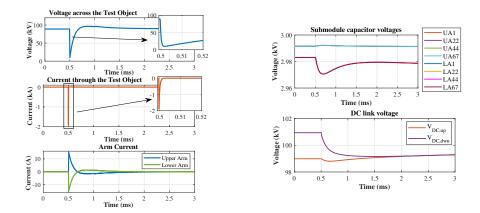

|   | 3.4  | Analytical, Simulation and Hardware Results                      | 36  |

|   | 3.5  | Results of Full-scale Prototype                                  | 43  |

|   | 3.6  | Conclusions for Promising HV AWG Solutions and Design Trade-offs | 47  |

| 4 |      | trol Aspects of HV AWG                                           | 49  |

|   | 4.1  | Active Damping Control Methodology                               | 50  |

|   |      | 4.1.1 Control System in Time Domain                              | 50  |

|   |      | 4.1.2 Discretization of the Closed Loop                          | 53  |

|   |      | 4.1.3 Stability Analysis of the Proposed Control System          | 53  |

|   |      | 4.1.4 Simulation Results of the Proposed Control System          | 55  |

|   | 4.2  | Control Hardware.                                                | 59  |

|   |      | 4.2.1 Real Time Simulator as a Controller                        | 59  |

|   |      | 4.2.2 Typhoon-HIL as a Controller.                               | 60  |

|   | 4.0  | 4.2.3 Experimental Setup and Results                             | 61  |

|   | 4.3  | Conclusions for Control Aspects of the HV AWG                    | 65  |

| 5 | Stee | ep Pulse Generation                                              | 67  |

|   | 5.1  | Introduction                                                     | 68  |

|   |      | Challenges Generating Steep Pulses from MMC.                     | 68  |

|   | 5.3  | Pulse Current Capability                                         | 69  |

|   |      | 5.3.1 Theoretical Background and Adopted Methodology             | 70  |

|   |      | 5.3.2 Experimental Setup and Results                             | 72  |

|   |      | 5.3.3 Discussion of Experimental Results                         | 76  |

|   |      | Motivation for the Hybrid Circuit                                | 77  |

|   | 5.5  | Schematic of the Proposed Hybrid Circuit                         | 78  |

|   |      | 5.5.1 Design Guidelines                                          | 80  |

|   |      | 5.5.2 Simulation and Experimental Results                        | 88  |

|   | 5.0  | 5.5.3 HV Simulation Results                                      | 91  |

|   | 5.6  | Conclusions for Steep Pulse Generation.                          | 95  |

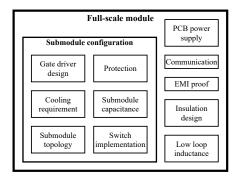

| 6 |      | dware Design of HV AWG                                           | 97  |

|   |      | Introduction to Hardware Design                                  |     |

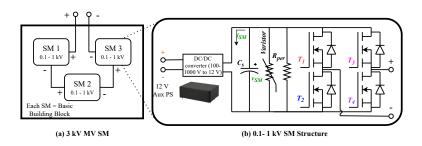

|   | 6.2  | MV SM Design Details                                             | 98  |

|   |      | 6.2.1 Switches                                                   |     |

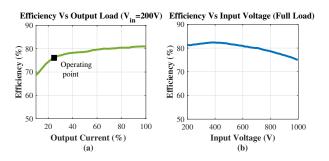

|   |      | 6.2.2 Auxiliary Power Supply.                                    |     |

|   |      | 6.2.3 Structure of MV Submodule                                  |     |

|   | 6.3  | Hardware and Control Challenges                                  |     |

|   |      | 6.3.1 Hardware Non-idealities                                    |     |

|   |      | 6.3.2 Start-up Procedure.                                        |     |

|   |      | 6.3.3 SM Capacitance Choice                                      |     |

|   |      | 6.3.4 Protection Design                                          |     |

|   | 6.4  | Hardware Setup and Results                                       |     |

|   | 6.5  | Conclusions for Hardware Design of the HV AWG                    | 117 |

\_ |

- I

| 7  | Futa<br>7.1<br>7.2<br>7.3<br>7.4 | ure Outlook of the HV AWG         Introduction         Design Flow for MMC Hardware and Control         Tests for Final Verification         Conclusions for Future outlook of the HV AWG | 120<br>123                      |

|----|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 8  | 8.1                              | Iclusions and Future Recommendations         Conclusions.         Future Recommendations                                                                                                  |                                 |

| A  | Sun                              | nmary of HV Test Requirement                                                                                                                                                              | 133                             |

| B  | B.1<br>B.2                       | <ul> <li>Experimental Setup</li></ul>                                                                                                                                                     | 146<br>146<br>146<br>146<br>148 |

|    | B.3<br>B.4                       | Discussion of Results                                                                                                                                                                     |                                 |

| Bi |                                  |                                                                                                                                                                                           | 150                             |

| Li | st of ]                          | Publications                                                                                                                                                                              | 163                             |

| Ac | knov                             | wledgements                                                                                                                                                                               | 165                             |

| Bi | ograj                            | phy                                                                                                                                                                                       | 171                             |

ix

|\_\_\_

\_ I

\_ I

## **LIST OF ABBREVIATIONS**

۱\_\_

| APS  | Auxiliary Power Supply                            |

|------|---------------------------------------------------|

| APOD | Alternate Phase Opposition Disposition            |

| AWG  | Arbitrary Wave shape Generator                    |

| CHB  | Cascaded H Bridge                                 |

| DAC  | Damped Alternating Current                        |

| DSP  | Digital Signal Processor                          |

| DUT  | Device Under Test                                 |

| EMC  | Electromagnetic Compatibility                     |

| EU   | European Union                                    |

| ESP  | Electrical Sustainable Power                      |

| FPGA | Field Programmable Gate Array                     |

| FRT  | Fault Ride Through                                |

| HV   | High Voltage                                      |

| HVDC | High Voltage Direct Current                       |

| IEC  | International Electrotechnical Commission         |

| IEEE | Institute of Electrical and Electronics Engineers |

| IGBT | Insulated Gate Bipolar Transistor                 |

| KVL  | Kirchhoff's Voltage Law                           |

| LCC  | Line Commutated Converters                        |

| LI   | Lightning Impulse                                 |

| LPIT | Low Power Instrument Transformer                  |

| LSC  | Level Shift Control                               |

| LV   | Low Voltage                                       |

| MMC  | Modular Multilevel Converter                      |

| MV   | Medium Voltage                                    |

| NLC  | Nearest Level Control                             |

| NPT  | Non Punch Through                                 |

| NPC        | Neutral Point Clamp                                               |

|------------|-------------------------------------------------------------------|

| PD         | Partial Discharge                                                 |

| PE         | Power Electronics                                                 |

| POD        | Phase Opposition Disposition                                      |

| PCB        | Print Circuit Board                                               |

| PCIe       | Peripheral Component Interconnect Express                         |

| PSC        | Phase Shift Control                                               |

| PT (Chp 2) | Potential Transformer                                             |

| PT (Chp 5) | Punch Through                                                     |

| PWM        | Pulse Width Modulation                                            |

| RES        | Renewable Energy Sources                                          |

| SHE        | Selective Harmonic Elimination                                    |

| SI         | Switching Impulse                                                 |

| SIC MOSFET | Silicon Carbide Metal Oxide Semiconductor Field-Effect Transistor |

| SM         | Submodule                                                         |

| SPC        | Standard Processing Cores                                         |

| SST        | Solid State Transformer                                           |

| SVM        | Space Vector Modulation                                           |

| THD        | Total Harmonic Distortion                                         |

| ТО         | Test Object                                                       |

| TOV        | Transient Over Voltages                                           |

| VLF        | Very Low Frequency                                                |

\_ |

- <sub>1</sub>

# LIST OF SYMBOLS

۱\_\_

| η                  | Voltage efficiency of the Marx generator                                       |

|--------------------|--------------------------------------------------------------------------------|

| $\eta_{APS}$       | Power efficiency of the APS                                                    |

| α_1                | Time constant which decides the tail time of the LI waveform                   |

| α_2                | Time constant which decides the front time of the LI waveform                  |

| a                  | Slope of the the average modulation index $(n_{u,l})$ during the soft start-up |

| C1                 | Equivalent input capacitance for Marx generator                                |

| $C_2$              | Equivalent output capacitance for Marx generator                               |

| C <sub>b</sub>     | Coupling capacitor                                                             |

| C <sub>cable</sub> | Capacitance of MV Cable                                                        |

| C <sub>CB(a)</sub> | Capacitance of MV circuit breaker: between contacts                            |

| C <sub>CB(b)</sub> | Capacitance of MV circuit breaker: between contact and Tank                    |

| C <sub>CT</sub>    | Capacitance of MV current transformer                                          |

| C <sub>DC</sub>    | DC-link capacitance                                                            |

| C <sub>eqv</sub>   | Equivalent capacitance in the circulating current circuit                      |

| C <sub>HG</sub>    | Capacitance of MV distribution transformer: between HV winding and ground      |

| C <sub>HL</sub>    | Capacitance of MV distribution transformer: between HV and LV winding          |

| Cload              | Load capacitance                                                               |

| C <sub>LG</sub>    | Capacitance of MV distribution transformer: between LV winding and ground      |

| C <sub>PT</sub>    | Capacitance of MV potential transformer                                        |

| Cs                 | Submodule capacitance                                                          |

| C <sub>se</sub>    | Additional input capacitance                                                   |

| C <sub>TO</sub>    | Capacitance of test object (general)                                           |

| C <sub>turn</sub>  | Capacitance of MV distribution transformer: between turns                      |

| d                  | Decimal part of the average modulation index $(n_{u,l})$                       |

| Fs                 | Switching frequency of the semiconductor devices                               |

| $f_{1\%error}$     | Large-signal bandwidth                                                         |

| f <sub>3dB</sub>   | Small-signal bandwidth                                                         |

| f <sub>suppres</sub>           | Suppressing frequency formed by the filter                                                                         |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------|

| $G_b(s)$                       | Band pass filter transfer function                                                                                 |

| G <sub>k</sub> (s)             | Controller transfer function                                                                                       |

| $G_p(s)$                       | Plant transfer function                                                                                            |

| i <sub>c</sub>                 | Circulating current                                                                                                |

| Ic                             | Average circulating current                                                                                        |

| i <sub>ch</sub>                | Charging current                                                                                                   |

| I <sub>ch</sub>                | Average Charging current                                                                                           |

| i <sub>i</sub>                 | Impulse current                                                                                                    |

| i <sub>u,l</sub>               | Upper and Lower arm current                                                                                        |

| is                             | Output current                                                                                                     |

| Is                             | Average output current                                                                                             |

| i <sub>SM</sub>                | Current consumption of the APS                                                                                     |

| Kp                             | Proportional controller gain                                                                                       |

| K <sup>i</sup> <sub>pu,l</sub> | Proportional controller gain for the arm controller for the i <sup>th</sup> submodule from the upper and lower arm |

| K <sub>i</sub>                 | Integral controller gain                                                                                           |

| La                             | Arm inductance                                                                                                     |

| n                              | Integer part of the average modulation index $(n_{u,l})$                                                           |

| Ν                              | Number of submodules per arm                                                                                       |

| n <sub>u,l</sub>               | Average insertion indices for upper and lower arm                                                                  |

| n <sup>i</sup> <sub>u,l</sub>  | Insertion index of i <sup>th</sup> submodule from upper and lower arm                                              |

| m <sub>a</sub>                 | Modulation index                                                                                                   |

| P <sub>APS</sub>               | Power consumption of the APS                                                                                       |

| R <sub>a</sub>                 | Arm resistor                                                                                                       |

| R <sub>f</sub>                 | Front resistor                                                                                                     |

| R <sub>G</sub>                 | Gate resistor                                                                                                      |

| R <sub>h</sub>                 | Tail resistor                                                                                                      |

| R <sub>leakge</sub>            | Leakage resistor parallel to the test object                                                                       |

| R <sub>p</sub>                 | Protection resistor                                                                                                |

| R <sub>per</sub>               | Parallel resistor                                                                                                  |

| THD <sub>nonsin</sub>          | THD definition for non-sinusoidal waveforms                                                                        |

| T <sub>c</sub>                 | Charging time required for the soft start-up algorithm to work                                                     |

|                                |                                                                                                                    |

\_ |

- <sub>1</sub>

| v <sub>SM,initial</sub> | Initial SM capacitor voltage across the basic building block                                             |

|-------------------------|----------------------------------------------------------------------------------------------------------|

| v <sub>u</sub>          | Total voltage across the lower arm submodules                                                            |

| $V_{ref}^{*}$           | Reference voltage waveform                                                                               |

| v <sub>u,l</sub> avg    | Average total voltage across the upper and lower arm submodules                                          |

| $v_{u,l}^i$             | Voltage of i <sup>th</sup> submodule from upper and lower arm submodules                                 |

| W                       | Angular frequency of the reference waveform                                                              |

| w <sub>c</sub>          | Resonant frequency                                                                                       |

| T <sub>s1</sub>         | Time taken for all SMs to have APS + Delay before the soft start-up algorithm starts                     |

| T <sub>s2</sub>         | Time for stage 2 in the soft start-up algorithms for 3 SMs                                               |

| T <sub>s</sub>          | Simulation step of the real-time simulator                                                               |

| T <sub>sw</sub>         | Period of the chosen switching frequency                                                                 |

| va                      | Output voltage applied across the test object                                                            |

| Va                      | Average output voltage applied across the test object                                                    |

| v <sub>c</sub>          | Circulating voltage                                                                                      |

| V <sub>CE</sub>         | Collector to emitter voltage in IGBT                                                                     |

| V <sub>DC</sub>         | Total input DC-link voltage                                                                              |

| V <sub>DS</sub>         | Drain to source voltage in MOSFET                                                                        |

| $V_{GE}/V_{GS}$         | Gate to emitter/source voltage in IGBT / MOSFET                                                          |

| V <sub>h,ref</sub>      | Voltage magnitude of h <sup>th</sup> harmonic from reference waveform                                    |

| V <sub>h,out</sub>      | Voltage magnitude of h <sup>th</sup> harmonic from output waveform                                       |

| V <sub>1,out</sub>      | Voltage magnitude of fundamental harmonic from out waveform                                              |

| v <sub>i</sub> (t)      | Voltage expression of LI waveform                                                                        |

| V <sub>m</sub>          | Peak magnitude of the LI waveform                                                                        |

| vl                      | Total voltage across the lower arm submodules                                                            |

| Vs                      | Internal switching voltage of the MMC                                                                    |

| v <sub>SM</sub>         | SM capacitor voltage across the basic building block                                                     |

| $v^{i}_{SM,u,l} \\$     | SM capacitor voltage across the $\mathrm{i}^{\mathrm{th}}$ basic building block from upper and lower arm |

| V <sub>SM,avg</sub>     | Average SM capacitor voltage across the basic building block                                             |

| V <sub>SM,avg,t</sub>   | Average SM capacitor voltage across the basic building block at time t                                   |

|                         |                                                                                                          |

|\_\_\_

\_ I

\_ I

# **LIST OF FIGURES**

۱\_\_

| 1.1  | New electrical stresses occurring in the electrical power network.        | 2  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | PhD scope                                                                 | 4  |

| 1.3  | Thesis Outline.                                                           | 6  |

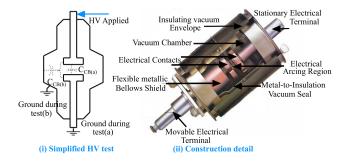

| 2.1  | MV vacuum circuit breaker [17].                                           | 9  |

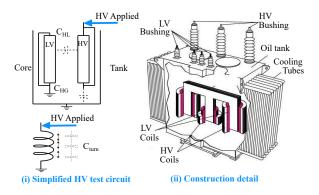

| 2.2  | MV Distribution Transformer [20]                                          | 9  |

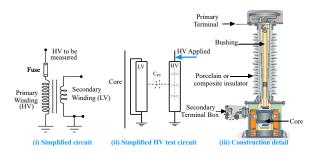

| 2.3  | Potential Transformer (PT) [27].                                          | 10 |

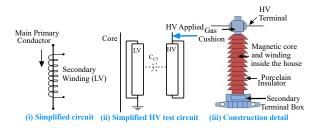

| 2.4  | Current Transformer (CT) [24]                                             | 10 |

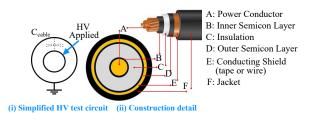

| 2.5  | MV AC Cable [29]                                                          | 11 |

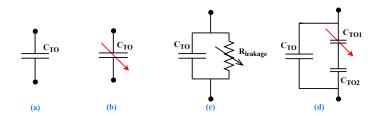

| 2.6  | Test Object Behaviour (a) Normal (b) During Breakdown (c) For Outdoor     |    |

|      | Equipment (d) For Partial Discharges within the HV insulation             | 11 |

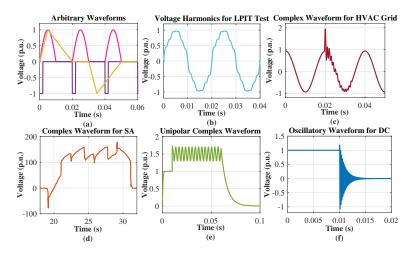

| 2.7  | Different impulse waveforms (a) Arbitrary waveforms for PD detection (b)  |    |

|      | Sinusoidal with voltage harmonics for LPIT test (c) Complex waveforms     |    |

|      | for HVAC Grid(d) Complex waveform for Surge Arrester (SA) (e) Unipolar    |    |

|      | complex waveform (f) DC oscillatory test waveform.                        | 13 |

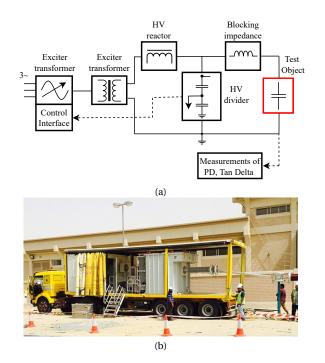

| 2.8  | (a) Resonant circuit (b) Commercial test device manufactured by HIGH      |    |

|      | VOLT for onsite testing [40].                                             | 14 |

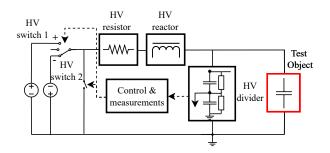

| 2.9  | VLF test circuit                                                          | 15 |

| 2.10 | (a) Test circuit for superimposed waveform generation [42] (b) Test setup |    |

|      | from Mannheim KEMA Lab [16]                                               | 15 |

| 2.11 | (a) Function Generator (b) Trek HV Amplifier [32].                        | 16 |

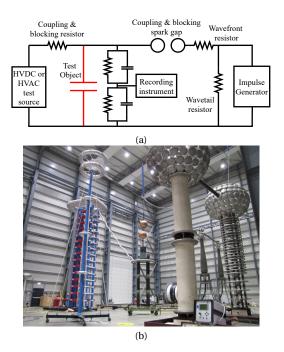

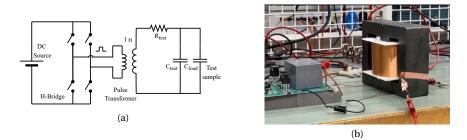

| 2.12 | H-Bridge and Pulse Transformer (a) Schematic (b) Experimental Setup [45]. | 17 |

|      | Limitations with the existing HV test source.                             | 18 |

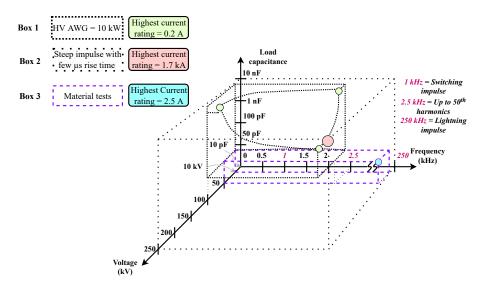

| 2.14 | Summary of HV test requirements for the power electronics-based HV AWG.   | 19 |

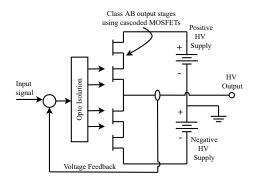

| 3.1  | Schematic of HV amplifier circuit [48].                                   | 22 |

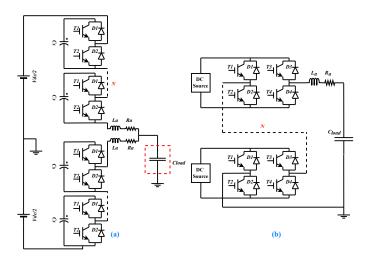

| 3.2  | Schematic of (a) MMC topology (b) CHB topology.                           | 23 |

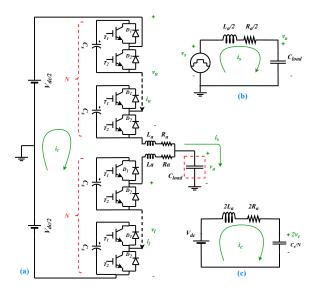

| 3.3  | (a) MMC Schematic for HV AWG application (b) Output current circuit (c)   |    |

|      | Circulating current circuit.                                              | 24 |

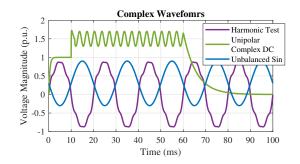

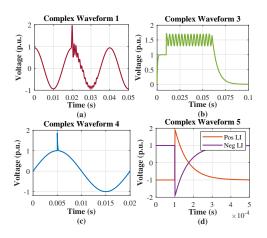

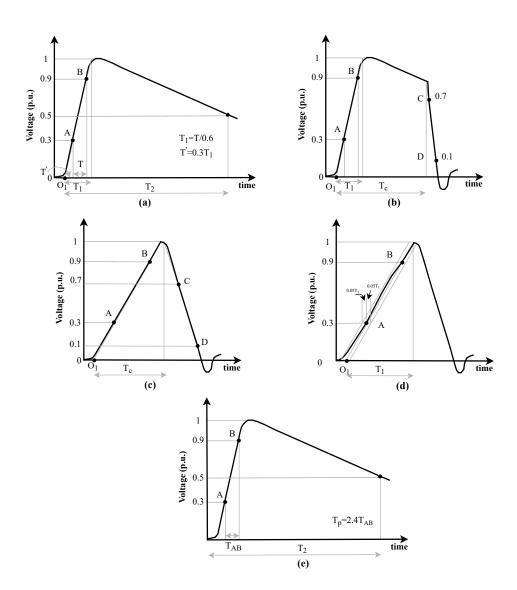

| 3.4  | Complex waveforms demonstrated in this Chapter                            | 26 |

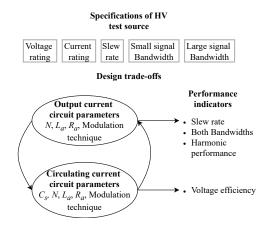

| 3.5  | Specifications and design trade-offs of MMC-based AWG.                    | 26 |

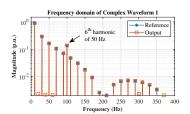

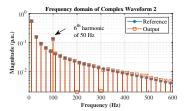

| 3.6  | Frequency spectrum of NLC modulated waveforms which were shown in         |    |

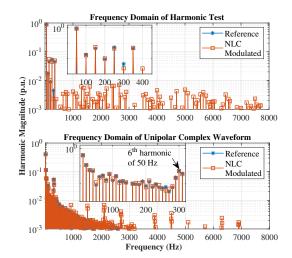

|      | Fig. 3.4                                                                  | 28 |

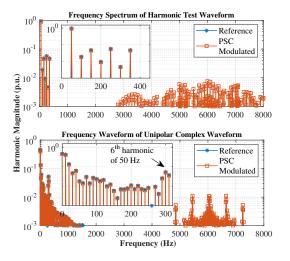

| 3.7  | Frequency spectrum of PSC modulated waveforms which were shown in         |    |

|      | Fig. 3.4                                                                  | 29 |

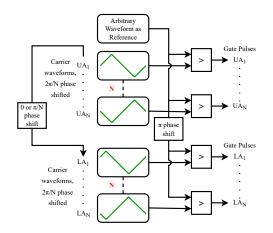

| 3.8  | Block diagram of the PSC modulation techniques.                           | 30 |

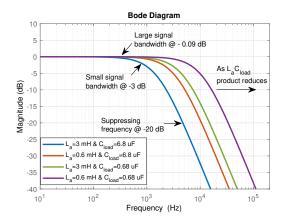

| 3.9  | Effect of $L_a$ and $C_{load}$ variation on the filter profile.           | 31 |

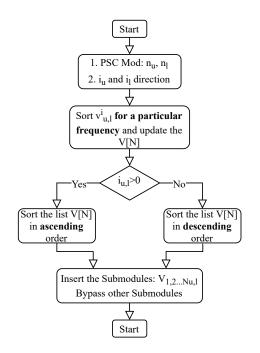

| 3.10 | Flowchart of the implemented sorting algorithm.                           | 35 |

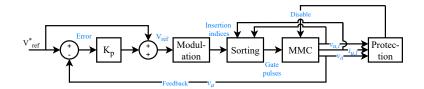

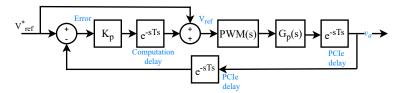

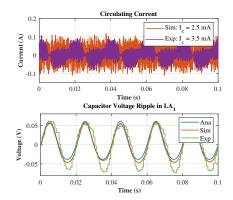

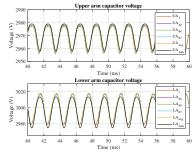

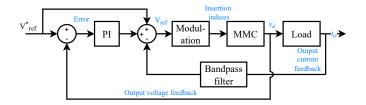

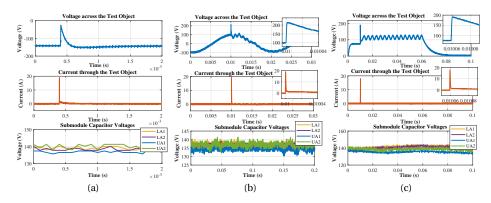

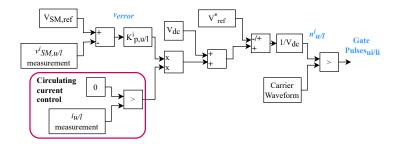

| 3.11 | Control system of the MMC-based AWG.                                                                                    | 35      |

|------|-------------------------------------------------------------------------------------------------------------------------|---------|

| 3.12 | Block diagram of the control system of the MMC-based AWG                                                                | 36      |

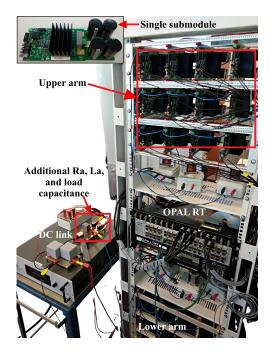

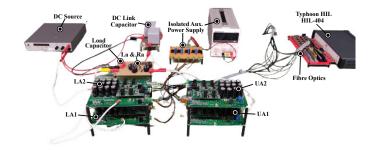

| 3.13 | Experimental hardware setup.                                                                                            | 37      |

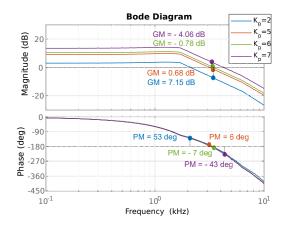

| 3.14 | Variations of the proportional gain on controller/system stability.                                                     | 38      |

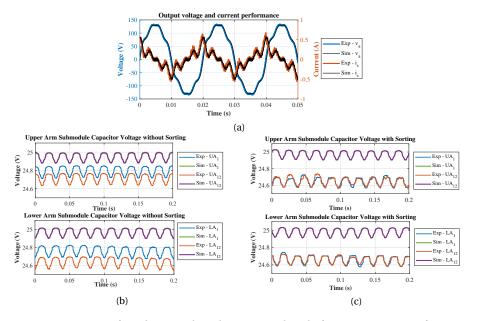

| 3.15 | Comparison of simulation results with experimental results for Harmonic                                                 |         |

|      | test waveform in time domain (a) Output voltage and current, Submodule                                                  |         |

|      | capacitor voltage (b) without sorting (c) with sorting                                                                  | 39      |

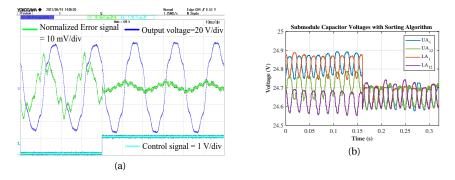

| 3.16 | Performance of (a) Proportional controller (b) Sorting algorithm imple-                                                 |         |

|      | mentation for Harmonic test waveform.                                                                                   | 39      |

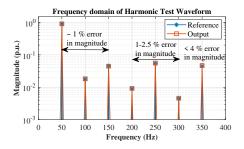

| 3.17 | Harmonic test waveform in frequency domain.                                                                             | 40      |

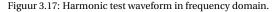

| 3.18 | Unipolar complex waveform in (a) Time domain (b) Frequency domain.                                                      | 40      |

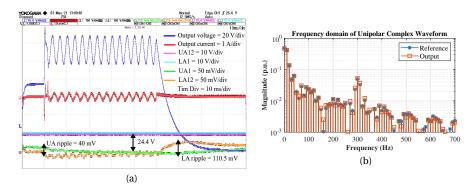

| 3.19 | Unbalanced sinusoidal waveform in (a) Time domain (b) Frequency domain.                                                 | 41      |

| 3.20 | Comparison of capacitor voltage ripple analytically, using simulations, and                                             |         |

|      | experimentally.                                                                                                         | 42      |

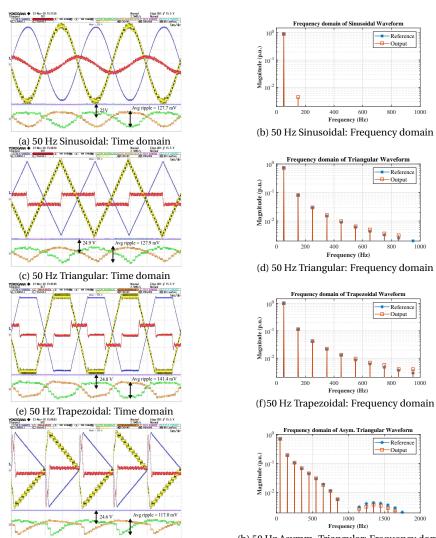

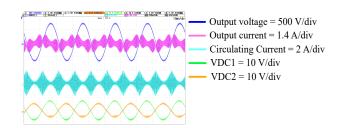

| 3.21 | Periodic waveforms generated from the small prototype of the MMC-based                                                  |         |

|      | AWG [Blue: $v_a=50$ V/div, red: $i_s=0.5$ A/div, Yellow: $v_s=50$ V/div, Pink & sky                                     |         |

|      | blue: UA <sub>12</sub> & LA <sub>1</sub> =10 V/div, Orange & Green: UA <sub>1</sub> & LA <sub>12</sub> =50 mV/div, Time |         |

|      | Div=5 ms/div]                                                                                                           | 44      |

| 3.22 | Complex waveforms generated from the small prototype of the MMC-based                                                   |         |

|      | AWG [Blue: $v_a=50$ V/div, red: $i_s=0.5$ A/div, Yellow: $v_s=50$ V/div, Pink & sky                                     |         |

|      | blue: UA <sub>12</sub> & LA <sub>1</sub> =10 V/div, Orange & Green: UA <sub>1</sub> & LA <sub>12</sub> =50 mV/div, Time | 4 -     |

| 0.00 | Div=20 ms/div]                                                                                                          | 45      |

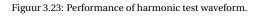

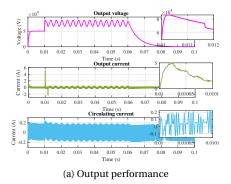

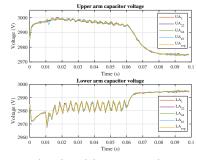

|      | Performance of harmonic test waveform                                                                                   | 46      |

|      | Performance of unipolar complex waveform.                                                                               | 46      |

| 3.25 | Performance of 50 Hz unbalanced sinusoidal.                                                                             | 46      |

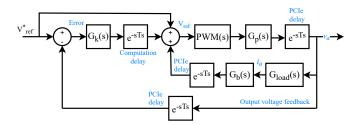

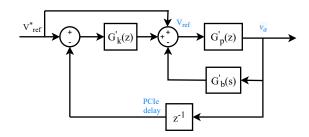

| 4.1  | Closed loop system of the MMC-based AWG                                                                                 | 50      |

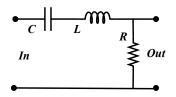

| 4.2  | Block diagram of the control system of the MMC-based AWG as a conti-                                                    |         |

|      | nuous equivalent                                                                                                        | 51      |

| 4.3  | Series band pass filter.                                                                                                | 52      |

| 4.4  | Simplified discretization system.                                                                                       | 54      |

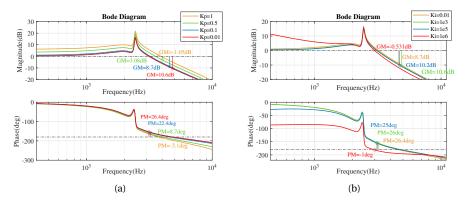

| 4.5  | Discrete domain (a) Variable Kp while Ki=0 (b) Variable Ki while Kp=0.01.                                               | 55      |

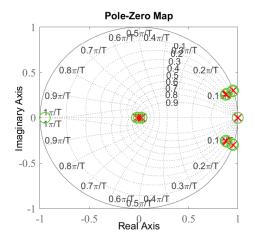

| 4.6  | Poles-zeros map with active damping                                                                                     | 55      |

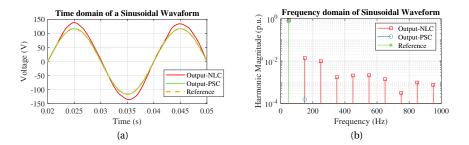

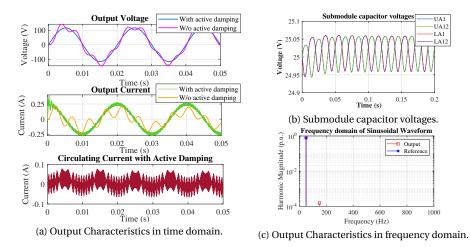

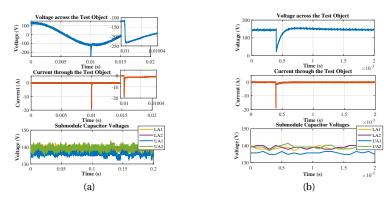

| 4.7  | Comparison between NLC and PSC with active damping control (a): Time                                                    |         |

|      | domain (b) Frequency domain.                                                                                            | 56      |

| 4.8  | Performance of active damping control methodology for 50 Hz sinusoidal                                                  |         |

|      | waveform.                                                                                                               | 57      |

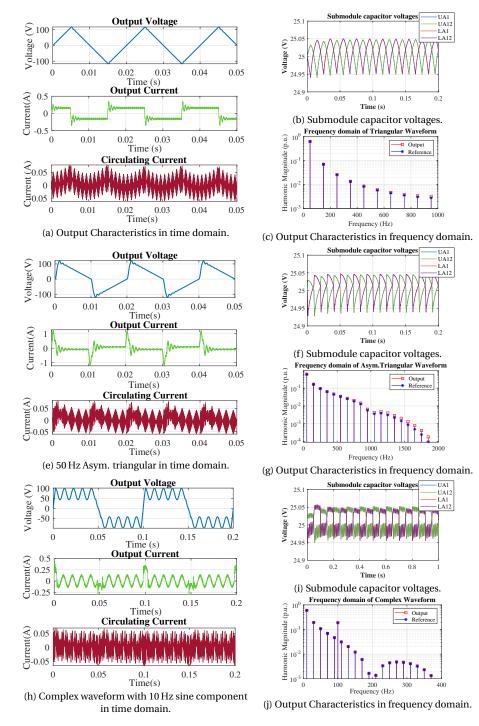

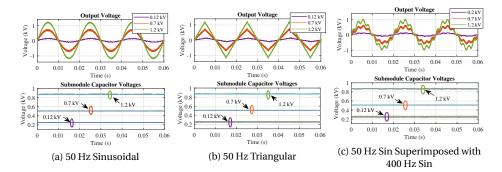

| 4.9  | Performance of active damping control methodology with different arbi-                                                  |         |

|      | trary waveforms.                                                                                                        | 58      |

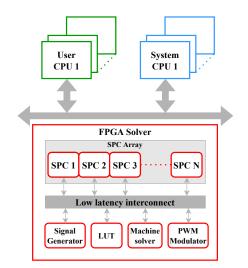

|      | Typhoon HIL architecture.                                                                                               | 60      |

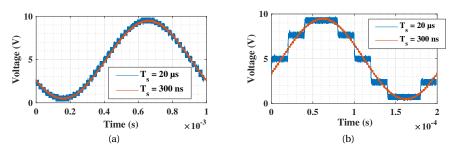

| 4.11 | Performance of RTS for generating high-frequency reference waveform (a)                                                 | _       |

|      | 1 kHz (b) 5 kHz.                                                                                                        | 61      |

| 4.12 | Scaled-down hardware prototype of the MMC-based AWG with Typhoon                                                        | <i></i> |

|      | HIL as a controller.                                                                                                    | 62      |

\_ |

- <sub>1</sub>

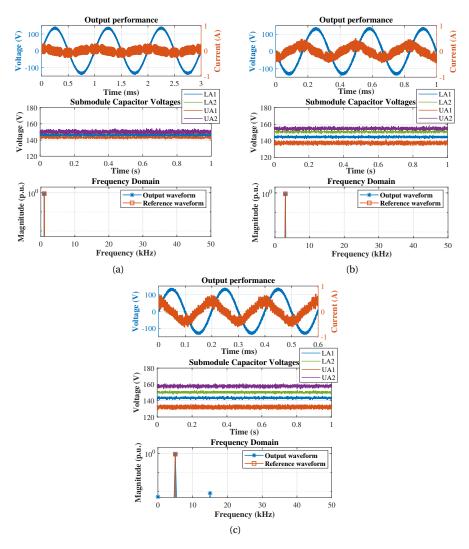

| 4.13 | Performance of RTS for generating high-frequency reference waveform (a) 1 kHz (b) 3 kHz (c) 5 kHz. | 63  |

|------|----------------------------------------------------------------------------------------------------|-----|

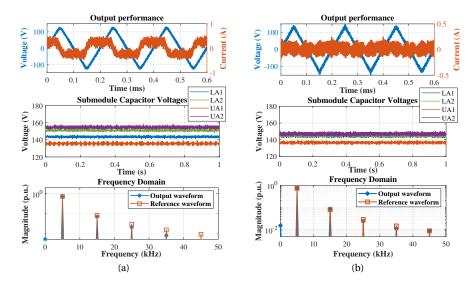

| 4.14 | Triangular waveform with 5 kHz Frequency (a) Filter 1 and switching fre-                           |     |

|      | quency of 144.750 kHz (b) Filter 2 and switching frequency of 178.750 kHz                          | 64  |

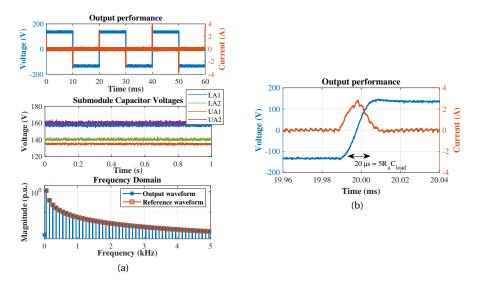

| 4.15 | (a) Square Waveform with 50 Hz frequency. (b) Zoomed version of Square                             |     |

|      | Waveform with 50 Hz frequency.                                                                     | 65  |

| 5.1  | Typical complex voltage waveforms required for the dielectric tests of grid                        |     |

| 0.1  | assets [110][111][99][112].                                                                        | 68  |

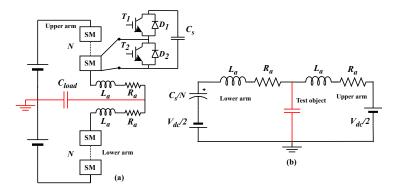

| 5.2  | (a) Schematic of the MMC-based HV AWG (b) Equivalent circuit of MMC                                | 00  |

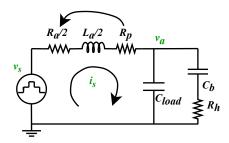

| 0.2  | for LI operation.                                                                                  | 69  |

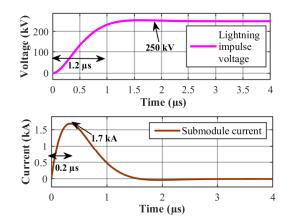

| 5.3  | LI voltage waveform and the required current provided by the MMC.                                  | 70  |

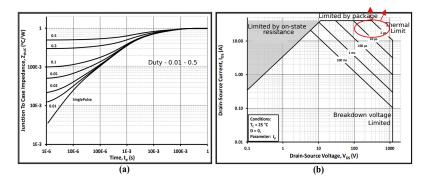

| 5.4  | C2M0160120D (a) Transient Thermal Impedances (Junction - Case) (b) Safe                            |     |

| 011  | Operating Area.                                                                                    | 71  |

| 5.5  | Details of the tested switches.                                                                    | 72  |

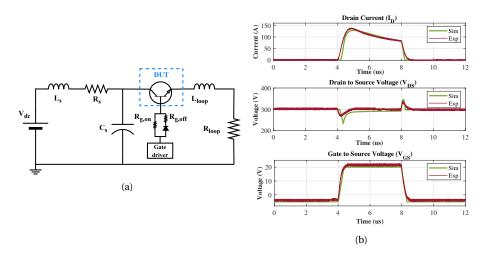

| 5.6  | (a) Schematic of the test setup (b) Comparison of LT-spice simulation and                          | • = |

| 0.0  | experimental results of C2M0160120D                                                                | 73  |

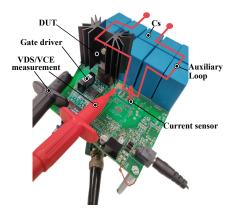

| 5.7  | Experimental setup for pulse current test of various switch technologies.                          | 73  |

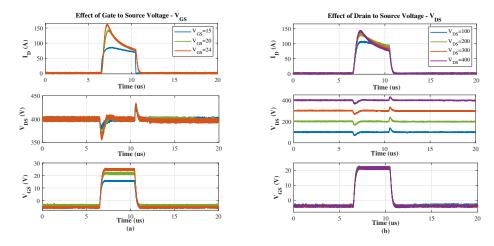

| 5.8  | C2M0160120D (a) Effect of the turn-on-gate-to-source voltage for constant                          |     |

|      | $V_{DS} = 400 V$ (b) Effect of applied drain-to-source voltage $V_{GS} = 20 V. \dots$              | 74  |

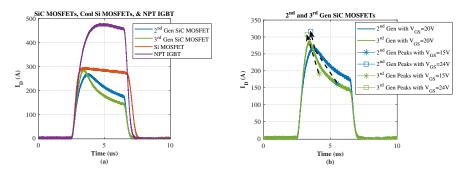

| 5.9  | $V_{GS} = 20 \text{ V}$ and $V_{DS} = 300 \text{ V}$ : Comparison of (a) SiC MOSFETs, Si MOSFET,   |     |

|      | and NPT IGBT (b) $2^{nd}$ and $3^{rd}$ generation SiC MOSFETs                                      | 75  |

| 5.10 | $V_{GS} = 24$ V and $V_{DS} = 300$ V: (a) Effect of blocking voltage for NPT IGBTs (b)             |     |

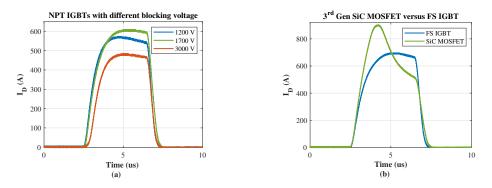

|      | Comparison of SiC MOSFETs and FS IGBT.                                                             | 76  |

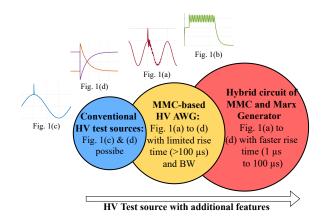

| 5.11 | Summary of additional capabilities offered by the MMC-based HV AWG.                                | 78  |

|      | MMC-based HV AWG to generate LI waveform.                                                          | 79  |

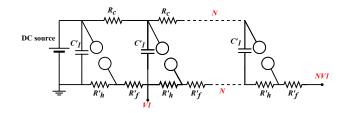

|      | Cascaded Marx generator circuit.                                                                   | 80  |

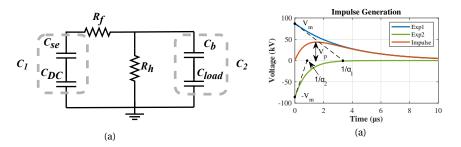

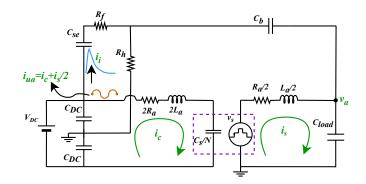

| 5.14 | (a) Equivalent Marx generator circuit (b) Impulse formation.                                       | 81  |

|      | MMC Side.                                                                                          | 83  |

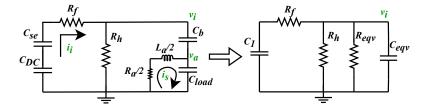

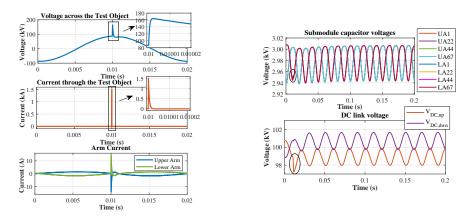

| 5.16 | Coupling with integrated hybrid circuit.                                                           | 84  |

|      | Updated Marx generator circuit with MMC.                                                           | 85  |

| 5.18 | LI when generated from Integrated Hybrid Circuit.                                                  | 87  |

|      | Parameter design procedure for the integrated hybrid circuit.                                      | 87  |

| 5.20 | Integrated hybrid circuit for negative impulse generation.                                         | 88  |

| 5.21 | Scaled-down experimental setup.                                                                    | 89  |

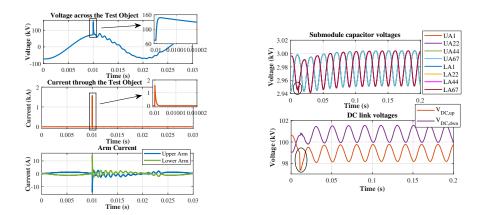

| 5.22 | Positive LI superimposed on 50 Hz sinusoidal waveform.                                             | 90  |

| 5.23 | Positive LI superimposed on (a) Negative DC (b) 50 Hz Sinusoidal and hig-                          |     |

|      | her harmonics (c) Unipolar complex waveform.                                                       | 91  |

| 5.24 | Negative LI superimposed on (a) 50 Hz sinusoidal (b) Negative DC wave-                             |     |

|      | form                                                                                               | 91  |

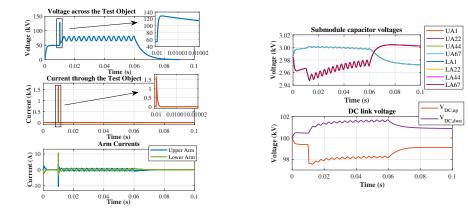

| 5.25 | Positive LI superimposed on positive peak of 50 Hz sinusoidal waveform.                            | 93  |

| 5.26 | Positive LI superimposed on negative DC waveform.                                                  | 93  |

| 5.27 | Positive LI superimposed on 50 Hz sinusoidal and higher harmonics wave-                            |     |

|      | form                                                                                               | 93  |

| 5.28 | Positive LI superimposed on unipolar complex waveform                                              | 94  |

|\_\_\_

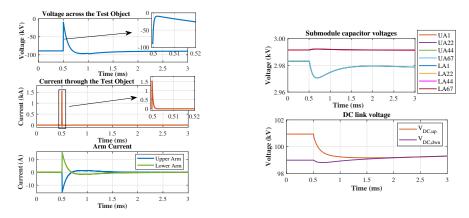

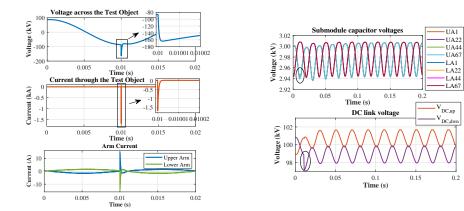

|      | Negative LI superimposed on negative peak of 50 Hz sinusoidal waveform.                           | 94  |

|------|---------------------------------------------------------------------------------------------------|-----|

| 5.30 | Negative LI superimposed on positive DC waveform                                                  | 94  |

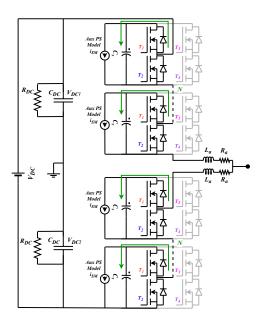

| 6.1  | Challenging elements in the full-scale submodule.                                                 | 98  |

| 6.2  | Commercially available auxiliary power supplies.                                                  | 100 |

| 6.3  | MV SM structure.                                                                                  | 101 |

| 6.4  | APS - PV15-27B12R3 (a) Efficiency vs Output Load (b) Efficiency vs Input                          |     |

|      | Voltage                                                                                           | 103 |

| 6.5  | Arm energy controller per SM                                                                      | 104 |

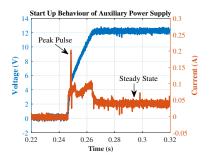

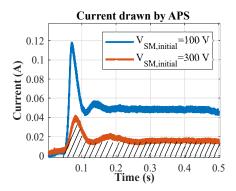

| 6.6  | Start up behaviour of auxiliary power supply with $V_{SM}$ =100 V and C <sub>s</sub> =75 $\mu$ F. | 104 |

| 6.7  | Issue with the auxiliary power supply at $C_s=75\mu\text{F.}\dots\dots\dots$                      | 105 |

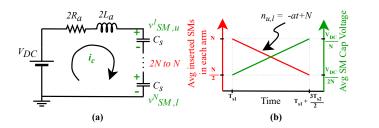

| 6.8  | Schematic of MMC during the start-up                                                              | 106 |

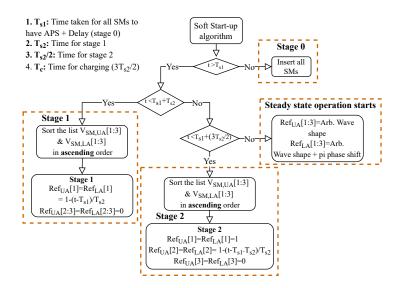

| 6.9  | Soft start-up algorithm for N = 3                                                                 | 107 |

| 6.10 | Working principle of soft start-up algorithm (a) Circulating current circuit                      |     |

|      | (b) Insertion index                                                                               | 107 |

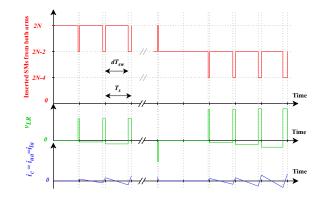

| 6.11 | Waveforms during the soft start-up.                                                               | 108 |

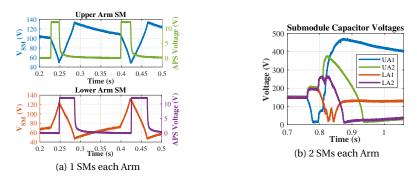

| 6.12 | SM capacitance design.                                                                            | 110 |

| 6.13 | Protection circuit of MMC-based AWG with single MV SM                                             | 112 |

| 6.14 | Overview of MMC-based AWG with single MV SM operation.                                            | 112 |

| 6.15 | Experimental setup                                                                                | 113 |

| 6.16 | Soft start-up and soft shut-down of the MMC-based AWG with single MV                              |     |

|      | SM                                                                                                | 114 |

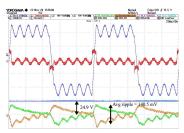

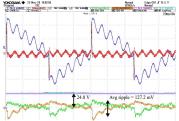

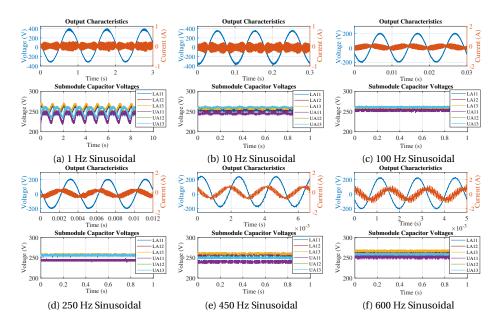

| 6.17 | Steady state performance the MMC-based AWG with single MV SM                                      | 115 |

|      | Experimental results with wide output voltage range                                               | 115 |

| 6.19 | Experimental results with wide output frequency range                                             | 115 |

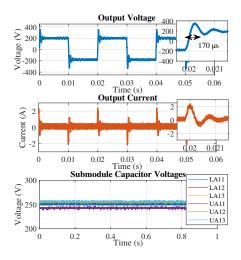

|      | Square pulse waveform.                                                                            | 116 |

| 6.21 | Fault Ride Through (FRT) performance (a) Output characteristics (b) SM                            |     |

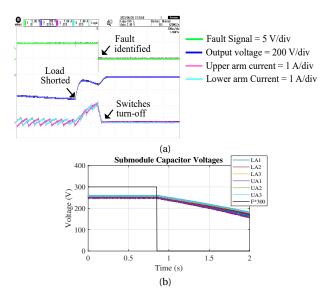

|      | Capacitor Voltages.                                                                               | 117 |

| 7.1  | Current status of the MMC-based HV AWG.                                                           | 119 |

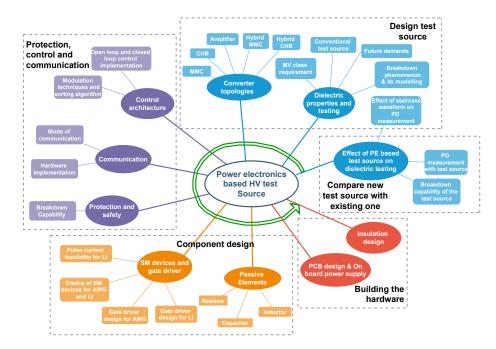

| 7.2  | Involved challenges in the PE-based HV AWG                                                        | 120 |

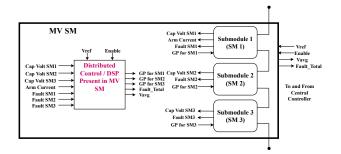

| 7.3  | Overall control architecture for MV SM                                                            | 121 |

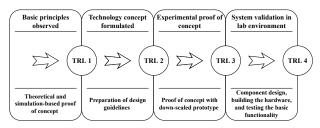

| 7.4  | Design flow for further development of the MMC-based HV AWG                                       | 122 |

| 7.5  | V model of the PE-based HV AWG                                                                    | 123 |

| 7.6  | Tests to be performed at SM level.                                                                | 123 |

| 7.7  | Most common issues that can happen in system integration of the MMC-                              |     |

|      | based HV AWG.                                                                                     | 124 |

| A.1  | Different Impulse Waveforms (a) LI (b) Tail chopped LI (c) Front chopped                          |     |

|      | LI (d) Linearly rising front chopped (e) SI [14]                                                  | 142 |

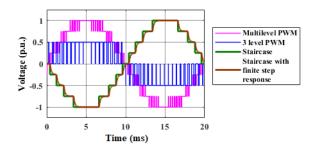

| B.1  | Different wave shapes as the output of the PE converters                                          | 144 |

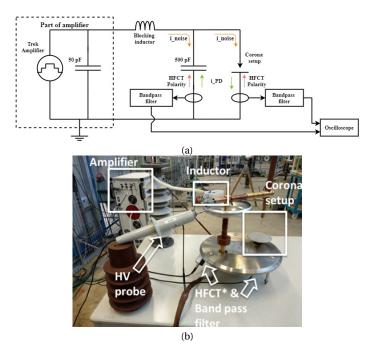

| B.2  | (a) Schematic (b) Actual PD Measurement Setup                                                     | 145 |

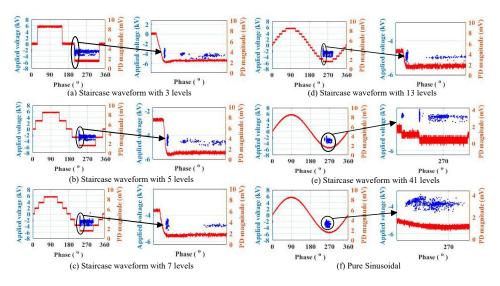

| B.3  | Comparison of sinusoidal and staircase waveform with a different number                           |     |

|      | of voltage levels on the PRPD pattern at $Vp = 5.6 \text{ kV}$                                    | 147 |

| B.4  | PRPD pattern for staircase waveform with 41 level at Vp = $5.6 \text{ kV} \dots \dots$            | 147 |

\_ |

-I

| B.5 | Comparison of sinusoidal and staircase waveform with 41 levels on the                                                                    |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | PRPD pattern at $Vp = 8 kV \dots $ | 147 |

| B.6 | PRPD pattern (a) to (d): $Vp = 5.6 \text{ kV } \& (e)$ to (h): $Vp = 8 \text{ kV}$                                                       | 148 |

|\_\_\_

\_ I

\_ I

# **LIST OF TABLES**

Ι\_\_

| 2.1 | Typical Range of the Equivalent Capacitance of Dielectric Insulation Materials                                          | 12  |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison of Conventional HV Test Sources versus Power Electronics-<br>based Test Source                               | 17  |

| 3.1 | Comparison of MMC and CHB Topology for the Same Output Voltage of $V_{\rm DC}/2$ magnitude and for N submodules per arm | 23  |

| 3.2 | Number of Submodule and Voltage Rating per Submodule                                                                    | 32  |

| 3.3 | System Parameters of Scaled-down MMC Setup                                                                              | 37  |

| 3.4 | Verification of SM Capacitor Ripple Calculations for Various Waveforms .                                                | 42  |

| 3.5 | Performance of Scaled-down MMC Setup for Waveforms Which Were Shown in Fig. 3.4                                         | 43  |

| 3.6 | System Parameters of Full-scale HV MMC Setup                                                                            | 43  |

| 3.7 | Performance of Full-scale HV MMC Setup for Waveforms Which were Shown                                                   |     |

|     | in Fig. 3.4                                                                                                             | 47  |

| 4.1 | System Parameters of the MMC Setup                                                                                      | 56  |

| 4.2 | THD of MMC-Based AWG with PSC for Periodic Waveforms                                                                    | 57  |

| 4.3 | System Parameters of Down-Scaled MMC Setup                                                                              | 62  |

| 4.4 | Performance of the MMC-based AWG for High Frequency Generation                                                          | 62  |

| 5.1 | Application Requirement on Pulse Current                                                                                | 69  |

| 5.2 | Comparison Among 2 <sup>nd</sup> and 3 <sup>rd</sup> Generation SiC MOSFETs, Si MOSFET, and NPT IGBT                    | 75  |

| 5.3 | Comparison between 3 <sup>rd</sup> Generation SiC MOSFET and FS IGBT                                                    | 76  |

| 5.4 | Relationship of Time Constants of Impulse Waveforms to $\alpha_1$ and $\alpha_2$                                        | 81  |

| 5.5 | System Parameters of the Scaled-down Prototype                                                                          | 89  |

| 5.6 | System Parameters of the HV Simulation Model                                                                            | 92  |

| 6.1 | Switches Considered                                                                                                     | 99  |

| 6.2 | Details of Commercially Available Auxiliary Power Supplies                                                              | 100 |

| 6.3 | Comparison of Different Submodule Topology with Constant Voltage per<br>Submodule (1 kV) and Output Voltage (100 kV)    | 101 |

| 6.4 | System Parameters of the MMC-based AWG with single MV SM                                                                | 114 |

| B.1 | Trend in the PD Repetition Rate with Sinusoidal and Staircase Waveform with a Different Number of Voltage Levels        | 146 |

| B.2 | Trend in the PD Repetition Rate with Sinusoidal and Staircase Waveform                                                  |     |

|     | with a Different Step Response                                                                                          | 148 |

\_ I

\_ I

## **SUMMARY**

Due to the massive integration of wind and solar energy using power electronic converters, High Voltage (HV) equipment in the electrical power system, such as switchgear, cables, and transformers, are experiencing new and/or different electrical stresses. This includes higher dV/dt stress and complex wave shapes due to the solid-state switching, which can degrade the reliability of the grid by weakening the dielectric material of the grid assets.

Additionally, existing HV test sources, i.e., transformers (cascaded and resonant), Marx generators, and rectifier circuits, face many limitations. Firstly, they do not have the flexibility to generate complex wave shapes. Secondly, the HV test sources have limited current capability from a few hundred milliamperes to a few amperes. Lastly, building a customized test setup is time-consuming when multiple HV test sources have to be combined to generate complex waveforms.

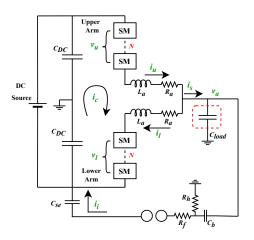

To address the above-mentioned challenges, an Arbitrary Wave shape Generator (AWG) for dielectric testing of HV grid assets is needed. A Modular Multilevel Converter (MMC) topology is selected as a promising solution, considering its modular structure, low harmonic content, and scalability to higher voltage levels. Dielectric testing of Medium Voltage (MV) class equipment is chosen as the first target for the MMC-based HV AWG, and a modular prototype is considered the final goal of the PhD.

## **HV** TEST REQUIREMENTS

HV test requirements and their procedures are compiled for the conventional tests of MV class equipment. Moreover, requirements for non-standards wave shapes are summarized considering the unconventional tests arising with the hybrid grid. This compilation delivers specifications for the MMC-based HV AWG in terms of the required voltage rating, current rating, and the bandwidth. It is important to highlight that HV grid assets behave electrically as a capacitance during the dielectric tests. Within this PhD thesis, two main HV test requirements are addressed. The first requirement for the HV AWG is the output voltage range of 10 kV to 100 kV, load capacitance range of 50 pF to 10 nF and large-signal bandwidth up to 2.5 kHz. The second requirement is about the generation of steep pulses with a rise time of a few microseconds for a voltage magnitude of 250 kV across the capacitive load of 10 nF.

## **DESIGN TRADE-OFFS OF MMC-BASED HV AWG**

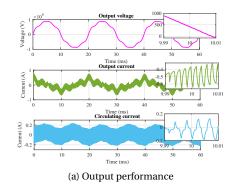

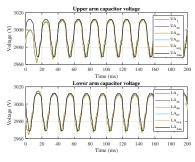

Although the MMC technology is well-maturated for HVDC transmission applications, the HV test requirements pose different challenges, and this thesis identifies different design trade-offs for the HV AWG application to generate accurate voltage waveforms. These design trade-offs are about the main MMC parameters, such as the number of Submodules (SMs) per arm, arm inductance, arm resistance, modulation technique, SM

capacitance, and control system, and their design criteria are developed. The performance of the proposed design guidelines is demonstrated with a simulation model and a scaled-down prototype with a 300 V DC-link voltage, where bipolar, unipolar, and mixed polarity waveforms are generated with a THD less than 3 %. Apart from the arm resistorbased passive damping, active damping methodology is investigated for HV AWG application to reduce the losses in the arm resistor. Additionally, the feasibility of the proposed design guidelines is validated with the simulation model for the full-scale prototype of the MMC-based HV AWG.

## **CONTROL HARDWARE OF HV AWG**

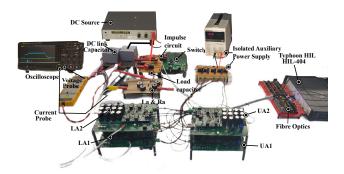

Though the modular structure of the MMC offers scalability with respect to its hardware SM, the controller hardware can be a challenge to generate high-frequency waveforms with arbitrary wave shapes. For this thesis, a commercially available Real Time Simulator (RTS) named Typhoon-HIL is selected, considering its flexibility to program arbitrary waveforms in the Field Programmable Gate Array (FPGA) without coding in any special hardware description language. Its performance is demonstrated in the scaled-down prototype where sinusoidal waveforms up to 5 kHz reference frequency are generated with THD less than 5 %.

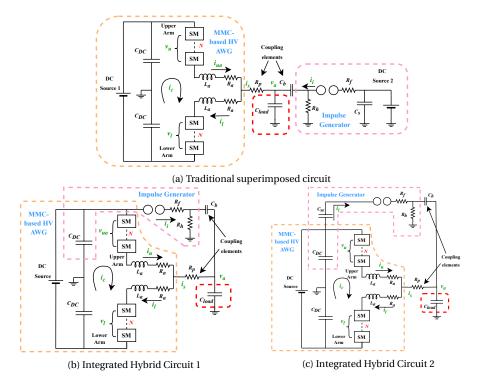

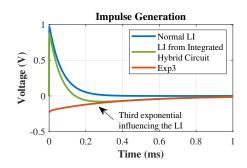

#### **STEEP PULSE GENERATION**

The second HV test requirement about the steep pulse generation is investigated with the MMC topology, and it has found that the inherent nature of series-connected SMs of MMC makes it very difficult to obtain such a short rise time across the large capacitive load of 10 nF. Hence, an integrated hybrid circuit of MMC and Marx generator circuit is proposed for the complex waveform with rise time faster than 100  $\mu$ s. The finite output impedance of the MMC interacts with the Marx generator circuit parameter and affects the front time and tail time. This thesis provides proper guidelines about choosing circuit parameters to obtain accurate rise and tail time, and these are validated experimentally with a scaled-down prototype.

## **DEMONSTRATION OF THE MV SM DESIGN**

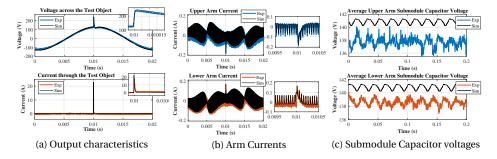

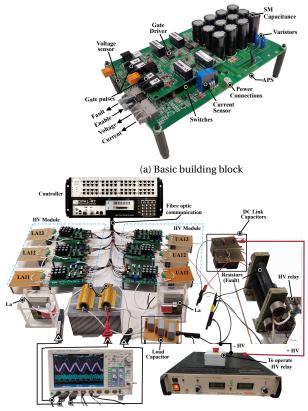

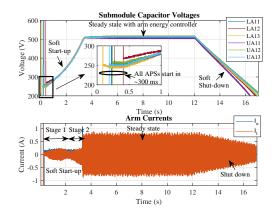

The important deliverable of this PhD thesis is the hardware design of a scalable MV SM (up to 3 kV) as a building block, to realize the 100 kV full-scale prototype of the HV AWG from commercially available components. The scalable design of MMC SM requires its Auxiliary Power Supply (APS) to be obtained from the SM capacitance. This additional component creates severe challenges to the MV SM design implementation in terms of its required SM capacitance value, start-up, steady-state, and shut-down procedures based on the derived current model of the APS. Based on the detailed quantitative analysis of the parameters mentioned above, the modular prototype of the MMC-based HV AWG is realized using a single MV SM per arm for various wave shapes, with the required wide output range of 0.12 kV to 1.2 kV, and frequency range of 1 Hz to 600 Hz with THD within 5 %. The proposed design of the scalable MV SM satisfies the second HV test requirement. Additionally, it can be used for performing dielectric tests such as partial discharge measurements or aging tests of the HV insulation material.

## SAMENVATTING

Als gevolg van de massale integratie van wind- en zonne-energie met behulp van vermogens elektronische omvormers krijgt hoogspanningsapparatuur in het elektriciteitsnet, zoals schakelapparatuur, kabels en transformatoren, nieuwe en/of andere elektrische belasting. Dit omvat hogere dV/dt en complexe golfvormen als gevolg van het schakelen van halfgeleiders, wat de betrouwbaarheid van het net negatief kan beïnvloeden door verzwakking van het isolatiemateriaal van de netcomponenten.

Bovendien hebben bestaande hoogspanningstestbronnen, zoals transformatoren (cascade en resonant), impulsgeneratoren en gelijkrichterschakelingen, veel beperkingen. Ten eerste hebben ze niet de flexibiliteit om complexe golfvormen te genereren. Ten tweede hebben deze testbronnen een beperkte stroomcapaciteit in het bereik van een paar honderd milliampère tot een paar ampère. Tot slot is het bouwen van een testopstelling tijdrovend wanneer meerdere bronnen gecombineerd moeten worden om complexe golfvormen te genereren.

Een oplossing voor bovengenoemde uitdagingen is het gebruik van een Arbitrary Waveshape Generator (AWG) voor het dielektrisch testen van hoogspanningscomponenten. De Modular Multilevel Converter (MMC) topologie is geselecteerd als veelbelovende oplossing op basis van de modulaire structuur, lage harmonische vervorming en schaalbaarheid naar hogere spanningsniveaus. Het dielektrisch testen van middenspanningsklasse apparatuur is gekozen als eerste doel voor de op een MMC-gebaseerde HV AWG, waarbij het modulaire prototype beschouwd wordt als het einddoel van dit proefschrift.

## HOOGSPANNINGSTESTEISEN

Voordat dieper wordt ingegaan op het ontwerp van de op een MMC-gebaseerde hoogspanningsgenerator Worden de testeisen en procedures voor conventionele middenspanningsapparatuur verzameld. Bovendien worden de vereisten voor niet-standaard golfvormen samengevat, rekening houdend met de onconventionele tests die bij het hybride net van de toekomst voorkomen. Dit overzicht levert specificaties op voor de op een MMC-gebaseerde HV AWG in termen van de vereiste spanning, stroom en bandbreedte. Het is belangrijk om te benadrukken dat de testen componenten zich elektrisch gedragen als een capaciteit tijdens dielektrische testen. In dit proefschrift worden twee belangrijke eisen Behandeld voor de AWG. De eerste eis omvat spanningen in het bereik van 10 kV tot 100 kV, belastingscapaciteiten tussen 50 pF tot 10 nF en een bandbreedte tot 2,5 kHz. De tweede eis gaat over het genereren van steile pulsen met een stijgtijd van enkele microseconden voor spanningen tot 250 kV over een capacitieve belasting van 10 nF.

## **ONTWERP KEUZES VAN OP EEN MMC-GEBASEERDE AWG**

Hoewel de MMC-technologie geschikt is voor HVDC transmissietoepassingen, geven de hoogspannignstesteisen andere uitdagingen. In dit proefschrift worden verschillende ontwerp keuzes geanalyseerd voor de HV AWG-toepassing om nauwkeurige spannings-golfvormen te genereren. Deze ontwerp keuzes omvatten de belangrijkste MMC parameters, zoals het aantal SMs per arm, de arminductie, de armweerstand, modulatie techniek, SM capaciteit en het regelsysteem. De prestaties van het voorgestelde ontwerp worden aangetoond met behulp van een simulatiemodel en een laagspanningsproto-type met 300 V DC-bus, waarmee bipolaire, unipolaire en complexe golfvormen kunnen worden gegenereerd met THD van minder dan 3 %. Naast de passieve demping gebaseerd op de armweerstand, wordt de actieve dempingsmethodologie onderzocht voor AWG-hoogspanningstoepassingen om de verliezen in de armweerstand te verminderen. De haalbaarheid van het voorgestelde ontwerp wordt gevalideerd met een simulatiemodel voor een MMC AWG op ware grootte.

## **BESTURINGSHARDWARE VAN DE AWG**

Hoewel de modulaire structuur van de MMC schaalbaarheid met betrekking tot de hardware biedt, kan de besturingshardware een uitdaging zijn om hoogfrequente golfvormen met willekeurige golfvormen te genereren. Voor dit proefschrift is een commercieel verkrijgbare Real Time Simulator (RTS) genaamd Typhoon-HIL geselecteerd vanwege de flexibiliteit van Typhoon-HIL om willekeurige golfvormen in de veldprogrammeerbare poortarray te programmeren zonder codering in Hardwarebeschrijvingstaal. De prestaties ervan zijn aangetoond door middel van een laagspanningsprototype waarmee sinusoidale golfvormen tot 5 kHz met een THD van minder dan 5 % zijn gegenereerd.

## **OPWEKKEN VAN STEILE PULSEN**

De tweede eis over het genereren van steile pulsen is onderzocht voor MMC-topologie, en het bleek dat de inherente eigenschappen van in serie geschakelde SMs het erg moeilijk maakt om pulsen met een korte stijgtijd te krijgen over een capacitieve belasting van 10 nF. Een geïntegreerde hybride schakeling van een MMC en Marx generator wordt voorgesteld voor complexe golfvormen met stijgtijden kleiner dan 100  $\mu$ s. De interactie van de eindige uitgangsimpedantie van de MMC met de parameters van het Marx generatorcircuit beïnvloedt de fronttijd en de rugtijd. Dit proefschrift geeft richtlijnen voor het kiezen van de juiste circuitparameters om een nauwkeurige front- en rugtijd te krijgen en wordt experimenteel gevalideerd met een prototype.

#### DEMOSTRATIE VAN HET ONTWERP VAN DE MIDDENSPANNINGS SM

Het belangrijke resultaat van dit proefschrift is het hardware ontwerp van een schaalbare Middenspannings SM (tot 3 kV) die geschikt is om het een 100 kV prototype AWG op ware grootte te realiseren met behulp van commercieel verkrijgbare componenten. Het schaalbare ontwerp van De MMC SM vereist dat de hulpvoeding (APS) uit de condensator van de SM wordt verkregen. Deze hulpvoeding creëert enkele grote uitdagingen voor de realisatie van het SM-ontwerp in termen van de vereiste grootte van de condensator, opstart-, stationaire en uitschakelprocedures op basis van het stroommodel van de APS. Gebaseerd op de gedetailleerde kwantitatieve analyse van bovengenoemde parameters, wordt het modulaire prototype van de op een MMC-gebaseerde AWG gerealiseerd met een enkele middenspannings SM per arm die geschikt is voor verschillende golfvormen, en het vereiste brede uitgangsbereik van 0,12 kV tot 1,2 kV, een frequentiebereik van 1 Hz tot 600 Hz en met maximaal 5 % THD. Het voorgestelde ontwerp van de schaalbare middenspannings SM voldoet aan de hoogspanningstesteisen en kan bovendien worden gebruikt bij het uitvoeren van dielektrische testen zoals partiele ontladingsmetingen of verouderingstesten van isolatiemateriaal.

\_ I

\_ I

# 1

## **INTRODUCTION**

## **1.1. MOTIVATION**

Extensive use of fossil fuels for electricity, heat, and transportation has significantly increased greenhouse gas emissions, impacting the Earth's ecosystem. To restore climate change and leave a safe space for future generations, the Paris Agreement was signed in 2015 by 196 parties to limit the temperature rise to 1.5 °C by the end of this century [1]. This has started extensive efforts to decarbonize the three sectors mentioned above with more sustainable solutions such as renewable energy sources for electricity and electrifying the other sectors. Hence, the electrical power network, the biggest man-made structure, is experiencing massive changes in its components and working operations. Earlier, the electricity used to flow in one direction from the generation centers to the demand centers. Currently, the electricity flow is multi-directional, and users can participate in supplying electricity with roof-top solar panels, electric vehicle batteries, or bio-fuel sources [2]. The growth in the semiconductor industry has revolutionized the electrical power network, where many variable energy sources generating DC or variable frequency AC can be integrated into the AC network with Power Electronic (PE) converters.

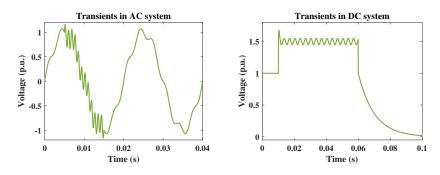

Due to numerous distributed generation systems and massive integration of Renewable Energy Sources (RES) by PE converters, High Voltage (HV) equipment in the electrical power system, such as switchgear, cables, and transformers, are experiencing new and/or different electrical stresses [3][4]. Fig. 1.1 illustrates a few examples of the new and/or different electrical stresses occurring in the hybrid electrical AC and DC power network. For this reason, HV equipment must endure higher dV/dt stress due to faster solid-state switching, which can degrade the grid's reliability by weakening the dielectric insulation of the HV grid assets. Conventional HV dielectric test sources, i.e., transformers (cascaded and resonant), impulse generators, and DC generators, face many limitations. Firstly, they do not have the flexibility to generate complex wave shapes. Secondly, HV test sources often have limited current capability in the range of mA to A. Lastly, building a customized test setup is time-consuming when multiple HV test sources have to be combined to generate complex waveforms. This emphasizes that a universal HV test source is necessary to cope with all the above challenges and limitations with the existing HV test sources and to facilitate the testing with the new future stresses, which are often customer specific. Eventually, this will speed up the necessary step-change needed for the energy transition. Since these new electrical stresses are mainly generated by the switching mechanisms of the semiconductor devices, the same ingredient is chosen to develop a programmable HV test source for future and advanced dielectric tests of various grid assets.

Figuur 1.1: New electrical stresses occurring in the electrical power network.

Though PE converters have been developed for a long time, adapting them as an HV test source for dielectric testing with arbitrary wave shape has many challenges. As the name suggests, the HV testing application requires an HV PE converter, ideally with a modular and scalable design to adapt to different voltage levels. The high voltage brings many challenges in realizing such a PE-based HV AWG from commercially available components. Next, it is important to highlight that the equivalent load during a dielectric test is capacitive [5]. Hence, there will not be any intended active power transfer in the PE-based HV Arbitrary Wave shape Generator (AWG). This significantly differs from the kW to GW (HVDC converters) range of active power transfer occurring in the typical PE converter. Lastly, the power efficiency of the converter is of utmost importance in energy transmission, whereas voltage accuracy is paramount in HV testing. With the differences mentioned above, specifications will be voltage and current capability, slew rate (rate of rise), and bandwidth.

## **1.2.** Scope, Objective and Research Questions

Based on the motivations and research challenges mentioned above, the PhD objective can be defined as follows:

#### "Design of a High Voltage Arbitrary Wave shape Generator for Dielectric Testing"

As a first attempt of the PE-based HV AWG, tests of Medium Voltage (MV) class equipment are targeted within this PhD. The voltage rating of the MV equipment ranges between 1 kV and 36 kV [6]. They are tested at much higher voltage, mainly with power frequency waveform and lightning impulse waveform at much higher voltage magnitude than its rated voltage [7]. Hence, a modular prototype of the HV AWG will be designed and realized in the ESP lab of TU Delft instead of moving directly to the full-scale prototype, and it is defined as the final goal of the PhD. Based on the research objective, the following research questions are formulated, which are investigated in detail in this thesis.

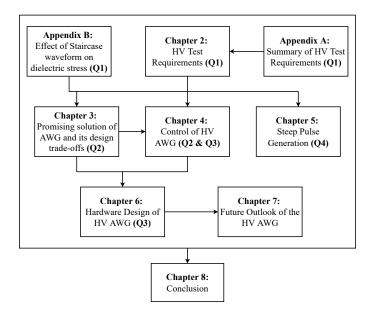

## Q1. What is HV testing/dielectric testing? How is it performed? (Chapter 2, Appendix A & Appendix B)

This research question provides the foundation for designing the PE-based HV AWG by compiling all test requirements and specifications. The conventional tests for MV equipment are summarized as per IEC standards in Chapter 2 and Appendix A in consulting with various test engineers from KEMA labs. Similar to Fig. 1.1, various unconventional test waveforms establish a concrete motivation for such a PE-based HV AWG, which is enhanced by showcasing limitations with existing HV test sources. Additionally, a PD measurement circuit is designed to study the effect of the switching waveform generated by the PE converter on the applied dielectric stress, which provides a good indication of choosing system parameters for the PE-based HV AWG.

## Q2. What is a promising solution direction for HV AWG? How to design the selected solution as a HV AWG? (Chapter 3 & Chapter 4)

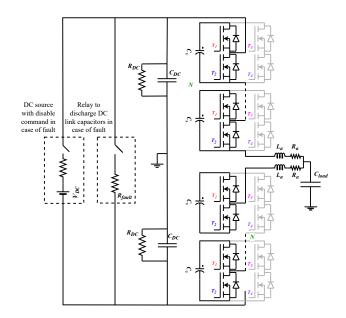

Various possible solutions, such as Modular Multilevel Converter (MMC), Cascaded H Bridge (CHB), and HV amplifier, are compared to choose a promising solution direction for the HV AWG. Then, the design trade-offs of the selected topology are investigated thoroughly with simplified equivalent circuits of the PE converter. The design trade-offs are about the choice of implemented modulation technique, control methodology, and passive elements. Then, the proposed design trade-offs are verified with the MATLAB-Simulink simulations and a scaled-down experimental prototype. In the end, system parameters for the full-scale prototype of the HV AWG are designed, and its performance is demonstrated with MATLAB-Simulink simulations. Ultimately, this chapter delivers a fundamental understanding and comprehensive design guidelines for realizing the HV AWG using the selected PE converter topology.

#### Q3. How to design hardware and control of HV AWG? (Chapter 4 & Chapter 6)

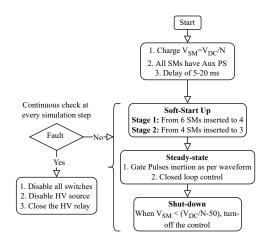

This question dives deeper into two main challenges of the HV AWG, i.e., the hardware and control design. Chapter 6 presents the innovative hardware design of an MV Sub-module (SM) from the commercially available components that satisfy all HV testing requirements. It is essential to highlight that the MV SM is scalable and can be stacked together to realize the full-scale prototype. A proper operation of the MV SM is achieved by formulating and designing precise start-up, steady-state, and shut-down procedures, and its performance is demonstrated in Chapter 6. Moreover, a protection system is designed in case a fault occurs in the part of the HV AWG or outside of the HV AWG when

the test object breaks down. The second challenge about the control hardware that can implement high-frequency gate pulse generation is discussed in Chapter 4, where an optimal control hardware is chosen considering the accuracy of waveform generation at high frequency with the ability to program different wave shapes and to withstand harsh Electromagnetic Compatibility (EMC) environments during the HV tests.

#### Q4. How to generate steep pulses with rise time as few microseconds using HV AWG? (Chapter 5)

Steep pulses with a rise time of as few µs, such as lightning impulse, can be challenging for the PE-based HV AWG, and its feasibility is studied with the selected topology from Chapter 3. Upon investigating the chosen topology, many challenges are observed concerning the switch current capability, communication error, and stray elements. For the PE-based HV AWG to be a universal test source, it has been integrated with the Marx generator to generate steep pulses and complex waveforms. This unique combination of two sources is studied analytically, and its performance is demonstrated with the simulations model and experimental setup.

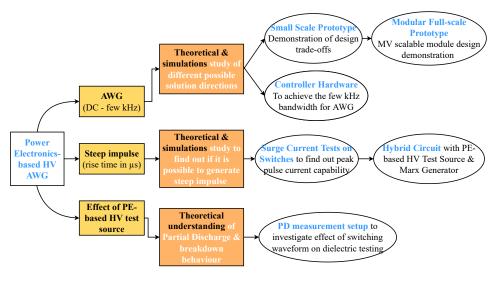

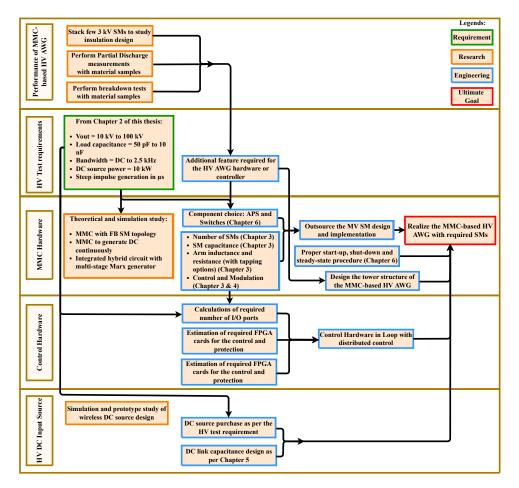

Figuur 1.2: PhD scope.

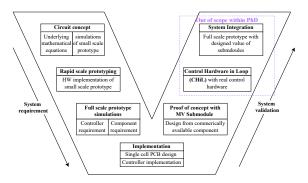

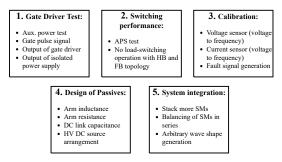

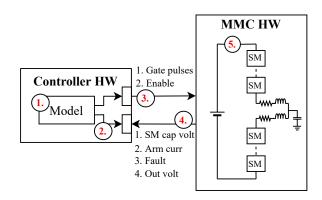

Fig. 1.2 summarizes the scope of the PhD with the above-mentioned research questions. Overall, the PhD research is divided into three aspects. The first aspect concerns generating arbitrary wave shapes up to a few kHz range. This research chooses a promising PE solution direction, and its design trade-offs are investigated analytically with simulation models and the experimental setup. With the help of these design trade-offs, an innovative and scalable MV module is realized using off-the-shelf components. Considering the harsh EMC environment in the HV test labs, the appropriate control hardware is chosen for the selected PE solution. The second research aspect is about performing