### Composable Virtual Platforms Chapter for bounded Mixed-Criticality template dissertation single multiple **Embedded Systems** architecture proposes CompSOC automotive may implement COT executing standard 1 example primitive C Ò solution laver order resc Ashkan Beyranvand Nejad

VP suppo operation

technique form vir gap partition

expressed underlying verification Figure

therefore

domai required

namely

hardware exec

service possibly data int

main

ces so

providing developed

set pi

de

pro

par

functio

# Composable Virtual Platforms for Mixed-Criticality Embedded Systems

Ashkan Beyranvand Nejad

### Composable Virtual Platforms for Mixed-Criticality Embedded Systems

#### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op woensdag 5 november 2014 om 12:30 uur

door

Ashkan BEYRANVAND NEJAD

Master of Science in Systems-on-Chip Design Kungliga Tekniska Högskola (KTH), Zweden geboren te Teheran, Iran Dit proefschrift is goedgekeurd door de promotor: Prof. dr. K.G.W. Goossens

Copromotor: Dr. Anca M. Molnos

Samenstelling promotiecommissie:

Rector Magnificus Prof. dr. Kees G.W. Goossens Dr. Anca M. Molnos Prof. dr. Koen L.M. Bertels Prof. dr. Ben Juurlink Prof. dr. Henk Corporaal Dr. Sorin D. Cotofana Prof. dr. Piet F.A. Van Mieghem voorzitter Technische Universiteit Delft, promotor CEA LETI, copromotor Technische Universiteit Delft Technische Universiteit Berlin Technische Universiteit Eindhoven Technische Universiteit Delft Technische Universiteit Delft

Ashkan Beyranvand Nejad Composable Virtual Platforms for Mixed-Criticality Embedded Systems

Met samenvatting in het Nederlands.

ISBN 978-94-6186-376-8

*Cover design:* The cover is designed by the author using the *word cloud* as the visual representation of the Introduction chapter of this dissertation, where the frequency of appearing each word in the text is shown relatively with its font size. The cloud is created using *Wordle<sup>TM</sup>* web-based tool.

Copyright © 2014 Ashkan Beyranvand Nejad

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

Printed in The Netherlands

Dedicated to my dear parents and to the love of my life, Jolnoosh.

### Abstract

*sECENT* trends show a steady increase towards concurrently executing more

*f* and more applications on a single embedded system. Multi-Processor Systemon-Chip (MPSoC) architectures are proposed to allow complex design of

*s* embedded systems. This is achieved by integrating as many processing

resources as possible on a single chip and therefore enabling the execution of multiple applications on a single embedded System-on-Chip (SoC). Due to cost implications, the applications have to share some resources when executing concurrently on these systems. To fully exploit the computational power of an MPSoC, an application is further split into a number of concurrent tasks. Depending on the intrinsic behavior of an application, its tasks may be either data- or time-interdependent, and accordingly, two different models of computation, namely data-driven and time-driven, are used to implement such an application. Besides this, applications typically have timing requirements expressed in three categories of firm, soft, and non real-time requirements. In a mixed *time-criticality* system, the applications that execute concurrently on a single embedded platform have widely varying real-time requirements, where resource sharing causes interference between the applications. In order to execute real-time applications on an embedded platform, the system has to be predictable to ensure that the timing requirements of the applications are met. Moreover, to enable independent design, verification, and integration of mixed-criticality applications, the system has to be strongly composable, i.e., concurrently executing applications are temporally isolated in such a way that the actual-case temporal behavior of each application is unaffected at the cycle-level. In this way, temporal interference between the applications is completely prevented.

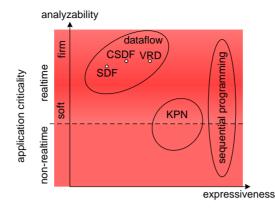

In this dissertation, we address two main challenges in designing and prototyping mixed time-criticality systems: (i) realizing strongly composable Virtual Platforms (VPs) for mixed-criticality embedded systems, and (ii) proposing a uniform abstract execution layer for applications expressed with different models of computation. Here, we target time-driven models of computation and, Kahn Process Network (KPN) and dataflow (specifically, Cyclo-Static DataFlow (CSDF)) as the two variants of data-driven models of computation. On the basis of these challenges we answer the main research question of *how to design and execute multiple applications concurrently on an embedded system, given that the applications are realized with different models of computation and having different levels of time-criticality?*

This dissertation proposes a solution to create a VP for every application by virtual-

izing all the hardware resources that are involved in the execution of the applications. For this, a temporal partitioning technique is applied to the CompSOC hardware architecture. On top of this architecture, the CoMik microkernel is designed as a minimum privileged software layer to provide resource partitioning. CoMik creates, controls and schedules processor partitions, and executes an application in its partition by virtualizing the processor's software hooks, offering an Application Programming Interface (API) to each application to use its allocated resources. Applications can therefore execute directly on their virtual platforms in the same manner as on a dedicated hardware platform. However there exists an execution abstraction gap between the models of computation's semantics and the platform's primitive operations. To fill this gap, a model of execution is proposed to define a common set of execution operations and their orchestrations in order to implement an specific model of computation.

The model of execution is implemented in the form of a lightweight operating system library, namely CompOSe, which is instantiated in every partition of a VP. CompOSe is designed in a number of software units and is implemented in such a way that it does not introduce any unpredictability in executing an application and complies with the composability property of the system provided by the CoMik microkernel.

We demonstrate that our proposed technique enables concurrent composable, predictable execution of applications realized with multiple models of computation by using two experimentation setups. One, a Matlab simulation environment is used to investigate the temporal behavior of the CoMik microkernel. Two, an FPGA prototype of the CompSOC platform is used to study the composability property and support of multiple models of computation by the CompOSe Real-Time Operating System.

### Acknowledgements

Well said by Ernest Hemingway, "It is good to have an end to journey toward; but it is the journey that matters, in the end". My journey began from 1987 when I started learning to read and write from my grandmother RIP. It was two years later, 22<sup>nd</sup> of September 1989, the night before the day that I went to the first grade of school, my farther called me in to tell me something very important: "Tomorrow you are going to take the first step of a long journey. Since you already know how to read and write, you are free to decide not to go to school. But, if you would decide to go, you should know that it could be a long journey that you cannot stop in the middle, and you have to go until the end. This is not what we force you to do, but the journey itself is so fascinating that you yourself cannot stop".

Now that you are reading this PhD thesis, I obviously decided that night to start the journey. I am now very satisfied with my decision, although I have gone through many ups and downs along the way to this point. Here, I cannot name all the people who helped and accompanied me in the first twenty years of this journey, before starting my PhD work, but I am thankful to all of them. I would also like to thank the committee members of my PhD defense and you, the reader, who may find this thesis interesting to you.

From the last six years, first and foremost I would like to sincerely thank my thesis promotor Prof.Kees Goossens for giving me the opportunity of pursuing my PhD under his supervision. I started my work with him from 2008 when I moved to the Netherlands for doing my M.Sc. thesis on a topic proposed by him at the time he was still in NXP Semiconductors. Since then, I have always enjoyed working with him and learnt a lot of things from all the technical and the non-technical discussions that I have had with him. I admire his high-quality research work and his personality, especially his patience.

I am sincerely grateful for the contribution of my thesis copromotor Dr.Anca Molnos to my work. Anca has been not only a good colleague for me who I enjoyed all the moments of working with her, but also a very nice friend of mine. I should acknowledge her noticeable influence on my writing skills for presenting a scientific work and her valuable feedback on the draft of this dissertation. I wish to express my appreciation and thanks for my great office-mate, good friend, and collaboration partner, Andrew Nelson. We have shared many memorable moments during the last five years in the trips, the meetings, the discussions, and most importantly in the work that we have done together. I would never forget his kind help during the preparation of my thesis, and I would also like to thank his girl-friend, Jorinde de Boer, for translating my propositions into Dutch.

From the CompSoC team, my thanks go to Radu Stefan, Benny Akesson, Martijn Koedam, Sven Goossens, Karthik Chandrasekar, Davit Mirzoyan, Manil Dev Gomony, and Shubhendu Sinha for all the great collaborations and discussions that we have had together. I should specifically thank Martijn and Sven for kindly having the abstract of my thesis translated into Dutch. I would also like to extend my gratitude to Bart Vermeulen who used to be the daily supervisor of my M.Sc. thesis and has been a good friend of mine for the last six years.

From the Computer Engineering Laboratory of TUDelft, my sincere appreciation goes to Prof.Koen Bertels for all his supports during the last five years. I would like to thank Lidwina Tromp, the secretary of the group, Erik de Vries and Eef Hartman, the IT administrators, for all their facilitating services kindly provided to us. I would also like to thank Arash Ostadzadeh, a good friend and colleague, for all the nice discussions that we had, and acknowledge his kindness for sharing this thesis template with me.

Last but the most important, I express my greatest gratitude towards my parents, Mehri and Reza, for all their encouragements and supports over the course of my life. Without always feeling them beside me, even from the long distance in the last eight years, I could not have taken even one step forward. I want to also thank my sister, Elham, for her unlimited supports and accompany in my life, and her husband, Babak, for his respectful encouragements from the time he joined our family. Finally, from the bottom of my heart, I would like to thank the love of my life, Golnoosh, for making my life sweat by being beside me from the first months of starting my PhD journey, and her endless supports without which I could not finish this dissertation.

Ashkan Beyranvand Nejad

Delft, The Netherlands, November 2014

# Table of contents

| Ał  | ostrac  | t                                                                 | İ    |

|-----|---------|-------------------------------------------------------------------|------|

| Ac  | knov    | vledgements                                                       | 벫    |

| Та  | ble o   | f contents                                                        | v    |

| Lis | st of f | âgures                                                            | ix   |

| Lis | st of 1 | ables                                                             | xiii |

| Lis | st of l | istings                                                           | xv   |

| Li  | st of A | Acronyms x                                                        | vii  |

| Те  | rmin    | ology                                                             | xix  |

| 1   | Intr    | oduction                                                          | 1    |

|     | 1.1     | Challenges                                                        | 3    |

|     | 1.2     | Overview of the Solution                                          | 5    |

|     | 1.3     | Contributions                                                     | 8    |

|     | 1.4     | Organization                                                      | 9    |

| 2   | Bacl    | rground                                                           | 11   |

|     | 2.1     | Predictability                                                    | 12   |

|     | 2.2     | Composability                                                     | 13   |

|     | 2.3     | Hardware Platform Architecture                                    | 13   |

|     |         | 2.3.1 CompSOC: A Composable & Predictable System-on-Chip Platform | 14   |

|     | 2.4     | Application Execution                                             | 17   |

|   |      | 2.4.1   | Scheduling                                        | 17 |

|---|------|---------|---------------------------------------------------|----|

|   |      | 2.4.2   | Task Temporal Model                               | 19 |

|   | 2.5  | Model   | of Computation                                    | 20 |

|   |      | 2.5.1   | Data-driven Model of Computation                  | 21 |

|   |      | 2.5.2   | Time-Driven Model of Computation                  | 25 |

|   |      | 2.5.3   | Summary                                           | 26 |

| 3 | Con  | posab   | le Virtualization                                 | 29 |

|   | 3.1  | Partiti | oning for Virtualization                          | 30 |

|   | 3.2  | Compo   | osable Virtual Platforms                          | 33 |

|   | 3.3  | CoMik   | a Composable Partitioning Microkernel             | 33 |

|   |      | 3.3.1   | Composable Temporal Partitioning                  | 35 |

|   |      | 3.3.2   | Scheduling & Swapping Partitions                  | 36 |

|   |      | 3.3.3   | Memory Partitioning Layout                        | 37 |

|   | 3.4  | A Hare  | dware Support for Virtualization                  | 38 |

|   |      | 3.4.1   | Counters                                          | 39 |

|   |      | 3.4.2   | Timers                                            | 39 |

|   |      | 3.4.3   | Interrupt Controller                              | 40 |

|   |      | 3.4.4   | Frequency Controller                              | 41 |

|   |      | 3.4.5   | Control Unit                                      | 42 |

|   | 3.5  | Interru | ıpt Virtualization                                | 42 |

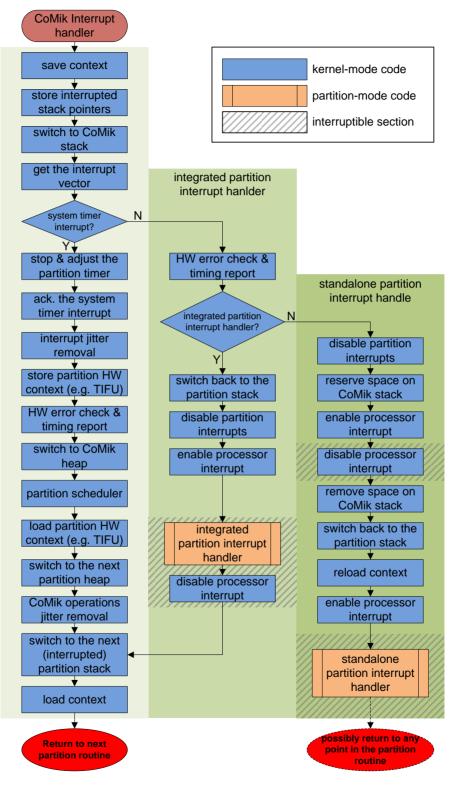

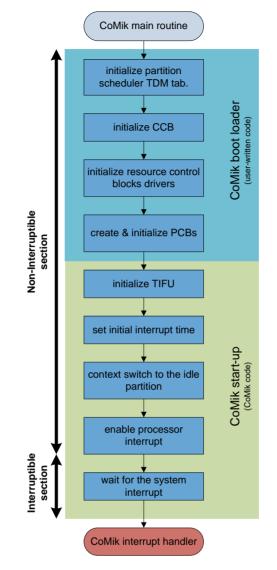

|   | 3.6  | Interru | ıpt Management in CoMik                           | 43 |

|   |      | 3.6.1   | CoMik Interrupt Handler                           | 43 |

|   |      | 3.6.2   | Partition Interrupt Handler                       | 44 |

|   |      | 3.6.3   | Exception Management in CoMik                     | 46 |

|   | 3.7  | Critica | ll Sections                                       | 46 |

|   |      | 3.7.1   | Kernel-Mode Critical Sections                     | 47 |

|   |      | 3.7.2   | Partition-Mode critical sections                  | 47 |

|   | 3.8  | CoMik   | Boot Loading                                      | 48 |

|   | 3.9  | Relate  | d Work                                            | 50 |

|   | 3.10 | Summ    | ary                                               | 52 |

| 4 | Real | ization | n of the Model of Execution                       | 53 |

|   | 4.1  | Model   | of Execution                                      | 54 |

|   |      | 4.1.1   | Execution Operations: Computation & Communication | 54 |

|   |      | 4.1.2   | Execution Operations: Scheduling                  | 58 |

|   |      |         |                                                   |    |

|     |                     | 4.1.3    | Realization of Models of Computation                                      | 59  |

|-----|---------------------|----------|---------------------------------------------------------------------------|-----|

|     |                     | 4.1.4    | Discussion on Realizing Models of Computation with the Model of Execution | 60  |

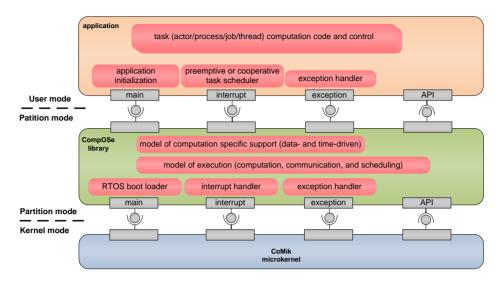

|     | 4.2                 | Comp     | DSe: an Operating System Library                                          | 61  |

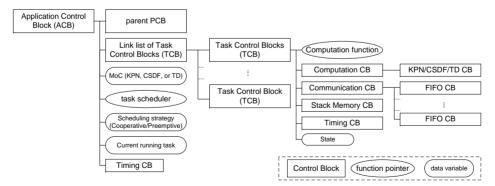

|     |                     | 4.2.1    | CompOSe Data Structure                                                    | 62  |

|     |                     | 4.2.2    | Partition Software Hooks                                                  | 64  |

|     |                     | 4.2.3    | Implementing the Model of Execution                                       | 65  |

|     |                     | 4.2.4    | Software Containers                                                       | 68  |

|     | 4.3                 | Related  | l Work                                                                    | 71  |

|     | 4.4                 | Summa    | ary                                                                       | 73  |

| 5   | Case                | e Studie | 28                                                                        | 75  |

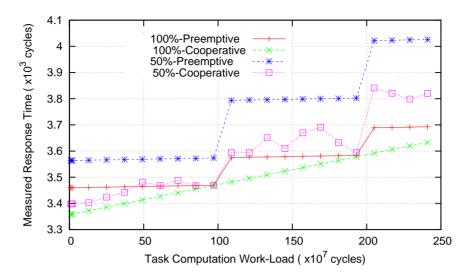

|     | 5.1                 | Predict  | ability of Time-Driven Applications                                       | 75  |

|     |                     | 5.1.1    | Matlab Simulation                                                         | 79  |

|     | 5.2                 | Compo    | osability & Mixed Models of Computation                                   | 82  |

|     | 5.3                 | Summa    | ary                                                                       | 91  |

| 6   | Con                 | clusion  | \$                                                                        | 93  |

|     | 6.1                 | Contri   | butions                                                                   | 93  |

|     | 6.2                 | Future   | Research Opportunities                                                    | 94  |

| A   | Soft                | ware-Ba  | ased Interrupt Virtualization                                             | 97  |

| Bi  | bliog               | raphy    |                                                                           | 103 |

| Li  | st of I             | Publica  | tions                                                                     | 111 |

| Sa  | menv                | atting   |                                                                           | 113 |

| Ste | elling              | en       |                                                                           | 115 |

| Pr  | oposi               | tions    |                                                                           | 116 |

| Ał  | bout the Author 117 |          |                                                                           | 117 |

# List of figures

| Chapte | r 1                                                                                                                             | 1  |

|--------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1    | An embedded system stack                                                                                                        | 2  |

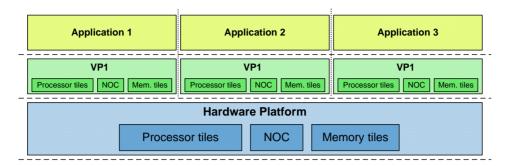

| 1.2    | An overview of the composable virtual platforms for mixed-criticality embedded systems.                                         | 6  |

| Chapte | r 2                                                                                                                             | 11 |

| 2.1    | Predictability and composability properties of the embedded system stack layers.                                                | 12 |

| 2.2    | The existing hardware architecture of the CompSOC platform. $\ldots \ldots$ .                                                   | 15 |

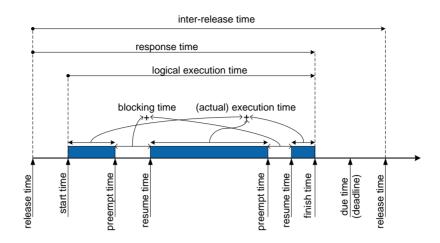

| 2.3    | A Task execution temporal model                                                                                                 | 20 |

| 2.4    | Analyzability versus expressiveness for common data-driven models of computation.                                               | 22 |

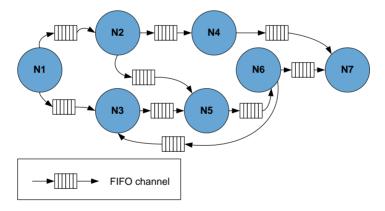

| 2.5    | Node graph of a data-driven model of computation                                                                                | 22 |

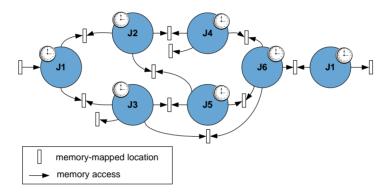

| 2.6    | Job graph of a time-driven model of computation                                                                                 | 25 |

| Chapte | r 3                                                                                                                             | 29 |

| 3.1    | An overview on the virtualization scheme of the CompSOC platform                                                                | 30 |

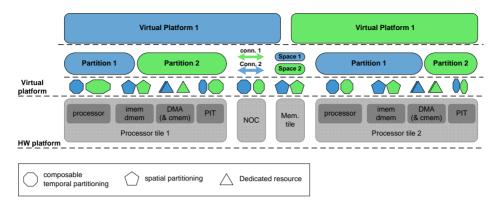

| 3.2    | An overview on applying partitioning techniques on the resources of the CompSOC platform to create Virtual Platforms (VPs)      | 31 |

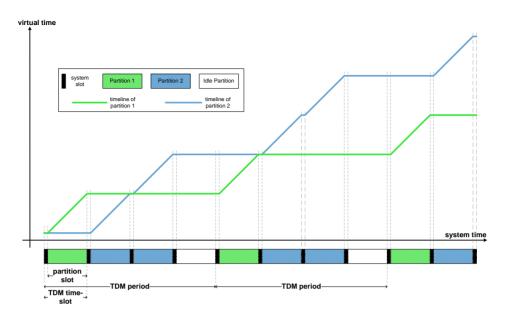

| 3.3    | A Time Division Multiplexing (TDM)-based processor partitioning tech-<br>nique illustrating virtual time-line of two partitions | 32 |

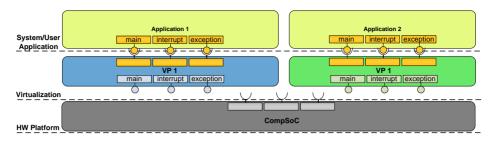

| 3.4    | Applications running on their dedicated virtual platforms                                                                       | 33 |

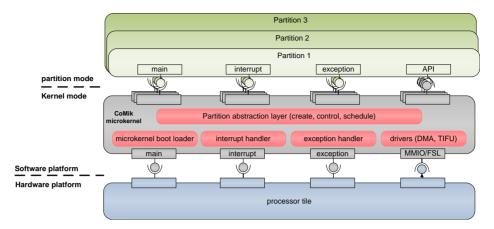

| 3.5    | The architecture of the software platform: CoMik in kernel mode, and partition routines in partition mode.                      | 34 |

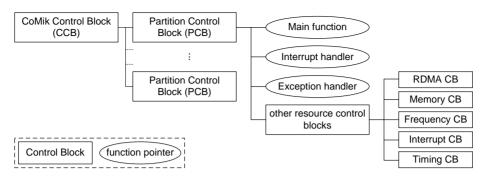

| 3.6  | Data structure of CoMik.                                                                               | 35 |

|------|--------------------------------------------------------------------------------------------------------|----|

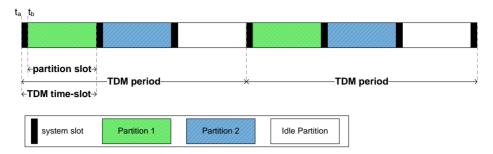

| 3.7  | A TDM-based processor partitioning technique.                                                          | 36 |

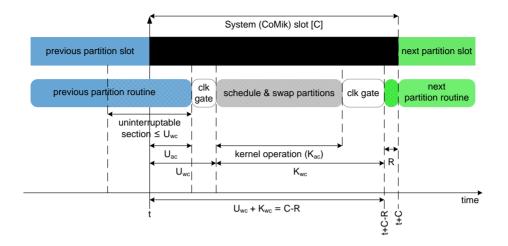

| 3.8  | A detailed view on the kernel operations and timeline in a CoMik slot. $% \mathcal{A} = \mathcal{A}$ . | 37 |

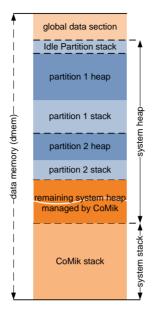

| 3.9  | The data memory partitioning layout.                                                                   | 38 |

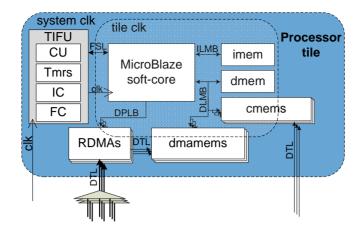

| 3.10 | The processor tile architecture including Timer-centric Interrupt and Fre-<br>quency Unit (TIFU).      | 39 |

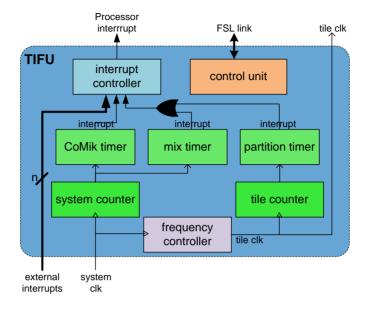

| 3.11 | The TIFU architecture                                                                                  | 40 |

| 3.12 | CoMik interrupt handling flow.                                                                         | 45 |

| 3.13 | Execution flow of the CoMik boot loader.                                                               | 49 |

### Chapter 4

|   | 2   |

|---|-----|

| 5 | - 4 |

|   | Э.  |

| 4.1 | CompSOC platform stack                                              | 53 |

|-----|---------------------------------------------------------------------|----|

| 4.2 | The structure of the model of execution implemented in form of Com- |    |

|     | pOSe Operating System (OS) library.                                 | 62 |

| 4.3 | Data structure of CompOSe                                           | 63 |

### Chapter 5

75

97

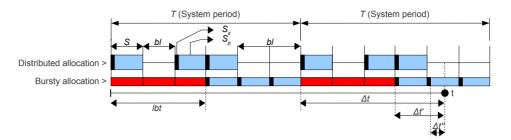

| 5.1  | An example of slots allocation to a partition (application) in a temporally-<br>partitioned system, illustrating the cumulative available processing time<br>and the (longest) blocking time of the partition. | 77 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

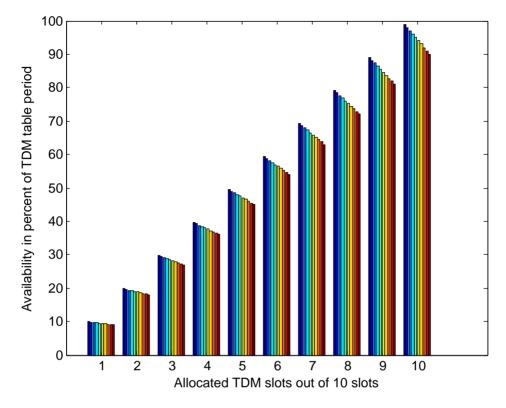

| 5.2  | Availability function of a partition in a 10-slot system.                                                                                                                                                      | 78 |

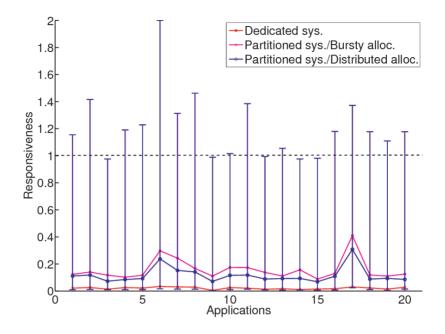

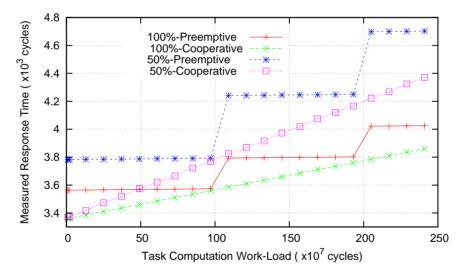

| 5.3  | Responsiveness of randomly generated applications.                                                                                                                                                             | 80 |

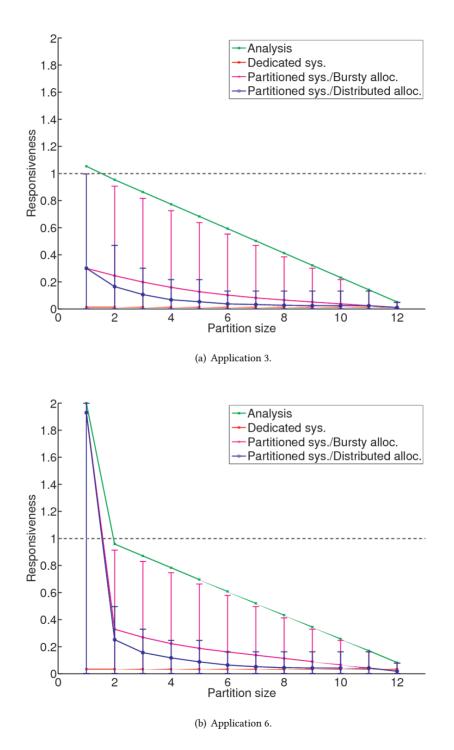

| 5.4  | Average responsiveness of two randomly generated applications                                                                                                                                                  | 81 |

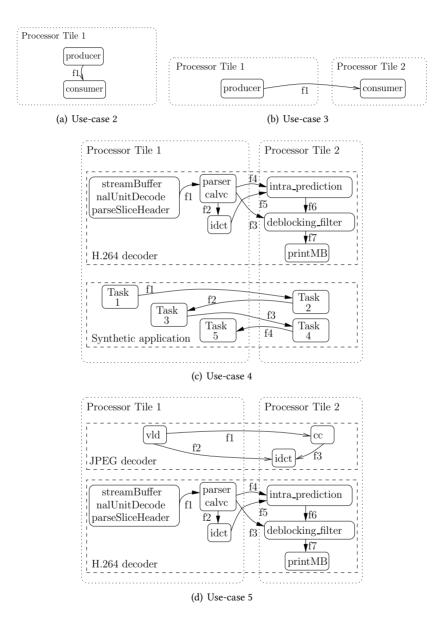

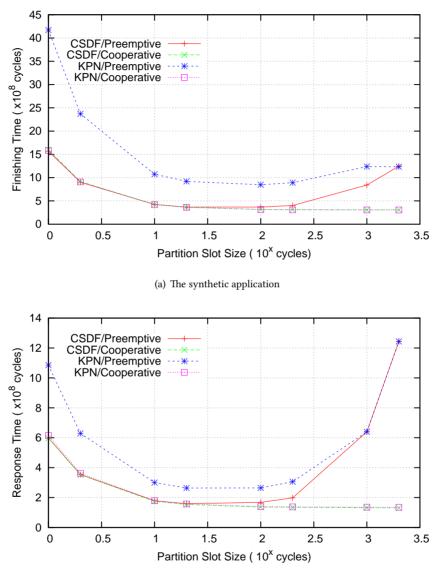

| 5.5  | Data-driven application use-cases                                                                                                                                                                              | 83 |

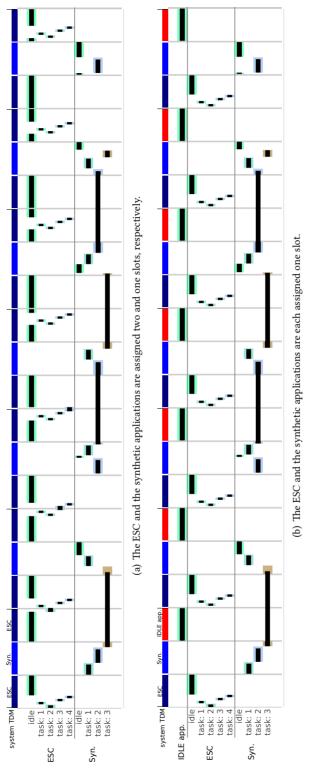

| 5.6  | Schedule trace of the applications running on an FPGA prototype                                                                                                                                                | 85 |

| 5.7  | Difference between response-time of the tasks in two runs, where the processor allocation to ESC application is changed.                                                                                       | 86 |

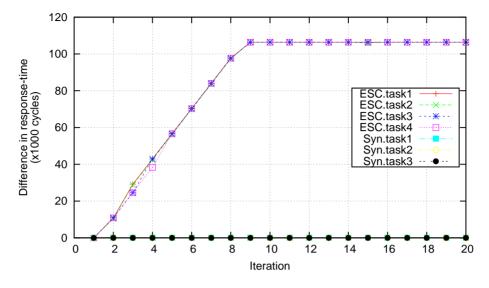

| 5.8  | Two use-cases of a simple synthetic application mapped on (i) one processor tile, and (ii) two processor tiles                                                                                                 | 87 |

| 5.9  | Synthetic and H.264 application on a two-Tile Multi-Processor System-<br>on-Chip (MPSoC) Platform                                                                                                              | 89 |

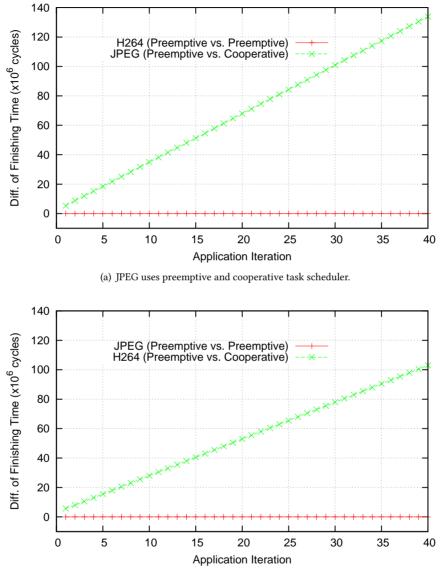

| 5.10 | The finishing time difference between two execution scenarios of JPEG and H.264 applications                                                                                                                   | 90 |

### Appendix A

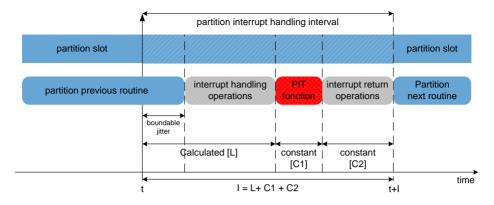

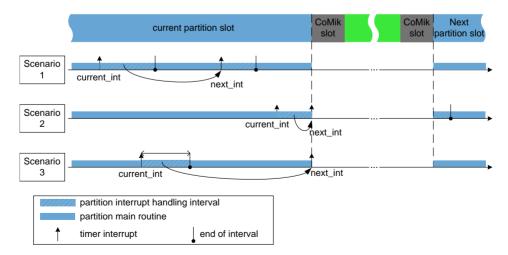

| A.1 | The General operational time-line of an application in a partition inter- |     |

|-----|---------------------------------------------------------------------------|-----|

|     | rupt handling interval                                                    | 98  |

| A.2 | Three possible scenarios of programming the timer interrupt.              | 100 |

## List of tables

| Chapte | r 2                                                                                                                                      | 11 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1    | Task scheduling overview of the models of computation                                                                                    | 27 |

| Chapte | r 4                                                                                                                                      | 53 |

| 4.1    | List of the execution operations required for executing the models of computation.                                                       | 54 |

| 4.2    | Implementation of the models of computation with the unified model of execution when task scheduling is either cooperative or preemptive | 59 |

| Appen  | dix A                                                                                                                                    | 97 |

| A.1    | Additional data structure required for Software-based interrupt virtual-<br>ization.                                                     | 99 |

# List of listings

| Chapte | r 2                                                                                                             | 11 |

|--------|-----------------------------------------------------------------------------------------------------------------|----|

| 2.1    | An example pseudo-code of a process in a Kahn Process Network (KPN) model of computation.                       | 23 |

| 2.2    | An example pseudo-code of an actor in a Cyclo-Static DataFlow (CSDF) model of computation.                      | 24 |

| 2.3    | An example pseudo-code of a process in a time-triggered model of com-<br>putation.                              | 25 |

| Chapte | r 4                                                                                                             | 53 |

| 4.1    | Execution operations corresponding to an example pseudo-code of a process in a KPN model of computation         | 57 |

| 4.2    | Execution operations corresponding to an example pseudo-code of an actor in a CSDF model of computation         | 57 |

| 4.3    | Execution operations corresponding to an example pseudo-code of an actor in a time-driven model of computation. | 58 |

| 4.4    | Pseudo code representation of CompOSe boot-loader                                                               | 64 |

| 4.5    | Pseudo code representation of CompOSe interrupt handler                                                         | 65 |

| 4.6    | Pseudo code representation of task's body container for KPN processes.                                          | 69 |

| 4.7    | Pseudo code representation of the task's body container for CSDF actors.                                        | 70 |

| 4.8    | Pseudo code representation of the firing-rules container for CSDF actors.                                       | 70 |

| 4.9    | Pseudo code representation of a task scheduler container for a CSDF actor.                                      | 71 |

| Append | dix A                                                                                                           | 97 |

| A.1 | Pseudo code representation of the Programming Timer Interrupt (PTI) |   |

|-----|---------------------------------------------------------------------|---|

|     | function                                                            | 0 |

# List of Acronyms

| ACB     | Application Control Block            |

|---------|--------------------------------------|

| AMP     | Asymmetric Multiprocessing           |

| API     | Application Programming Interface    |

| ARINC   | Aeronautical Radio Incorporated      |

| AUTOSAR | AUTomotive Open System ARchitecture  |

| ССВ     | CoMik Control Block9                 |

| ССМ     | Clock Control Module                 |

| CSDF    | Cyclo-Static DataFlow2               |

| DDR     | Double Data Rate 14                  |

| DLMB    | Data Local Memory Bus 10             |

| DPLB    | Data Processor Local Bus 1           |

| DTL     | Device Transaction Language10        |

| ECU     | Electronic Control Unit              |

| FCB     | FIFO Control Block                   |

| FIFO    | First-In-First-Out                   |

| FPGA    | Field Programmable Gate Array    114 |

| FRT     | Firm Real-time                       |

| FSL     | Fast Serial Link 10                  |

| ILMB    | Instruction Local Memory Bus 14      |

| IMA     | Integrated Modular Avionics          |

| KPN     | Kahn Process Network 2               |

| ΜΜΙΟ    | Memory-Mapped Input/Output1          |

| MMU     | Memory Management Unit 10            |

| MPSoC   | Multi-Processor System-on-Chip       |

| NI      | Network Interface                    |

| NOC     | Network-On-Chip                      |

| NRT     | Non Real-time                        |

| OEM   | Original Equipment Manufacturer1           |

|-------|--------------------------------------------|

| OS    | Operating System94                         |

| РСВ   | Partition Control Block                    |

| РІТ   | Programmable Interrupt Timer97             |

| РТІ   | Programming Timer Interrupt                |

| RISC  | Reduced Instruction Set Computer14         |

| RDMA  | Remote Direct Memory Access14              |

| RR    | Round-Robin                                |

| RTOS  | Real-Time Operating System    17           |

| SC    | Software Container                         |

| SDF   | Static Dataflow                            |

| SDRAM | Synchronous Dynamic Random-Access Memory14 |

| SoC   | System-on-Chip                             |

| SRT   | Soft Real-time                             |

| тсв   | Task Control Block   62                    |

| TDM   | Time Division Multiplexing93               |

| TIFU  | Timer-centric Interrupt and Frequency Unit |

| VM    | Virtual Machine                            |

| VMM   | Virtual Machine Monitor                    |

| VP    | Virtual Platform                           |

### Terminology

In this dissertation, we refer to several terms that are ambiguous and may specifically cause confusion when used in the context of Computer Science, especially in the field of embedded systems. In the following, we clarify the most important and frequently used terms with references to the first place that each terms is defined and used in this dissertation.

- **Application** is a set of algorithmic computational operations that realize a functionality which may be split is a set of communicating tasks [Section 2.5].

- **Task** is a piece of sequential code that implements a part of an application's functionality [Section 2.4.2].

- **Model of Computation** is a model that implements the application using a set of formal semantics defined to express the computational operations [Section 2.5]

- **Model of Execution** is a model that defines a set of execution operations and their orchestrations in order to implement an specific model of computation. It has to explicitly define computation, communication, and scheduling operations for each individual model of computation [Section 4.1].

- **Node** is a functional mapping from inputs to outputs in a model of computation [Section 2.5.1].

- **Process** is a node in the KPN model of computation and consists of a sequence of read, compute, and write operations which may be interleaved in any order [Section 2.5.1].

- Actor is a node in the CSDF model of computation with a sequence of consume, compute, and produce operations, in this strict order. A firing rule specifies, for one actor activation, for each incoming and outgoing edge, the number of input tokens consumed and the number of tokens produced, respectively [Section 2.5.1].

- **Job** is a node in the time-driven model of computation. It is ready to execute at an specific moment in time, when it assumes the data and the space that it may require for its execution are available [Section 2.5.2].

- **Time-Criticality** is a level of timing requirements expressed in one of the three categories of firm, soft, and non real-time requirements [The introduction of Chapter 1].

- **Predictability** is a system property which is defined as a level of how well the timing characteristics of the system are defined and implemented so that the system temporal behavior is known before it actually starts running the applications [Section 2.1].

- **Composability** is the property that the temporal (and functional) behavior of an application is isolated and independent from the one of other concurrent applications. A system is either *weakly* or *strongly* composable [Section 2.2].

- **Virtualization** is traditionally the technology to provide an illusion of execution resources to applications so that the applications behave like running directly on the bare resources [The introduction of Chapter 3].

- (Processor tile) Partition is created by the CoMik microkernel on every processor tile and it includes a composable temporal processor partition, an spatial *dmem* partition, a number of dedicated Remote Direct Memory Access (RDMA) modules [Section 3.2].

- **Virtual Platform (VP)** is logically defined as a set of resource partitions allocated to one application. Every VP provides the application with an illusion of a dedicated actual physical hardware architecture [Section 3.2].

- **Microkernel** a minimum privileged software layer that is designed to provide the essential services of partitioning for the purpose of virtualization [Section 3.3].

- **CompSOC** is a System-on-Chip (SoC) template developed following composability and predictability paradigm, and implements a tile-based multi-processor architecture which consists of a number of processor and memory tiles communicating via an on-chip interconnect [Section 2.3.1].

- **CoMik** is a microkernel that, on each processor, creates, controls, and schedules a number of partitions each of which is allocated to one application [Section 3.3].

- **CompOSe** is a Real-Time Operating System (RTOS) library that could execute as part of a *partition* created by the CoMik microkernel and implements the execution primitives proposed by the model of execution [Section 4.2].

- **Time-triggered scheduling** is a scheduling category in which the scheduler is invoked by a timed event, e.g., timer interrupt [Section 2.4].

- **Event-triggered scheduling** is a scheduling category in which the scheduler is invoked by any other event than a timed event, for example, an I/O interrupt or data availability [Section 2.4].

- **Preemptive scheduling** is a scheduling class in which the invocation of the scheduler preempts the executing task [Section 2.4].

- **Cooperative scheduling** is a scheduling class in which the executing task is allowed to finish (or signal that it can yield the processor) before the scheduler is invoked [Section 2.4].

# CHAPTER

### Introduction

*OWADAYS* embedded systems are widely used computing platforms in various domains such as automotive, consumer electronics, medical devices, avionics, etc. The common increasing demand of all these domains is to execute more and more applications concurrently on a single embedded system platform. Applications are functionally-independent software units that are developed by possibly different parties. The primary reason for such a demand varies per application domain. For example, in automotive domain, there are more than 70 individual Electronic Control Units (ECUs) developed by various Original Equipment Manufacturers (OEMs) integrated and communicating inside a middle class car [13]. In this domain, reducing the number of ECUs and increasing the number of applications executing on each one, not only reduces the manufacturing cost but also improves the reliability and maintainability of the systems since, for instance, the cabling complexity is decreased [37]. However, in avionics domain, to some extend the cost of reducing the number of electronic computing hardware modules is less important than reducing the weight of the aircrafts and complexity of the systems is an important objective [46, 70].

Shrinking the feature size of the transistors has led to low-cost integration of more and more number of processing resources on a single chip and consequently allows designing complex embedded system platforms using Multi-Processor System-on-Chip (MPSoC) [44]. Such platforms enable executing multiple applications on a single embedded System-on-Chip (SoC) architecture by providing each application with the required resources. However, since the requirements of applications grow faster, these architectures are still resource constrained. For cost reasons, the applications executing on these platforms have to share some resources, such as processors, interconnect, memory blocks, etc. An example of this trend is in avionics domain where the traditional federated computing architectures in which each subsystem occupied a physically separate hardware component is replaced with integrated computing architectures following Integrated Modular Avionics (IMA) design concept, in which multiple applications share the common computing platform [70, 81].

Furthermore, belonging to various domains such as consumer electronics, automotive, avionics, etc., the applications realize different functionality with different intrinsic behaviors. For example, multimedia applications have different functional behavior

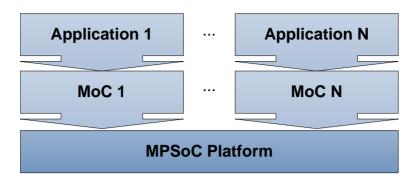

Figure 1.1: An embedded system stack.

compared to an engine control application. One example of multimedia applications is a video codec that typically receives an streaming input of data to which it applies some computation and outputs an stream of data for illustration. Instead, the engine control application, as an example of automotive applications, periodically reads some sensors, applies some computation, and produces a signal to control an actuator at specific moment in time. Thus, different models of computation are required to implement different applications. A model of computation implements the application using a set of formal semantics defined to express the computational operations [43]. Traditionally, the applications are first implemented in a sequential model of computation using an imperative programming language such as C. On MPSoC platforms multiple applications may execute in parallel. To fully exploit the computation power of an MPSoC, the parallelism is not restricted to the application level, but each application is further split in a number of concurrent tasks. Depending on the intrinsic behavior of an application, its tasks may synchronize naturally either on the basis of data availability or on specific times. In other words, the tasks may be either data- or time-interdependent. Accordingly, two different models of computation, namely data-driven and time-driven, are used to implement such inter-dependencies between the tasks.

Besides having different functional requirements, the embedded applications typically have timing requirements expressed in three categories of firm, soft, and non realtime requirements. These requirements are categorized with respect to the time, known as deadline, before which the application must produce an output and be finished. A Firm Real-time (FRT) application has strict timing requirements that must never miss a deadline otherwise damage may be caused to the system or environment [53]. While FRT applications can be found in various industries, the automotive and avionics applications are typically from such a kind. A Soft Real-time (SRT) application however may occasionally miss a deadline, whereas a Non Real-time (NRT) application do not have to meet any timing requirement and it has no deadline. The SRT and NRT applications exist in almost all the domains.

When the applications executing concurrently on a single embedded platform have different real-time requirements, the system has *mixed criticality* property. The term mixed-criticality may also apply to systems (mostly in automotive and avionics industries) with mixed-safety criticalities, however in this dissertation we aim at mixed time-criticality systems.

In summary, the ongoing trend of embedded systems is to design mixed time-criticality MPSoC platforms in order to execute multiple applications from various domains such as automotive, avionics, etc. The applications are implemented with either of data- or time-driven models of computation each of which has its own timing and functional requirements that has to be met when executing on the platform. Figure 1.1 illustrates an abstract overview of such system's stack. Now, let us explain the existing challenges in designing and prototyping such systems.

### 1.1 Challenges

To execute real-time applications on a platform, the system has to ensure that the timing requirements of the applications are met. For this purpose, the system has to be designed in such a way that the timing characteristics of the system are so well defined that the temporal behavior of the applications can be verified against their requirements before actually executing on the platform. Conventionally, this implies the *predictability* property of the system. Predictability is defined as a level of how well the timing characteristics of the system are defined and implemented so that the system temporal behavior is known before it actually starts running the applications.

In a mixed-criticality system in which multiple real-time applications execute concurrently on an embedded platform, resource sharing causes interference between the applications. Such interference might be either predictable (bounded) or unpredictable (unbounded). The predictable interference is typically between real-time applications with the bounded temporal execution behaviors; whereas the unpredictable interferences result from the non-real-time applications. In case of bounded unpredictable interference, as the number of concurrent execution combinations of the applications may grow exponentially, the verification and integration would become dramatically difficult [53]. It would be even worse when the applications are developed by different parties and all the applications has to be available at design time to be verified against their timing requirements. In the case of unbounded unpredictable interference, it is not possible at all to verify the timing requirements of the real-time applications and therefore to integrate them with the non-real-time ones.

In order to prevent the interference, the applications have to execute temporally isolated. For this, *composability* is proposed as one of the embedded system's properties. It is defined as: the temporal (and functional) behavior of an application is isolated and independent from of other concurrent applications [53, 85]. We denote a system as either *weakly* or *strongly* composable. Weak composability is denoted as a temporal-interference relaxed isolation between applications, where, with the help of predictability, a system could make the worst-case temporal behavior of an application unaffected by the other applications [55]. In this way, the system can guarantee a minimum service provided to the applications. However, in the mixed criticality systems, weak composability does not help to reduce the complexity of system verification and integration as it is not possible to come up with worst-case bounds for temporal behavior of the non real-time applications. *Strong* composability [4, 26] however is the isolation between the applications in such a way that the *actual-case temporal behavior* of each application is unaffected. This enables independent design, verification, and integration of mixed-criticality applications.

In order to implement a composable system, virtualization technology has gained recently a lot of attentions as a design trend in embedded systems [32]. In this technology an illusion of the execution resources are provided to the applications so that the applications behave like running on the bare hardware platform even though the resources are shared. Such an illusion of the system is called a *Virtual Platform (VP)*. Implementing the composability property for the system is then the challenge of creating temporally isolated VPs for the applications.

To virtualize the resources they have to be either dedicatedly allocated to an application or they have to be partitioned. Depending on the service provided by a resource, it can be partitioned either temporally or spatially [65]. For instance, in this context, two well-known standards, namely Aeronautical Radio Incorporated (ARINC) and AUTomotive Open System ARchitecture (AUTOSAR), have been developed in the automotive and the avionics domains, respectively. Real-Time Operating Systems (RTOSs) that are designed based on these standards are to support the partitioning of hardware resources in order to enable realization of VPs for mixed-criticality systems.

In the avionics domain, ARINC standard is a specification for time and space partitioning in mixed-criticality avionics RTOSs [83]. It specifies partitions at application level, where one or more applications with different criticality can belong to one partition [96]. The standard also specifies Application Programming Interfaces (APIs) for abstraction of the application from the underlying hardware and software platform. The RTOSs developed based on this standard guarantee the minimum amount of service that a partition receives. Thus, an application executing in a partition is affected by the presence/absence of other partitions.

In the automotive domain, AUTOSAR is a standard automotive software architecture, jointly developed by automobile manufacturers, suppliers and tool developers [9]. It contains an RTOS specification which defines real-time performance, scheduling strategy and temporal partitioning for executing applications with mixed-criticality. In this standard the partitions are implemented with a schedule table, and a time monitoring mechanism is used to limit the worst-case execution time of the applications. Thus, an application timing behavior can be possibly affected by the execution of other applications.

None of this existing systems fully comply with the definition of strong composability. As we argued, strong composability is very strict in the sense that the actual-case behavior of the applications has to be isolated. This means that the actual (and worstcase) timing properties of the an application are cycle-accurately independent of the other applications. A challenge here is to create VPs that comply with this strict definition of the composability.

Furthermore, the applications that are going to execute on VPs are possibly expressed with different models of computation, i.e., data- or time-driven. Each model of computation has its own execution primitives for computation and communication operations. Besides this, in the case of concurrent models of computation where an application is split into a number of tasks, scheduling operation comes into the application execution play. In order to hide the execution details of the implementation on the platform, these operations are typically specified at a high level of abstraction. For example, in a datadriven model of computation where inter-task communication is performed by means of First-In-First-Out (FIFO) queues, a read operation of a task is an abstraction of checking a queue for available data and retrieving the data from possibly a remote memory location on the platform. Thus, there is a gap of execution abstraction between the models of computation's semantics and the primitive execution operations supported by the platform. This gap causes a huge design effort to support the applications with various models of computation. A design challenge here is therefore to fill this gap by an intermediate execution layer to support the different models of computation in a unified manner.

In summary, in this dissertation we address two main design challenges: (i) realizing strongly composable VPs for mixed-criticality embedded systems, and (ii) proposing a uniform abstract execution layer for applications expressed with different models of computation on the VP. These two challenges lead us to the main research question of this dissertation that can be presented as follows:

#### How to design and execute multiple applications concurrently on an embedded system, given that the applications are realized with different models of computation and having different levels of time-criticality?

The rest of this chapter is going to explain our proposed solution to answer this question, where the solution makes several contributions to address the two aforementioned challenges.

#### 1.2 Overview of the Solution

In order to tackle the introduced research question our approach is to follow the explained design trends in embedded systems where the virtualization technology is applied to make the mixed-criticality systems predictable and composable.

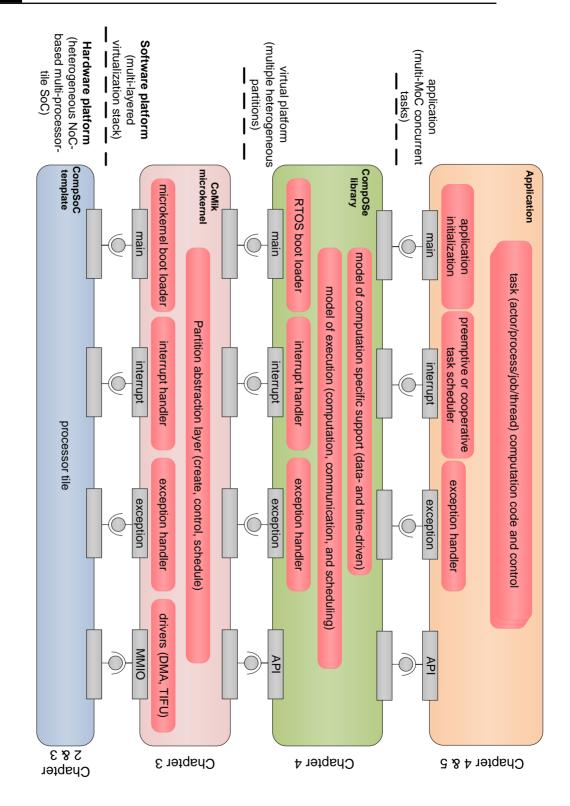

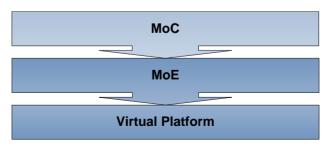

In this approach the aim is to create a VP for every application by virtualizing all the resources that are involved in the execution of the applications. For this, we use the partitioning technique. This technique is applied to different resources of the platform. Depending on the service type provided by a resource, it can be partitioned temporally or spatially [65]. In the context of mixed-time criticality systems, our main focus is on temporal partitioning of the resources. For this, we propose a complete platform-based approach as illustrated in Figure 1.2. This approach mitigates the complexity of a mixedcriticality system stack by proposing a multi-layered virtualization software platform on top of an MPSoC heterogeneous hardware architecture.

Starting from the bottom of the stack, in the hardware platform, each resource has to be specially designed and implemented for the purpose of guaranteeing predictable and composable execution of applications with mixed-time criticality. CompSOC is a SoC template developed following composability and predictability paradigm [29]. Here, we use this template as the basis of our hardware architecture. CompSOC has a tiled-based MPSoC architecture which consist of a number of processor and memory tiles communicating via a Network-On-Chip (NOC) [22, 27, 31, 89]. All its resources are designed and arbitrated between the executing applications in such a way that they realize predictable and composable system.

Figure 1.2: An overview of the composable virtual platforms for mixed-criticality embedded systems.

To create a composable temporal partition of the processor tile, the arbitration scheme has to provide a guarantee on when the service is exactly available to a partition in order to prevent the interference of other partitions. Every application executes in a dedicated partition. Time Division Multiplexing (TDM) is used as one of the arbitration schemes that can provide such a guarantee. Using this technique a set of time slots are created as fixed resource utilization time quanta. A temporal partition is then a set of these time slots allocated to an application. Applying the composable partitioning technique to all the resources involved in executing an application in a processor tile, a partition is formed. A VP is then a set of these partitions allocated to one application from resource in the platform.

On top of the hardware platform, a privileged software layer is designed to provide the essential services of partitioning for the purpose of virtualization. Our solution realizes this layer in the form of a microkernel, namely CoMik. CoMik virtualizes the underlying platform by executing the instruction routines in the form of three software hooks, i.e., main function, interrupt handler and exception handler, as illustrated in Figure 1.2. Using these, CoMik creates, controls, and schedules processor tile partitions. Moreover, it executes an application in its partition by virtualizing the software hooks and offering an API so that the application could use its allocated resources.

Created isolated partitions by the CoMik microkernel, an application can execute directly on its virtual platform. For this, the model of computation has to use the primitive execution operations offered by CoMik via the partitions. In our solution, a model of execution is however proposed to fill the gap of execution abstraction between the models of computation's semantic and the platform's primitive operations. The model of execution categorizes the execution operations as: (i) computation, (ii) communication, and (iii) scheduling operations.

The model of execution targets Kahn Process Network (KPN) and dataflow (specifically, Cyclo-Static DataFlow (CSDF)) as the two data-driven models of computation, and time-driven models of computation. Supporting these, a wide range of time-criticality application domains is covered. Data-driven models of computation typically require to schedule their tasks cooperatively, while the time-driven model needs a preemptive type of scheduler. The model of execution therefore proposes a unified manner to implement both data-driven and time-driven models of computation, and for this, it identifies the common operation primitives of these models.

The model of execution is implemented in form of a lightweight Operating System (OS) library, namely CompOSe. The CompOSe library is instantiated in every partition of the VP created by CoMik for an application. As illustrated in Figure 1.2, CompOSe is designed in a number of software units for: (i) providing the *main, interrupt handler*, and *exception* handler software hooks required by CoMik from a partition, (ii) implementing the execution primitives of the model of execution using the API provided by CoMik, and (iii) giving model of computation specific support to the application by providing Software Containers (SCs). CompOSe is implemented in such a way that it does not introduce any unpredictability in executing an application on top of the CoMik microkernel and therefore it complies with predictability and composability of the system.

Finally, at the application layer, multiple applications can be expressed in different models of computation each of which execute in a partition of a dedicated VP. The

applications may use its own arbitrary type of task schedules, and even handle their own interrupts and exception in fully isolation of the other concurrent ones.

### 1.3 Contributions

This dissertation makes six contributions to develop the solution of providing Composable VPs for mixed-criticality systems, as follows.

- The temporal partitioning technique is applied to the CompSOC embedded template for the purpose of creating composable VPs. For this, a Timer-centric Interrupt and Frequency Unit (TIFU) is developed. This hardware unit enables composable temporal partitioning of the processor, offers isolated virtual time management of the applications execute in a partition, and provides interrupt virtualization support<sup>1</sup>.

- 2. The CoMik microkernel is designed and implemented as virtualizing software layer that creates strongly composable temporal partitions for each application, and abstracts the execution operations of the underlying platform by providing a set of higher level of abstraction API to the applications execute in their partitions. CoMik implements a cycle-level composability between the partition without needing to modify the processor architecture<sup>1</sup>.

- 3. The unified model of execution is proposed to fill the gap of execution abstraction between the models of computation's semantics and the primitive execution operations supported by the VPs. It realizes the models of computation by using their common execution operations and representing them with a sequence of regular expressions.

- 4. The CompOSe library is designed as a lightweight OS to implement the model of execution. It is designed to run as an untrusted code in a partition and accesses the underlying platform resources in controlled and restricted mode. By the set of API and SC that it offers to applications, multiple models of computation with different time-criticality can be implemented on the platform.

- 5. The timing properties of the proposed composable platform are formalized by introducing a response time analysis of time-driven applications to check for their schedulability on the CompSOC platform. The formalization enables application developers following two design options: (i) (re-)design (legacy) applications to be schedulable on the CompSOC platform, and (ii) adjust the partition parameters, i.e., slot allocations and slot sizes, so that the available (legacy) applications would be schedulable.

- 6. The predictability, the composability, and the support of multiple models of computation are demonstrated empirically by using two major experiment setups. One, a Matlab simulation of the virtual platform is prepared to investigate the

<sup>&</sup>lt;sup>1</sup> This contribution is a joint research work done in collaboration with Andrew Nelson who also covers this in his dissertation [75].

temporal behavior of CoMik in partitioning the processor tiles. Two, an FPGA prototype of the platform is used to study the composability property and support of multiple models of computation. For this, a number of use-cases consisting of real and synthetic applications execute on an MPSoC instance of the CompSOC platform.

### 1.4 Organization

In the rest of this dissertation, the solution is organized and presented according to Figure 1.2. Immediately after this introduction chapter, Chapter 2 gives an overview of the background information, starting with the definition of the predictability and the composability properties for embedded systems. Afterward, it introduces how these properties is implemented in the existing template of CompSOC architecture. The chapter provides also a detailed description of data- and time-driven models of computation.

Chapter 3 first motivates the virtualization technique as the solution for composability. Then it proposes partitioning techniques that can be used for virtualization. Finally, it described the details of CoMik software architecture.

Chapter 4 presents the model of execution and its implementation in the form of the CompOSe library. It details the complete structure of CompOSe software units and how an application can be implemented using this library.

Chapter 5 first proposes a response time analysis of time-driven applications to check for their schedulability on the CompSOC platform. Second, it demonstrates the predictability, the composability properties of our system, and the support of multiple models of computation by Matlab simulation and Field Programmable Gate Array (FPGA) emulation of the platform. It presents the empirical results of some real and synthetic application use-cases.

Chapter 6 concludes this dissertation with respect to the contributions introduced in the introduction chapter. It proposes several opportunities for future research work.

# CHAPTER **2**

# Background

HE I tas

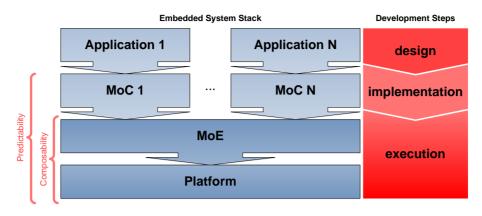

*HE* main objective of an embedded system is to carry out a set of algorithmic tasks realizing a number of applications. For this purpose, system developers have to follow three main steps. These steps are presented in Figure 2.1

together with their corresponding levels in an embedded system stack.

At the *design* step, the applications' tasks are expressed in high-level algorithms. At the *implementation* step, every application is then implemented using a model of computation. At the *execution* step the application is executed on the hardware/software platform. The *execution* step refers to two levels in the system stack: a model of execution and the execution platform. A model of execution fills the gap of execution abstraction between the model of computation's semantics and the primitive execution operations supported by the platform.

Nowadays, embedded applications have a time-criticality level, i.e., real-time or non real-time requirements. A mixed critical system therefore has applications with more than one criticality level. In case of real-time applications, the system has to ensure that the timing requirements of the applications are met. For this purpose, the system has to be designed in such a way that the timing characteristics of the system are so well defined that the temporal behavior of the applications can be verified against their requirements before actually executing on the platform. Resource sharing between applications with mixed time-criticality concurrently executing on a single platform causes interference between the applications. The interference may cause unpredictable (temporal) behavior of the applications. In order to prevent this, the applications have to execute temporally isolated.

*Predictability* and *composability* are two system properties that are proposed to deal with these challenges [85]. As depicted in Figure 2.1, predictability applies to the implementation and the execution steps. It therefore covers the model of computation, the model of execution and the platform layers of the system stack. Composability instead involves the layers that are shared between the applications, i.e., the model of execution and the platform layers.

In this chapter, we first define the predictability and the composability properties for an embedded system. Following that, starting from the bottom of the stack, we elaborate on the state-of-the-art approaches that are used to realize the predictability and

Figure 2.1: Predictability and composability properties of the embedded system stack layers.

the composability properties at each layer. The main contribution of this dissertation is in the model of execution layer, hence, it will be discussed separately in the later chapters.

# 2.1 Predictability

Predictability is a property of a system and is defined as a level of how well the timing characteristics of the system are defined and implemented so that the system temporal behavior is known before it actually starts running the applications [10]. In other words, a system is predictable if it is possible to derive a temporal-behavior model of the system so that the timing requirements of the running applications can be verified at design time [35].

A predictable temporal model can be either very detailed such that it corresponds to the actual case of the system, or less detailed such that provides a bounded worst-case behavioral model of the system [95]. In the detailed model, the temporal behavior of every resource of the system at each moment in time is known and therefore an exact execution trace of an application's temporal behavior can be derived from this model. Whereas in the bounded model, the worst-case temporal behavior of the system's resources can be extracted, and therefore, the worst-case temporal behavior, i.e., minimum throughput and maximum latency, of applications is known. In order to guarantee real-time requirements of applications executing on dedicated resources of a system, it is necessary and enough to come up with the worst-case behavioral model for all the components involved in execution of applications.

Predictability is a bottom-up property, meaning that it is not possible to have a predictable system developed on top of an unpredictable resource. Therefore, in the embedded system stack illustrated in Figure 2.1, every resource of the execution platform and the model of execution has to be predictable so that the temporal behavior of the applications implemented in the models of computation is predictable, as well.

Later, this chapter introduces the architecture of the predictable execution platform and the models of computation that are used to implement the applications with mixed temporal criticality.

# 2.2 Composability

To reduce the cost when a number of applications execute concurrently on a single platform, the resources are shared between the applications. Resource sharing causes temporal interference between the applications. In a mixed-criticality system, such interference might be either predictable or unpredictable. The predictable interference is typically between the real-time applications with the bounded temporal execution behaviors; whereas the unpredictable interference, as the number of concurrent execution combinations of the applications may grow exponentially, the verification and integration would become dramatically difficult [53]. In the case of unpredictable interference, it is not possible at all to verify the timing requirements of the real-time applications and therefore to integrate them with the non-real-time ones.

Composability is the property that the temporal (and functional) behavior of an application is isolated and independent from of other concurrent applications. A system is either *weakly* or *strongly* composable. Traditionally, weak composability is denoted as a relaxed isolation between applications, where with the help of predictability a system could make the worst-case temporal behavior of an application unaffected by the other applications [55]. This enables a compositional computation of worst-case bounds of the real-time applications. However, in the systems with mixed criticality applications the weak composability does not help to reduce the complexity of system verification and integration as whenever one of the applications changes or a new application has to be integrated with the existing ones, the overall process of verifying all the applications' timing requirements has to be repeated.

Recently, a stricter definition of composability, which is orthogonal to predictability, is proposed as *strong* composability [4, 26]. In this definition, the isolation between the applications is in such a way that the *actual-case temporal behavior* of each application is unaffected, i.e., the exact starting, finishing, and actual and worst-case timing properties of an application are *cycle-accurately* independent of the other applications. This enables independent design, verification, and integration of mixed-criticality applications. From now on, in this thesis, where we denote composability we mean such a strict definition.

Since composability is defined as an inter-application property, it only applies on the layers of the system stack that deal with shared resources between the applications. These are the model of execution and the platform layers in Figure 2.1. The layers have to implement the resources or manages the access of the applications to resources such that the temporal isolation between the applications are guaranteed at cycle-level. The technology to implement composability differs per resource type. Later, this chapter introduces how the composability is implemented in the existing architecture of the execution platform.

# 2.3 Hardware Platform Architecture

Shrinking the feature size of the transistors has led to low-cost integration of more and more number of processing resources on a single chip and consequently allows designing

complex chip multiprocessor architectures [44]. However, since the requirements of applications grow ever faster, these architectures are still resource constrained. For cost reasons, the applications executing on these platforms have to share some resources, such as processors, interconnect, memory blocks, etc.

In order to guarantee predictable and composable execution of applications with mixed time-criticality, each resource has to be specifically designed and implemented for this purpose. CompSOC is a system-on-chip template developed following composability and predictability paradigm [29]. In the rest of this section we are going to describe the CompSOC hardware architecture as the platform layer of the system stack depicted in Figure 2.1. All the other layers are developed on top of the CompSOC architecture.

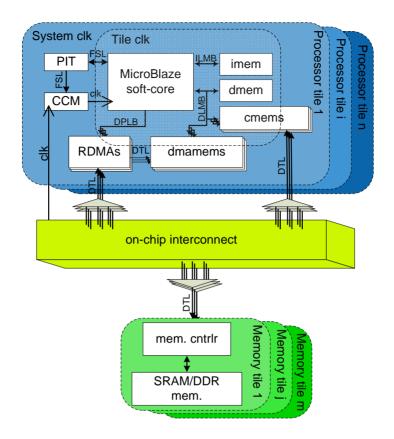

### 2.3.1 CompSOC: A Composable & Predictable System-on-Chip Platform

The CompSOC template implements a tile-based multi-processor architecture which consists of a number of processor and memory tiles communicating via an on-chip interconnect, as depicted in Figure 2.2. Multiple applications may run on each processor tile and the communicating tasks of one application may be mapped onto multiple processor tiles. Thus, the processor tiles, the interconnect, and the memory tiles are possibly shared between and within the applications. *All these resources have to be designed and arbitrated in such a way that they realize predictable and composable execution of applications*. In the rest of this section, we are doing to describe the detailed architecture properties of these resources.

### Processor Tile

A processor tile consists of a processing core, a data and an instruction memory, a number of communication memory blocks, a Programmable Interrupt Timer (PIT), a Clock Control Module (CCM), and a number of Remote Direct Memory Access (RDMA) modules each of which is equipped with a dedicated memory block.

The processing core is a MicroBlaze [101] embedded soft core which is highly configurable for some specific set of features that are necessary for the purpose of predictability and composability. The Microblaze is a 32-bit Reduced Instruction Set Computer (RISC) architecture, optimized to be implemented on Xilinx Field Programmable Gate Arrays (FPGAs) [100]. The processor can be configured for either three or five stage instruction pipelining.

In the CompSOC platform, the instruction cache is disabled to remove the interdependency between the applications due to cache misses/hits. The instruction code of the applications are therefore stored locally in an instruction memory (*imem* in Figure 2.2), which is single-cycle accessible via the Instruction Local Memory Bus (ILMB). Ideally private data of an executing application on a tile should also reside in the local data memory (*dmem* in Figure 2.2) of the tile to minimize the data access latency. However, practically an embedded application has to transfer data to/from other tile's memory locations (when part of the application is mapped and executed on another tile), to/from off-tile memory blocks such as Double Data Rate (DDR) Synchronous Dynamic Random-Access

Figure 2.2: The existing hardware architecture of the CompSOC platform.

Memory (SDRAM), or Memory-Mapped Input/Outputs (MMIOs). For this purpose, the application initiates data read/write transactions over the interconnect.

When the processor directly performs such a data transfer over the interconnect, it blocks until the transaction finishes. As the size of data being transferred may be variable (or even infinite, for example in case of continuously streaming in/out data), the blocking time is not known a priori. It is even worse when the processor executes a misbehaving application: the processor may be blocked indefinitely. This compromises the composability of the system when multiple applications execute concurrently on the processor.

For such off-tile communication, RDMA modules, each of which is associated with a memory block, denoted as *dmamem* in Figure 2.2, are used. Every RDMA is assigned to one application and can be programmed by the processor via the Data Processor Local Bus (DPLB) to transfer data (with the granularity of 1 to 64 words) from/to a location in its associated *dmamem* to/from another memory-mapped location through the interconnect, e.g., remote memory of other tiles. After being programmed, each RDMA performs off-tile communication independently of the application executing on the processor, and its status may be read by the application to check if the transaction is done.

Furthermore, other tiles in the system can use MMIO to transfer data to/from the tile through communication memory blocks, denoted as *cmems* in Figure 2.2. These dual port memories, from one side, are locally accessed by the processor via the Data Local Memory Bus (DLMB) as scratchpad memories, and from the other side, they interface with the interconnect via a Device Transaction Language (DTL) bus [80].

Traditionally, to protect against unwanted memory accesses by a running application, a Memory Management Unit (MMU) accompanies the processor. For the CompSOC platform, a predictable and composable MMU is proposed in [64]. Due to a large cost of this scheme, the module is not regularly instantiated in the platform. For stack protection, however, the Microblaze has an internal feature which is always enabled in the CompSOC platform. In the next chapter, we present how this feature is used by the software architecture.

The PIT, which is programmable from the processor via a Fast Serial Link (FSL), is used for two purposes: (1) to keep track of the time, and (2) to generate an interrupt at a given moment in time. The first one is necessary for performance monitoring of real-time applications. The latter is essential for implementing timed-event based functionality in the system. Keeping such basic functionality of the PIT, in this thesis, we later replace this component with a more advanced module, namely Timer-centric Interrupt and Frequency Unit (TIFU).

Every processor tile can run on a different clock frequency, for example, for the purpose of power management [76]. In an FPGA prototype of the CompSOC platform, this is emulated by the CCM which can divide the system clock frequency and provide the tile clock. To perform such clock division, the CCM has to be tightly coupled with the PIT. This technology leads to having two clock domains in every tile, as illustrated in Figure 2.2, with the tile clock and the system clock.

### Memory Tile

The memory tile consists of a front-end memory controller and a back-end memory technology which can be a SRAM and/or DDR. The memory controller arbitrates between the number of requester connections that want to access the back-end memory in such a way that the accesses are predictable and composable [3]. The details are out of scope of this dissertation, and for further information we refer to the literature [2].

#### **On-Chip Interconnect**

The interconnect consists of traditional bus technology and the Æthereal Network-On-Chip (NOC) architecture [22, 27, 31, 89]. A connection over this interconnect is recognized as a request channel from a master port to a slave port, and a response channel from a slave port to a master port. A master port may have a connection to multiple slaves, and multiple masters may also have connections to a single slave. In these cases, a master-bus at the master side and a slave-bus at the slave side are used to de-multiplex and multiplex the connections, respectively.

The basic building blocks of the NOC are *Network Interfaces (NIs)* and *routers*. The topology of Æthereal is arbitrary, where more than one NI may connect to a router. The