# M.Sc. Thesis

# Scalable Network Based Clock Synchronization for Digital PET System

## Martijn Bijwaard B.Sc.

#### Abstract

Typically in synchronous digital systems time-based tasks are synchronized using hard-wired clock distribution networks. However in the growing application of large (wireless) sensor networks it is not always feasible to connect each sensor node to a hard-wired clock distribution network. Generally in such systems the sensor nodes are only connected via a (wireless) communication network, hence there have been implementations where clocks are synchronized via the network nodes, in general these solutions synchronize the network nodes in the range of milliseconds up to microseconds. Though some applications, like SPADnet, demand a network based clock synchronization in the range of picoseconds.

Currently the SPADnet system is equipped with a hard-wired clock distribution network, this clock network does not scale well. Since one of the goals of SPADnet is to create a scalable system, a network based clock synchronization solution is a better alternative.

In this thesis a hybrid solution is presented, where a hard-wired clock synchronization network is combined with a network based clock offset estimator. This combination enables scalability while maintaining high precision. A novel least squares synchronization algorithm is optimized and implemented in hardware equipped with a delayline FPGA TDC, allowing picosecond clock synchronization.

# Scalable Network Based Clock Synchronization for Digital PET System a picosecond hardware implementation for SPADnet

THESIS

submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

Embedded Systems

by

Martijn Bijwaard B.Sc. born in Assendelft, The Netherlands

This work was performed in:

Circuits and Systems Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

Copyright  $\bigodot$  2015 Circuits and Systems Group All rights reserved.

## Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "Scalable Network Based Clock Synchronization for Digital PET System" by Martijn Bijwaard B.Sc. in partial fulfillment of the requirements for the degree of Master of Science.

Dated: 13-03-2015

Chairman:

prof.dr.ir. E. Charbon

Advisor:

ir. C. Veerappan

Committee Members:

prof.dr.ir G. Leus

dr. ir. S. Wong

# Abstract

Typically in synchronous digital systems time-based tasks are synchronized using hardwired clock distribution networks. However in the growing application of large (wireless) sensor networks it is not always feasible to connect each sensor node to a hard-wired clock distribution network. Generally in such systems the sensor nodes are only connected via a (wireless) communication network, hence there have been implementations where clocks are synchronized via the network nodes, in general these solutions synchronize the network nodes in the range of milliseconds up to microseconds. Though some applications, like SPADnet, demand a network based clock synchronization in the range of picoseconds.

Currently the SPADnet system is equipped with a hard-wired clock distribution network, this clock network does not scale well. Since one of the goals of SPADnet is to create a scalable system, a network based clock synchronization solution is a better alternative.

In this thesis a hybrid solution is presented, where a hard-wired clock synchronization network is combined with a network based clock offset estimator. This combination enables scalability while maintaining high precision. A novel least squares synchronization algorithm is optimized and implemented in hardware equipped with a delayline FPGA TDC, allowing picosecond clock synchronization.

# Acknowledgements

I am using this opportunity to express my gratitude to everyone who supported me throughout the course of this Master thesis project. Especially I would like to thank Edoardo Charbon for providing me the chance to work on this fascinating project, and Chockalingam Veerappan for his daily guidance throughout this thesis.

Also I want to thank the members of the Circuits and Systems group for inviting me to join the group activities, which I really enjoyed.

Finally I would like to thank my parents, brother and girlfriend for their support during my complete master study.

Martijn Bijwaard B.Sc. Delft, The Netherlands 13-03-2015

# Contents

| $\mathbf{A}$ | bstra                                          | nct                                                                                                                                                                                                                                                                                                                                                     | v                                                                                                                                                                               |

|--------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A            | cknov                                          | wledgements                                                                                                                                                                                                                                                                                                                                             | vii                                                                                                                                                                             |

| 1            | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4        | coduction         Motivation                                                                                                                                                                                                                                                                                                                            | <b>1</b><br>1<br>1<br>2<br>3<br>3                                                                                                                                               |

| 2            | 1.5<br>Clo<br>2.1                              | Positron emission tomography                                                                                                                                                                                                                                                                                                                            | 3<br>5<br>5<br>5<br>6                                                                                                                                                           |

|              | 2.2                                            | 2.1.3       Long-term clock stability         Clock synthesizer model                                                                                                                                                                                                                                                                                   | 7<br>8                                                                                                                                                                          |

| 3            | Clo<br>3.1<br>3.2<br>3.3                       | ck synchronizationHard-wired clock distributionNetwork based clock synchronization3.2.1Timestamp exchange protocolsClock synchronization algorithms3.3.1Least squares3.3.2Pairwise least squares3.3.3Global least squares3.3.4Asymmetrical time-stamping and passive listening3.3.5Performance3.3.6Cramer-Rao lower bound3.3.7Complexity3.3.8Conclusion | <ol> <li>9</li> <li>9</li> <li>9</li> <li>10</li> <li>11</li> <li>12</li> <li>12</li> <li>13</li> <li>15</li> <li>16</li> <li>16</li> <li>16</li> <li>17</li> <li>17</li> </ol> |

| 4            | <b>SP</b> <i>A</i><br>4.1<br>4.2<br>4.3<br>4.4 | ADnet system         Sensor tile         Data processing communication unit         Network architecture         SPADnet system clock synthesizers         4.4.1         LMK04906         Ultra low noise clock jitter cleaner         4.4.2         ICS8534-01:         1-to-22         fanout buffer                                                  | <ol> <li>19</li> <li>19</li> <li>20</li> <li>22</li> <li>22</li> <li>23</li> </ol>                                                                                              |

| <b>5</b> | Har | d-wired clock distribution networks 25                                                                                                                       |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1 | Distribution topography                                                                                                                                      |

|          |     | 5.1.1 Ring clock distribution network                                                                                                                        |

|          |     | 5.1.2 Star clock distribution network                                                                                                                        |

|          | 5.2 | Characterization                                                                                                                                             |

|          |     | 5.2.1 Jitter                                                                                                                                                 |

|          |     | 5.2.2 Multi node jitter                                                                                                                                      |

|          |     | 5.2.3 Phase difference star distributed clock network                                                                                                        |

|          |     | 5.2.4 Phase difference ring distributed clock network                                                                                                        |

|          | 5.3 | Conclusion   31                                                                                                                                              |

|          | 0.0 | 5.3.1 Ring network                                                                                                                                           |

|          |     | 5.3.2 Star network                                                                                                                                           |

|          |     | 5.5.2 Star hetwork                                                                                                                                           |

| 6        | SPA | ADnet solution 33                                                                                                                                            |

| U        | 6.1 | Allan variance measurement   33                                                                                                                              |

|          | 6.2 | Hybrid clock synchronization solution                                                                                                                        |

|          | 6.3 | Phase synchronization protocol                                                                                                                               |

|          | 0.5 | 6.3.1         Broadcasting         37           37                                                                                                           |

|          |     | 0.5.1 Dioadcasting                                                                                                                                           |

| 7        | Har | dware implementation 39                                                                                                                                      |

| •        | 7.1 | Phase estimator   39                                                                                                                                         |

|          | 1.1 | 7.1.1 Hardware implementation                                                                                                                                |

|          |     | 7.1.1       Hardware implementation       40         7.1.2       Coarse timer overflow       41                                                              |

|          |     | 7.1.2         Coarse timer overnow         41           7.1.3         Simulation results         43                                                          |

|          | 7.2 |                                                                                                                                                              |

|          | 1.2 | 0 1                                                                                                                                                          |

|          |     |                                                                                                                                                              |

|          |     |                                                                                                                                                              |

|          | 7.0 | 7.2.3 FPGA TDC implementation $\dots \dots \dots$            |

|          | 7.3 | Time synchronization module                                                                                                                                  |

|          |     | 7.3.1 Hardware implementation, normal node                                                                                                                   |

|          |     | 7.3.2 Hardware implementation, reference node                                                                                                                |

| 0        | Vor | ification 53                                                                                                                                                 |

| 0        |     |                                                                                                                                                              |

|          | 8.1 | Phase estimator stability $\dots \dots \dots$                |

|          | 8.2 | Resolution (LSB)                                                                                                                                             |

|          | 8.3 | Scalability study                                                                                                                                            |

|          | 8.4 | Hybrid synchronization versus hard-wired synchronization 59                                                                                                  |

| 9        | Car | clusion 61                                                                                                                                                   |

| 9        |     |                                                                                                                                                              |

|          | 9.1 | J                                                                                                                                                            |

|          |     | 9.1.1 Characterization of hard-wired clock distribution networks 61                                                                                          |

|          |     | 9.1.2 Network based clock synchronization                                                                                                                    |

|          | 0.0 | 9.1.3 Hybrid solution $\ldots \ldots \ldots$ |

|          | 9.2 | Future work                                                                                                                                                  |

|          |     |                                                                                                                                                              |

# 10 List of my Publications

69

| $\mathbf{A}$ | Veri | log Phase Estimator         | 71 |

|--------------|------|-----------------------------|----|

|              | A.1  | Verilog source              | 71 |

|              | A.2  | Synthesis report            | 72 |

| в            | Aur  | ora 8B/10B                  | 73 |

|              | B.1  | 8B/10B encoding             | 73 |

|              | B.2  | GTP transceivers            | 73 |

|              | B.3  | Clock correction            | 74 |

|              | B.4  | Deterministic communication | 74 |

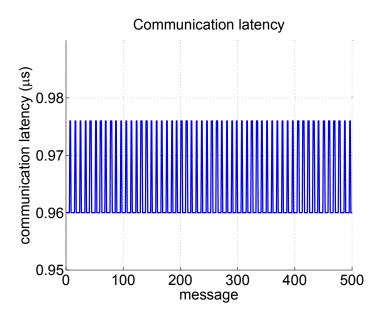

|              | B.5  | Communication latency       | 76 |

| 1.1<br>1.2<br>1.3                                                                                                               | SPADnet system                                                                | 3<br>4<br>4                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2$                                                                                                                    | Comparison of ideal clock versus a real clock                                 | $5 \\ 6$                                                                                       |

| <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> </ul> | Example of typical hard wired clock distribution networks for digital systems | 9<br>10<br>11<br>11<br>13<br>14<br>15<br>15                                                    |

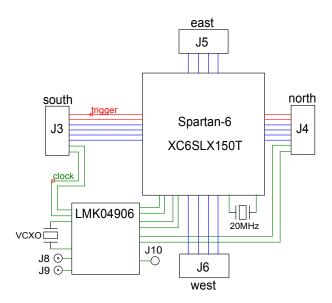

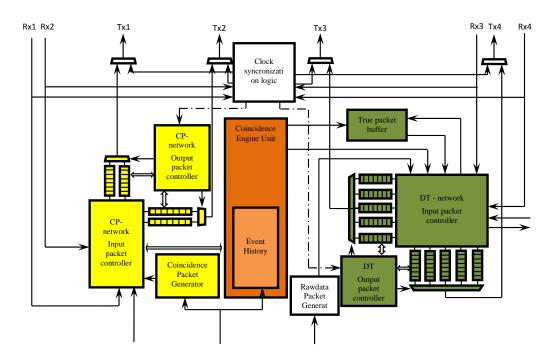

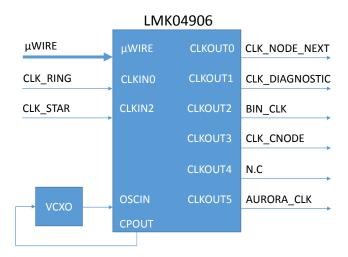

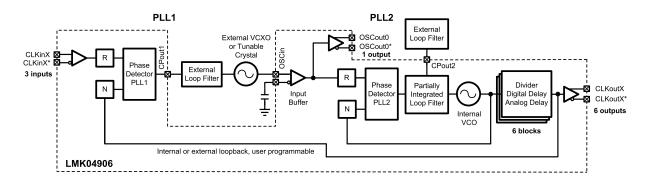

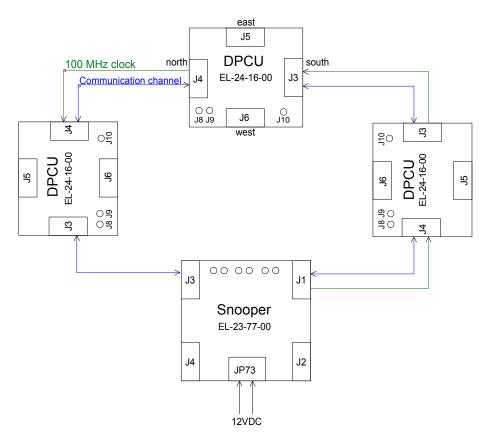

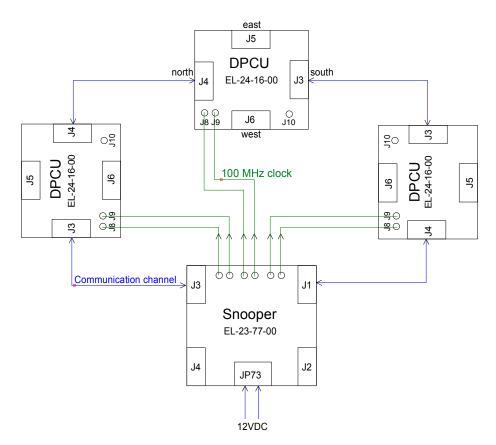

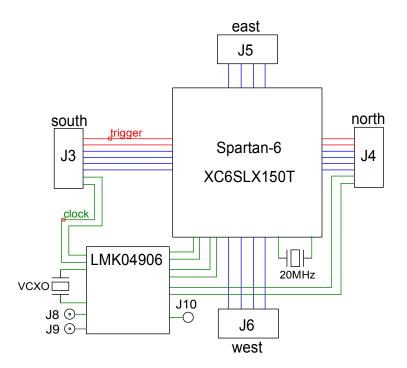

| $ \begin{array}{r} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ \end{array} $                                                      | nite clock resolution                                                         | <ol> <li>16</li> <li>19</li> <li>20</li> <li>20</li> <li>21</li> <li>22</li> <li>23</li> </ol> |

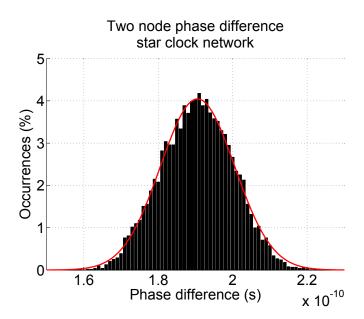

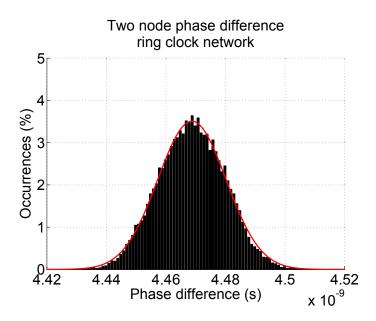

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                                                                                      | Clock distribution network: ring topography                                   | 26<br>27<br>28<br>29                                                                           |

| 5.5        | Phase difference between two adjacent nodes, using the star distributed clock network.                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.6        | Phase difference between two adjacent nodes, using the ring distributed clock network.                                                                                                                                                                            |

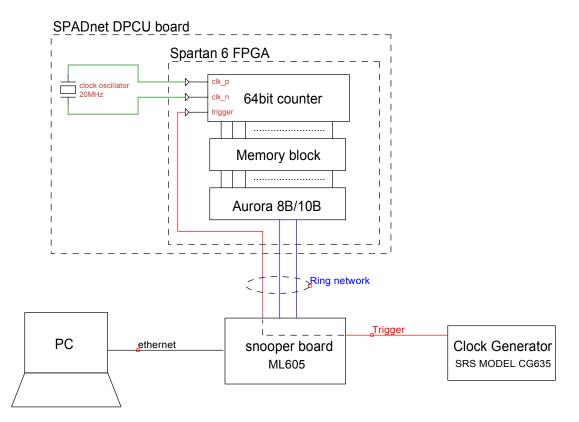

| 6.1        | Hardware setup used to perform the Allan variance measurement                                                                                                                                                                                                     |

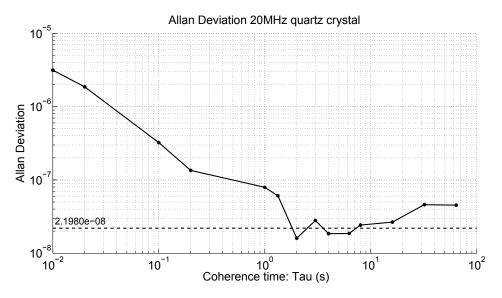

| 6.2        | Result of the Allan variance measurement                                                                                                                                                                                                                          |

| 6.3        | Clock distribution network: Ring topography. The phase of the clock<br>will be different at each node, because of the distribution network. The<br>phase will be estimated using pairwise least squares                                                           |

| 6.4        | Final two-way timestamp exchange protocol                                                                                                                                                                                                                         |

| 6.5        | Two-way packet construction                                                                                                                                                                                                                                       |

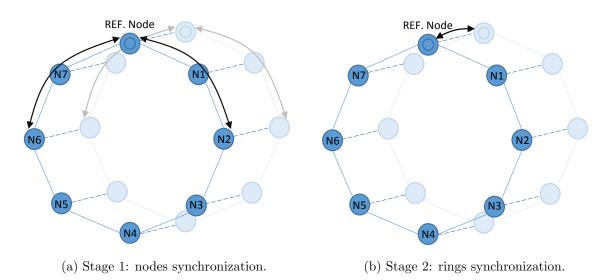

| 6.6        | Stages of the synchronization protocol                                                                                                                                                                                                                            |

| 6.7        | The use of broadcast messages to obtain timestamps. The reference node broadcasts a message to all nodes, while the individual nodes reply to the broadcast, while recording the transmission and reception times                                                 |

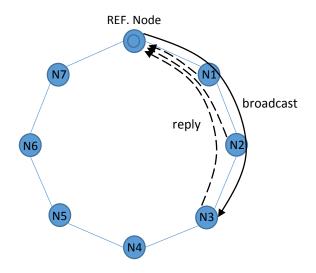

| 7.1        | Two-way timestamp exchange protocol, with node $i = 1$ and node $j = 2$ .                                                                                                                                                                                         |

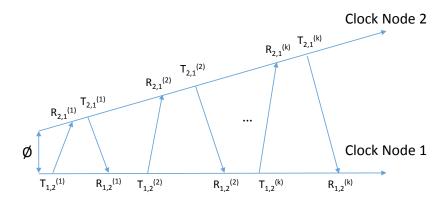

| 7.2        | Verification of the fixed point phase estimator implementation, using ISim and Matlab.                                                                                                                                                                            |

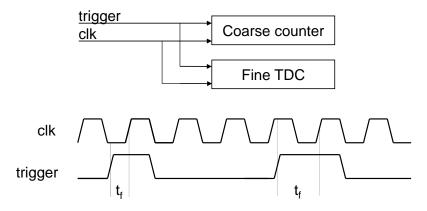

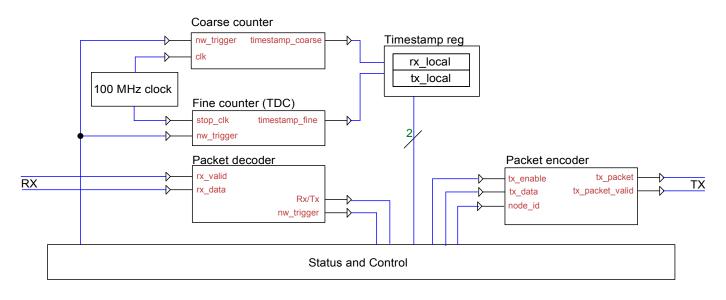

| 7.3        | Combination of the fine delayline TDC and coarse counter                                                                                                                                                                                                          |

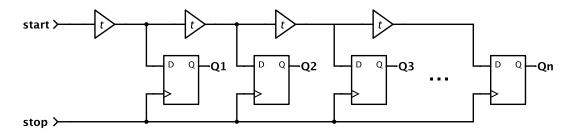

| 7.4        | General single delayline time-to-digital converter. In the case of the FPGA TDC the delay elements are carry units.                                                                                                                                               |

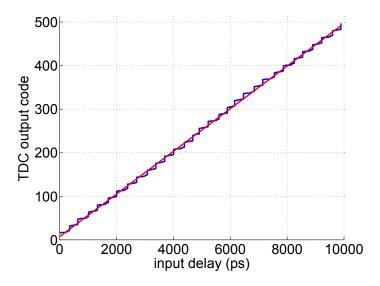

| 7.5        | Timing simulation of the FPGA TDC                                                                                                                                                                                                                                 |

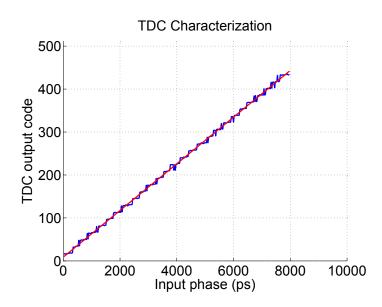

| 7.6<br>7.7 | transfer function of the implemented FPGA TDC Floor plan of the TDC, between every 16 slices there is a gap. In the middle of the 16 slices there is a clock domain crossing. These gaps and crossings introduce delays, affecting the non-linearities of the TDC |

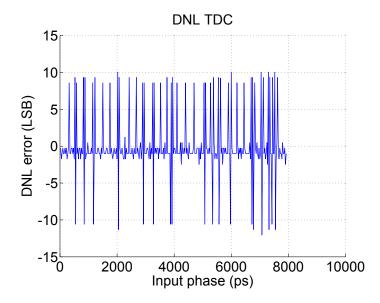

| 7.8        | Differential non-linearity of the implemented TDC.                                                                                                                                                                                                                |

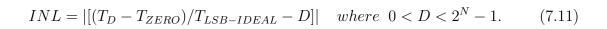

| 7.9        | Integral non-linearity of the implemented TDC.                                                                                                                                                                                                                    |

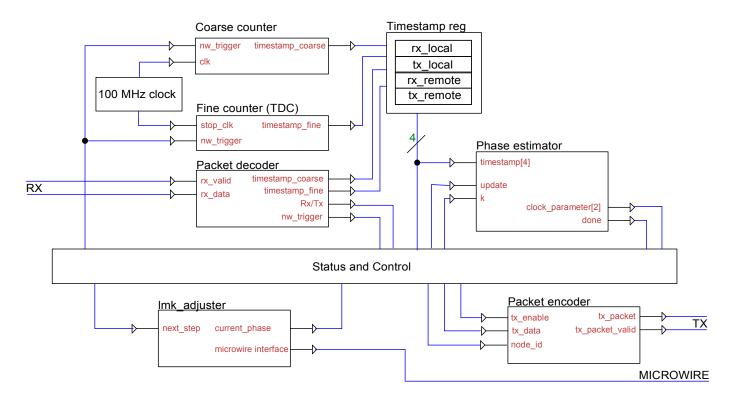

| 7.10       | Simplified architecture of the normal node                                                                                                                                                                                                                        |

| 7.11       | Simplified architecture of the reference node                                                                                                                                                                                                                     |

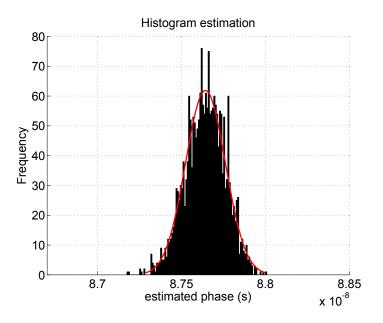

| 8.1        | 2000 Executions of the hardware implemented phase estimation, 4096 two-way timestamp exchanges, 328 ms observation window, 124 ps stan-                                                                                                                           |

|            | dard deviation. For a fixed phase between two adjacent nodes                                                                                                                                                                                                      |

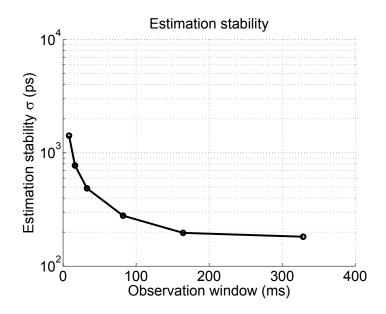

| 8.2        | Estimation stability, standard deviation, of 2000 estimations. For fixed                                                                                                                                                                                          |

|            | k = 2048 two-way messages, and increasing observation window $(8 - 328$ ms).                                                                                                                                                                                      |

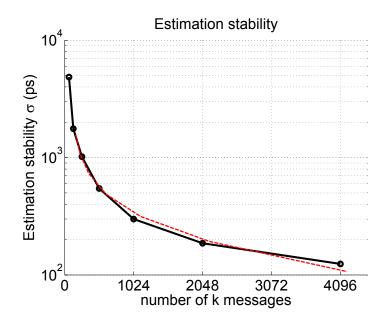

| 8.3        | Estimation stability, standard deviation, of 2000 estimations. With increasing $k$ two-way messages and fixed communication interval of 40 microseconds.                                                                                                          |

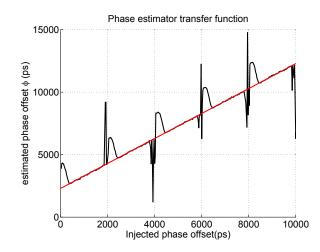

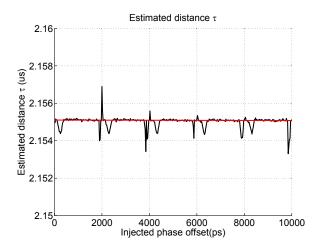

| 8.4        | Transfer function of the phase estimator                                                                                                                                                                                                                          |

| 8.5        | Transfer function of the estimated distance.                                                                                                                                                                                                                      |

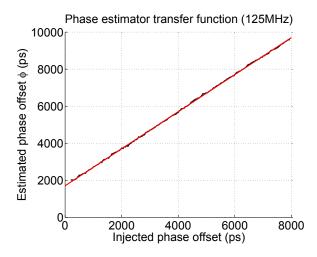

| 8.6 | Transfer function of the phase estimator, showing the average of 25 es- |    |

|-----|-------------------------------------------------------------------------|----|

|     | timations per injected phase offset. Using $k = 4096$ two-way timestamp |    |

|     | exchanges over a observation window of 328 ms                           | 57 |

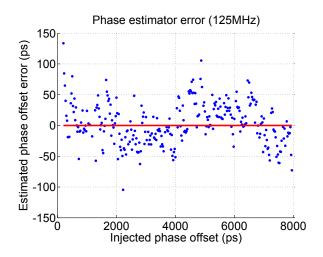

| 8.7 | Estimation error compared to ideal transfer function. Presenting the    |    |

|     | average of 25 estimations per injected phase offset. Using $k = 4096$   |    |

|     | two-way timestamp exchanges over a observation window of 328 ms         | 57 |

| 8.8 | Three node ring system                                                  | 58 |

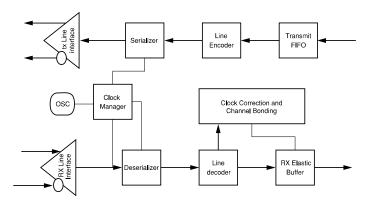

| B.1 | Generic block diagram of a SERDES                                       | 73 |

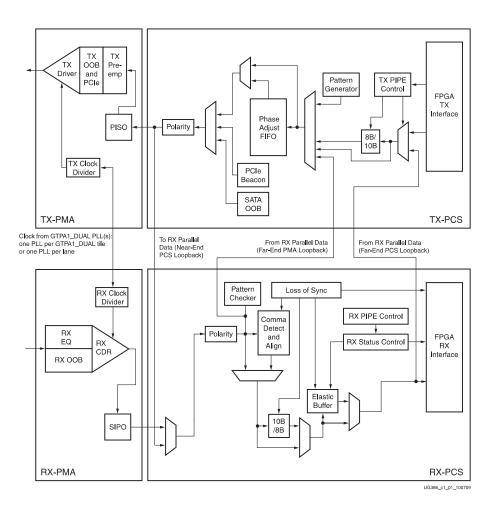

| B.2 | Simplified Spartan-6 FPGA GTP transceiver block diagram                 | 75 |

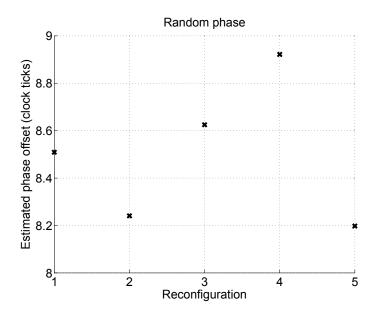

| B.3 | After reconfiguring the FGPA a non-deterministic phase is introduced    |    |

|     | in the GTP transceiver. This random phase can be corrected by using     |    |

|     | the GTP transceivers dedicated phase-alignment circuits.                | 76 |

| B.4 | Communication latency between two adjacent nodes, using a 2.5 GB/s      |    |

|     | Aurora 8b/10b network link                                              | 77 |

# List of Tables

| 3.1                                           | Operation sizes of each least squares operation. With $K$ number of messages, $K' = K_1 + K_2 + K_N$ , $L = 2N + M - 2$ , $M$ the number of unique links in the network and with $N$ nodes                                                                                                                                                                                                                       | 17       |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1                                           | Specifications SPADnet system clock synthesizers                                                                                                                                                                                                                                                                                                                                                                 | 22       |

| $5.1 \\ 5.2$                                  | Jitter measurement in a four node ring system                                                                                                                                                                                                                                                                                                                                                                    | 29<br>31 |

| 6.1                                           | Alternative stable clock oscillators. Obtained from [23]                                                                                                                                                                                                                                                                                                                                                         | 34       |

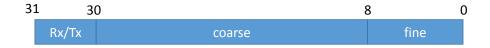

| <ul><li>7.1</li><li>7.2</li><li>7.2</li></ul> | Two-way timestamp exchange, the transmission and reception times are<br>marked using a 22 bit 100 MHz counter. Overflowing of the counter<br>sometimes needs to be corrected, as we can see from the results of the<br>first steps of the algorithm                                                                                                                                                              | 41<br>42 |

| 7.3                                           | Corrected timestamps, using the overflow correction                                                                                                                                                                                                                                                                                                                                                              | 42       |

| 8.1                                           | Phase estimation in a three node network for five different injected phase offsets. Results are obtained from about 2000 estimations per injected phase offset, with 2048 two-way timestamp exchanges over an observation window of 165 ms. ABS: absolute, SD: standard deviation. The injected phase does not match the estimated phase due to the error discussed in Section 8.2, this fault has been resolved | 58<br>59 |

| 9.1                                           | Comparison of the hybrid solution versus the hard-wired clock synchro-                                                                                                                                                                                                                                                                                                                                           | 60       |

|                                               | nization solution.                                                                                                                                                                                                                                                                                                                                                                                               | 62       |

# 1

# 1.1 Motivation

In systems like wireless sensor networks (WSN) [1], SPADnet [2] and OLFAR [3] clock synchronization is of great importance. In these systems time-based tasks for instance: data sampling, time-stamping of data, data fusion, sleep and wake-up coordination and synchronized communication, requires that the clocks of each individual node are synchronized. Typically in synchronous digital systems the clock is distributed via a hard-wired clock distribution network to each component. But in (wireless) network based systems, it is not always feasible to connect each node to a hard-wired clock distribution network. In these systems each node will operate on their own local clock. However, to perform time-based tasks, the clocks of these nodes require to be synchronized [4]. The only way to do so is to synchronize via the network. Implementations exist for network based synchronization, in general these solutions synchronize the network nodes in the range of milliseconds up to microseconds [5] [6] [7] [8].

This thesis focusses on the SPADnet system [2]. This system uses a network of modules for photon-starved biomedical applications, such as positron emission tomography (PET). Each module relies on a hard-wired clock distribution network, driven by a single clock oscillator, to allow the execution of time-based tasks. One of the main goals of SPADnet is to construct a scalable system. Since the hard-wired clock distribution is not scalable, this thesis investigates if the SPADnet clock distribution network can be made scalable using network based approach.

#### 1.1.1 SPADnet requirements

The requirements for the clock synchronization depends on the configuration of SPADnet. Three types of PET configurations exist: pre-clinical, brain and clinical. In timeof-flight brain and clinical systems clock synchronization better than 50 ps is required. For pre-clinical systems that do not use time-of-flight information, clock synchronization around 500 ps is sufficient.

#### 1.1.2 Thesis goals

The goal of this thesis is to answer the following questions:

- 1. What is the performance of the hard-wired clock network of SPADnet?

- 2. Can a network based solution improve the scalability of SPADnet?

# 1.2 Contribution

The thesis presents a survey on various clock synchronization techniques (hard-wired and network based) for SPADnet. The existing hard-wired clock distribution network is characterized. Then it is investigated if network based clock synchronization can improve the scalability of SPADnet. For this the performance of novel clock synchronization techniques are examined, and a study is done on how to apply these techniques to SPADnet.

A hybrid clock synchronization solution is invented and implemented in a field programmable gate array (FPGA). This solution combines a hard-wired clock distribution circuit with a network based phase estimator, enabling scalability while maintaining picosecond performance. The performance of this hybrid solution is compared to the existing hard-wired clock distribution network of SPADnet, and tested in a three node system.

Although this thesis focusses on the SPADnet system, the findings can be used as a guideline for other systems as well.

The main contributions of this thesis are:

- 1. Characterization of the hard-wired clock distribution network of SPADnet.

- 2. Survey on network based clock synchronization techniques.

- 3. Implementation and verification of a hybrid synchronization solution.

- 4. Comparative study on hard-wired versus network based clock synchronization solution for SPADnet.

## 1.3 Related work

Probably the most used network based time synchronization protocol is the network time protocol (NTP) [9]. NTP is an internet protocol that synchronizes computers to within a few milliseconds of coordinated universal time (UTC). NTP is based on measuring the round-trip delay between the client and, preferably multiple, time-servers.

The growing interest of collecting physical and environmental data on a large scale using Wireless Sensor Networks (WSN), demands network based clock synchronization. Without synchronized sensor modules, time-stamping of data, data fusion, sleep and wake-up coordination and synchronized communication would fail. Multiple solutions for synchronization in WSN are available [5] [6] [7] [8]. In general these solutions synchronize the clocks in the range of milliseconds up to microseconds.

However some applications, for example SPADnet, demand more precise synchronization of the clocks. One of the most novel clock synchronization algorithms are presented in [10] and [11]. It is stated that these solutions approach the theoretical limits of clock synchronization. This thesis will investigate if they are applicable for SPADnet.

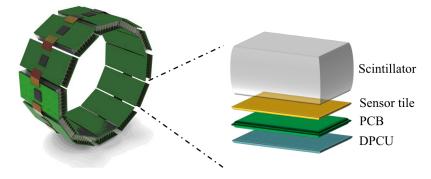

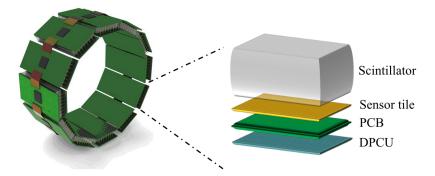

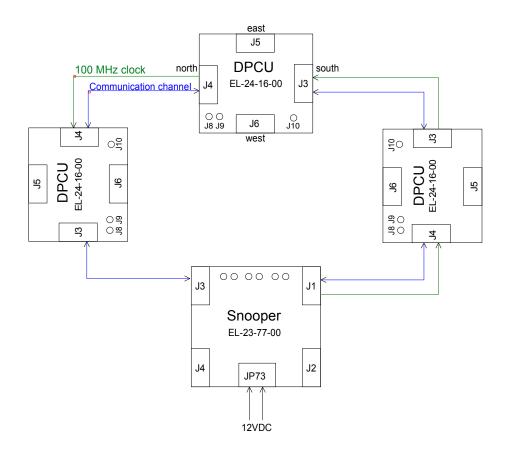

### 1.4 Application: SPADnet

The SPADnet FP7 European project aims to develop a new generation of smart, large area networked image sensors, based on a conventional CMOS fabrication technology, for photon-starved biomedical applications. SPADnet will build ring-assembly modules for positron emission tomography (PET) medical imaging, and carry out performance tests in a PET system evaluation test bed [2].

Figure 1.1: SPADnet system

## 1.5 Positron emission tomography

PET is a technique to create a three dimensional image of functional processes in the body. The patient is injected with a positron-emitting radionuclide on a biologically active molecule, also called a tracer. There are different kinds of biologically active molecules that can be used for different tissue of interest. For PET fludeoxyglucose (FDG) is commonly used as an active molecule, FDG marks certain types of tissues metabolism for example: heart, lungs, brain and tumours.

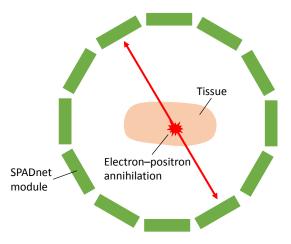

Figure 1.2: Annihilation of electron-positron pair, detected by the SPADnet modules

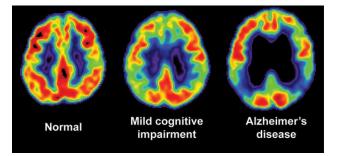

When the emitted positron of radionuclide collides with an electron, the two particles annihilate, the resulting energy is converted in to a pair of gamma rays. The gamma rays can be detected by the SPADnet modules. The pair of gamma rays are emitted back-to-back, using this property and time information of the detections, the origin of the annihilation can be determined. By recovering many events a three dimensional image can be reconstructed. The resolved image will only show the regions marked by the radionuclide. An example of an image recovered with PET of a human brain is shown in Figure 1.3.

Figure 1.3: Example of functional neuroimaging, showing transaxial slice of the human brain recovered with PET. Blue regions indicate low accumulated tracer, red regions indicate show higher accumulated tracer. The tracer marks the active sections of the brain.

The characteristics of the applied clock synthesizers are important factors for the eventual performance of the network based synchronization algorithm. The most important characteristic is the clock synthesizer stability. The stability will limit the maximum achievable synchronization resolution and the interval rate, at which the synchronization needs to be performed.

In this chapter the characteristics of quartz clock synthesizers are investigated. And a clock model is presented, that expresses the clock correction parameters.

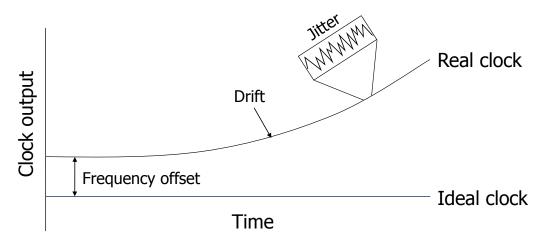

## 2.1 Clock synthesizer imperfections

Ideally the output of a clock synthesizer would not change over time, and has the exact required frequency. Unfortunately, real clock synthesizers have phase output errors [12]. Clock synthesizers will not generate the exact specified frequency, and over time this frequency will drift. Besides drift, clock synthesizers suffer stationary noise on the frequency, know as jitter.

Figure 2.1: Comparison of ideal clock versus a real clock.

#### 2.1.1 Quartz clock synthesizers

Quartz clock synthesizers are the most commonly used clock synthesizer, because of their low-cost and small size[13]. The SPADnet system also utilizes quartz oscillators.

Typically, a quartz clock synthesizer has an output frequency tolerance of 5-100 ppm. A quartz clock of 1 MHz with a frequency tolerance of 10 ppm, has an output frequency error of at most 10 Hz. The error in output frequency is the result of imperfections in the clock synthesizer.

The clock synthesizer frequency is also influenced by changes in environmental conditions. Clocks are affected by temperature, pressure, mechanical stress and humidity [14]. Typical quartz clock synthesizer frequency outputs change 20-100 ppm over 40 to +85 °C. There exist solutions to compensate for temperature changes, two examples are: temperature compensated crystal oscillators (TCXO) and oven controlled crystal oscillators (OCXO). TCXO includes a temperature compensation circuit, and corrects to about 1 ppm error over the operating temperature range. OCXO oscillators are oscillators placed in temperature controlled chambers and achieve a temperature stability of 50-500 ppb over -55 to +85 °C. The influences of the pressure, mechanical stress and humidity are controlled by packaging and the manufacturing process of the crystal oscillator.

Crystal oscillators undergo a slow gradual change of the frequency with time, known as ageing. This ageing process originates from small and slow changes of the physical aspects of the quartz crystal. Over time the ageing effect slowly decreases, for example the ageing effects in the first life year can be  $\pm$  3 ppm and the drift over 15 years life time a total  $\pm$  10 ppm.

Note that changes in the power supply, load, and other electrical interference will have an influence on the oscillator output.

#### 2.1.2 Short-term clock stability

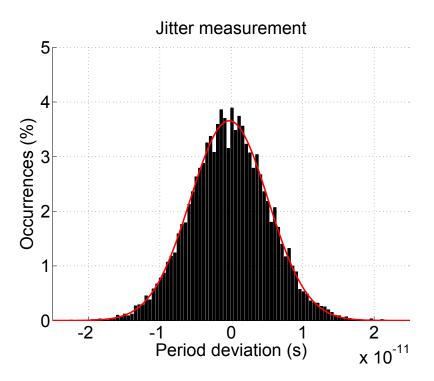

Besides the error introduced by ageing and environmental conditions on the output frequency, oscillators suffer from short-term variations of their signal, this is called jitter. Jitter comprises of two primary components: random jitter and deterministic jitter.

Random jitter is directly related to phase noise, the aggregate result of stochastic noise processes (thermal, shot and flicker noise). Random jitter typically shows a Gaussian distribution and can be quantified by its standard deviation (rms) value [15].

Deterministic jitter behaves predictably and repeatedly. The sources are generally related to imperfections in the behaviour of the device, transmission media, power supply noise and cross-talk. The range of the maximum phase deviations of this type of jitter can be bounded and expressed as a peak-to-peak value.

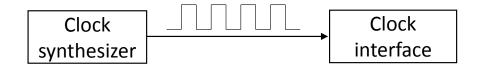

Not only the oscillator introduces jitter on the clock, but the clock interface also introduces phase noise. The analog clock signal is converted to digital by the clock interface. This clock interface does this by checking if the input signal is above or below a threshold value. Fluctuations in this threshold value, adds noise to the digital clock. The fluctuations are mainly induced by temperature and power supply instabilities. In this thesis it is assumed that this noise is random and has a zero mean.

Figure 2.2: A complete clock system.

There are three commonly used methodologies for the measurement of different types of jitter, namely: period jitter, cycle to cycle jitter and time interval error measurement [16].

With period jitter, the deviation in period is measured with respect to the average period, with a random number of cycles between each measurement. From this measurement the RMS value is easily derived by taking the standard deviation of the measured data set.

Cycle to cycle jitter is the variation in cycle time of a signal between adjacent cycles. Cycle to cycle jitter is usually expressed as a peak value, defining the maximum deviation between the edges of two consecutive cycles.

Another methodology of jitter measurement is time interval error (TIE). TIE is a measure for the time deviation of a signal edge from its ideal position compared to a reference point. For this measurement an ideal signal is needed to compare the actual signal with. This signal is often created using software.

#### 2.1.3 Long-term clock stability

Allan Variance [17] (AVAR), also called two-sample variance, is a technique to determine the long-term stability of a clock (or other types of signals, where stability is of interest). Variance normally used in statistics is defined by the expected value of the squared deviation from the mean.

$$\operatorname{Var} = \sigma^{2} = E \left[ (X - E [X])^{2} \right].$$

(2.1)

In contrast, AVAR calculates the variance based on the difference of adjacent fractional frequency measurements, calculating the two-sample variance. The AVAR method is shown in Equation 2.2.

$$\sigma_y^2(\tau) = E\left[\left(\Delta y\right)^2\right],\tag{2.2}$$

where  $\Delta y$  denotes the difference of adjacent fractional frequency measurements and  $\tau$  the coherence time (space between measurements). So AVAR gives insight on the variation of two adjacent  $\tau$  spaced samples. If we apply AVAR on a clock signal we can see how stable the clock is for a given coherence time. For clock synchronization this is of great interest, since it determines the maximum achievable performance of the clock synchronization.

In order to determine the interval time of the clock synchronization algorithm the long-term stability of the clock oscillators needs to be known. One way to infer the long-term drift is with the use of Allan variance. A Quartz crystal synthesizer has a frequency drift of  $10^{-11} - 10^{-12}$  [17] per second. So the RMS error after 1 second is 1-10ps.

# 2.2 Clock synthesizer model

To be able to correct clocks a clock model is needed. This clock model will define the parameters that will be used to correct a clock. The short-term (< 100s) relation between local time and global time can be modelled by a first order clock model [10]:

$$t_i = w_i t + \phi_i, \tag{2.3}$$

where  $t_i$  is the local time at node *i*, *t* the reference clock,  $w_i$  the clock skew and  $\phi_i$  the clock offset. The conversion from local time to global time can be written as:

$$t = \alpha_i t_i + \beta_i, \tag{2.4}$$

where  $\alpha = w_i^{-1}$  and  $\beta = w_i^{-1}\phi_i$  are the parameters needed to correct the local time of node *i*. These clock correction parameters will be used throughout the thesis.

This chapter first shortly covers the basic principles of hard-wired clock distribution networks. After that the basics of network based clock synchronization are addressed. Three novel network based clock synchronization algorithms will be covered. This chapter concludes with which of these three solutions can be best applied to the SPADnet system.

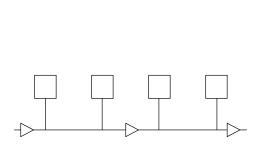

# 3.1 Hard-wired clock distribution

Typically, in synchronous digital systems the clock is distributed using a hard wired network. In these digital systems the clock originates from a single clock source and is distributed via a clock network to each component. There are different types of clock distribution networks, the simplest form is where the clock is daisy chained from each component to the next. A more sophisticated system, is the clock tree. In a clock tree the distance between the clock origin and each component is the same, and therefore the clocks are perfectly aligned at the leaves. In the daisy chained system on the contrary, the distance between the clock and component is not the same. Therefore there will be a clock offset at each node, which for some applications is not highly undesirable. The phase difference can be compromised by correcting the phases, with phase adjustment logic.

(a) Daisy chained clock network.

(b) Tree clock distributed network.

Figure 3.1: Example of typical hard wired clock distribution networks for digital systems.

# 3.2 Network based clock synchronization

In certain network based systems it is sometimes impossible to connect each node to a hard-wired clock distribution network. For example in wireless sensor networks (WSNs). A WSN containing standalone modules, who are connected only via a wireless communication network, might need to fulfil synchronous tasks, and therefore need a way to synchronize each module in the system. Generally this is done by time-stamping of data packets.

#### 3.2.1 Timestamp exchange protocols

To gain time information of each node data packets are used in network based synchronization. Time-stamping of data packets is the solution to get information about the clock drift and skew at each node. There are numerous timestamp exchange protocols.

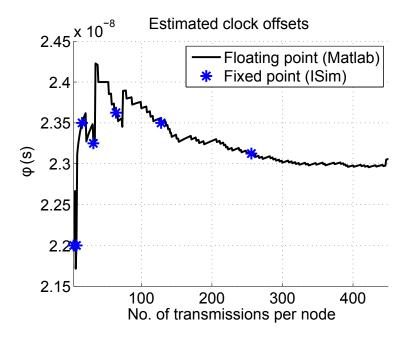

#### Two-way timestamp exchanges

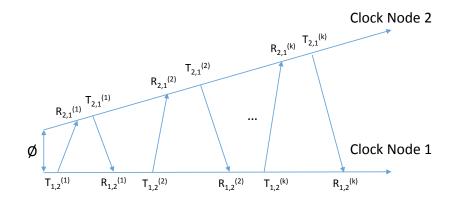

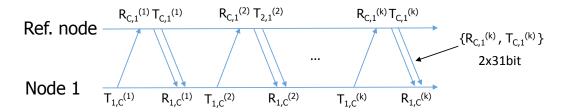

Most clock synchronization algorithms are based on two-way timestamp exchanges. Figure 3.2 shows the two-way timestamp exchange between a pair of nodes. Node 1 initiates the timestamp exchange, by sending a message to node 2. The message is marked with timestamp  $T_{1,2}(1)$ . Immediately when the message is received by node 2, the reception time is marked  $R_{2,1}(1)$ . Node 2 replies, again recording the transmission and reception times. This goes on until K two-way messages have been achieved.

Figure 3.2: Conventional two-way timestamp exchanges between a pair of nodes.

After K two-way timestamp exchanges an algorithm can be applied to find the clock correction parameters [10].

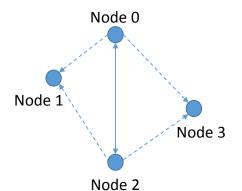

#### Reference broadcast exchange

In the reference broadcast exchange protocol [18] one node transmits a broadcast message, marking the transmission time. The other nodes mark the reception times of this broadcast. After executing multiple broadcasts, this timing information can be used to estimate the clock drift and skew, assuming the distance is known.

Figure 3.3: Reference broadcast protocol in a four node network. Node 0 transmits broadcast messages to the complete network, while capturing the transmission and reception times.

#### Passive listening protocol

The passive listening protocol is based on two-way timestamp exchanges, while the other nodes listen to this interaction of messages between the two nodes. The passive listening nodes also timestamp these overheard messages, which increases the amount of data collected which can contribute to a better estimation. A synchronization algorithm that uses passive listing is presented in [11].

Figure 3.4: Passive listening protocol in a four node network.

## 3.3 Clock synchronization algorithms

There are various solutions to synchronize clocks in networks. In this section three novel clock synchronization solutions will be presented. The best solution for this application will be selected, based on the performance, complexity and scalability.

In [10] two solutions for clock synchronization for wireless networks are presented: pairwise least squares (PLS) and global least squares (GLS). The solutions efficiently estimate the first order clock parameters, clock skews ( $\omega$ ), clock offsets ( $\phi$ ) and pairwise distances (**d**). Both solutions are based on timestamp exchanges via two-way messages and least squares. In PLS, pairs of nodes are synchronised per pair. GLS aims to find the global optimal solution for all unknown clock parameters and pairwise distances of the entire network.

The remaining novel clock synchronization algorithm is the asymmetrical timestamping and passive listening (ATPL) protocol [11]. The ATPL solution uses passive listening and least squares in order to find all unknown clock parameters and pairwise distances of the entire network.

#### 3.3.1 Least squares

All three novel clock synchronization algorithms use least squares to find the clock correction parameters. In general, least squares can be applied to problems where there are more equations than unknowns and, in general no solution exists [19]. Assume we have the set of linear equations

$$\mathbf{A}\mathbf{x} = \mathbf{b},\tag{3.1}$$

where **A** is a  $n \times m$  matrix and **x** is an *m*-dimensional vector containing unknowns. In the case m < n, an arbitrary vector **b** cannot be represented as a linear combination of the columns of matrix **A**. So the coefficients in vector **x** must be found, who will result in the best approximate of **b**.

$$\hat{\mathbf{b}} = \sum_{i=1}^{m} x_i \mathbf{a}_i. \tag{3.2}$$

The least squares solution minimizes the norm of the error:

$$\|\mathbf{e}\|^2 = \|\mathbf{b} - \mathbf{A}\mathbf{x}\|. \tag{3.3}$$

This minimization problem has a unique solution, provided that the columns of the matrix  $\mathbf{A}$  are linearly independent, given by solving the normal equations

$$\hat{\mathbf{x}} = \left(\mathbf{A}^T \mathbf{A}\right)^{-1} \mathbf{A}^T \mathbf{b}. \tag{3.4}$$

#### 3.3.2 Pairwise least squares

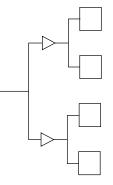

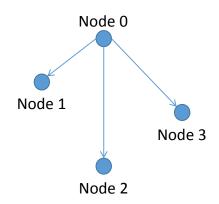

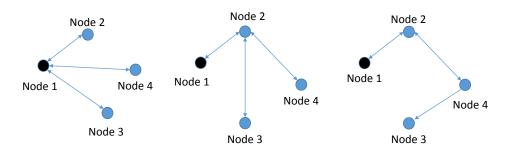

The pairwise least squares (PLS) solution synchronizes a pair of nodes, one node being the reference. For networks with N > 2 nodes the PLS solution needs to be applied N-1 times to synchronize all nodes. PLS can exploit only one link per pair. In Figure 3.5 a network of four nodes is shown, with node 0 as reference node. In this network the pairs where PLS is applied to are {Node0, Node1}, {Node0, Node2} and {Node0, Node3}.

Figure 3.5: four node network for the PLS solution.

To synchronize a node pair, for example node 0 and node 1, first K two-way timestamp exchanges are executed, which results in time recordings at node 0 ( $\mathbf{t}_{12}$ ) and node 1 ( $\mathbf{t}_{21}$ ). Then, the time recordings of node 1 are sent to node 0. After that, node 0 can perform the PLS algorithm, Equation 3.5. Subsequently, node 0 sends the clock correction parameters [ $\alpha_2 \beta_2$ ] to node 1. Finally node 1 corrects its clock with the received parameters. The same holds for the other node pairs. More explicitly, we obtain

$$\hat{\boldsymbol{\theta}}_{j} = \left(\mathbf{A}_{ji}^{T}\mathbf{A}_{ji}\right)^{-1}\mathbf{A}_{ji}^{T}\mathbf{t}_{ij}, \qquad (3.5)$$

with

$$\mathbf{A}_{ji} = [\mathbf{t}_{ji} \ \mathbf{1}_{2K} \ \mathbf{e}]^T \in \mathbb{R}^{2K \times 3},\\ \boldsymbol{\theta}_j = [\alpha_j \ \beta_j \ \tau_{ij}]^T \in \mathbb{R}^{3 \times 1},$$

where  $\mathbf{t}_{ij}, \mathbf{t}_{ji} \in \mathbb{R}^{2K \times 1}$  are the timestamps recorded at node *i* and *j* for all the two-way communications respectively,  $\mathbf{e} = [-1, +1, -1, \cdots, +1]^T \in \mathbb{R}^{2Kx1}, \mathbf{1}_{2K} \in \mathbb{R}^{2K \times 1}$  is a vector of ones with length 2*K*, and  $\alpha_j, \beta_j$  are the correction parameters for the clock skew  $\omega$  and the clock offset  $\phi$  of node j.

#### 3.3.3 Global least squares

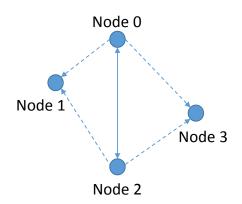

Global least squares (GLS) is an extended version of the pairwise model. The GLS solution is capable of estimating all the clock correction parameters of all nodes in the network at once. GLS can make use of every link available in the network, as shown in Figure 3.6. GLS can be applied on any network configuration, as long as each node has atleast one link connected to the network. In GLS, on each link K timestamp exchanges are executed. When the message exchanges are completed, the timestamps are send to the reference node, and the clock correction parameters for each node are calculated, using Equation 3.6.

Figure 3.6: Example configurations of four node networks, where the GLS algorithm can be applied to

The global least squares solution is obtained by minimizing the least squares norm

$$\hat{\boldsymbol{\theta}} = \left(\bar{\mathbf{A}}^T \bar{\mathbf{A}}\right)^{-1} \bar{\mathbf{A}}^T \bar{\mathbf{t}}_1, \qquad (3.6)$$

with

$$ar{\mathbf{A}} = ig[ar{\mathbf{T}} \ ar{\mathbf{E}}_1 \ \mathbf{E}_2ig] \in \mathbb{R}^{2KM imes L}, \ oldsymbol{ heta} = ig[ar{oldsymbol{lpha}} \ oldsymbol{eta} \ oldsymbol{ heta} = ig[ar{oldsymbol{lpha}} \ oldsymbol{ heta} \ oldsymbol{ heta} \ oldsymbol{eta} \ oldsymbol{eta} \ oldsymbol{eta} \ oldsymbol{eta} \ oldsymbol{a} \ oldsymbol{eta} \ eldsymbol{eta} \ oldsymbol{eta} \ eldsymbol{eta} \ eldsymb$$

where L = 2N + M - 2 and  $\bar{\mathbf{T}}, \bar{\mathbf{E}}_1 \in \mathbb{R}^{2KM \times (N-1)}$  are submatrices of  $\mathbf{T}$  and  $\mathbf{E}_1$  respectively, excluding the corresponding first columns.  $\bar{\boldsymbol{\alpha}}, \bar{\boldsymbol{\beta}} \in \mathbb{R}^{(N-1)\times 1}$  represent the unknown clock parameters of all the nodes excluding node 1 (reference node).  $\bar{\mathbf{t}}_1 \in \mathbb{R}^{2KM \times 1}$  is the first column of matrix  $\mathbf{T}$  which contains the timing markers recorded at node 1.

The matrix  $\mathbf{T} \in \mathbb{R}^{2KM \times N}$  contains all the timing vectors from all N nodes,  $M = \binom{N}{2}$ number of unique pairwise distances,  $\mathbf{E}_1 \in \mathbb{R}^{2KM \times N}$ ,  $\mathbf{E}_2 - \mathbf{I}_M \otimes \mathbf{e} \in \mathbb{R}^{2KM \times N}$ . For N = 4 $\mathbf{T}$  and  $\mathbf{E}_1$  are of the form

$$\mathbf{T} = \begin{bmatrix} \mathbf{t}_{12} & -\mathbf{t}_{21} & & \\ \mathbf{t}_{13} & & -\mathbf{t}_{31} & \\ \mathbf{t}_{14} & & & -\mathbf{t}_{41} \\ & \mathbf{t}_{23} & -\mathbf{t}_{32} & \\ & \mathbf{t}_{24} & & -\mathbf{t}_{42} \\ & & \mathbf{t}_{34} & -\mathbf{t}_{43} \end{bmatrix},$$

(3.7)

$$\mathbf{E}_{1} = \begin{bmatrix} +\mathbf{1}_{2K} & -\mathbf{1}_{2K} \\ +\mathbf{1}_{2K} & & -\mathbf{1}_{2K} \\ +\mathbf{1}_{2K} & & -\mathbf{1}_{2K} \\ & +\mathbf{1}_{2K} & -\mathbf{1}_{2K} \\ & & +\mathbf{1}_{2K} & -\mathbf{1}_{2K} \end{bmatrix}.$$

(3.8)

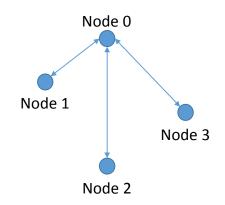

#### 3.3.4 Asymmetrical time-stamping and passive listening

Asymmetrical time-stamping and passive listening (ATPL) [11] exploits the broadcast property to estimate the clock parameters. During communication between a pair of nodes timestamps are recorded and exchanged, like in the PLS and GLS solution. Besides this, the remaining nodes in the network passively listen and record the timestamps with their individual clocks. In this way more information is obtained to solve the unknown clock parameters. Figure 3.7, shows how the other nodes listen, while a two-way timestamp exchange is done between a pair of nodes.

In the ATPL there are no constraints on the sequence of forward links and reverse links, hence the reverse link does not always need to follow the forward link. This means that a node does not need to respond to the request from another node immediately. In the ATPL protocol the two-way communication always occurs between node i and the central node, where node i initiates the two way communication. The other nodes in the network passively listen and timestamp the messages.

Figure 3.7: four node network for ATPL solution. The dotted arrows indicate the nodes passive listening to other nodes two-way timestamp exchange.

The clock parameters can be estimated using least squares as

$$\hat{\boldsymbol{\theta}} = \left(\bar{\mathbf{A}}^T \boldsymbol{\Sigma}^{-1} \bar{\mathbf{A}}\right)^{-1} \bar{\mathbf{A}}^T \boldsymbol{\Sigma}^{-1} \bar{\mathbf{x}}, \qquad (3.9)$$

The construction of the matrices are presented in Figure 3.8; more information about this can be found in [11].

|                                                               |                        |                                                                                              |                                          | Āel                                                                                         | $\mathbb{R}^{2K \times 6}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |                                                                         |                                                                    |                                                                                              | $\mathbf{x} \in \mathbb{R}^{2K}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $\times 1$                                                              |                                                           |     |

|---------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|-----|

| Node 0 responds<br>( $i=0$ )<br>Node 1 transmits<br>( $i=1$ ) | j=1 $j=2$ $j=0$ $j=2$  | $\begin{bmatrix} \mathbf{t}_0 \\ \mathbf{t}_0 \\ -\mathbf{r}_{1,0} \\ 0_{K_1} \end{bmatrix}$ | $1_{K_0}$ $1_{K_0}$ $-1_{K_1}$ $0_{K_1}$ | $\begin{array}{c} -\mathbf{r}_{0,1} \\ 0_{K_0} \\ \mathbf{t}_1 \\ \mathbf{t}_1 \end{array}$ | $-1_{K_0}\\ 0_{K_0}\\ 1_{K_1}\\ 1_{K_1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{c c} 1_{K_0} \\ 0_{K_0} \\ 1_{K_1} \\ 0_{K_1} \end{array}$ | $\begin{array}{c} 0_{K_0} \\ 1_{K_0} \\ 0_{K_1} \\ 0_{K_1} \end{array}$ | $\begin{array}{c} & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & $ | $\begin{bmatrix} 0_{K_0} \\ -\mathbf{r}_{0,2} \\ 0_{K_1} \\ -\mathbf{r}_{1,2} \end{bmatrix}$ | $\begin{array}{c} 0_{K_0} \\ -1_{K_0} \\ 0_{K_1} \\ -1_{K_1} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\begin{array}{c} 0_{K_0} \\ 0_{K_0} \\ 0_{K_1} \\ 1_{K_1} \end{array}$ | $\begin{bmatrix} \mathbf{c}_2 \\ 	au_{1,2} \end{bmatrix}$ | + n |

| Node 2 transmits<br>(i=2)                                     | $\substack{j=0\\ j=1}$ | $\begin{bmatrix} -\mathbf{r}_{2,0} \\ 0_{K_2} \end{bmatrix}$                                 | $-1_{K_2}$<br>$0_{K_2}$                  | $egin{array}{c} 0_{K_2} \ -\mathbf{r}_{2,1} \end{array}$                                    | $egin{array}{c} egin{array}{c} egin{array}$ | $\begin{array}{c} 0_{K_2} \\ 0_{K_2} \end{array}$                         | $oldsymbol{1}_{K_2}$<br>$oldsymbol{0}_{K_2}$                            | $\lfloor \boldsymbol{\tau}_0  floor$                               | $egin{array}{c} \mathbf{t}_2 \ \mathbf{t}_2 \ \mathbf{t}_2 \end{array}$                      | $egin{array}{c} egin{array}{c} egin{array}$ | $egin{array}{c} 0_{K_2} \ 1_{K_2} \end{array}$                          |                                                           |     |

Figure 3.8: Construction of the matrices for the ATPL solution from [11]

#### 3.3.5 Performance

The performance of the presented algorithms is bounded by the stability of the local clocks. Ideally, the two-way timestamp exchanges would be performed in the region where the clocks are most stable, to estimate the clock correction parameters. As shown in Figure 6.2 on page 34 the window where the clock is most stable is 2-16 seconds with a stability of 22 ns. No algorithms can compensate for this random noise on the clock output.

The performance of PLS, GLS and ATPL is the same, they all follow the Cramer-Rao lower bound, shown to approach the theoretical limits. Because GLS, and especially ATPL, can exploit more communication links they can be more efficient, and reach the lower bound faster than PLS.

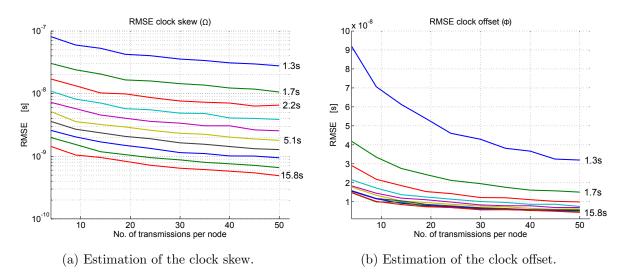

The number of timestamp exchanges, K, has a strong influence on the performance. The more timestamp exchanges, the better the estimation. Not only the amount of message exchanges, but also the length of the observation window wherein the exchanges take place, effect performance. The estimation will be better for longer observation windows. Figure 3.9 show how the estimation is affected by the number of timestamp exchanges and length of the observation window.

Figure 3.9: Estimation of the clock parameters using PLS in a two node system, for different transmissions and observation windows. The algorithm was performed with MATLAB, with an observation noise of 22 ns, and infinite clock resolution.

#### 3.3.6 Cramer-Rao lower bound

The algorithms follow the Cramer-Rao lower bound (CRLB), which defines the smallest variance of any unbiased estimator. If an estimator is found that achieves the CRLB, we call this a minimum variance unbiased estimator (MVUE).

In the case of PLS, GLS and ATPL the CRLB is most influenced by the noise on the time-stamping of the messages, this noise is called observation noise. This noise originates from the instability of the clock, used for time-stamping of the two-way message exchanges, and communication latency uncertainty of the network. With simulations, using infinite clock resolution and averaging, it is possible to reach below the observation noise. In a practical situation, the random clock noise, cannot be compensated for by the algorithm, and therefore the estimation will be bound by the observation noise. The algorithm only estimates the first order clock parameters, which does not include any compensation for the clock noise.

### 3.3.7 Complexity

Table 3.1 shows the sizes of the operations needed to compute the least squares solution, as presented in Equation 3.4. To solve the least squares problem, one matrix multiplication, one matrix inversion and two matrix vector multiplications are necessary.

The most complex operation is the matrix inversion. For PLS a 3x3 matrix needs to be inverted, whereas for ATPL a 3Nx3N matrix needs to be inverted. Clearly we see that PLS has the lowest complexity, GLS having a moderate complexity and ATPL the highest complexity.

Table 3.1: Operation sizes of each least squares operation. With K number of messages,  $K^{\iota} = K_1 + K_2 + K_N$ , L = 2N + M - 2, M the number of unique links in the network and with N nodes.

|      | C = AA           | d = Ab          | $E = C^{-1}$ | Ed            |

|------|------------------|-----------------|--------------|---------------|