# MSc Thesis

# **FPGA** accelerated Facial Recognition

### Nikolaos Stekas

ES-MS-4415833

#### Abstract

The ability to recognize faces is highly important in many areas of development. Though the years, the evolving technologies, enabled this process to be adapted in modern computer systems. These systems can be found in a wide variety of areas that yield significant impact. Therefore, there is an increasing demand for fast and accurate systems, able to perform facial recognition.

In this thesis, a face recognition implementation on a FPGA-based System on Chip (SoC), is presented. This implementation utilizes Local Binary Patterns Histograms to extract features from test face images and Manhattan Distance to retrieve the correct match from the systems face database. The SoC utilized is a Zynq-7030. The feature extraction and the distance computations, between the database, are implemented on the FPGA. The ARM processor of the SoC is responsible for receiving the input stream and presenting the output result, using the acquired distances. Real-time, high accuracy face recognition, with an execution time of 2.4 ms and accuracy of 78%, is achieved through this implementation.

Faculty of Electrical Engineering, Mathematics and Computer Science

#### THESIS

# submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### EMBEDDED SYSTEMS

by

Nikolaos Stekas born in Volos, Greece

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

#### by Nikolaos Stekas

#### Abstract

The ability to recognize faces is highly important in many areas of development. Though the years, the evolving technologies, enabled this process to be adapted in modern computer systems. These systems can be found in a wide variety of areas that yield significant impact. Therefore, there is an increasing demand for fast and accurate systems, able to perform facial recognition.

In this thesis, a face recognition implementation on a FPGA-based System on Chip (SoC), is presented. This implementation utilizes Local Binary Patterns Histograms to extract features from test face images and Manhattan Distance to retrieve the correct match from the systems face database. The SoC utilized is a Zynq-7030. The feature extraction and the distance computations, between the database, are implemented on the FPGA. The ARM processor of the SoC is responsible for receiving the input stream and presenting the output result, using the acquired distances. Real-time, high accuracy face recognition, with an execution time of 2.4 ms and accuracy of 78%, is achieved through this implementation.

| Laboratory<br>Codenumber | : | Computer Engineering<br>ES-MS-4415833   |

|--------------------------|---|-----------------------------------------|

|                          |   |                                         |

| Committee Members        | : |                                         |

| Advisor:                 |   | dr.ir. Stephan Wong, CE, TU Delft       |

| Chairman:                |   | dr.ir. Stephan Wong, CE, TU Delft       |

| Member:                  |   | dr.ir. Arjan van Genderen, CE, TU Delft |

| Member:                  |   | dr.ir. Rene van Leuken, CAS, TU Delft   |

| Member:                  |   | Dirk van den Heuvel, Topic              |

"It is the mark of an educated mind to be able to entertain a thought without accepting it."

- Aristotle

# Contents

| List of Figures  | viii |

|------------------|------|

| List of Tables   | ix   |

| List of Acronyms | xi   |

| Acknowledgements | xiii |

| 1        | Intr | roduction                                        | 1              |

|----------|------|--------------------------------------------------|----------------|

|          | 1.1  | Motivation of Work                               | 1              |

|          | 1.2  | Project Definition                               | 2              |

|          | 1.3  | Project Goals                                    | 3              |

|          | 1.4  | Thesis Outline                                   | 3              |

| <b>2</b> | Bac  | kground                                          | <b>5</b>       |

|          | 2.1  | Facial Recognition Systems                       | 5              |

|          | 2.2  | Reconfigurable Computing                         | 6              |

|          | 2.3  | Topic Development Kit                            | $\overline{7}$ |

|          | 2.4  | Conclusion                                       | 8              |

| 3        | Lite | erature Review                                   | 9              |

|          | 3.1  | Facial Recognition Algorithms                    | 9              |

|          |      | 3.1.1 Eigenfaces                                 | 9              |

|          |      | 3.1.2 Fisherfaces                                | 11             |

|          |      | 3.1.3 Elastic Bunch Graph                        | 12             |

|          |      | 3.1.4 Local Binary Patterns Histograms           | 14             |

|          |      | 3.1.5 Scale Invariant Feature Transform          | 17             |

|          |      | 3.1.6 Algorithms Comparison                      | 20             |

|          | 3.2  | Local Binary Patterns Histograms Implementations | 25             |

|          | 3.3  | Conclusion                                       | 28             |

| 4        | Alg  | orithm Development                               | 31             |

|          | 4.1  | Number of Regions                                | 31             |

|          | 4.2  | Weights of Regions                               | 33             |

|          | 4.3  | Distance Measures                                | 35             |

|          | 4.4  | Classification                                   | 36             |

|          | 4.5  | Conclusion                                       | 39             |

| <b>5</b> | Imp   | plementation                          | 41 |

|----------|-------|---------------------------------------|----|

|          | 5.1   | Design Approach                       | 41 |

|          | 5.2   | Feature Extraction IP core            | 43 |

|          |       | 5.2.1 Modulo Operation                | 45 |

|          |       | 5.2.2 Input and Output Size           | 48 |

|          |       | 5.2.3 Block RAM Utilization           | 48 |

|          |       | 5.2.4 Temporary Output Initialization | 51 |

|          |       | 5.2.5 Pipelining $\ldots$             | 52 |

|          |       | 5.2.6 Loop Unroll                     | 53 |

|          | 5.3   | Histograms Comparison IP core         | 56 |

|          |       | 5.3.1 Input Data                      | 58 |

|          |       | 5.3.2 Input Size                      | 59 |

|          |       | 5.3.3 Block RAM Utilization           | 60 |

|          |       | 5.3.4 Pipeline                        | 62 |

|          |       | 5.3.5 Loop Unroll                     | 62 |

|          | 5.4   | Programmable Logic integration        | 66 |

|          | 5.5   | Operation of the ARM processor        | 69 |

|          | 5.6   | Conclusion                            | 69 |

|          | _     |                                       |    |

| 6        |       |                                       | 71 |

|          | 6.1   |                                       | 71 |

|          | 6.2   |                                       | 73 |

|          | 6.3   |                                       | 75 |

|          | 6.4   |                                       | 76 |

|          | 6.5   | 1                                     | 78 |

|          | 6.6   | Conclusion                            | 79 |

| 7        | Cor   | nclusion                              | 81 |

| •        | 7.1   |                                       | 81 |

|          | 7.2   |                                       | 83 |

|          | 7.3   |                                       | 83 |

|          |       |                                       | 00 |

| Bi       | bliog | graphy                                | 87 |

# List of Figures

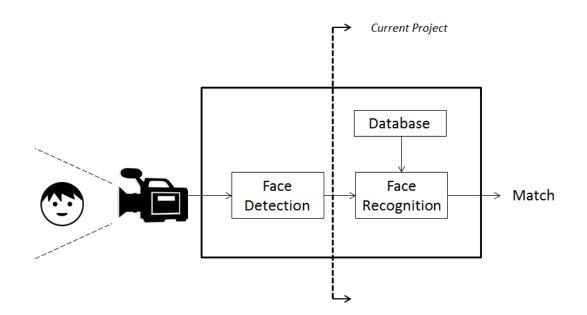

| 1.1  | General overview of the project.                                                                                                                                                                                                         | 2        |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

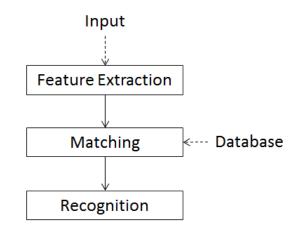

| 2.1  | The procedure of face recognition.                                                                                                                                                                                                       | 5        |

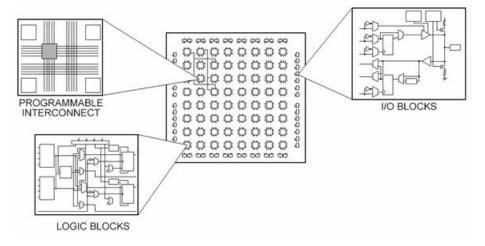

| 2.2  | FPGA overview. [12]                                                                                                                                                                                                                      | 7        |

| 2.3  | Z-7030 specifications. $[15]$                                                                                                                                                                                                            | 8        |

| 3.1  | Different eigenfaces corresponding to varying eigenvalues $[17]$                                                                                                                                                                         | 10       |

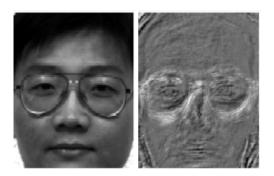

| 3.2  | Fisherface derived from a face image in the Yale Database $[4]$                                                                                                                                                                          | 12       |

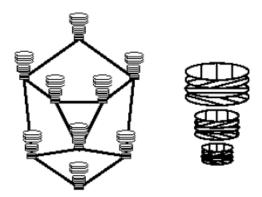

| 3.3  | An image graph with a jet seen on the left $[5]$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                            | 13       |

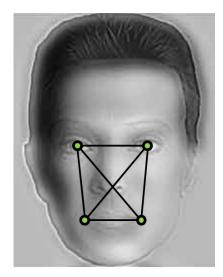

| 3.4  | Positioning four nodes and six edges applied in a face image. $\ldots$                                                                                                                                                                   | 13       |

| 3.5  | A face bunch graph. $\ldots$                                                                                                                            | 14       |

| 3.6  | Different grids for rotated faces.                                                                                                                                                                                                       | 15       |

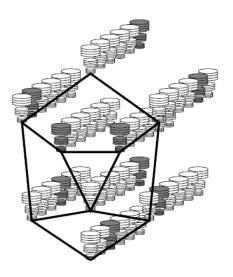

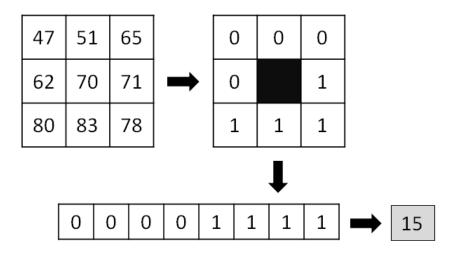

| 3.7  | LBP operator example.                                                                                                                                                                                                                    | 15       |

| 3.8  | Process of creating the final histogram $[22]$                                                                                                                                                                                           | 16       |

| 3.9  | Neighbors of a pixel in the 3-D space $[27]$                                                                                                                                                                                             | 18       |

| 3.10 | Process to reach DOGs in keypoint exploration $[27]$                                                                                                                                                                                     | 18       |

| 3.11 | Keypoints represented as different size bolbs depending on the scale $[27]$                                                                                                                                                              | 19       |

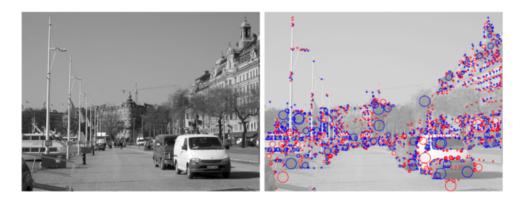

| 3.12 | Keypoints example of an image [25]                                                                                                                                                                                                       | 19       |

| 3.13 | Creating a histogram for a $16x16$ neighborhood using magnitude and orienta-<br>tion values [27]                                                                                                                                         | 20       |

| 3.14 | Error rate of fisherfaces and eigenfaces in Yale Database [4]                                                                                                                                                                            | 21       |

| 3.15 | Fisherface (LDA) and eigenface (PCA) accuracy rates for different pose angles [28]                                                                                                                                                       | 21       |

| 3.16 | EBGM, fisherfaces and eigenfaces comparison in Feret Database, fafb subset [29]                                                                                                                                                          | 22       |

| 3.17 | EBGM, fisherfaces and eigenfaces comparison in Feret Database, dup2 subset [29]                                                                                                                                                          | 22       |

| 3.18 | LBPH, EBGM and Eigenfaces comparison in fafb, fafc and dup2 subsets [29]                                                                                                                                                                 | 23       |

| 3.19 | Eigenfaces, Fisherfaces, LBPH and SIFT comparison for images with different compression level [30]                                                                                                                                       | 24       |

| 3.20 | Block diagram of SIMD LBP evaluation [9]                                                                                                                                                                                                 | 26       |

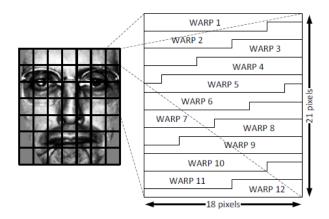

| 3.21 | Arrangement of the thread blocks for a sample image divided to 7 7 regions.<br>Each warp in a thread block constructs a per-warp histogram for a 32 pixel area in the corresponding region as shown on the right side of the figure. [8] | 20<br>27 |

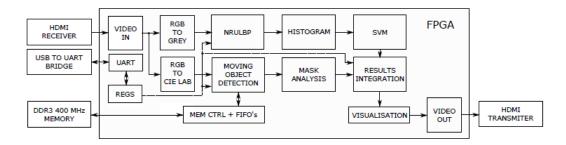

| 3.22 | FPGA based system overview. [32]                                                                                                                                                                                                         | 28       |

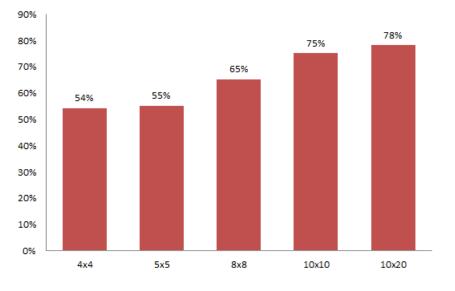

| 4.1  | Accuracy results for different region numbers. (X axis x Y axis) $\ldots \ldots \ldots$                                                                                                                                                  | 32       |

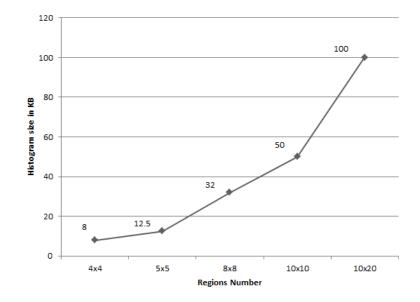

| 4.2  | Image Histogram size for different region numbers                                                                                                                                                                                        | 33       |

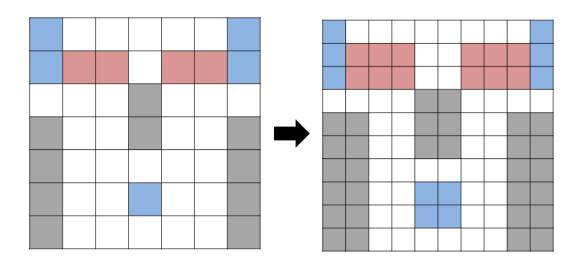

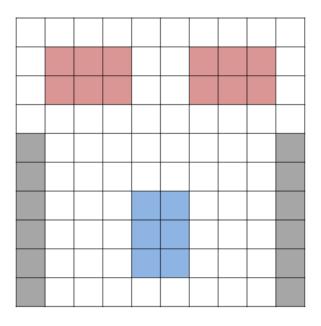

| 4.3  | 7x7 regions weights [6] modified for 10x10 regions (red squares indicate region weight 4.0, blue 2.0, white 1.0 and grey 0.0)                                                                                                            | 34       |

| 4.4  | Proposed region weights (red squares indicate region weight 8.0, blue 4.0, white                                                                                                                                                         |          |

|      | 2.0 and grey 1.0)                                                                                                                                                                                                                        | 34       |

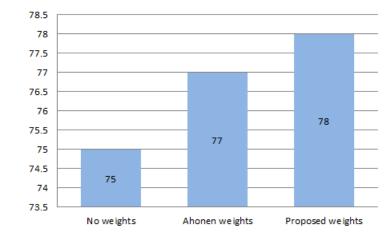

| 4.5  | Region weights comparison (No weights, Ahonen weights [6], Proposed weights)                                                                  | 35 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

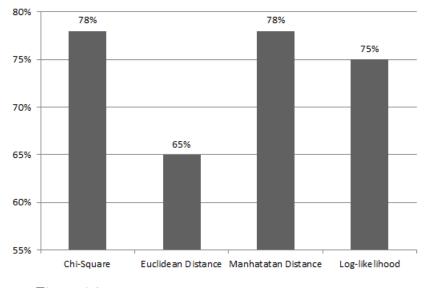

| 4.6  | Accuracy of different distance calculation models                                                                                             | 36 |

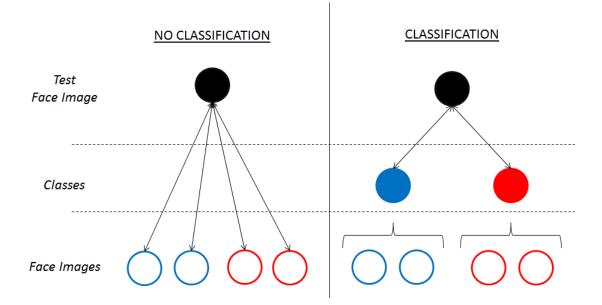

| 4.7  | Matching process with and without classification                                                                                              | 37 |

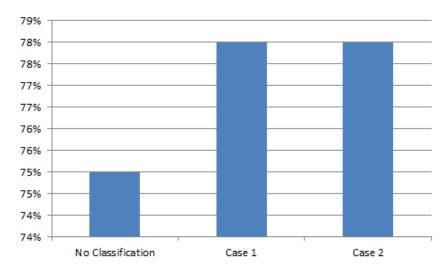

| 4.8  | Classification cases accuracy results                                                                                                         | 38 |

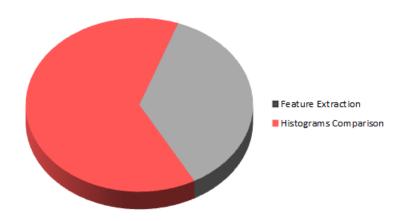

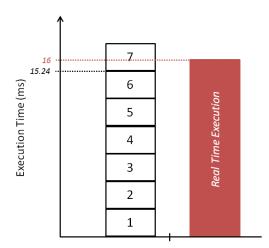

| 5.1  | Feature Extraction, Histograms Comparison ration                                                                                              | 42 |

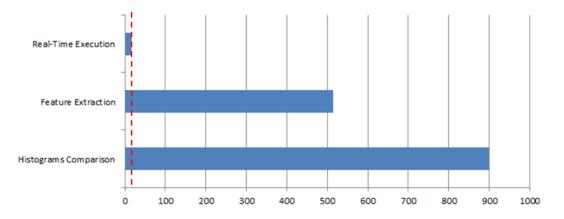

| 5.2  | Real-Time execution compared to Feature Extraction and Histograms Com-<br>parison time                                                        | 42 |

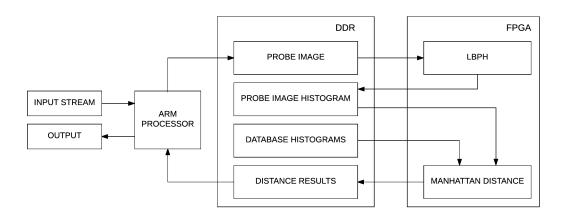

| 5.3  | System Overview [38]                                                                                                                          | 43 |

| 5.4  | Grouping of fist conditional statement. (Same color regions belong to the same group)                                                         | 46 |

| 5.5  | Overview of the proposed modulo operation design.                                                                                             | 47 |

| 5.6  | Input Word Data Organization                                                                                                                  | 48 |

| 5.7  | Ideal BRAM number utilization (The different color implies the utilization of a different BRAM)                                               | 50 |

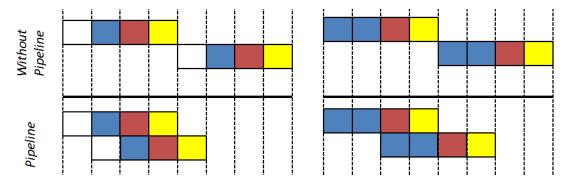

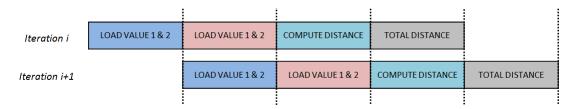

| 5.8  | Two (right and left) examples of pipeline application. (The squares indicate tasks and the different colors the different resources utilized) | 52 |

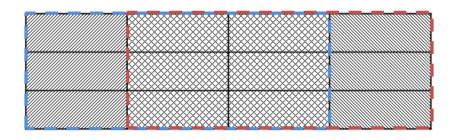

| 5.9  | Data overlapping of two consecutive LBP operations (blue and red border lines                                                                 | 02 |

| 0.0  | indicate the data for the first and second operation respectively                                                                             | 54 |

| 5.10 | Process to check the bin values accessed in the BRAM                                                                                          | 54 |

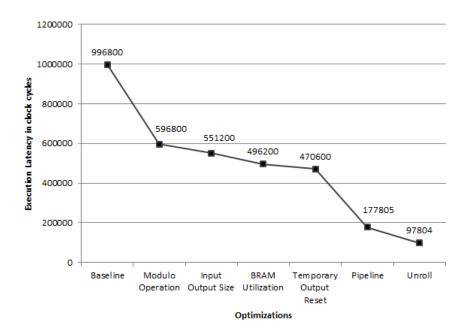

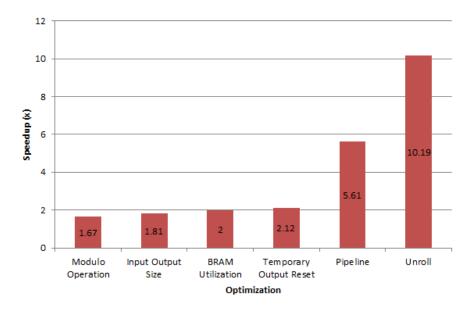

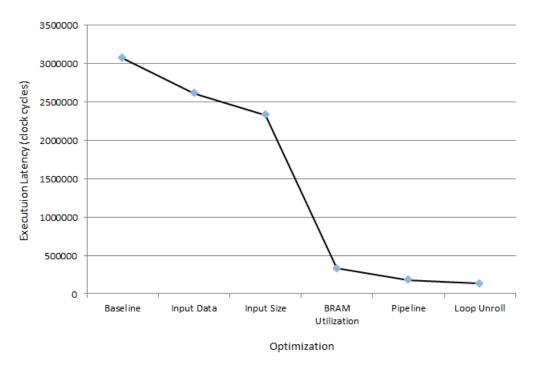

| 5.11 | Execution Latency of different optimizations in clock cycles                                                                                  | 55 |

| 5.12 | Speedup of different optimizations compared to baseline design.                                                                               | 56 |

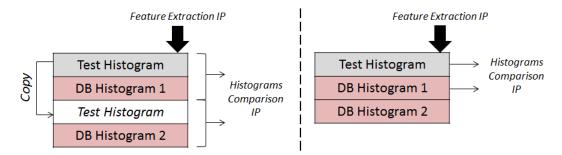

| 5.13 | Import input methods. (Left: One unified input, Right: Two inputs                                                                             | 57 |

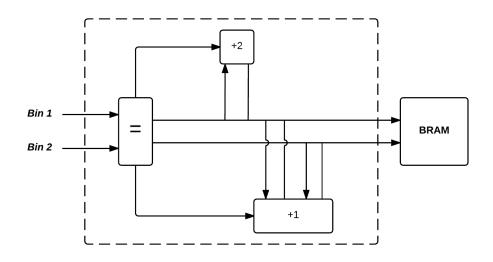

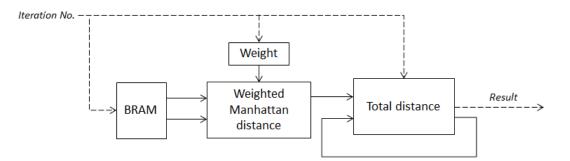

| 5.14 | Overview of two histograms' distance calculation                                                                                              | 58 |

| 5.15 | Input Format                                                                                                                                  | 60 |

| 5.16 | Distance Calculation Pipeline                                                                                                                 | 62 |

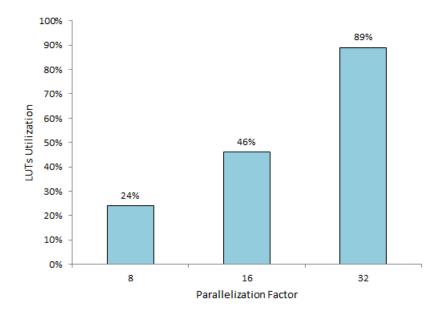

| 5.17 | LUTs utilization for different parallelization factors.                                                                                       | 64 |

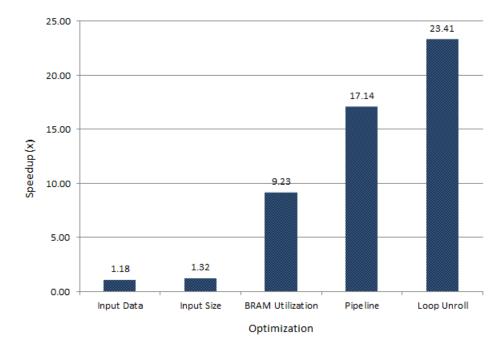

| 5.18 | Execution Latency in clock cycles for different optimizations.                                                                                | 65 |

| 5.19 | Speedup of different optimizations compared to baseline design                                                                                | 66 |

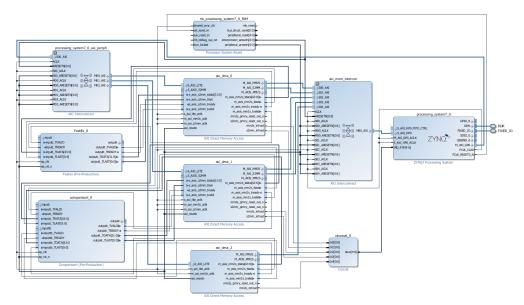

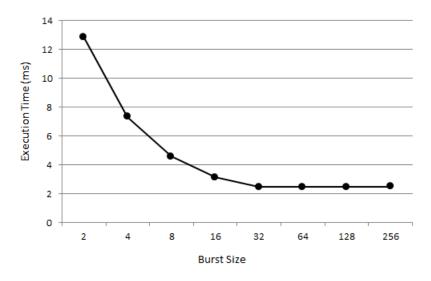

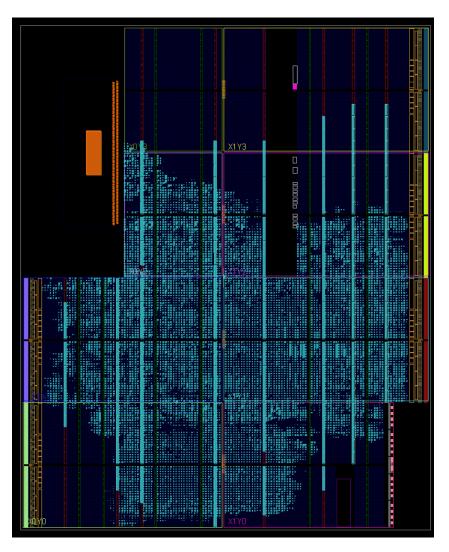

| 5.20 | FPGA design of our system                                                                                                                     | 67 |

| 5.21 | Performance of different burst sizes.                                                                                                         | 68 |

| 6.1  | Face images of 4 people used in the database $[33]$                                                                                           | 72 |

| 6.2  | Example Test Images [33]                                                                                                                      | 72 |

| 6.3  | Editing of an UFI image [33]                                                                                                                  | 73 |

| 6.4  | Result Output                                                                                                                                 | 73 |

| 6.5  | Execution time compared to real-time execution                                                                                                | 74 |

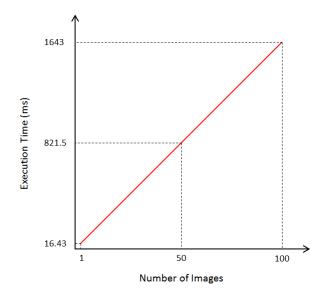

| 6.6  | Execution time for 100 images                                                                                                                 | 75 |

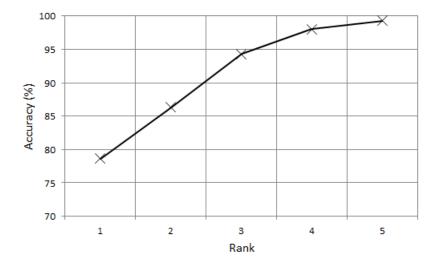

| 6.7  | Accuracy for different ranks                                                                                                                  | 76 |

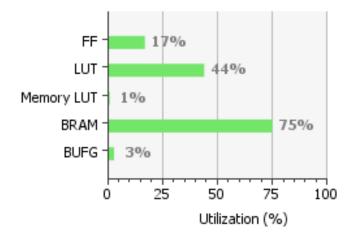

| 6.8  | Resource Utilization Percentage                                                                                                               | 77 |

| 6.9  | FPGA overview                                                                                                                                 | 78 |

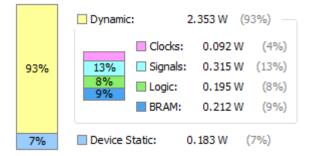

| 6.10 | On chip power consumption                                                                                                                     | 79 |

|      |                                                                                                                                               |    |

# List of Tables

| 3.1  | Algorithms' Database Size                                                                | 24 |

|------|------------------------------------------------------------------------------------------|----|

| 3.2  | Database size for 100 images of size $100x100 \dots \dots \dots \dots \dots \dots \dots$ | 24 |

| 3.3  | Calculations for extracting features from a $200x200$ probe image                        | 25 |

| 3.4  | Object detection in <i>frames per second</i> for two different target error rate         |    |

|      | <i>a</i> classifiers                                                                     | 27 |

| 3.5  | Feature extraction times of the GPU and CPU implementations for var-                     |    |

|      | ious cases using a single stream [8]                                                     | 27 |

| 3.6  | Detection results. Correct detections (CD), false detections (FD), missed                |    |

|      | detections (MD), accuracy = $CD/(CD+FD)$ [32]                                            | 28 |

| 4.1  | Distance between the best match and the second best match distance                       | 32 |

| 5.1  | Baseline design performance in clock cycles                                              | 44 |

| 5.2  | Baseline design resources utilization                                                    | 45 |

| 5.3  | Design performance in clock cycles with proposed modulo operation $\ . \ .$              | 47 |

| 5.4  | Design utilization with proposed modulo operation                                        | 47 |

| 5.5  | Core design performance in clock cycles with new input and output data                   |    |

|      | size                                                                                     | 49 |

| 5.6  | Block design performance in clock cycles with the proposed BRAMs                         |    |

|      | utilization                                                                              | 51 |

| 5.7  | Block design utilization with the proposed BRAMs utilization                             | 51 |

| 5.8  | Design performance in clock cycles with the proposed reset design                        | 52 |

| 5.9  | Core design performance in clock cycles with pipeline applied                            | 53 |

| 5.10 | Final IP core design performance in clock cycles (after further paral-                   |    |

|      | lelization)                                                                              | 55 |

| 5.11 | Final IP core design utilization (after further parallelization)                         | 55 |

| 5.12 | Histograms Comparison core baseline design performance in clock cycles                   | 58 |

| 5.13 | Histograms Comparison core baseline design resource utilization                          | 58 |

| 5.14 | Design performance in clock cycles by importing the half database                        | 59 |

| 5.15 | IP design performance in clock cycles with new input size                                | 60 |

| 5.16 | Core design performance in clock cycles with proposed BRAM utilization.                  | 61 |

| 5.17 | Core design utilization with proposed BRAM utilization                                   | 61 |

| 5.18 | Design performance in clock cycles with pipeline applied                                 | 63 |

| 5.19 | Final IP core design performance in clock cycles (loop unroll applied)                   | 65 |

| 5.20 | Final IP core design utilization with proposed BRAM utilization                          | 65 |

| 6.1  | System execution time                                                                    | 73 |

| 6.2  | Different implementations comparison                                                     | 75 |

| 6.3  | Experiments' Accuracy Results                                                            | 76 |

| 6.4  | FPGA Resources Utilization                                                               | 77 |

| 6.5  | Power Consumption Information                                                            | 79 |

# List of Acronyms

ASIC Application Specific Integrated Circuit

AXI Advanced eXtensible Interface

BRAM Block Random Access Memory

DMA Direct Memory Access

FF Flip-Flop

FPGA Field Programmable Gate Array

GPU Graphics Processing Unit

IP Intellectual Property

LBPH Local Binary Patterns Histograms

LUT Look Up Table

PL Programmable Logic

SoC System on Chip

TDK Topic Development Kit

UFI Unconstrained Facial Images

# Acknowledgements

Foremost, I would like to express my sincere gratitude to my parents, Dimitrios and Garyfallia, and the rest of my family for their support, during all the years of my studies. I would also like to thank my friends, that encouraged me throughout the whole thesis and assisted me, whenever needed, on different tasks.

I also owe thanks to my supervisor dr. ir. Stephan Wong, for his valuable help and guidance, during my thesis. In addition, I would like to show my appreciation to my other professors in TU Delft, for the knowledge and experience I acquired during my studies.

Last but not least, I would like to thank wholeheartedly Topic Embedded Systems and all the people there, for providing me with all the necessities, in order to complete my work successfully. I should, moreover, offer thanks to Dirk van den Heuvel, who was my supervisor on behalf of Topic and helped me achieve my goals with his ideas and experience.

Nikolaos Stekas Delft, The Netherlands May 30, 2016 Facial Recognition is a subject that researchers have focused on for years. In the current Master of Science thesis, a real-time facial recognition system will be implemented, exploiting FPGA technology. This project was carried out in collaboration with TOPIC Embedded Systems, that set the specifications of the project and provided all resources needed to proceed with the implementation. In this chapter, in Section 1.1 the motivation around this project is stated, in Section 1.2 a description about the project and its specifications are given, in Section 1.3 the goals of this project are stated and finally in Section 1.4 the outline of the Thesis is described.

### 1.1 Motivation of Work

Humans mainly use faces to recognize individuals. In the past decades, the advances in technology enabled this recognition to take place, similarly, in computing systems. The first implementations [1], [2] could be characterized as semi-automated. The required features for recognition, were located and marked manually and then compared by the computer system. In the future years, completely automated simple geometrical models, based on linear algebra models, were utilized to perform recognition. Such models are described in Chapter 3 ([3], [4]). Nowadays, sophisticated models are utilized for the same purpose. Those models utilize geometrical features of the face in combination with advanced mathematical models ([5], [6], [7]), increasing this way the accuracy of the process significantly.

Aside from the accuracy, execution time of facial recognition processes is also of high importance. The newly introduced, complex, models demand intensive computations that consume a notable amount of time. New technologies in the field of processors made it possible to accelerate the facial recognition process, achieving, presently, real-time demands ([8], [9], [10]).

This evolution in the field of facial recognition, enabled solutions in a number of different sections varying from medical assistance to security systems. The introduction of face recognition in these areas of interest, combined to the wide spreading into simple industry solutions, highlighted the importance of the subject and its mandatory evolution. Thus, the bar for face recognition technologies is raised constantly, with a need on implementing systems that are faster and of higher accuracy.

The current project aims to cope with those demanding needs and derive effective solutions. Taking advantage of contemporary technology, FPGAs in specific, will be the main aid towards this goal.

### 1.2 **Project Definition**

The present project is aiming on designing a facial recognition system, in an embedded platform utilizing FPGA technology. The basic idea, is to utilize a camera and recognize the face that is being recorded. A database that has been stored in the platform will be used for this purpose.

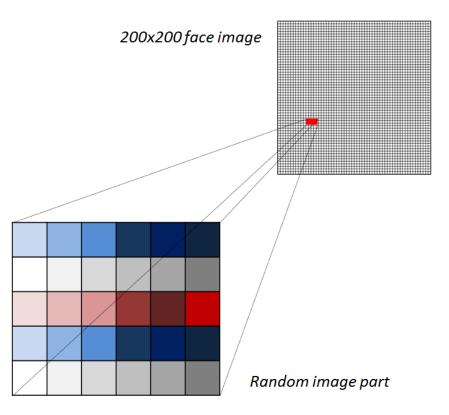

In more detail, a camera recording at a rate of 60 fps will be used to import images. Those images will first go through a face detection process, that has been already implemented separately, and gives one or multiple faces as an output, in a specific image size, 200x200 pixels.

After this process is complete, the current project part takes over. The face that has been detected, must be recognized. An algorithm is first used to extract features out of the recorded face. Then, the matching process can take place. A database of faces is required for this. We should mention here that the creation of the database has been done beforehand and the computation intensity to create it is not of our concern and is not needed to be taken in consideration. The total number of faces in the database will be 100, and a total of 20 different people(5 images per person), as specified for the project. Also, as specified for this project, we assume that the face detected is of someone included in the database and not an unknown individual. This way, the best match is recognized as the recorded person. The last two specifications were set by Topic and are derived by the final product needs. The overview of the project can be viewed in Figure 1.1

Figure 1.1: General overview of the project.

The embedded platform utilized includes a heterogeneous processor (Zynq-7030) consisting of both a CPU and a FPGA. The implementation will exploit both features, but will focus on the FPGA processor in order to carry out the compute-intensive parts, achieving this way a real-time system responding to the frame rate of the camera (60fps).

### 1.3 Project Goals

The main goal of this project is to implement a face recognition system utilizing FPGA technology. Accuracy and execution time are the main aspects, that focus is needed on, in order to achieve real-time, high accuracy face recognition. Real-time performance is met, if the recognition is performed in less than 16 ms. This time is derived by the frame rate of the camera. As 60 frames must be processed at 1 second, each frame must be processed in less than 16 ms (1/60 = 0.016 seconds). In addition, high-accuracy is translated to a first rank accuracy percentage of higher than 75%, matching the accuracy achieved by the state of the art models, that will be described in Chapter 3.

To achieve this, research regarding facial recognition algorithms and implementation needs to be carried out. Through this research, an effective algorithm, that can provide high accuracy in a manageable time, needs to be chosen to apply it on our system and also identify how other completed implementations perform. Research is also needed concerning the implementation process, this way the proper path for reaching our goal effectively can be approximated and followed during our implementation design. The goals of this project can be summarized to the following:

- Research on facial recognition algorithms and conclude on the most suitable for our system.

- Research on other implementations of the algorithm and investigate on their performance and efficiency.

- Analyze the algorithm and select the proper parameters for better efficiency.

- Examine the role of the FPGA, to efficiently accelerate the chosen model.

- Implement the design for the system specified.

- Achieve real-time face recognition, with an execution time below 16 ms.

- Obtain high-accuracy, which is equal or higher than 75%, analogous to the accuracy of the state of the art recognition models.

#### 1.4 Thesis Outline

The thesis is organized in the following way. Chapter 2, includes background information regarding this project, helping with its comprehension. In Chapter 3, facial recognition algorithms are presented and a comparison between them takes place in order to determine the most suitable one for our implementation. Next, other implementations of the chosen algorithm on different platforms are presented and their performance is being examined. In Chapter 4, an analysis of the algorithm development takes place. This analysis regards the selection of the most appropriate models and parameters for the

algorithm in order to achieve the best possible result. In Chapter 5, the implementation, itself, is being described thoroughly, from the implementation approach to the last design details . Next, in Chapter 6, experimental results of the implemented design are examined and compared to similar implementations. Finally, in Chapter 7, a summary of our work is given and future work is proposed. Background information relevant to this work will be described in this chapter. The main fields combined in this work are facial recognition and reconfigurable computing. In Section 2.1 an introduction on the first field will be presented. Next, in Section 2.2 some basic concepts of reconfigurable computing will be described. In Section 2.3, the platform utilized in this work, combining the two fields, will be introduced. In the end, in Section 2.4, a conclusion concerning the background information will be presented.

## 2.1 Facial Recognition Systems

A facial recognition system is a computer application, that its purpose is identifying an input face successfully. In Section 1.1, the evolution on the field has been presented, leading to today's complex, but efficient models. Those models, alongside with present accelerated face recognition implementations, will be described, in more detail, in Chapter 3.

Despite the differences (based-model, input form, etc.) every facial recognition system is based on the same outline as follows: Import an input face, extract a set of facial features, match those features to the system's facial features database and finally recognize the face according to the best matching. This procedure can be observed in Figure 2.1.

Figure 2.1: The procedure of face recognition.

In the first part of the system, the facial features, that are going to be extracted, and the process of this extraction, need to be decided. Those features should lead to accurate facial recognition, by being as unique as possible for every different face. For example, the size of the face is not a proper feature, as many faces may have the same size. Moreover, these features should be tolerant to different conditions such as environmental conditions, e.g. lighting, expressions, etc. The process for doing that should be also designed carefully, in order to decrease complexity and maintain a high performance.

Once the facial features, the system utilizes, are decided, a database is constructed. This database consists of the facial features of a number of different persons. Those persons are the ones intended to be identified through the system. The system's memory should be taken in account, so that the size of the database is within its limits.

Next, the matching phase should be designed. The facial features acquired by the input face, need to be compared to all the facial features of the database. As those feature are represented by values in computer applications, distance measures are utilized for this purpose. At the end of this process, a distance is calculated between the test face and each face of the database. The recognition is then finalized by returning the face identification of the minimum distance, also called best match.

Concerning the input and the output of a facial recognition system, they are completely depended on the purpose of the system utilization. The input may vary from continuous video frames, to face images imported from a large database. Same for the output, where a face picture of the matching person or just an identity word (e.g. person's name) might be returned.

In conclusion, the same process is the basis behind every facial recognition systems. Every step of this process differs between different application and should be examined carefully depending on the systems specifications.

#### 2.2 Reconfigurable Computing

The subject of reconfigurable computing will be examined in this section, as it is the basis for the current system design.

In traditional computing, two ways are met for computing algorithms [11]: ASIC (Application Specific Integrated Circuit) and software-programmed processors.

ASICs are used to perform the operations in hardware, that has been designed specifically for the current algorithm. Because of this specific design, the execution time for an algorithm reduces significantly, leading to faster implementations. Therefore, ASICs are proven to be really efficient. The drawback of this determinate design, is that no alteration is feasible after fabrication, making ASICs inflexible.

Processors on the other hand, are characterized by flexibility. The change of instructions leads to a different system functionality, on the same hardware. The cost of this flexibility, though, is much slower execution. The processor must first read each instruction from the memory, translate it, and only then proceed with its execution. This process is resulting in a high execution overhead for each operation.

A need for systems that combine the flexibility of processors and the high performance of ASICs is obvious. Reconfigurable computing is intended to merge those beneficial aspects together. Reconfigurable devices can be configured specifically to execute complex combinational functions, like ASICs, and in addition, this configuration may be altered later on time, providing flexibility, like processors. The most common reconfigurable devices are the Field-Programmable Gate Arrays (FPGAs). Every FPGA consists of a finite number of predefined resources connected with programmable interconnects to implement a reconfigurable digital circuit and I/O blocks to allow the circuit to access the outside world [12], as seen in Figure 2.2.

Figure 2.2: FPGA overview. [12]

Logic blocks, also referred as configurable logic blocks (CLBs), are the basic logic unit of the FPGAs. Those blocks are made up of two primary components: Flip-Flops (FFs) and Look-Up Tables (LUTs). LUTs are a set of gates that are combined together to create an entity of K inputs. This entity is able to perform any K-input function effectively [13], and is therefore the prime unit on FPGA implementations.

FPGAs have evolved radically in the past years. More resources available for configuration are presently included in the FPGAs. Moreover, partial reconfiguration (reconfiguring only a part of the FPGA while the rest is operating) is nowadays feasible. Aside from that, FPGAs have been integrated into platforms and Systems on Chips (SoCs), to exploit their performance, as the benefits derived from their utilization are more and more needed in modern applications.

### 2.3 Topic Development Kit

The integration of FPGAs in complete platforms is common nowadays, as mentioned in Section 2.2. A platform of this type will be utilized for the purposes of this project. This platform is the Topic Development Kit [14] developed by Topic Embedded Systems.

The main component of the platform is the Miami System-on-Module (SoM) assembled on the Florida carrier board, both developed by Topic Embedded Systems. The specifications of the Miami SoM are the primary concern of the current project. The Florida carrier aims on enabling the platform for multiple kinds of development, including many communication interfaces. This is useful for creating practical interaction extensions, but should not concern as in the present.

The Miami SoM includes a Z-7030 SoC from the Zynq<sup>®</sup>-7000 series All Programmable SoCs [15]. Regarding other main features, a DDR3 memory of 512MB is available and 140 pins for interface connections such as UART, JTAG, etc. In more detail, the Z-7030 includes an ARM Cortex-A9 with two cores at 800Mhz, and an FPGA, Kintex<sup>®</sup>-7. All specifications of the the Z-7030 are given in detail in Figure 2.3, for a better overview of the platform. The available resources will be taken more carefully in consideration, during the implementation stages, to achieve the best result. However, in general the resources, as presented, indicate a powerful system that can help towards the project goal of real-time face recognition. Most of those

|                    | Device Name                                          | Z-7030                                                                                     |

|--------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|

|                    | Part Number_                                         | XC7Z030                                                                                    |

|                    | Processor Core                                       | Dual ARM <sup>®</sup> Cortex™-A9 MPCore™ with CoreSight™                                   |

|                    | Processor Extensions                                 | NEON™ & Single / Double Precision Floating Point for each processor                        |

|                    | Maximum Frequency                                    | 866MHz Up to 1GHz <sup>(1)</sup>                                                           |

| ε                  | L1 Cache                                             | 32KB Instruction, 32KB Data per processor                                                  |

| ste                | L2 Cache                                             | 512KB                                                                                      |

| ŝ                  | On-Chip Memory                                       | 256KB                                                                                      |

| , E                | External Memory Support <sup>(2)</sup>               | DDR3, DDR3L, DDR2, LPDDR2                                                                  |

| ess                | External Static Memory Support <sup>(2)</sup>        | 2x Quad-SPI, NAND, NOR                                                                     |

| Processing System  | DMA Channels                                         | 8 (4 dedicated to Programmable Logic)                                                      |

| •                  | Peripherals                                          | 2x UART, 2x CAN 2.0B, 2x I2C, 2x SPI, 4x 32b GPIO                                          |

|                    | Peripherals w/ built-in DMA <sup>(2)</sup>           | 2x USB 2.0 (OTG), 2x Tri-mode Gigabit Ethernet, 2x SD/SDIO                                 |

|                    | Security <sup>(3)</sup>                              | RSA Authentication of First Stage Boot Loader,                                             |

|                    | Security                                             | AES and SHA 256b Decryption and Authentication for Secure Boot                             |

|                    | Processing System to                                 | 2x AXI 32b Master, 2x AXI 32b Slave                                                        |

|                    | Programmable Logic Interface Ports                   | 4x AXI 64b/32b Memory                                                                      |

|                    | (Primary Interfaces & Interrupts Only)               | AXI 64b ACP                                                                                |

| _                  | <b>X</b> <i>I I I</i>                                | 16 Interrupts                                                                              |

|                    | 7 Series Programmable Logic Equivalent               | Kintex®-7 FPGA                                                                             |

| <u>.9</u>          | Logic Cells (Approximate ASIC Gates <sup>(4)</sup> ) | 125K (~1.9M)                                                                               |

| ğ                  | Look-Up Tables (LUTs)                                | 78,600                                                                                     |

| 읭                  | Flip-Flops                                           | 157,200                                                                                    |

| at                 | Total Block RAM (# 36Kb Blocks)                      | 9.3Mb (265)                                                                                |

| Ē                  | Programmable DSP Slices (18x25 MACCs)                | 400                                                                                        |

| Bra                | Peak DSP Performance (Symmetric FIR)                 | 593 GMACs                                                                                  |

| Programmable Logic | PCI Express <sup>®</sup> (Root Complex or Endpoint)  | Gen2 x4                                                                                    |

|                    | Analog Mixed Signal (AMS) / XADC <sup>(2)</sup>      | 2x 12 bit, MSPS ADCs with up to 17 Differential Inputs                                     |

|                    | Security <sup>(3)</sup>                              | AES and SHA 256b Decryption and Authentication for Secure Programmable Logic Configuration |

Figure 2.3: Z-7030 specifications. [15]

### 2.4 Conclusion

In the current chapter, a brief introduction on the background information, needed to comprehend our work, was presented. The basic outline of a facial recognition system was described in Section 2.1. Next, the field of reconfigurable computing was presented in 2.2 and in the end, in Section 2.3 our development kit is presented. The information shared, although it is on an introductory level, is helpful for comprehending the work carried out later.

In the current chapter the background of facial recognition models and implementations will be examined. Firstly, in Section 3.1, the most dominant algorithms for achieving recognition, the basis of facial recognition systems, are presented and compared. This way the most suitable algorithm will be chosen for our implementation. Second, in Section 3.2, implementations of the selected algorithm in different platforms will be shown and their performance will be discussed. Finally, in Section 3.3, conclusion for the current chapter will be derived.

### 3.1 Facial Recognition Algorithms

The groundwork for any face recognition system is the algorithm that is responsible for recognizing a face. As seen in Chapter 2.1, the process of recognizing a face is first extract features from a probe face and then, use this features to match this face to a face in the existing database. Therefore, we can distinguish two parts: features extraction and matching. All the recognition algorithms focus on the first part, as the matching can be done efficiently with presently existing distance measures for any of the features. Different kind of features have been proposed for efficient face recognition, from simple geometrical features, to high contrast values existence.

After a research around the subject a number of different algorithms that can be utilized were found. The most dominant ones should be examined and compared in order to conclude to the algorithm that our system is going to utilize. The algorithms that were found to be the most promising and are going to be examined are: Eigenfaces, Fisherfaces, Elastic Bunch Graph Matching (EBGM), Local Binary Patters Histograms (LBPH), Scale Invariant Feature Transform (SIFT).

#### 3.1.1 Eigenfaces

The eigenfaces method for recognizing faces was introduced in 1991 [3] and it is based on principal component analysis (PCA) [16], where a set of possibly correlated values is converted to set of linearly uncorrelated values. This way the amount of values needed is decreased significantly. This method enabled for the first time reliable, automated, realtime face recognition systems. The basic idea of the method is to utilize the eigenvectors (eigenfaces) of faces, as the linearly uncorrelated values, to distinguish them.

More specifically, a number, K, of gray-scaled images of size MxN that will form the database are needed. Each of these images will be represented as a vector,  $I_K$ , of size Ix(MxN). Having all those images the mean image, AI, is calculated

$$AI = \frac{\sum_{k=1}^{K} I_k}{K}$$

and also the deviance for each of the images.

$$ID_K = I_K - AI$$

Next, the all the vectors,  $ID_K$ , are merged into matrix A of size Kx(MxN). Matrix C is then calculated

$$C = AA^T$$

and the eigenvectors and eigenvalues of the matrix are calculated. A number, i, of eigenvectors, corresponding to the highest eigenvalues, depending on the size of information needed is maintained. Those eigenvectors,  $E_i$ , correspond to faces called eigenfaces. Such eigenfaces can be viewed in Figure 3.1

Figure 3.1: Different eigenfaces corresponding to varying eigenvalues [17]

The eigenfaces,  $E_i$ , are then used to find a set of weights,  $w_{ki}$  for each image.

$$w_{Ki} = I_K * E_i$$

These weights represent the contribution of each eigenface in forming the original image. So in the end each image is described by a set of weights.

A probe image,  $I_P$ , is then needed to be identified. The weights,  $w_{KP}$ , of this image are calculated the same way. Finally, a distance measure is used (e.g. Euclidean Distance) to find the distance between the probe image's weights and the weights of each of the database images. After the distances between all images have been calculated, the one with the smaller number leads to the best face match and identification is completed.

The research indicates that 40 eigenfaces are enough to succeed with recognition. This way the database has to consist of 40 eigenfaces and 40 weights for each of the images that we want to include in. Also we can observe that for every probe image the computations are simple to lead to recognition, with the matrix multiplications being the most intensive part. Eigenfaces ,though, is not so effective under different light conditions and expressions. Generally, it performs well under controlled conditions which are difficult to get in everyday life environments.

#### 3.1.2 Fisherfaces

Fisherfaces [4] is another popular face recognition algorithm. It was developed in 1997 and it is based on Fisher's Linear Discriminant [18], a method used to find a linear combination of features that characterizes classes of objects. Many similarities can be reported between Eigenfaces and Fisherfaces as both are based on linearly projecting.

More in detail, once again, a number, K, of gray-scaled images of size MxN, represented as vectors,  $I_K$ , that will form the database are used. In addition we categorize those images into a number of classes, c. This categorization is usually done by including the images of the same person in the same class. With all those images the average image, AI, is calculated

$$AI = \frac{\sum_{k=1}^{K} I_k}{K}$$

Also the average image,  $AI_c$  for each class is calculated

$$AI_c = \frac{\sum_{c=1}^{size} I_c}{K}$$

where *size* is the size of the class and  $I_c$  are the images included in the class. Each class' mean image deviation from the mean image,  $CD_c$ , can now be calculated.

$$CD_c = AI_c - AI$$

The deviation of the images inside a class from the class' mean image,  $I\!D_c$  , is also calculated.

$$ID_c = I_c - AI$$

Two merged matrices are then created, A which includes  $CD_c$  for all classes and B which includes  $ID_c$  for all classes. Using A and B the relative eigenvectors, E and eigenvalues, l, are calculated.

$$(AA^T)E = l(BB^T)E$$

From this point on we proceed as in eigenfaces. A number, i, of eigenvectors depending on the eigenvalues is maintained. Those eigenvectors correspond to images called fisherfaces, Figure 3.2 shows such fisherface. The weights for each image are once more calculated.

$$w_{Ki} = I_K * E_i$$

Whenever a probe image is inserted the same recognition procedure is followed as in eigenfaces for calculating its weights and the image with the closest weight values is marked as the best match, completing the identification process.

A problem that might be encountered while using fisherfaces, is when the classes are more than the images. To override this issue, when fisherfaces is used, the sample vectors are projected onto the PCA space used in eigenfaces and the fisherfaces are then computed in this PCA.

A system utilizing fisherfaces will need the same size database as in eigenfaces, 40 fisherfaces and 40 weights per image in the database. Moreover, the recognition process calculations are the exact same as in eigenfaces. Creating the database is the only part

Figure 3.2: Fisherface derived from a face image in the Yale Database [4]

that requires more calculations, but as stated in Section 1.2, it should not concern the current project.

Regarding, the accuracy of the algorithm, we can observe that fisherfaces enables classification, which can improve accuracy noticeably. A database that includes a person's images under different lightning or expression conditions can make the algorithm insensitive to those changes. More images of a person under different conditions lead to better results. This way a probe image, taken in a random environment, can be recognized correctly.

#### 3.1.3 Elastic Bunch Graph

Elastic Bunch Graph Matching (EBGM) [5], developed in 1997, is a biologically inspired algorithm utilized for recognition in the field of computer vision. This biological inspiration [19] can be derived by ,first, the visual features used are based on Gabor wavelets, which have been found to be a good model of early visual processing in the brain, more precisely simple cells in primary visual cortex and second, the matching algorithm itself is an algorithmic version of dynamic link matching (DLM) [20], which is a model of invariant object recognition in the brain.

Regarding the functionality of the algorithm, a set of database images is needed. Each image of the DB is represented with a graph of nodes and edges. The edges are labeled with the distance in between the nodes and the nodes are labeled with jets, as seen in Figure 3.3. A jet [5] describes a small patch of grey values in an image  $I(\vec{x})$ around a pixel  $\vec{x} = (x, y)$ . It is based on a wavelet transform, defined as a convolution

$$J_j(\vec{x}) = \int I(\vec{x'}) y_j(\vec{x} - \vec{x'}) d^2 \vec{x'}$$

with a family of Gabor Kernels  $y_j$ . Those Gabor Kernels are employed for different frequencies and orientations. This way, all kernels are being generated from one *mother* wavelet by dilation and orientation.

The number and position of the nodes selection is done customarily, but is based on covering key characteristics of the face. For example, as seen in Figure 3.4, four nodes can be selected, two of them being positioned in the center of the eyes and the other two in the edges of the mouth. For face recognition it is suggested that the nodes are

Figure 3.3: An image graph with a jet seen on the left [5]

placed in the inner face and not in the outline, as the recognition is based mainly on these features. The outline is used mainly for face detection.

Figure 3.4: Positioning four nodes and six edges applied in a face image.

When nodes and edges, which are of the same number for all images, have been placed and labeled for every picture in the database, the average position of the nodes is being calculated. A face bunch graph can be then created, as seen in Figure 3.5, where the nodes are positioned in the average position and labeled with all images' jets. The set of jets in a node is called a bunch.

A probe image, to be recognized, is then inserted in the system. Initially the nodes are placed in the average position calculated before. The exact correct position of the nodes is then searched. To perform this, the jets for a region nxn around the given positions are calculated. A similarity function, utilizing values distance, is then used to define which jet position is more accurate. This way the right positions of the nodes are found and the jets are being calculated. The identification of the image is then taking

Figure 3.5: A face bunch graph.

place. The difference in the jets' values between the probe image and the database image is found and the smaller one is marked as a best match. Edges length can be also utilized in case of more than one close match.

The database for such a system depends on the number of images and the number of the nodes per image. Most researches select this number in the range 10-40. We can see, this way, that the database takes up small size. The calculations, though, needed to identify a probe image are of high number. This has to do, mainly, with finding the accurate position of the nodes, as the jets have to be calculated for every pixel in a frame *nxn* around each node. This increases significantly the calculations. Finally, the accuracy of the algorithm depends directly on the variety of images of a person in the database. Grids for different face rotations have to be included for the algorithm to be insensitive to rotations, as seen in Figure 3.6. Also pictures of different environmental conditions have to be included to effectively identify a probe image. This way the database size can increase remarkably. However, if all these specifications are followed the algorithm can achieve very high accuracy.

#### 3.1.4 Local Binary Patterns Histograms

The Local Binary Patterns Histograms (LBPH), proposed in 2006 [6], is another algorithm used for face recognition, that is based on the local binary operator [21]. It is a very popular algorithm used widely because of its discriminative power and computation simplicity [22].

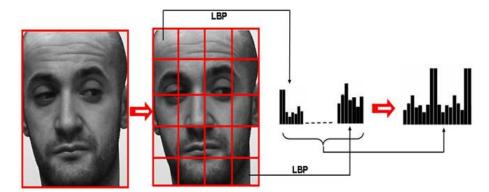

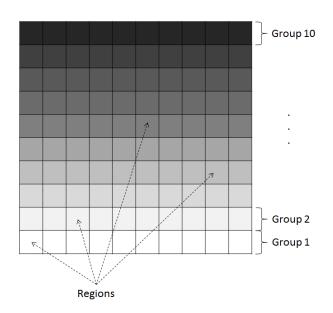

In more detail, a number k of gray-scaled images, sized NxM, is used as the database. First each image is split into sections. Usually the same size for splitting is used, in both width and height, resulting in mxm sections. Then for each image a histogram is calculated.

In each section the local binary operator is utilized. This operator, applied in images, compares a pixel to its eight neighbors. This comparison checks if the neighbor pixel is

Figure 3.6: Different grids for rotated faces.

higher than the current pixel and if so, is labeled with '1' otherwise is labeled with '0'. Applying this to all 8 neighbors we end up with 8 binary values. Merging those values in a single number we have formed an 8-bit binary number that can be translated to a decimal number in the range 0-255. This operation can be observed in Figure 3.7. This process is done for every pixel in the section. Other variations of the algorithm, perform the operator in more neighbors or even in different distance from the center pixel, increasing in sometimes the accuracy.

Figure 3.7: LBP operator example.

The histogram for the current section is then created by calculating how many times a value appears in this section. This way, the histogram for each section consists of 256 bins. This can be summed up to the following equation

$$H_i = \sum_{x,y} I\{LBP(J(x,y)) = i\}, i = 0, ..., 255$$

where  $H_i$  is the bin of value *i*, J(x, y) is the (x, y) pixel of the image and *I* is an *if* operator returning '1' if the statement is true or '0' otherwise. When the histograms for all sections have been calculated a single histogram is create by unifying all the histograms for each section as seen in Figure 3.8. This final histogram will contain 256 \* m \* m bins and is defined as the feature vector of the image.

Figure 3.8: Process of creating the final histogram [22]

An image seeking recognition is now ready to enter our system. The same process is followed for this image to derive its own histogram. Once the histogram is retrieved, it is compared to the database's histograms and the closest match is identified, finishing the recognition process. Weights in different sections of the pictures can be added in this process. Sections that include important features (e.g. eyes, mouth) should be taken in more account when we try to find the closest match, and weights enable that.

An important extension of the algorithm is using classification. This way images of the same person can be added in the same class. When the comparison between the histograms of the database takes place, the distance from all the pictures in a class is averaged.

$$\Delta_n = \frac{\sum_{i=0}^s \delta_i}{s}, n = 0, \dots, N$$

where  $\delta_i$  is the difference between image's *i* histogram, s = size of class and N = number of classes. The probe image takes in account all pictures of a single person and not just one. This way the algorithm becomes more robust in different environmental conditions.

Two other extensions that are often seen, reduce the bins used in the histograms. The first one [23], introduces the uniform patterns. Uniform patterns consist only of the values with up to 2 spatial transitions (bit wise 0/1 changes) in the binary vector. For example 00001100, 11110001 (2 transitions) are uniform patterns where 00110011 (4 transitions) and 01010111 (6 transitions) are not. Using only uniform patterns, the histogram bins reduce from  $2^P$  to P(P-1) + 2 for a P neighbor implementation. The second implementation [24], reduces the feature vector by considering the values retrieved from the LBP operator and their complements as equal (e.g. 11110000 and 00001111). This way the bins in each histogram reduce from  $2^P$  to  $2^{P-1} + 1$ . Both implementations are very useful when the feature vectors need to be of small size and in addition robustness has been reported to environmental alterations in some cases.

Having said that, it is now obvious why this algorithm is preferred very often. The calculations are simple consisting mostly of simple pixel comparison. Also the database is small in size depending on number of sections per image and the number of images, size = Images \* Sections \* 256. Moreover, the LBP operator adds insensitivity to different illumination increasing the accuracy rate. Finally, through classification robustness is added to other conditions.

#### 3.1.5 Scale Invariant Feature Transform

Scale Invariant Feature Transform (SIFT) [7] is an algorithm developed in 1999 for object recognition, but has been applied effectively for face recognition as well. Its main functionality is point matching between different views of a 3-D scene and view-based recognition. SIFT is invariant to translations, rotations and scaling transformations and robust to moderate perspective transformations and illumination variations. Experimentally, the SIFT descriptor has been proven to be very useful in practice for image matching and object recognition under real-world conditions [25].

The algorithm can be divided into two parts. In the first part, keypoints of an image are found. In the second part, feature vectors for this points are calculated. So, having a database of images in our system the keypoints of the images are found first.

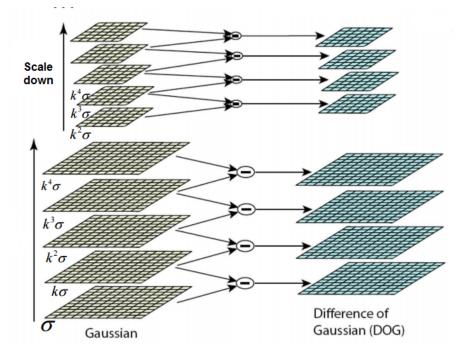

The keypoints need to be invariant with respect to image translation, scaling, and rotation, and are minimally affected by noise and small distortions. The Gaussian kernels and next the difference of Gaussian function (DOG) in scale space are applied for this reason first, as they are the only smoothing kernels for scale space analysis [26]. For the first scale, each image is convolved with the Gaussian function in both axis.

$$G(x,y;k\sigma) = \frac{1}{2\pi k^2 \sigma^2} e^{(-x^2 + y^2)/(2k^2 \sigma^2)}$$

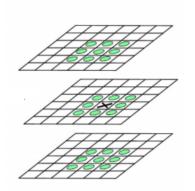

Four convolutions for  $k, k^2, k^3, k^4$  are performed in order to receive 3 DOGs. In this space maxima and minima are found. This is done by selecting pixels that are smaller or bigger than their 26 neighbors in the 3-D space. Those 26 neighbors are represented in Figure 3.9.

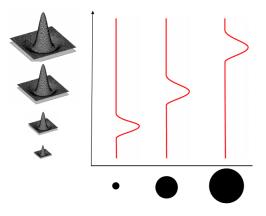

Next the image is scaled down. Billinear Interpolation is used in this stage to achieve correct scaling. Four convolutions with the Gaussian kernels are once more taking place but with  $k^2, k^3, k^4, k^5$  this time. The minima and maxima are found in this scale DOG space as well. This process is repeated depending on how large the scale space needs to be. An overview of the process to receive the DOGs is shown in Figure 3.10.

After all this process a number of key points, that can be represented as different size blobs depending on the scale they correspond (Figure 3.11), has been found. An example image with keypoints is presented in Figure 3.12. The second part of the algorithm, for finding feature vectors for those key points, kicks in. For each keypoint, the magnitude M and orientation R for each pixel in a 16x16 neighborhood (neighborhood size can be

Figure 3.9: Neighbors of a pixel in the 3-D space [27]

extended depending on the design) are computed:

$$M_{ij} = \sqrt{(A_{ij} - A_{i+1,j})^2 + (A_{ij} - A_{i,j+1})^2}$$

$$R_{ij} = atan2(A_{ij} - A_{i+1,j}, A_{i,j+1} - A_{ij})$$

Figure 3.10: Process to reach DOGs in keypoint exploration [27]

By calculated magnitude and orientation, robustness in size and rotation is added. Moreover with utilizing neighbor pixels the algorithm can be invariant to illumination

Figure 3.11: Keypoints represented as different size bolbs depending on the scale [27]

Figure 3.12: Keypoints example of an image [25]

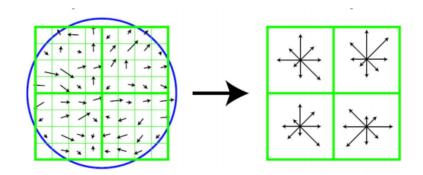

changes as well. Moving on, the 16x16 space is split into four 4x4 sections. In each of these sections an 8 bin histogram is calculated. Each bin corresponds to one direction  $0^{\circ}, 45^{\circ}, ..., 315^{\circ}$  and the value of each bin is the addition of magnitudes for this orientation. The directions used, therefore the bins, may be of a higher number depending on how the algorithm is designed. The highest values direction is usually used to represent the orientation of the keypoint. This way, for each keypoint four 8-bin histograms are calculated (Figure 3.13). The unity of this histograms constitute the feature vector of this keypoint.

When a test image is inserted in the system the keypoints and feature vectors of the keypoints are calculated. The keypoints are then compared to the database images' keypoints and the one with the most matching keypoints is identified as the best match.

The SIFT algorithm introduces invariance in many different levels making it a very accurate recognition solution. A database for a system utilizing SIFT is small in size and depends on the keypoints per image, the orientations we want to include in the histograms and the images we will include. The computations, though, to recognize a test image are exceeding by far the calculations needed by other recognition algorithms. For extracting feature vectors, a series of convolutions, interpolations and summations are needed, making the algorithm really intensive. Moreover, this level of invariance is

Figure 3.13: Creating a histogram for a 16x16 neighborhood using magnitude and orientation values [27]

not needed in face recognition, as rotation and size variations are inside a certain range, contrary to object recognition. This way, the cost of the calculations is not reflected in the results' difference.

### 3.1.6 Algorithms Comparison

The most dominant algorithms for face recognition have been described in Sections 3.1.1-3.1.5. Their main functionality was explained briefly in order to understand the needs of each algorithm in calculations power, in database size, etc. Those algorithms have been implemented in the past and experimental results have been retrieved. In this section a comparison between them will be attempted in order to conclude to the algorithm that is most suitable for our implementation.

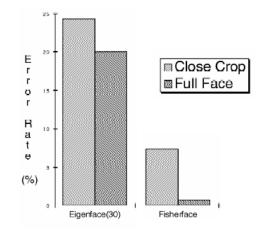

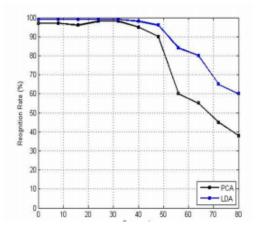

A comparison between the first two algorithms Eigenfaces and Fisherfaces is presented first, as those two algorithm have lots of common ground. In the first introduction of Fisherfaces [4], an extensive comparison between the two algorithms is reported. In all of the experiments the fisherfaces outperforms eigenfaces. The error rate difference is reaching even 30% in favor of fisherfaces, for complex image subsets. In Figure 3.14 the error rate for the algorithms is presented when the Yale face database is utilized, which contains variation in facial expression and lighting. It is obvious through this graph the difference between the two algorithms. Moreover, in [28], another comparison between the two algorithms is presented. In this research, the two algorithms are tested in different pose variations and the fisherfaces outperforms eigenfaces. Figure 3.15 shows the accuracy rate for different pose angle for the two algorithms. It has been clear that fisherfaces is a more accurate algorithm than eigenfaces. Also, the calculations needed for recognizing a face are of the same exact number for both algorithms, consisting of multiplying the probe image with the number of fisherfaces or eigenfaces. The database also is of the same size for both of them.

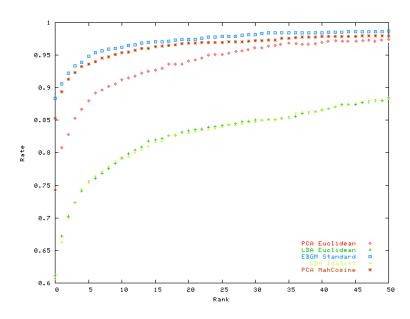

EBGM is examined next. The algorithm's accuracy was compared to different versions of eigenfaces and fisherfaces in the FERET Database which contains different subsets. The accuracy rate is checked for different ranks. In this point we should define rank as the number of best-matching images among which the correct answer is found. Rank is used oftenly to evaluate face recognition systems. In all of those experiments

Figure 3.14: Error rate of fisherfaces and eigenfaces in Yale Database [4]

Figure 3.15: Fisherface (LDA) and eigenface (PCA) accuracy rates for different pose angles [28]

EBGM outperforms the other algorithms. In Figure 3.16 we can see the results for the fafb subset, images with alternative facial expression, and in Figure 3.17 the results for the dup2 subset, images taken in different time under different conditions. In both cases we observe the better accuracy of EBGM. Concerning the database needed for EBGM, is at the same size as the other compared algorithms. The drawback of EBGM is the heavy calculations needed for the probe image as described in Section 3.1.3 which may lead to a huge lateness.

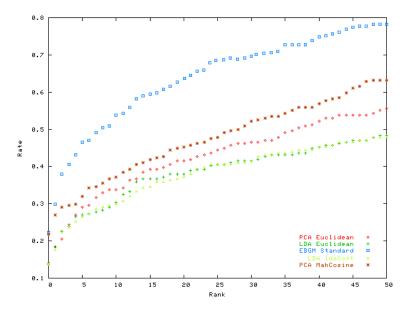

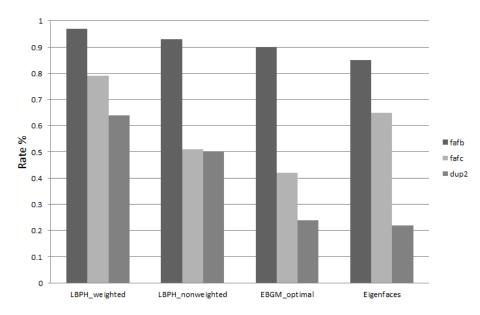

Next, LBPH is investigated. We will concentrate on Ahonen's work [6], where an extensive comparison to the already proposed algorithms is being performed. LBPH is more accurate than the other algorithms in all of the experiments. Figure 3.18 we can see the performance of LBPH, with and without weights added (see Section 3.1.4), Eigenfaces, and EBGM optimal which is a better extension of EBGM. The experiments performed in the Feret database for the fafb (images taken with different expressions), the fafc (images taken with different illuminations), dup2 (images taken in different times

Figure 3.16: EBGM, fisherfaces and eigenfaces comparison in Feret Database, faß subset [29]

Figure 3.17: EBGM, fisherfaces and eigenfaces comparison in Feret Database, dup2 subset [29]

and conditions). For all subsets even the non weighted LBPH outperforms the other algorithms. Compared to EBGM, weight LBPH can report differences up to 40% for complex databases. Furthermore, the calculations needed for recognizing a test image are much less compared to EBGM, while the databases of LBPH systems remain in the same small size.

Finally, the SIFT algorithm is compared to the other models. As reported in Section 3.1.5 is a very accurate algorithm. Many researches, conducted through time, confirm

Figure 3.18: LBPH, EBGM and Eigenfaces comparison in fafb, fafc and dup2 subsets [29]

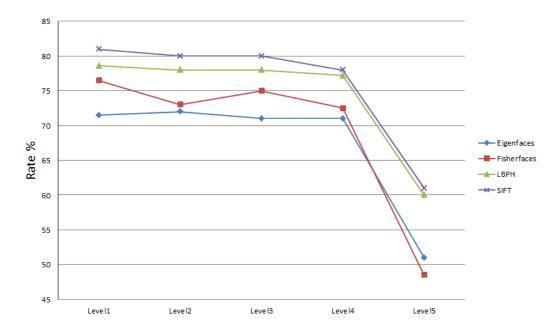

this[30] [31]. SIFT achieves higher accuracy rates outperforming all the other algorithms. In Figure 3.19 the accuracy rate for different image compression levels in an open universe environment are presented. SIFT results are better with a big difference compared to fisherfaces and eigenfaces methods. In comparison to LPBH, although the difference is much smaller with an average of 1.64%, SIFT is still returning better accuracy. Comparing the database size of SIFT utilizing systems to that of the other algorithms, similar size is reported. SIFT calculations though for recognizing a probe image exceed those of the other algorithms.

Below, Table 3.1 we give a brief estimate of the database size for the different models. In the features column we present the parameters for which the calculations are done. Those parameters are average approach and are used to have a general comparison. Also the image size is MxM and N images are used in the database. Also for every feature value we choose the 16 bits representation (2 bytes) as the range 0-65535 is adequate. In Table 3.2, an example database size is given for 100 images of size 100x100. We observe that the sizes range from 49kb to 800kb which are very small values. As reported in Section 1.2, 100 images would be included in our database as well, making this example very useful. Although there are variations between the different algorithms, the size remains insignificant to affect directly our algorithm choice.

The calculations needed in average for each algorithm to extract the required features are presented as well. This is a very important part, as we do not want the calculation to be very complex in order to be translated to a low level logic effectively. Furthermore less intensive algorithms are also preferable to reduce the lateness boundary. As seen in Table 3.3 Eigenfaces, Fisherfaces and LBPH require the simplest and less calculcations of all algorithms containing matrix multiplications, additions and substractions. EBGM and SIFT need a large numbers of calculations which are also complex as convolutions are needed. SIFT specifically requires a huge amount of calculations that exceed by far

Figure 3.19: Eigenfaces, Fisherfaces, LBPH and SIFT comparison for images with different compression level [30]

| Algorithm   | Parameters                          | Database size (bytes) |

|-------------|-------------------------------------|-----------------------|

| Eigenfaces  | 10 Eigenfaces used                  | 10*MxM*2+N*10*2       |

| Fisherfaces | 10 Fisherfaces used                 | 10*MxM*2+N*10*2       |

| EBGM        | 10 Nodes used and 5 orientations, 5 | 10 * 5 * 5 * N * 2    |

|             | frequencies used in the Gabor       |                       |

|             | Kernels                             |                       |

| LBPH        | 16 sections used                    | 16 * 256 * N * 2      |

| SIFT        | Average 20 keypoints, 4 neighbor    | 20 * 4 * 8 * N * 2    |

|             | sections used                       |                       |

Table 3.1: Algorithms' Database Size

the simple calculations of Eigenfaces, Fisherfaces and LBPH.

The distance calculations for matching the probe image are not presented as they

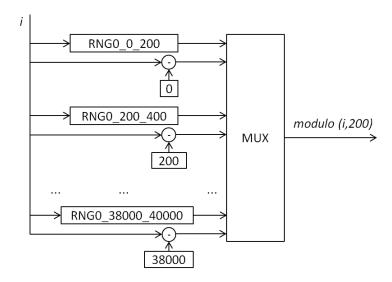

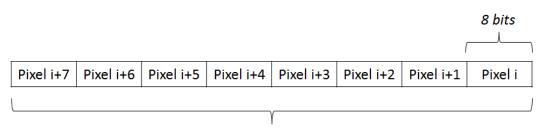

Table 3.2: Database size for 100 images of size 100x100