# Ultra Linear Low-loss Varactors & Circuits for Adaptive RF Systems

Cong Huang

## Ultra Linear Low-loss Varactors & Circuits for Adaptive RF Systems

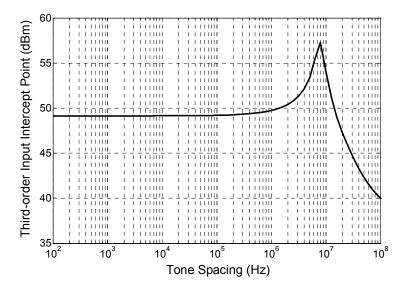

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus Prof. ir. K. C. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 8 maart 2010 om 12:30 uur

door

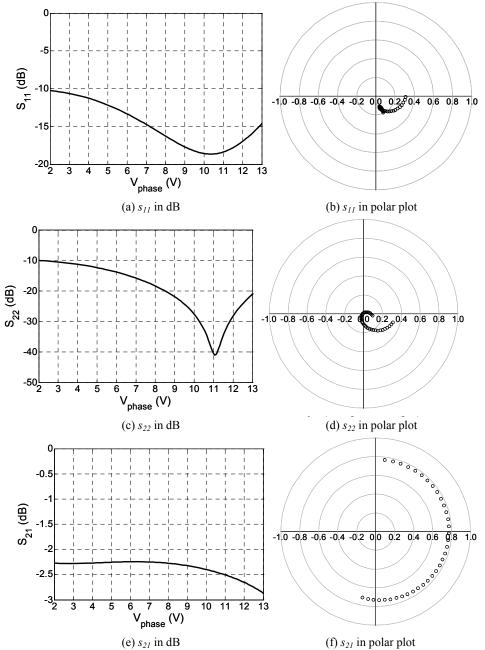

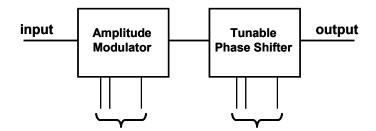

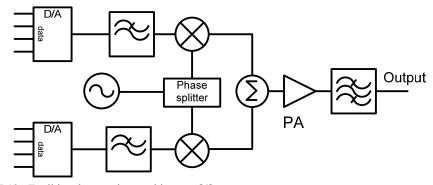

Cong HUANG

elektrotechnisch ingenieur Master of Science van Fudan University, Shanghai, China geboren te Shanghai, China Dit proefschrift is goedgekeurd door de promotor: Prof. Dr.-Ing. J. N. Burghartz

Copromotor: Dr. ing. L. C. N. de Vreede

Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof. Dr.-Ing. J. N. Burghartz, Technische Universiteit Delft, promotor

Dr. ing. L. C. N. de Vreede, Technische Universiteit Delft, copromotor

Prof. dr. L. E. Larson, University of California, San Diego (USA)

Prof. dr. ir. F. E. van Vliet, Universiteit Twente

Prof. dr. J. R. Long, Technische Universiteit Delft

Prof. dr. ir. L. K. Nanver, Technische Universiteit Delft

Dr. ir. H. C. de Graaff, adviseur

Reservelid: Prof. dr. ir. P. M. Sarro, Technische Universiteit Delft

The work described in this thesis was supported by NXP, The Netherlands, Skyworks' Solutions, Newbury Park, USA, and the Delft University of Technology.

Cong Huang, Ultra Linear Low-loss Varactors & Circuits for Adaptive RF Systems, Ph.D. Thesis Delft University of Technology, with summary in Dutch.

ISBN: 978-90-8559-922-7

Copyright © 2010 by Cong Huang

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means without the prior written permission of the copyright owner.

Printed by Optima Grafische Communicatie, Rotterdam, The Netherlands.

To My Family

### Contents

### 1 Introduction

| 1.1 | From B  | eacon Tower to Mobile Phone                  | 1 |

|-----|---------|----------------------------------------------|---|

| 1.2 | The Ne  | ed for Linear RF Tunable Components          | 3 |

|     | 1.2.1   | Adaptive Impedance Control                   | 4 |

|     | 1.2.2   | Adaptive Power Control                       | 5 |

|     | 1.2.3   | Adaptive Multi-band Multi-mode Radio Systems | 6 |

|     | 1.2.4   | Amplitude and Phase Modulators               | 8 |

| 1.3 | Outline |                                              | 9 |

### 2 Review of Tunable Components

| 2.1 Introduction ·····                                    | 13 |

|-----------------------------------------------------------|----|

| 2.2 Currently Available Tunable Elements                  | 13 |

| 2.2.1 Thin-Film Barium Strontium Titanate (BST) Varactors | 13 |

| 2.2.2 MEMS Based Switches and Varactors                   |    |

| 2.2.3 Conventional Semiconductor Based Varactors          |    |

| 2.2.4 Semiconductor Based Switches                        |    |

| 2.2.5 Modern Semiconductor Based Varactors                |    |

| 2.3 Discussion on Current Varactor Topologies             |    |

### 3 Ultra Linear Low-loss Varactor Diode Configurations for Adaptive RF Systems

| 3.1 Introduction                                                    | · 23 |

|---------------------------------------------------------------------|------|

| 3.2 Theory of Operation                                             | · 24 |

| 3.3 Doping Profile and Performance Compromise                       | · 26 |

| 3.3.1 Doping Profile ······                                         | · 26 |

| 3.3.2 Varactor Diode Performance Tradeoffs                          | · 29 |

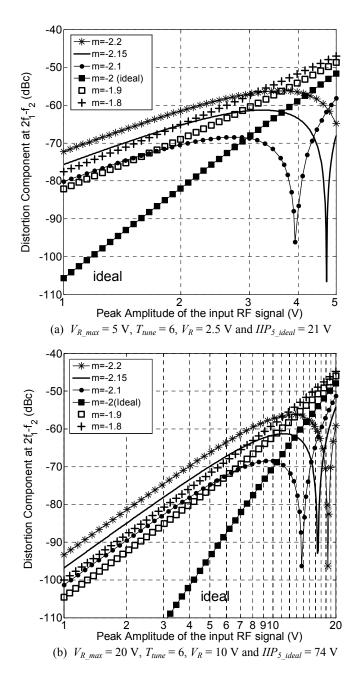

| 3.4 The Influence of $IM_5$ on the Linearity                        | · 31 |

| 3.4.1 Fifth-order Volterra Series Analysis                          | · 31 |

| 3.4.2 Tradeoff between Linearity, Quality factor, $V_{R_{max}}$ and |      |

| Effective Tuning Range                                              | · 32 |

| 3.4.3 Influence of Center-Tap Impedance on Linearity                | · 35 |

| 3.5 The Influence of Process Variation on Linearity                 | · 36 |

i

|   | 3.5.1 Process Tolerance                                                     | 36       |

|---|-----------------------------------------------------------------------------|----------|

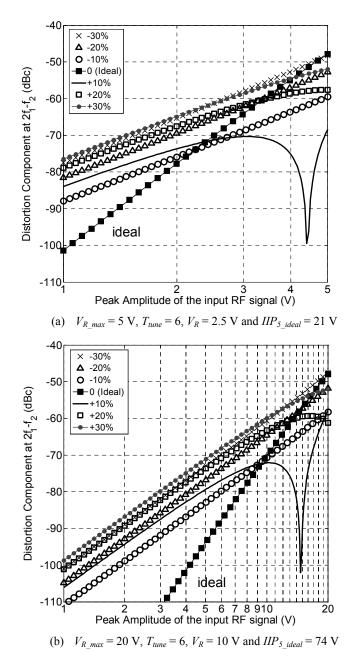

|   | 3.5.2 The Influence on Linearity due to Process Deviation of                |          |

|   | the Power Law Exponent ( <i>m</i> )                                         |          |

|   | 3.5.3 Effect of Spacer Layer Thickness ( $x_{low}$ ) Variation on Linearity | 39       |

|   | 3.6 Wide Tone-Spacing Varactor Stack                                        |          |

|   | 3.6.1 Third-Order and Even-Order Distortion Cancellation                    |          |

|   | 3.6.2 Influence of Fifth-Order Distortion on Linearity                      |          |

|   | 3.6.3 Influence of Center-Tap Impedance on Linearity                        | 44       |

|   | 3.7 Conclusions                                                             | 47       |

| 4 | Comparison of the Varactor Configurations                                   |          |

|   | 4.1 Varactor configurations and their Performance in General                | 51       |

|   | 4.2 Varactor as Linear Modulator                                            | 56       |

|   | 4.3 Multi-stacked varactors for Improved Power Handling and Linearity       |          |

|   | 4.4 System-level Linearity Comparison                                       | 64       |

|   | 4.5 Conclusions                                                             | 70       |

| 5 | Technology Implementations and Experimental Results                         |          |

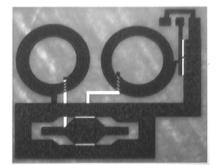

|   | 5.1 Technology Implementations                                              | 74       |

|   | 5.1.1 Silicon-on-Glass Technology                                           |          |

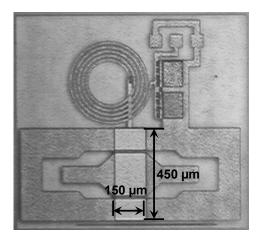

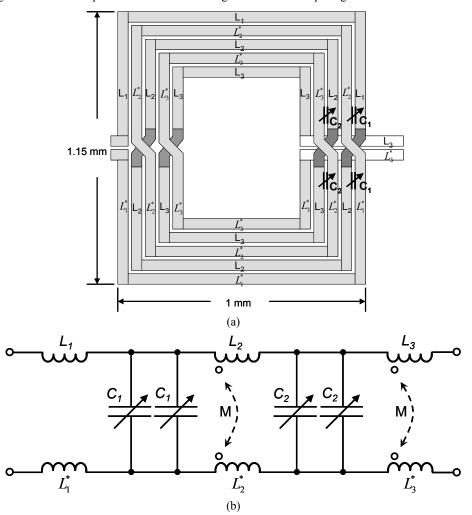

|   | 5.1.2 Finger based implementation of the varactor stack                     |          |

|   | 5.1.3 Micromachined Back-side Contacted Varactor Stack                      |          |

|   | 5.2 Experimental Results of the Silicon-on-Glass (SOG) Low-voltage          |          |

|   | Varactor Devices                                                            | ····· 78 |

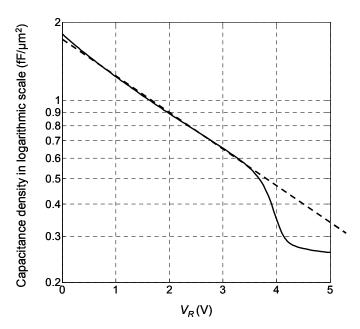

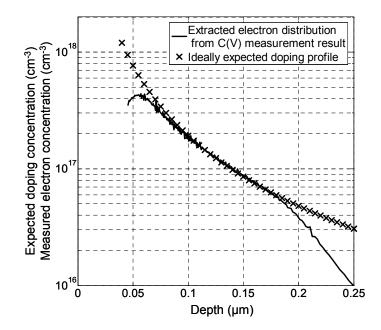

|   | 5.2.1 Measurement of the $C-V_R$ Dependence and Doping Profile              |          |

|   | for the SOG Low-voltage Varactor Diode                                      | ····· 78 |

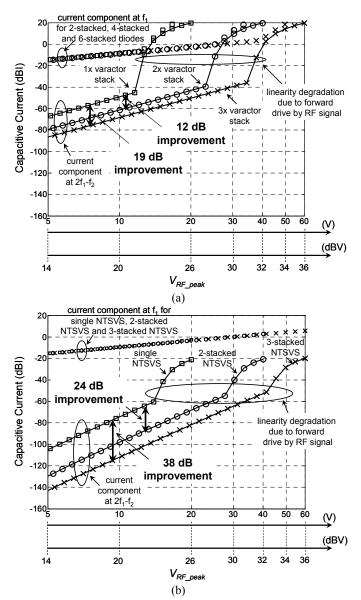

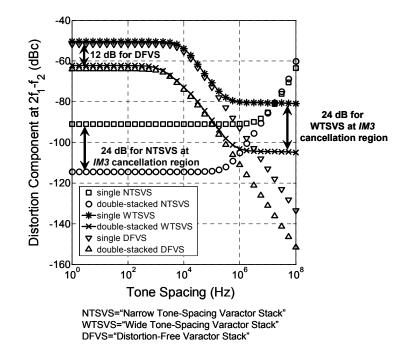

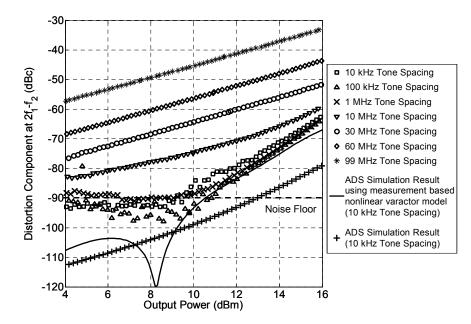

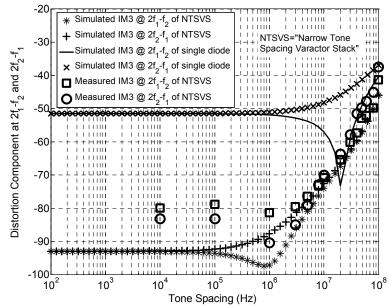

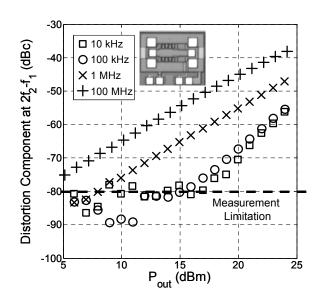

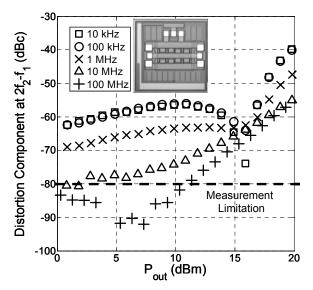

|   | 5.2.2 Linearity Measurements of the SOG Low-voltage Devices                 | 80       |

|   | 5.3 Experimental Results of the SOG High-voltage Varactor Devices           | 82       |

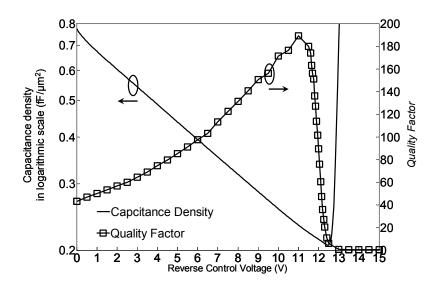

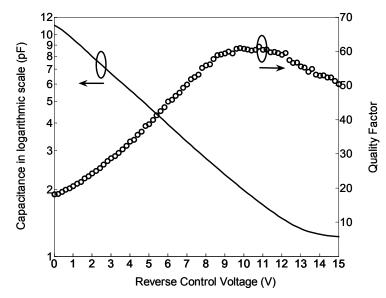

|   | 5.3.1 Measurement of the $C-V_R$ and $Q-V_R$ Dependence for the             |          |

|   | SOG High-voltage Varactor Diode                                             | 82       |

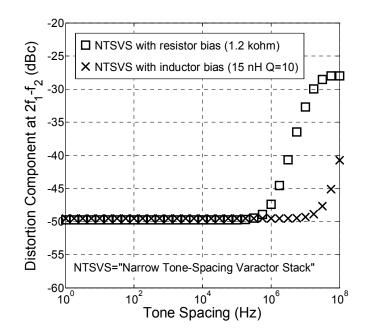

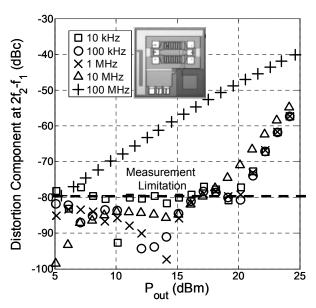

|   | 5.3.2 Linearity Measurements of the Narrow Tone-spacing                     |          |

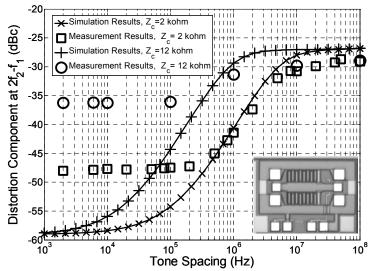

|   | Varactor Stack using SOG High-voltage Varactor Diodes                       | 83       |

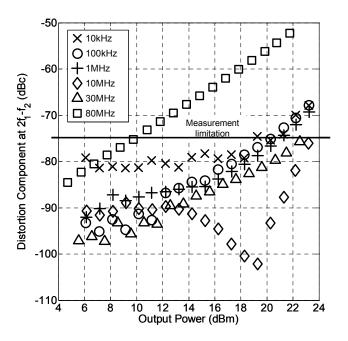

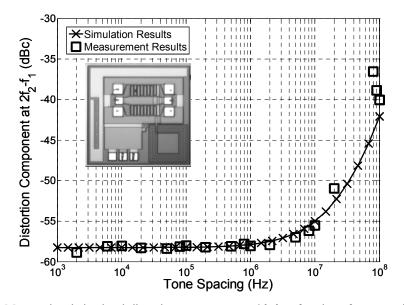

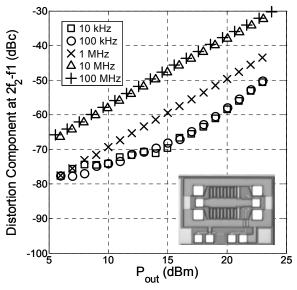

|   | 5.3.3 Linearity Measurements of the Wide Tone-spacing                       |          |

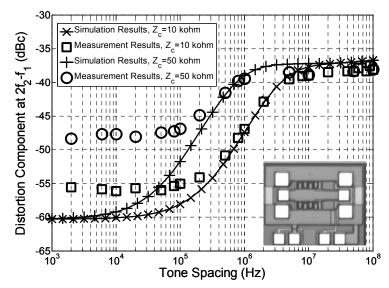

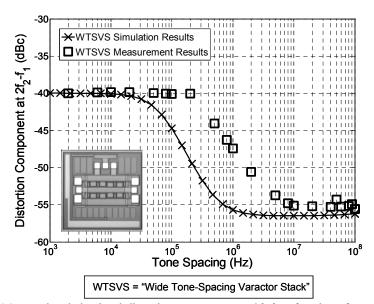

|   | Varactor Stack using SOG High-voltage Varactor Diodes                       | 87       |

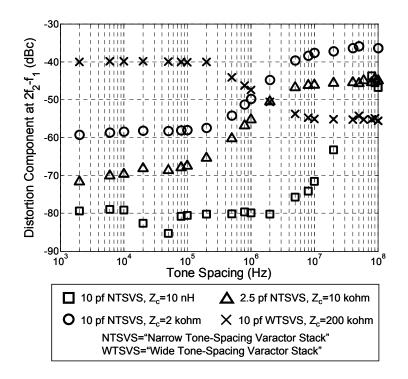

|   | 5.3.4 Overview of the Narrow Tone-Spacing Varactor Stack                    |          |

|   | and the Wide Tone-Spacing Varactor Stack                                    | 89       |

|   | 5.3.5 Measurement of the Multi-stacked Narrow Tone-Spacing                  |          |

|   | Varactor Stack using SOG High-voltage Varactor Diodes                       | 90       |

ii

| 5.4 Experimental Results of the GaAs Large-tuning-range Varactor |     |

|------------------------------------------------------------------|-----|

| Devices                                                          | 92  |

| 5.4.1 Measurement of the $C-V_R$ and $Q-V_R$ Dependence for the  |     |

| GaAs Large-tuning-range Varactor Diode                           |     |

| 5.4.2 Linearity Measurements of the GaAs Large-tuning-range      |     |

| Varactors·····                                                   |     |

| 5.5 Conclusions                                                  | 100 |

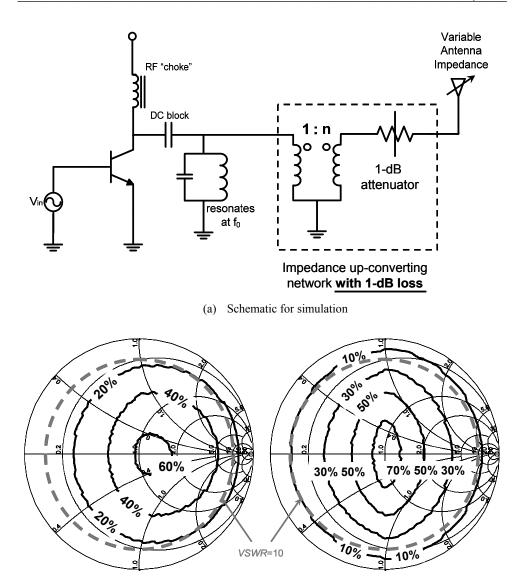

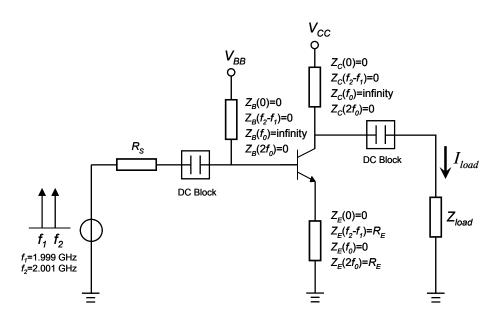

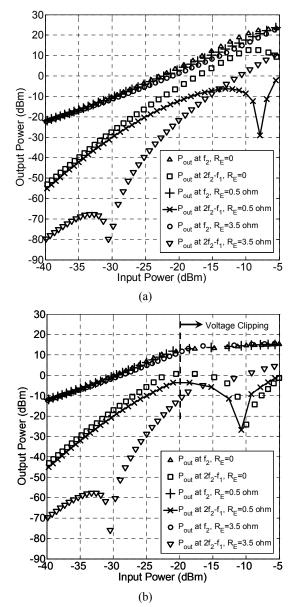

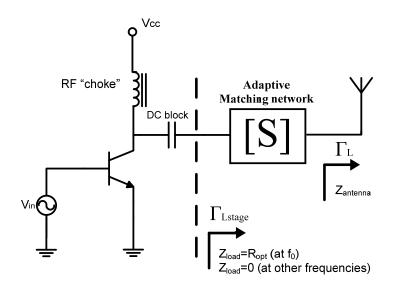

### 6 Antenna Mismatch Correction for Mobile Handsets

| 6.1 Introduction                                                  |

|-------------------------------------------------------------------|

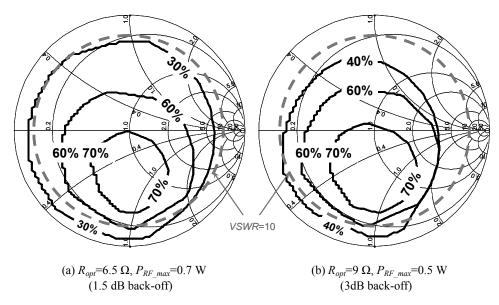

| 6.2 Antenna Mismatch Issues 105                                   |

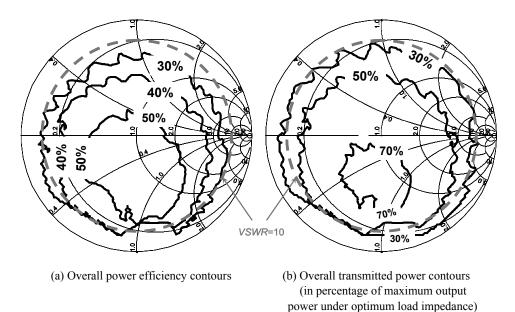

| 6.2.1 Reduction of Efficiency and Output Power 105                |

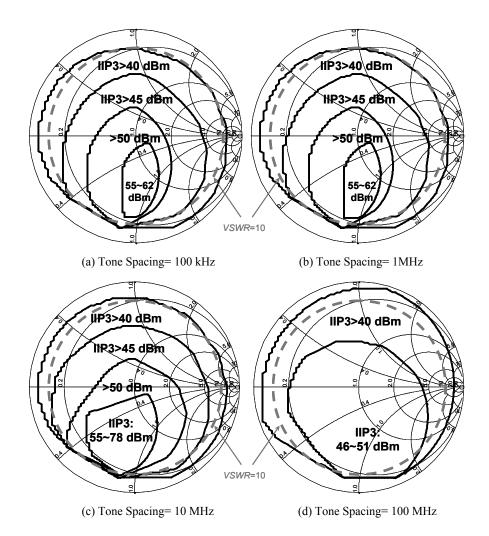

| 6.2.2 Linearity Degradation 109                                   |

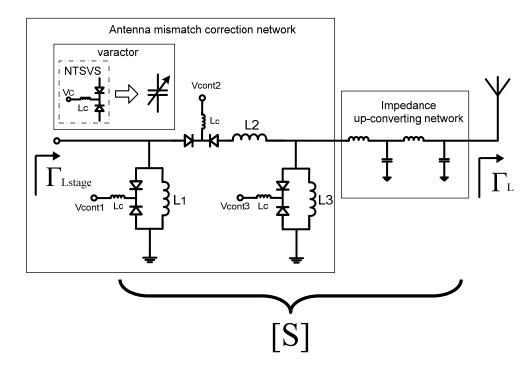

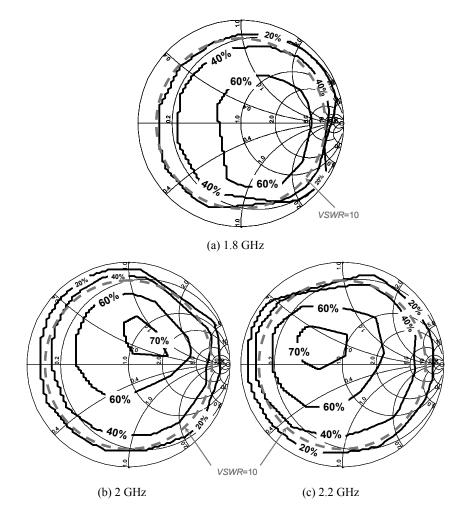

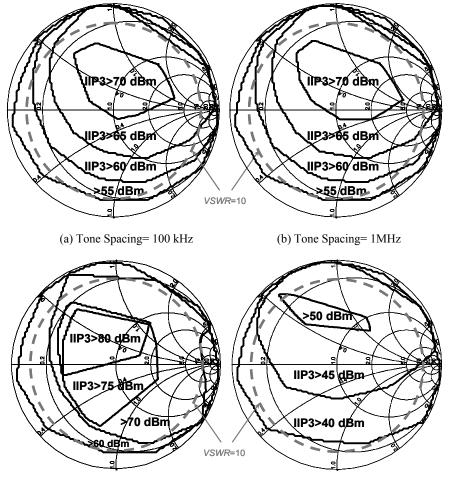

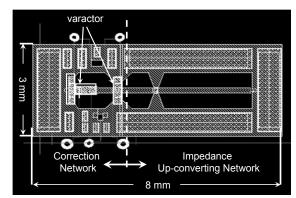

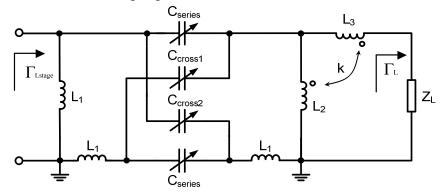

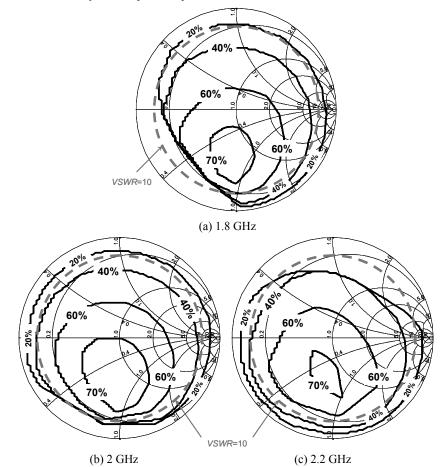

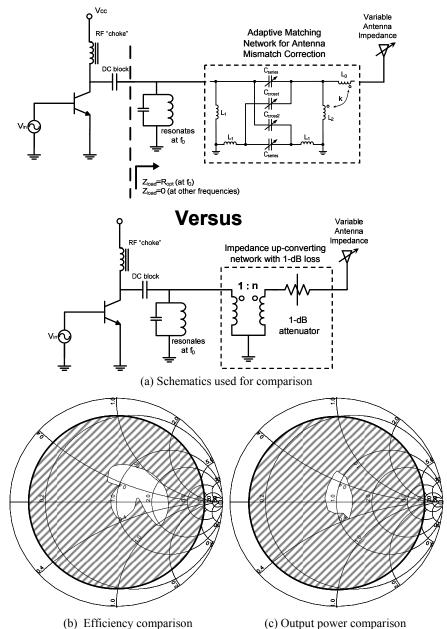

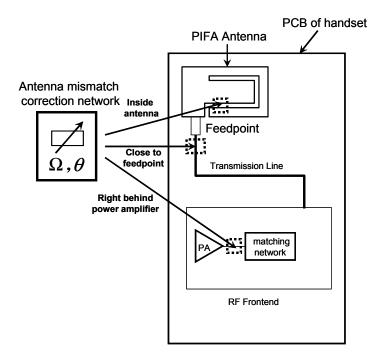

| 6.3 Design of the Adaptive Matching Network 112                   |

| 6.3.1 Performance Evaluation of the Adaptive Matching Network 112 |

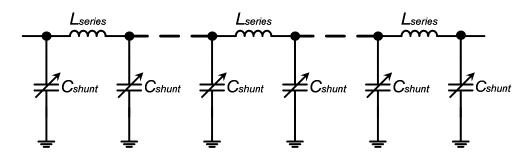

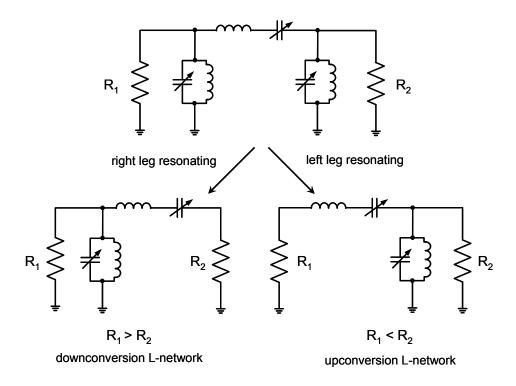

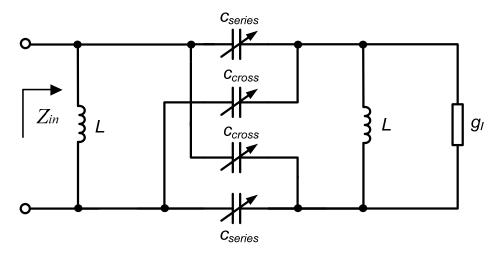

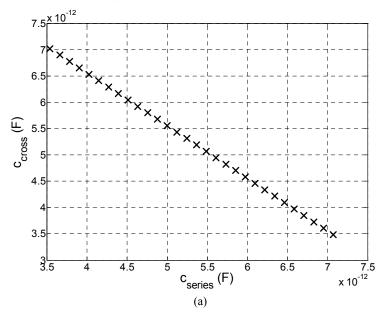

| 6.3.2 LC Resonators based Π-section Network ······ 113            |

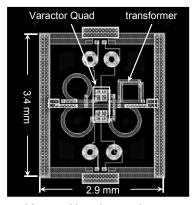

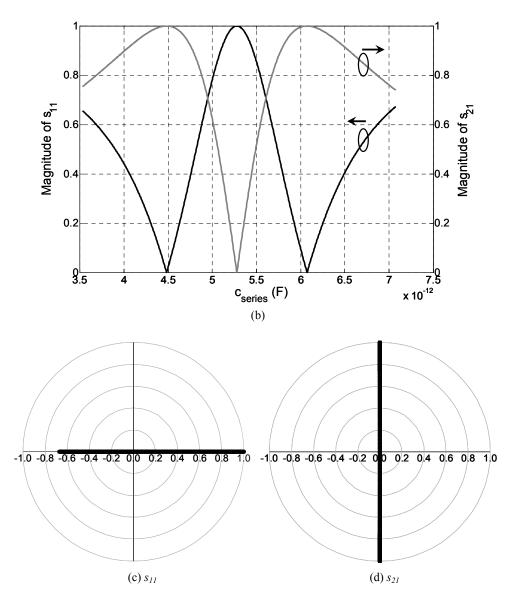

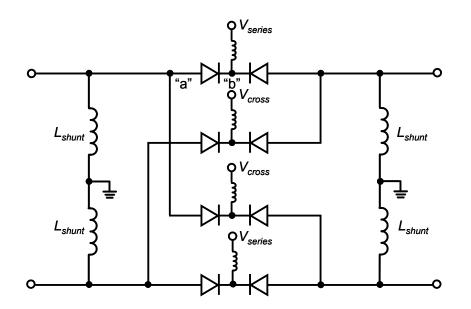

| 6.3.3 Capacitive Quad based network ······ 118                    |

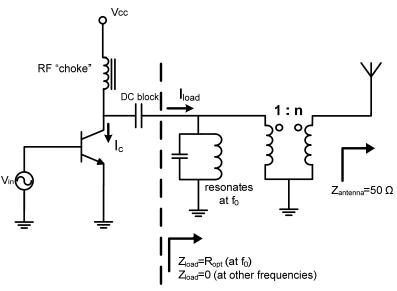

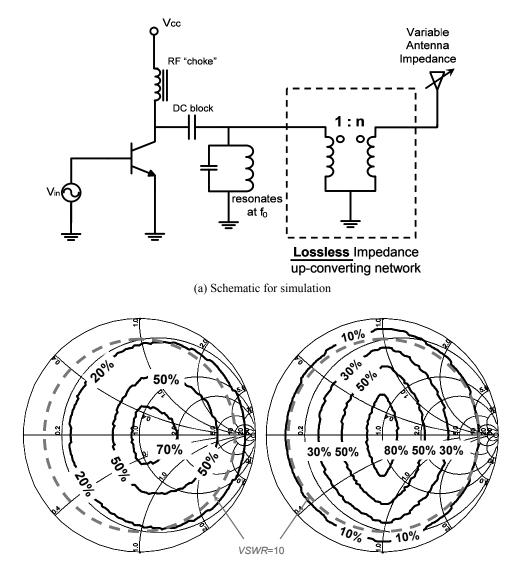

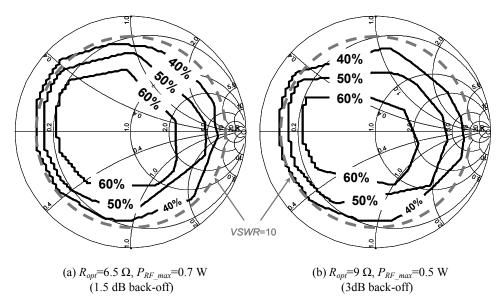

| 6.4 Load-line Adaptation 123                                      |

| 6.5 Locations to Place the adaptive Network 124                   |

| 6.6 Conclusions 126                                               |

### 7 A Varactor-Based Amplitude and Phase Modulator

| 7.1 Introduction ·····                                      | 129 |

|-------------------------------------------------------------|-----|

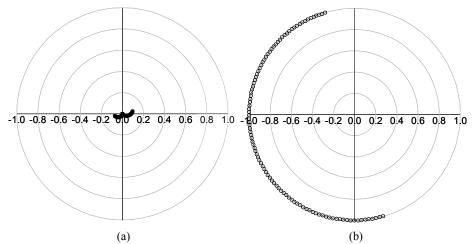

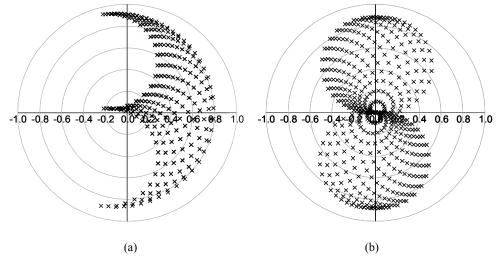

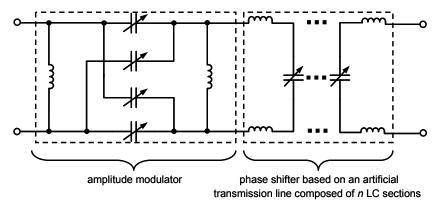

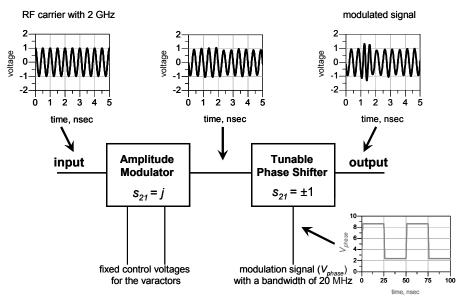

| 7.2 Differential Varactor Amplitude Modulator (DVAM) ······ | 130 |

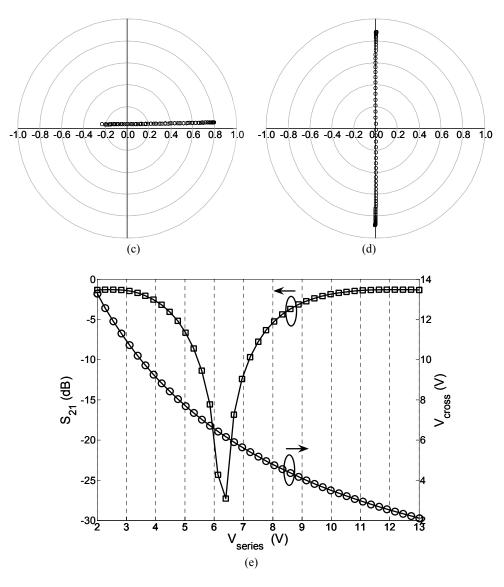

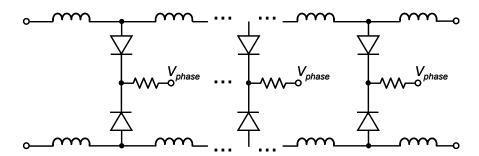

| 7.3 Phase Shifter with Narrow Tone-Spacing Varactor Stack   | 136 |

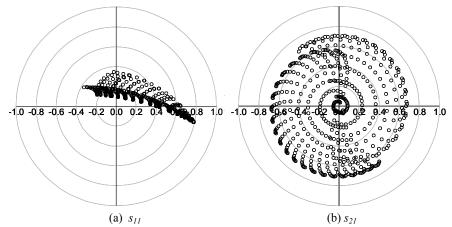

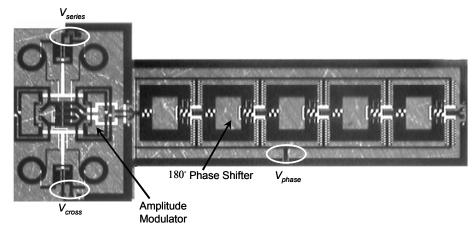

| 7.4 Novel Implementation of Polar Modulator                 | 141 |

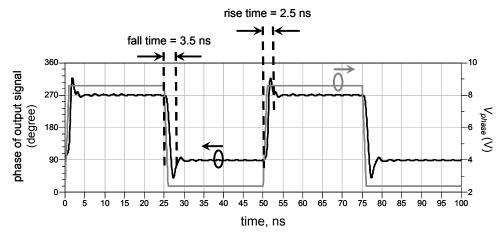

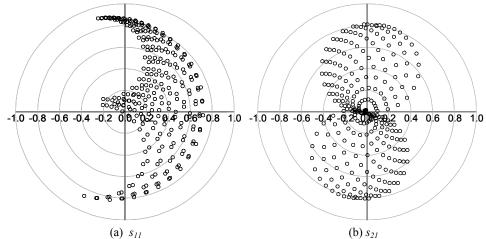

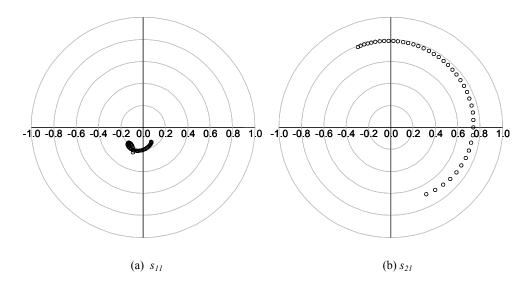

| 7.5 Experimental Results ·····                              | 146 |

| 7.6 Conclusions                                             | 149 |

### 8 Conclusions and Outlook

| 8.1 | Conclusions                                                   | 151 |

|-----|---------------------------------------------------------------|-----|

|     | 8.1.1 Summary of Varactor Device                              | 151 |

|     | 8.1.2 Tunable Networks in the Mobile Systems                  | 154 |

|     | 8.1.3 Multiple-standard Modulators for Transceivers and Phase |     |

|     | Diversity Systems ······                                      | 155 |

| 8.2 | Recommendations for Future Work                               | 155 |

|     | 8.2.1 Varactor Device ······                                  | 155 |

|     | 8.2.2 Varactor Applications                                   | 156 |

|     |                                                               |     |

|     | ۱. |

|-----|----|

| - 1 | v  |

|     |    |

| Appendix A:<br>Calculation of Electric Field Due to the Doping of the Spacer Layer                                        |

|---------------------------------------------------------------------------------------------------------------------------|

| <b>Appendix B:</b><br>Derivation of the Doping Profile for the Exponential $C(V_R)$ Relation                              |

| Appendix C:Derivation of $C(V_R)$ Relation in the Case of Variation From the IdealPower Law Exponent163                   |

| <b>Appendix D:</b> Derivation of $C(V_R)$ Relation for Variation of Doping Density at the Origin                          |

| Appendix E:<br>Calculation of 6 dB Corner Frequency for the Resistive Center-tapped<br>Narrow Tone-Spacing Varactor Stack |

| 0                                                                                                                         |

| Summary 169              |

|--------------------------|

| Samvatting 173           |

| List of Publications 177 |

| Acknowledgements 179     |

| About the Author 181     |

iv

### Chapter 1

### Introduction

### **1.1 From Beacon Tower to Mobile Phone**

Since the advent of human beings, the desire to communicate faster and farther has never ceased. In the ancient time, "town criers" [1] held an annual contest to discover who can shout a comprehensible message over the greatest distance. Up to date, the world record for this early human voice based message system is less than 100 meters [2]. The history of communication is mankind's search for ways to improve upon shouting. Over years, the techniques of communication have evolved from beacon and postage to modern telegraph, telephone, internet, mobile cellular phone and personal communication systems, each of them associated with a massive network such as the Great Wall of China, and the famous network of Roman roads.

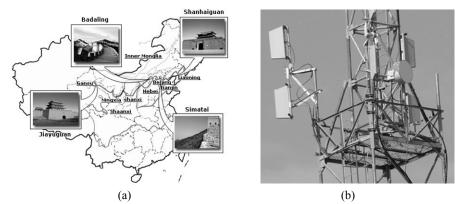

A brief comparison between the Chinese Great Wall beacon tower system and the modern cellular phone system (Table I) reveals that significant technical improvements have been achieved in terms of distance, data volume, speed, cost, power consumption and reliability by replacing the beacon tower with a modern base station (see Fig. 1.1, [3], [4]). All of this owes to Maxwell's theoretical prediction of the existence of electromagnetic (EM) waves in the 1860s and subsequent experiments by Hertz, Marconi and many others. Since then, the nature of communication has undergone a substantial change and new wireless communication methods and services have been enthusiastically adopted by people all around the world.

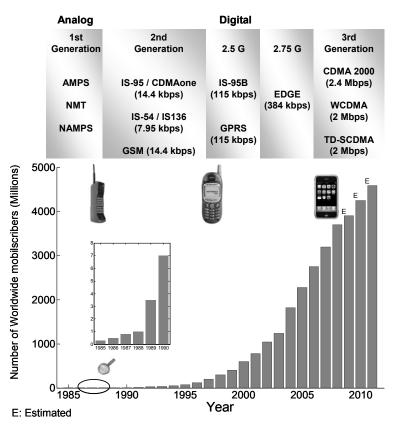

Today, the mobile radio communication industry has grown by orders of magnitude, fueled by digital and RF circuit fabrication improvements, high-level monolithic integration of active and passive components, and other miniaturization technologies, which make portable radio equipment smaller, cheaper and more reliable [5]. In the light of "faster and farther", mankind's insatiable desire upon communication, the global mobile system has evolved from the first analogue

generation (1G), mainly intended for voice communication, to the third generation (3G) in the past thirty years. As visualized in Fig. 1.2, the number of subscribers has grown at a phenomenal rate and the global mobile penetration is over 50 percent of total human population at the end of 2008, covering the entire world [6]. The data rate of 3G mobile systems has reached 2.4 Mbps and it is this feature that makes it possible to combine voice, multimedia applications and mobility in a never experienced manner.

Next-generation systems such as fourth generation (4G) and Worldwide Interoperability for Microwave Access (WiMax) promise to add additional capability. The 4G mobile communication services are expected to provide broadband, large capacity, high speed data transmission, providing users with high quality color video images, 3D graphic animation games, and audio services in 5.1 channels.

| •                                | Chinese Great Wall<br>Beacon Tower System                                                              | Modern Mobile System                                                                            |

|----------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Space Coverage                   | point to point over 6700 km                                                                            | entire world                                                                                    |

| Cost                             | The construction of the Great Wall<br>had never ceased for nearly all the<br>Chinese feudal dynasties. | The total cost is shared by over<br>3 billion subscribers and is<br>therefore quite affordable. |

| Date Rate                        | $\sim$ 1 bit / day                                                                                     | CDMA2000: 2.4 Mbps                                                                              |

| Power<br>Consumption             | For one bit binary signal, hundreds of beacon towers need to be ignited.                               | Handset during talk:<br>~ 1 Watt                                                                |

| Reliability &<br>Privacy of Data | As an alarm signal, the intruders are free to watch and to interfere.                                  | Reliable coded information                                                                      |

Table I. Comparison between the Beacon Tower System and Modern Mobile System

Fig. 1.1. (a) Being the oldest and most effective original telegram, beacon towers are the most important component of the defensive project on the Great Wall. They are built continually to pass military messages. In ancient times, if intruders approached, soldiers on the wall would create smoke in the daytime and light a fire at night to warn their troops. (figure from [3]) (b) Modern Code Division Multiple Access (CDMA) base station (figure from [4]).

Fig. 1.2. Growth of worldwide mobile subscribers and evolution of cellular networks over years [5], [6].

#### **1.2 The Need for Linear RF Tunable Components**

Accompanied by the evolution of wireless communication are the various technical difficulties. First, the use of increased data rates requires the use of complex modulated signals, making the energy consumption of the transmitting stage a concern. Since limited progress is made in battery technology, significant achievements have to, and will be made, in the mobile phone to reduce the power consumption. One of the key ideas is to reduce the power waste of the transmitter related to the environmental changes (e.g. location of the handset with respect to the basestation, disturbance of the antenna, etc.). Second, with the extensive use of cellular phones globally and the migration toward advanced systems, it is desired to build a mobile radio that is flexible enough to handle various communication standards. This leads to research on the multi-mode multi-band RF frontend, in which the main RF parameters, such as operation frequency and bandwidth, can be adaptively adjusted. Last but not the least,

3

besides the improvement of performance, the cost should be affordable for more subscribers, which in turn motivates the evolution of the wireless communication. To address the issue of cost, on one hand, the cost of a mobile unit can be reduced through high-level integration and hardware reusability. On the other hand, the shared cost of the network can be reduced through the enhancement of system capacity. Note that the former solution relates again with the multi-standard RF reconfiguration and the latter one turns to RF adaptive control of the transmitted power, e.g. as in use for Code Division Multiple Access (CDMA) systems.

In this section, we address how linear RF tunable components, like variable reactors (varactors) and switches, can enable RF reconfigurability for future telecommunication systems. Several case studies are given: (i) linear tunable components based networks can be used to correct the mismatched impedance of the antenna, which helps to maintain the link quality and reduce the power consumption; (ii) they can adaptively control the transmitting power in CDMA systems to increase the total system capacity; (iii) they facilitate to miniaturize and implement multi-band multi-mode radio systems, something that is beneficial for the data rate and system's space coverage; (iv) linear tunable circuits bring even some new functionalities that can serve upcoming modern communication systems. The challenges on tunable components for these applications are brought out, which suggests an urgent need for high-performance tunable components (this is apparent through the survey of currently existing tunable components in Chapter 2).

### **1.2.1** Adaptive Impedance Control

In modern telecommunication systems, the link quality of cellular phones normally suffers from antenna impedance mismatch caused by the narrow bandwidth of miniaturized high-Q antennas and by detuning of the antenna resonance frequency [7] due to fluctuating body-effects and changes in phone form-factor. For conventional handset transmitter implementations, the effective antenna impedance is supposed to have a nominal value of 50  $\Omega$  when the antenna is in the free-space operation without any objects around. However, when the handset is operated close to a metal object or in close proximity to the human body, the effective antenna impedance will vary over a wide impedance range [7]-[13]. When the input impedance varies, there is a mismatch between the power module and the antenna, with two major effects. First, the power module will not perform at its optimum efficiency under the variations of the loading conditions, and, second, the radiated power decreases due to the reflected power. This will result in an increase in energy consumption (i.e., decreased battery endurance) or transmission quality deterioration, increased distortion. In the worst case, the high standing wave amplitude or possible oscillation caused by the mismatch in the circuit

may damage the power amplifier. In view of this, it is desirable to use an impedancedependent adaptive matching network to maintain the link quality.

### **1.2.2** Adaptive Power Control

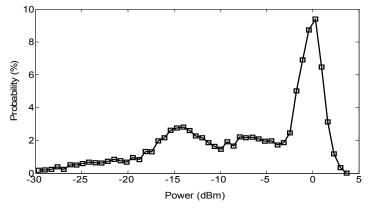

In modern telecommunication systems, power control of RF transmitters is usually required to maximize the system capacity. In order to minimize the interference, the mobile units need to transmit power at variable levels so that the signal strength is similar for all users. This is especially true in the case of CDMA and WCDMA protocols, where the power control is implemented in both base station and handset transmitters [14]-[17]. Power control in the base-station transmitter mitigates the "corner" problem, in which mobile units near the edges of a cell require more power due to transmission losses and adjacent cell interference. On the mobile unit side, to allow for the required variation of RF signal envelopes with modulation schemes, such as quadrature phase-shift keying (QPSK) or multicarrier signaling, power amplifiers have to operate with large peak-to-average power outputs, usually 5 dB or more as shown in Fig. 1.3. Note that such modulation characteristics caused variations are normally on a time scale of microseconds corresponding to the inverse of the modulation bandwidth, and we refer to them as fast variations.

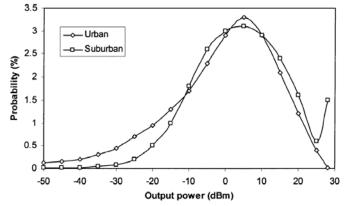

Variations in output power also occur over a slower time scale (ms scale) for CDMA transmission (as well as for all most other cellular protocols) in order to accommodate variable distance between mobile and base, as well as multipath and shadow fading, i.e., slow variations. The transmitted power usage probability density for CDMA applications [15], [17] for rural and urban areas is shown in Fig. 1.4 indicating that the power amplifier operates mostly at 15-20-dB backoff from the peak power, e.g. 27 dBm for this case.

Fig. 1.3. Power output probability distribution for CDMA 2000 forward link under fast variations (peak power = 4 dBm, average power = -3 dBm and chip rate = 1.2288 Mbps).

5

Fig. 1.4. The transmitted power usage probability density for CDMA applications for rural and urban areas under slow variations (data from [14], [17]).

Consequently, the power amplifier operates mostly within regions of low efficiency due to the requirement of power control. Since the power amplifier uses a large portion of the battery power in handsets, it is desirable for power amplifiers in these applications to have higher efficiencies at power-back-off conditions to extend battery life [15]. Techniques that address the efficiency in the back-off mode are dynamic biasing or regulation of the supply voltage of the output stage. Dynamic biasing provides only modest improvements in efficiency. Supply voltage regulation requires an efficiency improvement is load-line adjustment as a function of output power using an adaptive or reconfigurable output matching network. Note that the network in this operation needs to handle fast signal variations, requiring a short response time, and for this reason it is called dynamic adaptive matching network.

#### 1.2.3 Adaptive Multi-band Multi-mode Radio Systems

Wireless communication bands and services are proliferating. Cellular technology standards such as global system for mobile communications (GSM), code division multiple access (CDMA), enhanced data rates for GSM evolution (EDGE), and wideband CDMA (WCDMA) are being developed for long-range voice, data and video transfer. In addition to these public mobile services, many private systems such as IEEE 802.11 WLAN and Bluetooth are also becoming very popular. All these services have different carrier frequencies, channel bandwidths, and modulation schemes. These differences have motivated the industry to look for multi-band multi-mode systems to enable ubiquitous connectivity [18].

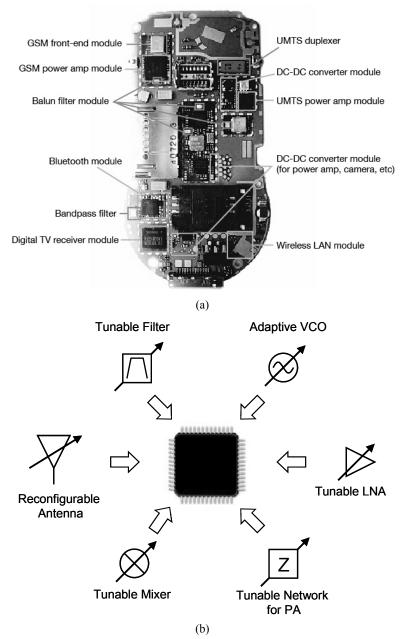

Fig. 1.5. (a) The board for Nokia 6630 mobile phone supporting GSM and UMTS, from Nokia Corp.. In this board, distributed front-end and power amplifier modules are utilized to meet multi-band multi-mode operation (data from [19]). (b) Proposed fully integrated adaptive multi-band multi-mode radio system. With the aid of the high-performance tunable components, multi-standard transceivers can share most circuit functions in an adaptive manner.

In order to fulfill the multi-band multi-mode demands of today's cellular market, current handset implementations are based on distributed modules [see Fig. 1.5(a)], associated with switches, to meet the specific requirements of each communication standard. However, the required extra RF hardware to implement such type of multistandard radio increases the total chip area and current consumption, therefore neither optimal in cost nor in power. Next-generation wireless systems aiming for size and cost reduction will utilize one or two fully adaptive modules [see Fig. 1.5(b)] to replace the current parallel path concept. Transceivers in such situations can share circuit functions between different standards in an adaptive manner and therefore have the advantages of low power consumption, efficient chip area usage, long talk time, and, most importantly, low cost [20]. In this new architecture, linear tunable components facilitate to implement most of the circuit functions, like adaptive low noise amplifier (LNA), adaptive voltage-controlled oscillator (VCO) [21], [22], tunable high-Q bandpass filters [23], adaptive power amplifiers (PAs). Note that with the trend of multi-band multi-mode integration, above-mentioned power-control and impedancecontrol matching networks need to be adapted to synchronously meet different communication standard requirements.

It is important to notice that practical design considerations place severe challenges on the tunable elements, the most critical component in the above-mentioned matching networks. First, their tuning range needs to be high enough to implement matching over a wide range at different bands. Second, they should be extremely low loss accompanied with a high breakdown voltage from the power handling and consumption point of view. Last but not the least, the matching networks are mostly placed behind the power amplifier, operating at high power levels, thus the linearity of the tunable components used in these networks is one of most critical issues under consideration, especially in the mobile communication systems with densely populated frequency spectrum.

#### **1.2.4** Amplitude and Phase Modulators

In addition to the applications in power amplifiers and tunable filters, linear tunable components are the most critical elements for passive amplitude modulators and phase shifters, which can act as enablers for the implementation of various radar and communication systems that make use of smart antennas.

In view of this, compact high performance phase shifters are and will be vital components in the realization of modern phase diversity systems. In these systems, the phase of each individual antenna element is controlled to steer the radiation pattern of the antenna without any mechanical movement. As a result of this functionality, a

lower power is required in transmit mode, while signal degradation due to fading in receive mode is significantly reduced [24].

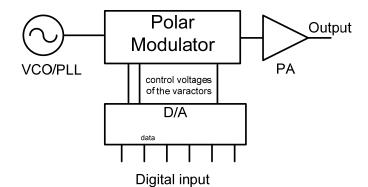

Besides the applications on smart antennas, amplitude and phase modulators provide potential for polar modulators. In contrast to the traditional I/Q modulator, polar modulation techniques can provide magnitude and phase adjustment in a very direct way. Consequently, it can offer a single architecture for various RF transmit systems, which presents opportunities for future communication systems.

Although attractive, the requirements on the amplitude and phase modulators are high: they should be low-loss, compact, require no additional power, and should be highly linear to avoid signal distortion, which directly translate to the challenges on the capacitance density, quality factor and linearity of the tunable components [24].

### 1.3 Outline

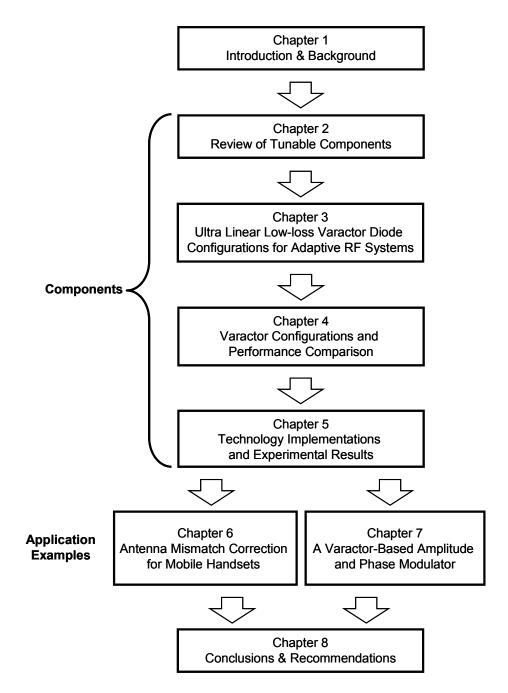

The outline of the thesis is shown schematically in Fig. 1.6. Chapter 2 presents an overview of the state-of-the-art tunable components such as thin-film Barium Strontium Titanate (BST) varactors, Microelectromechanical systems (MEMS) based switches and varactors, and currently available semiconductor switches and varactors. Their advantages and drawbacks are discussed. Chapter 3 deals with the theory of two novel extremely linear varactor diode configurations with complementary linearity properties in a single varactor diode technology, which aims to overcome the limitations of existing tunable components. Both varactor configurations use anti-series varactor diode configurations, where the diodes share the same exponential  $C(V_R)$ depletion capacitance relation. However, the proposed structures differ in their harmonic terminations and varactor area ratios, resulting in a fundamentally different linearity behavior versus tone spacing. In Chapter 4, all types of the diode based varactor configurations, aiming for the cancellation of third order intermodulation distortion, are summarized and their performance are compared as guideline for choosing the semiconductor-based varactor configurations. Chapter 5 focuses on the implementation issues of the proposed varactor configurations, together with measurements to support the theory. As two application examples of the novel varactors, the adaptive matching networks for mobile handsets are demonstrated in Chapter 6 and phase shifter and amplitude modulator are created in Chapter 7. Finally, Chapter 8 gives the main conclusions and recommendation for future works.

Fig. 1.6. Outline of the thesis

#### References

- [1] http://freespace.virgin.net/albans.crier/page3.html

- [2] "History of Communication." Available: http://www.historyworld.net

- [3] http://www.chinahighlights.com/greatwall/map.htm

- [4] <u>http://catel.az/en/news6.php</u>

- [5] T. S. Rappaport, "Wireless communications: principal and practice," 2nd ed., 2002.

- [6] "Portio research mobile factbook 2008," Portio Research Ltd.

- [7] A. van Bezooijen, M. A. de Jongh, C. Chanlo, L. C. H. Ruijs, F. van Straten, R. Mahmoudi and A. H. M. van Roermund, "A GSM/EDGE/WCDMA adaptive series-LC matching network using RF-MEMS switches," *IEEE J. Solid-State Circuits*, vol. 43, no. 10, pp. 2259-2268, Oct. 2008.

- [8] G. F. Pedersen, K. Olesen, and S. L. Larsen, "Bodyloss for handheld phones", 49th IEEE Vehicular Technology Conference Proceedings, May. 1999, Houston, Texas, vol. 2, pp. 1580-1584.

- [9] K. R. Boyle, Y. Yuan, and L. P. Lighthart, "Analysis of mobile phone antenna impedance variations with user proximity," *IEEE Trans. Antennas Propag.*, vol. 55, no. 2, pp. 364-372, Feb. 2007.

- [10] S. C. Ming, W. C. Hsien, W. K. Lu, Y. S. Huang and T. C. Lun, "User's hand effects on EMC internal GSM/DCS mobile phone antenna," *IEEE Antennas and Propagation Society International Symposium*, Jul. 2006, Albuquerque, NM, pp. 2097-2100.

- [11] H. King and J. Wong, "Effects of a human body on a dipole antenna at 450 and 900 MHz," *IEEE Trans. Antennas Propag.*, vol. 25, no. 3, pp. 376-379, May 1977.

- [12] J. Toftgard, S. N. Hornsleth, and J. B. Andersen, "Effects on portable antennas of the presence of a person," *IEEE Trans. Antennas Propag.*, vol. 41, no. 6, pp. 739-746, Jun. 1993.

- [13] J. de Mingo, A. Valdovinos, A. Crespo, D. Navarro and P. Garcia, "An RF electronically controlled impedance tuning network design and its application to an antenna input impedance automatic matching system," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 2, pp. 489-496, Feb. 2004.

- [14] J. B. Groe and L. E. Larson, "CDMA Mobile Radio Design," Boston, MA: Artech House, 2000.

- [15] G. Hanington, P. F. Chen, P. M. Asbeck and L. E. Larson, "High-efficiency power amplifier using dynamic power-supply voltage for CDMA applications," *IEEE Trans. Microwave Theory Tech.*, vol. 47, no. 8, pp. 1471-1476, Aug. 1999.

- [16] M. Iwamoto, A. Williams, P. F. Chen, A. G. Metzger, L. E. Larson and P. M. Asbeck, "An extended Doherty amplifier with high efficiency over a wide power range," *IEEE Trans. Microwave Theory Tech.*, vol. 49, no. 12, pp. 2472-2479, Dec. 2001.

- [17] B. Sahu and G. A. Rincon-Mora, "A High-efficiency linear RF power amplifier with a power-tracking dynamically adaptive buck-boost supply," *IEEE Trans. Microwave Theory Tech.*, vol. 52, no. 1, pp. 112-120, Jan. 2004.

- [18] "International technology roadmap for semiconductors: radio frequency and analog / mixed-signal technologies for wireless communications," 2007 edition. Available: http://www.itrs.net/Links/2007ITRS/Home2007.htm

- [19] "LTCC technology finds wider variety of applications." Available: http://techon.nikkeibp.co.jp/article/HONSHI/20061124/124305/

- [20] W. C. Edmund, Y. Lin, X. D. Liu, L. C. N. de Vreede, L. E. Larson, M. Spirito, M. J. Pelk, K. Buisman, A. Akhnoukh, A. de Graauw and L. K. Nanver, "Adaptive multi-band multi-mode power amplifier using integrated varactor-based tunable matching networks," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp. 2166-2176, Sep. 2006.

- [21] A. Tasic, W. A. Serdijn, and J. R. Long, "Multi-standard/multi-bandadaptive voltagecontrolled oscillator," in *Proc. IEEE Radio FrequencyIntegrated Circuits Symp.*, 2004, pp. 135–138.

- [22] A. Tasic, W. A. Serdijn, and J. R. Long, "Design of multi-standard adaptive voltage controlled oscillators," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 2, pp. 556-563, Feb. 2005.

- [23] K. Buisman, L. C. N. de Vreede, L. E. Larson, Y. Lin, X. D. Liu and L. K. Nanver, "A monolithic low-distortion low-loss silicon-on-glass varactor-tuned filter with optimized biasing," *IEEE Microwave and Wireless Components Letters*, vol. 18, no. 11, pp. 749-751, Nov. 2008.

- [24] J. H. Qureshi, S. Kim, K. Buisman, C. Huang, M. J. Pelk, A. Akhnoukh, L. E. Larson, L. K. Nanver and L. C. N. de Vreede, "A Low-loss Compact Linear Varactor Based Phase-shifter," *IEEE Radio Frequency Integrated Circuits (RFIC) Symposium*, Honolulu, pp. 453-456, Jun. 2007.

### Chapter 2

### **Review of Tunable Components**

### **2.1 Introduction**

Next-generation wireless systems, such as multi-mode transceivers and "cognitive radios" require circuit techniques that facilitate RF adaptivity. Some examples of adaptive circuits include tunable filters [1], [2] and tunable matching networks for low-noise and power amplifiers [3], [4]. An ideal tuning element for these applications will exhibit extremely low loss, low dc power consumption, high linearity, ruggedness to high voltage and high current, wide tuning range, high reliability, very low cost, low area usage, and will be continuously tunable with a high tuning speed. In this chapter, state-of-the-art tunable components such as thin-film Barium Strontium Titanate (BST) varactors, Microelectromechanical systems (MEMS) based switches and varactors, and conventional semiconductor capacitive switches and varactors are reviewed and compared.

### 2.2 Currently Available Tunable Elements

### 2.2.1 Thin-Film Barium Strontium Titanate (BST) Varactors

High-permittivity thin-film dielectrics that exhibit strong field dependence in the dielectric constant can be exploited for voltage-variable capacitors in RF circuits. Thin-film barium strontium titanate (BST) is an example of materials that have been investigated by many research groups [5]-[7]. This research is motivated by the following properties that make it attractive for high-frequency applications:

- High field dependent permittivity variation: as much as 4:1 variation in permittivity.

- High dielectric constant: typically in the range of 200-300.

- "Fast" polarization response: allows for rapid tuning and frequency conversion devices.

- High breakdown electric field: typically  $> 2 \times 10^6$  V/cm, allows for large bipolar voltage swings and hence good power-handling.

- Wide variety of substrate materials available for thin-film deposition.

BST thin-film based varactors [5]-[7] offer advantages in terms of integratability, capacitance density, high speed and they usually exhibit moderate tuning ratio over a relatively low control voltage, which is of the order of 10-20 V, in contrast to 50-100 V [8]-[11] for the microelectromechanical systems (MEMS) varactors or switches. Unlike varactor diodes, BST varactors do not have a forward conduction region and hence can support a relatively large AC voltage swing at low bias voltages, making them useful for moderate-power-level RF applications. However, due to the inherent nonlinear nature of the ferroelectric materials, linearity has been both a concern and challenge in the applications of BST varactors, especially in the spectrally-packed communication systems. In addition, the reproducibility of BST varactors is currently still an issue and hampers their massive manufacture.

#### 2.2.2 MEMS Based Switches and Varactors

Microelectromechanical systems are well suited to implement variable capacitors, inductors, switches and reconfigurable circuits. There are two generic types of MEMS tunable elements: switches and varactors, which have demonstrated impressive performance in terms of low losses, linearity and power handling capability, and for this reason, they are intensively investigated for applications in radar and communication systems.

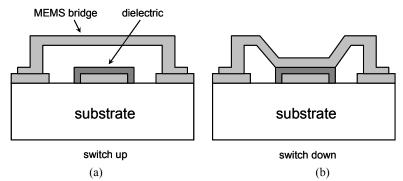

MEMS switches are composed of a thin metal membrane (or beam), which can be moved to RF line using an electrostatic force due to a voltage between the bridge and bottom electrode, as illustrated in Fig. 2.1. MEMS based switches [10], [11] can provide very low losses while consuming little dc power (microjoule during the switching process). When switching in fixed capacitors, very large capacitance ratios, very low loss and very high linearity can be accomplished. In addition, they can be fabricated on almost any substrate and can also be used to implement tunable circuits by routing the signal through a different path or by providing a stepped control of capacitance. An array with *N* MEMS switches, for example, will provide  $2^N$  different combinations of capacitance values, forming a switchable capacitor bank.

However, MEMS switches have several intrinsic disadvantages which restrict their applications in communication systems. First, they are not continuously tunable. For applications where fine tuning is required, a switchable capacitor bank composed of a large number of switching elements is needed, each of them requiring a control voltage. Consequently, the physical metal connections to these switching elements will in practice degrade the overall quality factor of the whole switchable capacitor bank. Second, they have slow switching speeds (1-100  $\mu$ s) and therefore don't allow fast modulation of the capacitance value. In the meanwhile, their pull-in voltage must be chosen sufficiently large in order to avoid self-actuation due to RF signal and the pullout voltage must be sufficiently large to avoid non-release under hot-switching conditions [12], which result in a high control voltage (50-100 V). In general, MEMS switches are sensitive to reliability issues, although it has exhibited significant improvement recently.

The MEMS varactor is more or less advanced capacitive membrane switch where analogue control voltage is used to allow continuous tuning. In practice, its structures are very similar to MEMS switches except for the implemented solution to resolve the collapse (snap-down) problem which normally limits the tuning range. The MEMS varactor [8]-[11] is considered to be less sensitive to reliability issues compared to MEMS switches, it provides a very high Q for moderate capacitance values. Nevertheless, its continuous tunable implementations can suffer from intermodulation distortion, since the position of the membrane can move with changes in the modulation envelope of the applied RF voltage [11], [13]. It requires non-standard processing and expensive packaging costs, and its switching speed is still poor compared to the BST and semiconductor-based solutions. Moreover, its relatively small continuous tuning range and high control voltage constrain its RF performance. Also, its relatively small capacitance density makes it difficult to implement large valued capacitors and for this reason its application is mostly found above 5 GHz.

Fig. 2.1. Cross section of an electrostatically actuated capacitive membrane MEMS switch. (a) The switch is off. (b) The switch is on. The switch alternates between a high and low capacitance.

### 2.2.3 Conventional Semiconductor Based Varactors

Semiconductor varactors, like p-n diode, Schottky diode and MOS varactors, are basically voltage-controlled capacitances, making good use of the voltage dependence of the depletion thickness of the space charge region. Due to relatively high dielectric constants of semiconductor materials, their capacitance densities are normally at least 10 times larger than the MEMS counterparts. In addition, the semiconductor solutions show advantages in terms of integration, reliability, high tuning speed (1-100 ns), low-control voltage and ruggedness. However, their inherently nonlinear behavior does not comply with modern communication systems with densely populated frequency spectrum, and their related quality factors are usually limited at the microwave frequencies of interest for most demanding applications.

#### 2.2.4 Semiconductor Based Switches

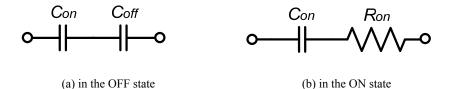

When the diodes or transistors are switched between the forward and reverse bias condition, they alternate between a resistor  $(R_{on})$  in the ON state and a capacitor  $(C_{off})$  in the OFF state. In order to obtain a capacitive tuning, a bigger constant capacitor  $(C_{on} > C_{off})$  is normally connected in series to form a capacitive switch as shown in Fig. 2.2.

Fig. 2.2. Equivalent circuits of a capacitive switch in the OFF and ON state.

When the diode is under zero or reverse bias (transistor can be also regarded as switching element), it exhibits a low capacitance close to  $C_{off}$  as shown in Fig. 2.2(a) resulting in high impedance at RF frequency. Under a forward bias condition, the switched capacitor will behave as a small RF resistance ( $R_{on}$ ) in series with  $C_{on}$  instead [see Fig. 2.2 (b)]. In this case, a smaller  $R_{on}$  is favored to achieve a better quality factor, however by lowering  $R_{on}$  through up-scaling the switching element typically the capacitance under off-state ( $C_{off}$ ) will increase, which in turn limits the resulting switchable capacitance ratio ( $T_{tune}$ ). In view of this, care is normally taken to improve the  $R_{on}$ - $C_{off}$  product by making use of special process technologies, like silicon-on-sapphire (SOS) CMOS [14] and pseudomorphic high electron mobility transistor (pHEMT) [15].

The state-of-the-art  $R_{on}$ - $C_{off}$  products of semiconductor capacitive switches are listed in Table II and they are translated to Q- $T_{tune}$  product using [16]

$$Q \times (T_{tune} - 1) = \frac{1}{\omega R_{on} C_{off}}$$

(2.1)

where  $\omega$  is the angular RF frequency;

$$Q = 1/(\omega R_{on} C_{on})$$

(2.2)

is the quality factor of the capacitive switch in the ON state, and

$$T_{tune} = C_{on} \left( \frac{C_{on} C_{off}}{C_{on} + C_{off}} \right) = 1 + \frac{C_{on}}{C_{off}}$$

(2.3)

is the capacitance ratio between ON and OFF states.

| Process Technology                    | $R_{on} \times C_{off}$ (fs) | $Q \times (T_{tune} - 1)$<br>at 2 GHz | $Q \times (T_{tune} - 1)$<br>at 5 GHz |

|---------------------------------------|------------------------------|---------------------------------------|---------------------------------------|

| 0.15 µm pHEMT                         | 435 [15]                     | 183                                   | 73                                    |

| 0.5 <i>μm</i> pHEMT                   | 360 [15]                     | 221                                   | 88                                    |

| 0.5 $\mu m$ 10 nm T <sub>ox</sub> SOS | 756 [14]                     | 105                                   | 42                                    |

| 0.25 $\mu m$ 5 nm T <sub>ox</sub> SOS | 448 [14]                     | 178                                   | 71                                    |

Table II. Survey of state-of-the-art  $R_{on}$ - $C_{off}$  products from different process Technology and corresponding Q- $T_{tune}$  products at 2 GHz and 5 GHz

Table II implies that the room for compromise between the quality factor and tuning range are very limited especially when the RF operation frequency is high, which can be regarded as the bottleneck for semiconductor switches. For this reason, their applications are mostly found below 2 GHz.

#### 2.2.5 Modern Semiconductor Based Varactors

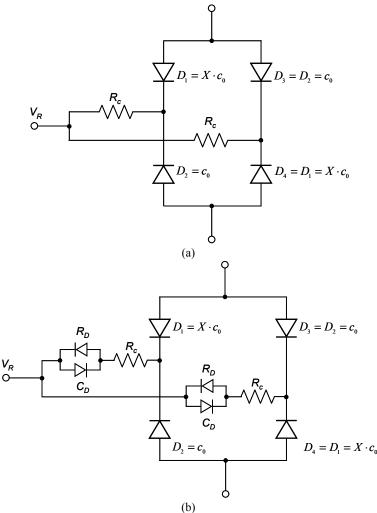

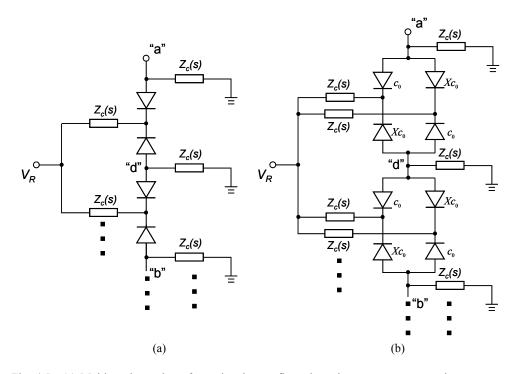

In order to overcome above-mentioned drawbacks and to create low-loss, easy to integrate, highly reliable and ultra-linear continuous tunable capacitors, varactor diodebased circuit topologies - along with a high performance silicon-on-glass varactor diode process technology - have been presented [17], [18]. These varactor configurations, proposed and initiated by K. Buisman et al., can act as variable capacitors with ideally zero, or extremely low distortion [17]-[23]. A brief description of these two previous low-distortion varactor configurations is given below.

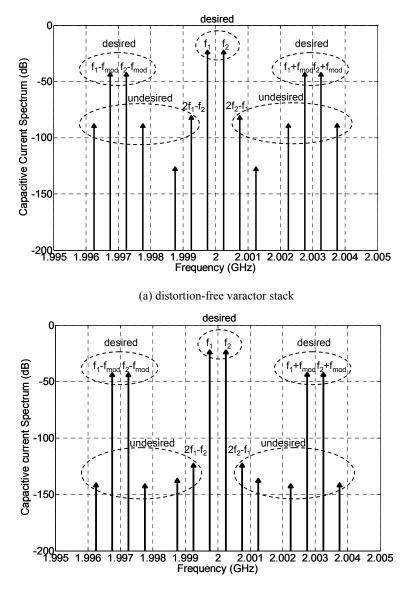

• The distortion-free varactor stack (DFVS) [19]-[23]: is based on an anti-series connection of two identical uniformly doped varactors (capacitance power law

- coefficient n = 0.5), which use an infinitely high impedance as center-tap connection. Under these conditions, all distortion components at the RF terminals are perfectly cancelled, yielding a distortion-free operation.

- The high tuning range varactor stack (HTRVS) [17]: is a combined anti-series/antiparallel topology of four hyperabrupt varactor diodes [24] (capacitance power law coefficient n > 0.5), which uses two infinitely high center-tap impedances. At the RF terminals, the resulting even and third-order distortion products are cancelled through a proper selection of the varactor area ratio.

For the implementation of these two varactor configurations, methods are applied to reduce or eliminate the losses from the connecting metals, contact resistance, buried layer and substrate. Consequently, the fabricated distortion-free varactor stack has the lowest quality factor of 180 at zero bias voltage and a tuning range of 4:1 at 2 GHz [17], a value corresponding to a  $Q \times (T_{tune} - 1)$  product of 540 even for a silicon implementation. Note that further improvement is possible through the use of high-mobility intrinsic material and the theoretically achievable Q- $T_{tune}$  product can be predicted by [25]

$$Q(worst) \times \left[ (T_{tune}^2 - 1)(T_{tune} - 1) \right] = \frac{\mu_n E_{breakdown}^2}{2\omega V_i}$$

(2.4)

where  $\mu_n$  is the electron mobility,  $E_{breakdown}$  is the maximum electric field at breakdown and  $V_i$  is the built-in potential.

### Table III. Calculated Q- $T_{tune}$ products of the uniformly doped diodes for a given tuning range ( $T_{tune}$ ) at different RF frequencies

| Tuning Range $(T_{tune})$ | $Q \times (T_{tune} - 1)$<br>at 2 GHz | $Q \times (T_{tune} - 1)$<br>at 5 GHz | $Q \times (T_{tune} - 1)$<br>at 100 GHz |

|---------------------------|---------------------------------------|---------------------------------------|-----------------------------------------|

| 3                         | 15360                                 | 6144                                  | 307                                     |

| 6                         | 3510                                  | 1404                                  | 70                                      |

| 9                         | 1674                                  | 670                                   | 34                                      |

| 12                        | 858                                   | 343                                   | 17                                      |

$[\mu_n = 6000 \ cm^{-2} / (V \cdot s), E_{breakdown} = 6 \times 10^5 \ V / cm \text{ and } V_i = 0.7 \ V]$

As a comparison with the semiconductor based switches, Table III lists the calculated Q- $T_{tune}$  products of the uniformly doped diodes in a GaAs implementation. It is seen that the new semiconductor varactors are much better at 2 GHz band and readily operated up until 100 GHz.

Although very good results have been achieved with the configurations above, their practical implementations still have linearity constraints for complex modulated

18

signals, or other signals with narrow tone spacing. This is caused by the severe requirements for the center-tap impedance, which should approximate infinity when the tone-spacing approaches zero. Due to the requirement of these very high center-tap impedances, rapid modulation of the capacitance value of the distortion-free varactor stack and high tuning range varactor stack becomes problematic. Also, parasitic leakage currents of the diodes can cause voltage drops over this center-tap impedance, yielding an undesired shift of the intended capacitance value.

### 2.3 Discussion on Current Varactor Topologies

In general, the performance of varactors, like tuning range, control voltage, quality factor, linearity etc, are traditionally trade-off against each other, by choosing either the technology or the element parameters.

|                                 | Conventional<br>Semiconductor | DFVS/<br>HTRVS                | BST                       | Continuously<br>Tunable MEMS  |

|---------------------------------|-------------------------------|-------------------------------|---------------------------|-------------------------------|

| Tuning<br>Range                 | High                          | High                          | Moderate                  | Low                           |

| Loss (Q)                        | Moderate<br>(Q < 60 typ.)     | High<br>(Q < 200)             | Moderate<br>(Q < 60 typ.) | Very High<br>(Q < 200)        |

| Capacitance<br>Density          | Moderate                      | Moderate                      | Very High                 | Low                           |

| Control<br>Voltage              | < 10 V                        | typically<br>< 10V            | 10-20 V                   | 50-100 V                      |

| Tuning<br>Speed                 | Fast                          | Slow                          | Fast                      | Slow                          |

| Voltage<br>Handling             | Poor                          | Moderate                      | Moderate                  | Excellent                     |

| Linearity<br>(IM <sub>3</sub> ) | Poor                          | Excellent at large $\Delta f$ | Poor                      | Excellent at large $\Delta f$ |

| Reliability                     | Excellent                     | Excellent                     | Good                      | Poor                          |

Table IV. Varactor Performance Comparison

As compared in Table IV, no solution surpasses the others in all aspects. Currently, MEMS varactors play an important role in the high-frequency (above 5 GHz) regions, while the BST and conventional semiconductor varactors are widely used for low-power applications. The distortion-free varactor stack and high tuning range varactor

stack are newly-invented components and they have shown many promising applications over the DC to 2 GHz frequency range and would appear to have a bright future for high-frequency applications as well. Although very good results have been achieved, they have limitations when rapid modulation of their values is desired while their linearity performance at narrow tone spacings is also of importance. Solutions to these limitations will be addressed in the next chapters.

### References

- K. Entesari and G. M. Rebeiz, "A differential 4-bit 6.5-10-GHz RF MEMS tunable filter," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 1103-1110, Mar. 2005.

- [2] K. Entesari and G. M. Rebeiz, "A 12-18-GHz three pole RF MEMS tunable filter," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 2566-2571, Aug. 2005.

- [3] F. Ellinger, H. Jackel and W. Bachtold, "Varactor-loaded transmission-line phase shifter at C-band using lumped elements," *IEEE Trans. Microwave Theory Tech.*, vol. 51, pp. 1135-1140, Apr. 2003.

- [4] T. M. Hancock and G. M. Rebeiz, "A 12-GHz SiGe phase shifter with integrated LNA," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 977-983, Mar. 2005.

- [5] D. R. Chase, L. Y. Chen, R. A. York, "Modeling the capacitive nonlinearity in thinfilm BST varactors" *IEEE Trans. Microw. Theory Tech.*, vol. 53, pp. 3215-3220, Oct. 2005.

- [6] J. S. Fu, X. A. Zhu, D. Y. Chen, J. D. Phillips and A. Mortazawi, "A linearity improvement technique for thin-film barium strontium titanate capacitors," in *IEEE MTT-S Int. Microwave Symp. Dig.*, San Francisco, CA, pp. 560-563, Jun. 2006.

- [7] L. Y. V. Chen, R. Forse, D. Chase and R. A. York, "Analog tunable matching network using integrated thin-film BST capacitors," in 2004 IEEE MTT-S Int. Microwave Symp. Dig., Fort Worth, Texas, Jun. 2004.

- [8] I. C. Reines, C. L. Goldsmith, C. D. Nordquist, C. W. Dyck, G. M. Kraus, T. A. Plut, P. S. Finnegan, F. Austin and C. T. Sullivan, "A low loss RF MEMS Ku-band integrated switches filter bank," *IEEE Microwave Wireless Comp. Lett.*, vol. 15, no. 2, pp. 74-76, Feb. 2005.

- [9] Y. Lu, L. P. B. Katehi and D. Peroulis, "High-power MEMS varactor and impedance tuners for millimeter-wave applications," *IEEE Trans. Microwave Theory Tech.*, vol. 53, pp. 3672-3678, Nov. 2005.

- [10] J. B. Muldavin and G. M. Rebeiz, "High-isolation CPW MEMS shunt switches-Part 1: Modeling," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1045-1052, Jun. 2000.

- [11] L. Dussopt and G. M. Rebeiz, "Intermodulation distortion and power handling in RF MEMS switches, varactors and tunable filters," *IEEE Trans. Microwave Theory Tech.*, vol. 51, pp. 1247-1256, Apr. 2003.

- [12] A. van Bezooijen, M. A. de Jongh, C. Chanlo, L. C. H. Ruijs, F. Van Straten, R. Mahmoudi and A. H. M. Van Roermund, "A GSM/EDGE/WCDMA adaptive series-LC mataching network using RF-MEMS switches," *IEEE J. Solid-State Circuits*, vol. 43, pp. 2259-2268, Oct. 2008.

- [13] D. Girbau, N. Otegi, L. Pradell and A. Lazaro, "Study of intermodulation in RF MEMS variable capacitors," *IEEE Trans. Microwave Theory Tech.*, vol. 54, pp. 1120-1130, Mar. 2006.

- [14] D. Kelly, C. Brindle, C. Kemerling and M. Stuber, "The state-of-the-art of silicon-onsapphire CMOS RF switches," CSIC 2005 digest, pp. 200-203, Nov. 2005.

- [15] S. Makioka, Y. Anda, K. Miyatsuji and D. Ueda, "Super self-aligned GaAs RF switch IC with 0.25 dB extremely low insertion loss for mobile communication systems," *IEEE Trans. Electron Devices*, vol. 48, pp. 1510-1514, Aug. 2001.

- [16] P. Sjoblom and H. Sjoland, "Measured CMOS switched high-quality capacitors in a reconfigurable matching network," *IEEE Trans. Circuit Syst. II*, vol. 54, pp. 858-862, no. 10, Oct. 2007.

- [17] K. Buisman, L. C. N. de Vreede, L. E. Larson, M. Spirito, A. Akhnoukh, T. L. M. Scholtes and L. K. Nanver, "Distortion free varactor diode topologies for RF adaptivity," in 2005 IEEE MTT-S Int. Microwave Symp. Dig., Long Beach, CA, Jun. 2005.

- [18] K. Buisman, L. C. N. de Vreede, L. E. Larson, M. Spirito, A. Akhnoukh, Y. Lin, X. Liu and L. K. Nanver, "Low-distortion, low-loss varactor-based adaptive matching networks, implemented in a silicon-on-glass technology," in *Proc. Radio Frequency IC Symp.*, Long Beach, CA, Jun. 2005.

- [19] R. G. Meyer and M. L. Stephens, "Distortion in variable-capacitance diodes," *IEEE J. Solid-State Circuits*, vol. SC-10, pp. 47-55, Feb. 1975.

- [20] K. Buisman, C. Huang, A. Akhnoukh, M. Marchetti, L. C. N. de Vreede, L. E. Larson, and L. K. Nanver, "Varactor topologies for RF Adaptivity with improved power handling and linearity", in 2007 *IEEE MTT-S Int. Microwave Symp. Dig.*, Honolulu, HI, Jun. 2007.

- [21] Q. Han, K. Inagaki and T. Ohira, "Perturbation analysis and experimental verification on intermodulation and harmonic distortion in an anti-series varactor pair," *IEICE Trans. Electron.*, vol. E88-C, no. 1, pp. 89-97, Jan. 2005.

- [22] M. Akaike, T. Ohira, K. Inagaki and Q. Han, "An analysis of nonlinear terms in capacitance-voltage characteristic for anti-series-connected varactor-diode pair," *Int. J. RF Microw.*, vol. CAE 14, pp.274-282, 2004.

- [23] Q. Han, K. Inagaki, R. Schlub, T. Ohira and M. Akaike, "Harmonic distortion suppression technique for varactor-loaded parasitic radiator antennas," *IEICE Trans. Electron.*, vol. E85-C, no. 12, pp. 2015-2020, Dec. 2002.

- [24] D. A. Neamen, "Semiconductor Physics & Devices", 2nd ed., Chicago: Irwin, 1997.

- [25] L. K. Nanver, H. Schellevis, T. L. M. Scholtes, L. La Spina, G. Lorito, F. Sarubbi, V. Gonda, M. Popadic, K. Buisman, L. C. N. de Vreede, C. Huang, S. Milosavljevic, E. J. G. Goudena, "Improved RF Devices for Future Adaptive Wireless Systems Using Two-sided Contacting and AlN Cooling", *IEEE J. Solid-State Circuits*, vol. 44, no. 9, Sep. 2009.

### Chapter 3

## Ultra Linear Low-loss Varactor Diode Configurations for Adaptive RF Systems

### **3.1 Introduction**

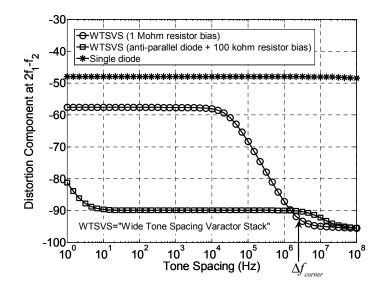

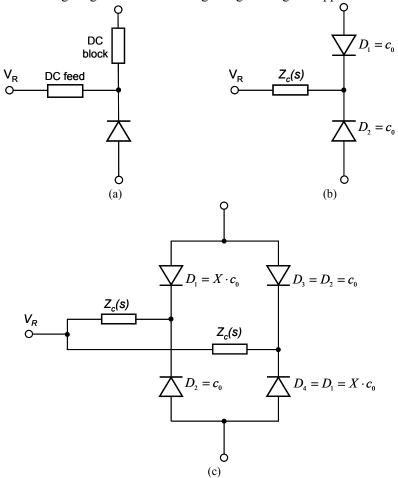

In this chapter, we focus on the implementation of two highly linear varactor diode configurations with complementary linearity properties in terms of tone spacing in a single varactor diode technology, which aims to overcome the limitations of existing tunable elements specified in Chapter 2. Both varactor configurations use an anti-series varactor diode topology, where the diodes share the same exponential  $C(V_R)$  depletion capacitance relation. However, the proposed structures differ in their harmonic terminations and varactor area ratios, resulting in a fundamentally different linearity behavior versus tone spacing. The first structure has the highest linearity for narrowband modulated signals and is named the narrow tone-spacing varactor stack. This new configuration exhibits improved linearity for narrowband signals, little sensitivity to leakage currents, higher capacitance control range and lower control voltages. The second varactor configuration exhibits the highest linearity for modulated signals with wide tone spacing, and is hereafter named the wide tone-spacing varactor stack. This structure is a direct derivation of the earlier proposed high tuning range varactor stack [1] and for this reason it preserves all the merits of that component.

In receiver applications the input signal is typically small in amplitude (< -30 dBm) relaxing the in-band linearity requirement. Therefore, for the receiver, the most troublesome distortion comes from strong out-of-band interferers whose undesired mixing products can fall in-band and pollute the reception of the desired signal. Note that in practical situations these interfering or jammer signals are typically separated

from the desired signal by more than 100 kHz. As a result the linearity for signals with larger tone spacing is most important. Considering the above, the wide tone-spacing varactor stack is a very attractive candidate for adaptive receivers. On the other hand, the linearity properties of the narrow tone-spacing varactor stack are best suited for the transmitting path. Here, complex modulated signals with a high output power need to be handled without introducing channel-to-channel interference or increasing the error vector magnitude due to intermodulation distortion.

This chapter is organized as follows. The theory of operation for the narrow tonespacing varactor stack is given in Section 3.1. The requirements for the doping profile and its optimization for the tuning range, breakdown voltage and quality factor are discussed in Section 3.2. The influence of fifth-order intermodulation distortion on the linearity is considered in Section 3.3. The practical implementation issues related to process deviation are discussed in Section 3.4. In Section 3.5, we focus on the analysis of the wide tone-spacing varactor stack, yielding its required varactor area ratio for  $IM_3$ cancellation. The remaining  $IM_5$  distortion for the wide tone-spacing varactor stack has been quantified by a compact expression, while the influence of the center-tap impedances on the linearity as a function of tone spacing has been analyzed. We conclude this chapter in Section 3.6 with a comparison of the two varactor linearization techniques.

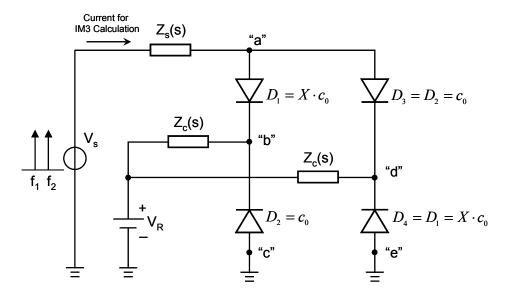

#### **3.2 Theory of Operation**

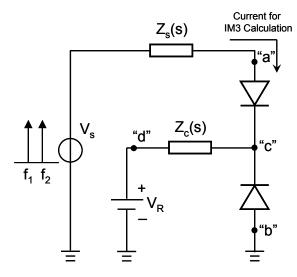

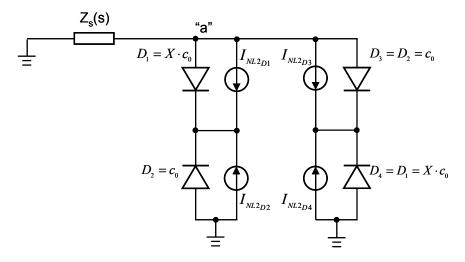

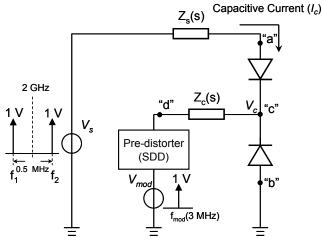

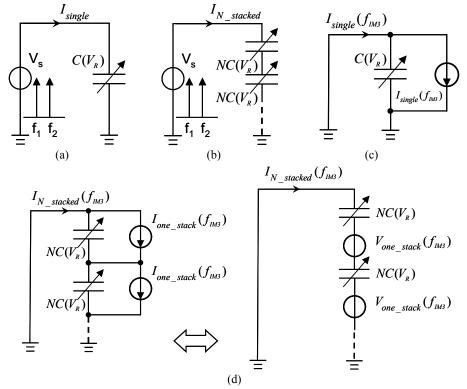

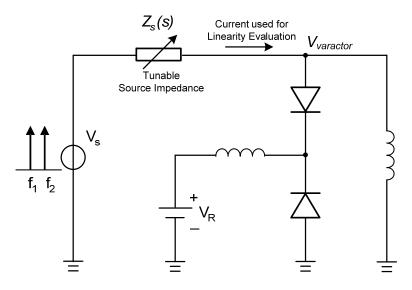

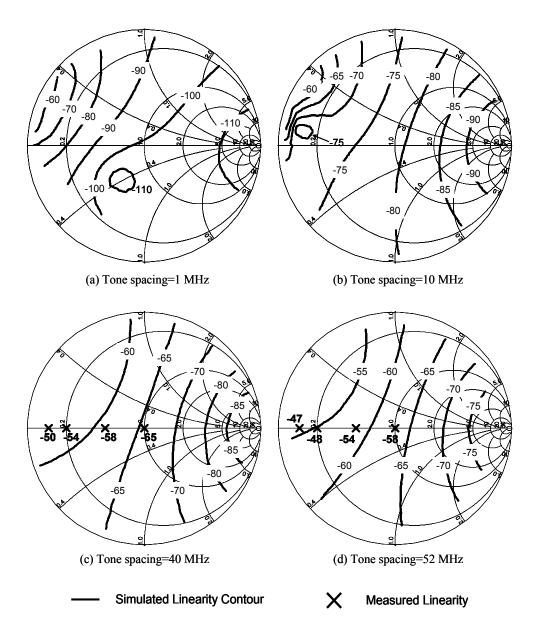

The novel high-linearity narrow tone-spacing varactor stack configuration is based on a Volterra analysis of the circuit shown in Fig. 3.1. As a measure of the varactor linearity we consider the  $IM_3$  current flowing through the varactor diodes at frequency  $(2f_1-f_2)$ .

The low-frequency impedance of the center-tap is set to zero  $[Z_c(f_2-f_1) = 0]$  while this center-tap impedance is set to infinity at the higher harmonics. Using general Volterra series techniques [2], the resulting  $IM_3$  at narrow tone spacing  $[(f_2-f_1)/f_1 \approx 0]$ for this specific varactor configuration can be achieved, namely:

$$IM_{3}\Big|_{Z_{c}(s=0)=0} = \frac{(3c_{0}c_{2} - 2c_{1}^{2})\overset{^{2}}{A}}{2c_{0}^{2}(s_{RF}c_{0}Z_{s}(-s_{RF}) - 2)(s_{RF}c_{0}Z_{s}(s_{RF}) + 2)^{2}}$$

(3.1)

where

$$c_0 = C(V_R), \qquad (3.2)$$

$$c_1 = \frac{1}{2} \frac{dC(V_R)}{dV_R},$$

(3.3)

$$c_2 = \frac{1}{6} \frac{d^2 C(V_R)}{d^2 V_R}$$

(3.4)

are the capacitance Taylor coefficients of each varactor diode with  $V_R$  being the reverse applied voltage with a positive value,  $Z_s(s)$  is the source impedance,  $s_{RF}$  is the complex RF center frequency ( $j\omega_{RF}$ ) of the two-tone signal and  $\hat{A}$  represents the voltage amplitude of the source signal.

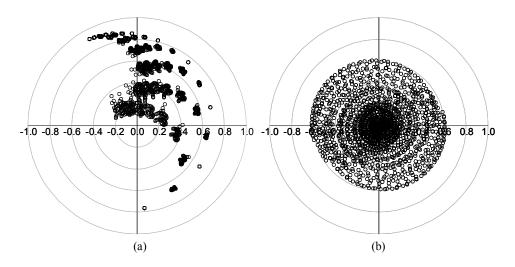

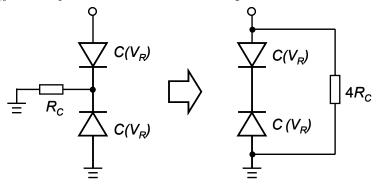

Fig. 3.1. Schematic for the Volterra analysis of the anti-series varactor diode circuit.

By setting (3.1) to zero we can enforce  $IM_3$  cancellation and we find an exponential  $C(V_R)$  relation for the varactors, i.e.,

$$C(V_R) = a_1 \exp(-a_2 V_R)$$

. (3.5)

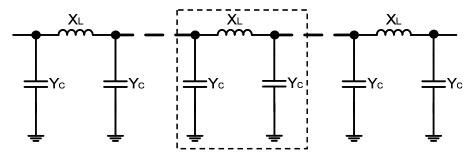

In this relation,  $a_1$  and  $a_2$  indicate the integration constants, which add some flexibility to the solution. Note that any choice of  $a_1$  and  $a_2$  with positive values will satisfy (3.1) yielding perfect cancellation of the  $IM_3$  distortion component. For this low distortion to be achieved in practice, there must be a *low impedance* path (relative to the AC impedance of the varactor capacitance itself) between the center node c and two RF terminals (a and b) of the varactor stack at low frequency ( $f_2$ - $f_1$ ). At the same time, there must be a *high impedance* path for the high frequency components (fundamental and higher harmonics) of the impedance between the center node c and two RF terminals (a and b) of the varactor stack. When these conditions are met, a very high linearity tunable capacitance is achieved between the RF terminals of the varactor stack.

Note that the condition for  $IM_3$  cancellation [numerator of (3.1) equal to zero] only demands a functional relation between the Taylor coefficients, which is fully satisfied by using varactors with an exponential  $C(V_R)$  relation. Consequently, the achieved  $IM_3$ cancellation does not depend on the value of the reverse bias voltage, nor the surrounding circuitry [Note, for example, that  $Z_s$  does not appear in the numerator of (3.1)]. Therefore, this low-distortion tunable capacitive element can be applied in any circuit topology (including series configuration), provided that the designer takes the proper measures to guarantee the low-impedance paths for the baseband components between the center node *c* and the RF terminals (*a* and *b*), while loading of the center node for higher frequencies should be avoided. The resulting component will also exhibit excellent in-band linearity for the typical wireless complex modulated signals. Linearity restrictions with respect to the bandwidth of these signals (e.g. B >> 10MHz), only arise when the baseband short circuit between center node and RF terminals fails to provide a sufficiently low impedance.

#### **3.3 Doping Profile and Performance Compromise**

#### **3.3.1 Doping Profile**

Based on a Volterra series analysis and the solution of (3.1), the desired capacitance-voltage relation for ideal  $IM_3$  cancellation was determined in (3.5). The next step is to determine the required doping profile. For this purpose we assume a one-sided junction (e.g. a Schottky diode) and solve for the doping profile using [3]

$$N(x) = \frac{C(V_R)^3}{e\varepsilon_s} \left(\frac{dC(V_R)}{dV_R}\right)^{-1}$$

(3.6)

where

$$x = \frac{\varepsilon_s}{C(V_R)} \quad . \tag{3.7}$$

Making use of these relations, it can be shown that the required doping profile for an exponential capacitance voltage relation is

$$N(x) = N_d x^{-2} (3.8)$$

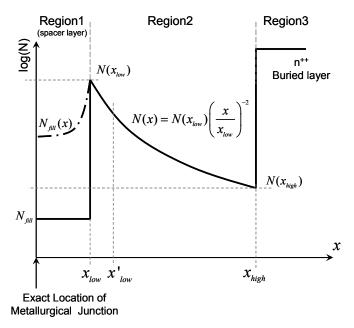

in which  $N_d$  is a doping concentration constant to be defined and x is the distance from the metallurgical junction. It should be noted that this result is singular for x = 0, and measures to avoid this singularity must be taken. In order to explain how the doping profile should be defined, we consider Fig. 3.2.

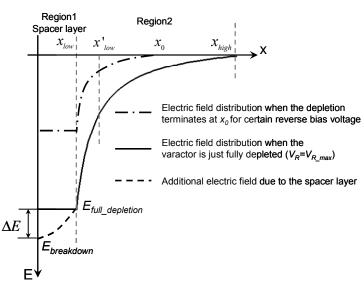

Fig. 3.2. Required varactor doping profile of the narrow tone-spacing varactor stack, to achieve the exponential  $C(V_R)$  relation. The black dashed line shows the restriction on the doping level of the "spacer" layer due to the sheet resistance (see Appendix *A*). The solid line represents the ideal doping profile (see Appendix *B*).

In this figure, the ideal doping profile is indicated by the solid line. Since we cannot provide an infinitely high or extremely low doping concentration, this limits the validity of the  $N_d x^{-2}$  relationship between  $x_{low}$  and  $x_{high}$ . Therefore, we define the useful capacitance tuning range  $(T_{tune})$ , since the capacitance is inversely proportional to the distance x, i.e.,

$$T_{tune} = \frac{C_{\max}}{C_{\min}} = x_{high} / x_{low}$$

(3.9)

To maintain the "exponential"  $C(V_R)$  relation, a spacer layer (Region 1 in Fig. 3.2) is

required in order to satisfy the  $N_d x^{-2}$  doping versus depth relation with respect to the metallurgical junction position (e.g. a doubling in distance to the metallurgical junction should result in one-fourth the doping concentration). To avoid reduced breakdown voltage, quality factor and capacitance tuning range ( $T_{tune}$ ), the normally-depleted spacer layer should not significantly increase the electric field. To achieve this, the doping concentration of this spacer layer must be kept low with respect to  $N(x_{low})$ . In Appendix A this is analyzed, resulting in a lower bound on the effective sheet resistance of this spacer layer.

Here we assume for reasons of simplicity that the low doped spacer layer consumes the total built-in voltage of the junction, while the applied voltage is used to deplete the  $N_d x^{-2}$  region. As a result, the exponential  $C(V_R)$  relation of the fabricated diode (see Appendix *B*) is given by

$$C(V_R) = \frac{A\varepsilon_s}{x_{low}} \exp\left(-\frac{\varepsilon_s}{eN(x_{low})x_{low}^2}V_R\right)$$

(3.10)

where A is the area of the capacitor and the constant ( $A\varepsilon_s / x_{low}$ ) represents the zero bias capacitance value.

Although, in principle we can always choose an appropriate doping concentration of the spacer layer to make (3.10) valid, some practical implementations might use an even lower doping of the spacer layer. In this situation, the depletion distance  $(x'_{low})$  at zero applied voltage can be larger than  $x_{low}$ , as shown in Fig. 3.2, and consequently the  $C(V_R)$  relation has to be modified to (Appendix B):

$$C(V_R) = \frac{A\varepsilon_s}{x'_{low}} \exp\left(-\frac{\varepsilon_s}{eN(x_{low})x_{low}^2}V_R\right).$$

(3.11)

The formulation above indicates that the zero-bias capacitor value is now  $A\varepsilon_s / x'_{low}$ , which will reduce the capacitance tuning range by a factor of  $x'_{low} / x_{low}$  for the same maximum depletion depth  $(x_{high})$ . Note that although the tuning range is reduced, the exponential  $C(V_R)$  relation remains, and the  $IM_3$  distortion cancellation condition is still valid. In addition, due to the same doping profile in the  $N_d x^{-2}$  region, the exponent coefficient  $a_2$  in (3.5) is unchanged. Later, we investigate the doping profile constraints for practical varactor implementations, which exhibit deviations from the ideal profile.

## **3.3.2 Varactor Diode Performance Tradeoffs**

Based on the equations above, we can optimize the tuning range and quality factor of the varactor for a maximum reverse applied voltage  $(V_{R_max})$ . The maximum operation voltage  $(V_{R_max})$ , the series resistance *R* and the quality factor at zero applied voltage  $(Q|_{V_R=0})$  of the varactor are given by:

$$V_{R_{max}} = \frac{eN(x_{low})x_{low}^{2}}{\varepsilon_{s}} \left( \ln \frac{x_{high}}{x_{low}} \right)$$

(3.12)

$$R\Big|_{V_R=0} = \int_{x_{low}}^{x_{high}} \rho(x) \frac{dx}{A} = \frac{1}{Ae\mu_n N(x_{low}) x_{low}^2} \left(\frac{x_{high}^3}{3} - \frac{x_{low}^3}{3}\right)$$

(3.13)

$$Q\Big|_{V_R=0} = \frac{\left|\frac{1}{j\omega C}\right|}{R\Big|_{V_R=0}} = \frac{3e\mu_n N(x_{low})}{\omega \varepsilon_s \left[\left(\frac{x_{high}}{x_{low}}\right)^3 - 1\right]}$$

(3.14)

where  $\mu_n$  is the electron mobility.

Since the increase of the electric field due to the lightly doped spacer layer can be neglected, we can use the electric field at the boundary of lightly doped region (Region 1 in Fig. 3.2) and the  $N_d x^{-2}$  region (Region 2 in Fig. 3.2) to estimate the peak electric field when the capacitor is just fully depleted ( $V_R = V_{R_max}$ ), which is given by

$$E_{full\_depletion} = \frac{eN(x_{low})x_{low}^{2}}{\varepsilon_{s}} \left(\frac{1}{x_{low}} - \frac{1}{x_{high}}\right) \le E_{breakdown} \approx 6 \times 10^{5} \text{ V/cm}. \quad (3.15)$$

Based on (3.9) and (3.12)-(3.15), the quality factor at zero bias can be rewritten as

$$Q\Big|_{V_R=0} = \frac{3\mu_n \ln(T_{tune})}{\omega V_{R_{max}}(T_{tune}^3 - 1)} \left(\frac{T_{tune}E_{full\_depletion}}{T_{tune} - 1}\right)^2.$$

(3.16)

Since the quality factor at zero bias is proportional to the square of  $E_{full\_depletion}$  for a given tuning range and maximum reverse applied voltage, the quality factor can be optimized by dimensioning the varactor such that  $E_{full\_depletion} = E_{breakdown}$ , which is, for

silicon, approximately  $6 \times 10^5$  V/cm [3]. Consequently, the maximum reverse applied voltage to deplete the varactor should be chosen close to the breakdown voltage of the varactor. Using this approach, the maximum achievable quality factors at zero bias  $(Q_{opt})$  for different  $V_{R_max}$  and tuning ranges  $C_{max}/C_{min}$ ) are listed in Table V for a silicon implementation.

| Tuning<br>Range<br>$(T_{tune})$ | $V_{R_{max}} = 5 \text{ V}$ | $V_{R_{max}} = 10 \text{ V}$ | $V_{R_max} = 20 \text{ V}$   | $V_{R_max} = 40 \text{ V}$   |

|---------------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|

| 3                               | $Q_{opt} = 1634$            | $Q_{opt} = 817$              | $Q_{opt} = 408$              | $Q_{opt} = 205$              |

|                                 | $a_2 = 0.22 \text{ V}^{-1}$ | $a_2 = 0.11 \text{ V}^{-1}$  | $a_2 = 0.055 \text{ V}^{-1}$ | $a_2 = 0.028 \text{ V}^{-1}$ |

| 6                               | $Q_{opt} = 206$             | $Q_{opt} = 103$              | $Q_{opt} = 52$               | $Q_{opt} = 26$               |

|                                 | $a_2 = 0.36 \text{ V}^{-1}$ | $a_2 = 0.18 \text{ V}^{-1}$  | $a_2 = 0.09 \text{ V}^{-1}$  | $a_2 = 0.045 \text{ V}^{-1}$ |

| 9                               | $Q_{opt} = 66$              | $Q_{opt} = 33$               | $Q_{opt} = 16$               | $Q_{opt} = 8$                |

|                                 | $a_2 = 0.44 \text{ V}^{-1}$ | $a_2 = 0.22 \text{ V}^{-1}$  | $a_2 = 0.11 \text{ V}^{-1}$  | $a_2 = 0.055 \text{ V}^{-1}$ |

| 12                              | $Q_{opt} = 30$              | $Q_{opt} = 15$               | $Q_{opt} = 7$                | $Q_{opt} = 4$                |

|                                 | $a_2 = 0.50 \text{ V}^{-1}$ | $a_2 = 0.25 \text{ V}^{-1}$  | $a_2 = 0.12 \text{ V}^{-1}$  | $a_2 = 0.062 \text{ V}^{-1}$ |

| 15                              | $Q_{opt} = 16$              | $Q_{opt} = 8$                | $Q_{opt} = 4$                | $Q_{opt} = 2$                |

|                                 | $a_2 = 0.54 \text{ V}^{-1}$ | $a_2 = 0.27 \text{ V}^{-1}$  | $a_2 = 0.14 \text{ V}^{-1}$  | $a_2 = 0.070 \text{ V}^{-1}$ |

Table V. Optimized calculated quality factor at 2 GHz for given tuning range ( $T_{tune}$ ) and  $V_{R max}$  ( $\mu_n = 1000 \text{ cm}^2/\text{V}\cdot\text{s}$ )

As indicated by (3.16), for a given fixed tuning range ( $T_{tune}$ ), the optimized quality factor ( $Q_{opt}$ ) is inversely proportional to the maximum operation voltage ( $V_{R_max}$ ). The quality factor can be further improved through the use of wide bandgap materials, since these materials allow higher electric fields at the device junction and typically provide higher mobilities, enabling even higher quality factor values. For example, in GaAs an enhancement factor of 6 is feasible since  $\mu_n = 6000 \text{ cm}^2/(\text{V} \cdot \text{s})$  and  $E_{breakdown} = 6 \times 10^5 \text{ V/cm}$ , and in SiC even a factor of 25 is possible with  $\mu_n = 900 \text{ cm}^2/(\text{V} \cdot \text{s})$  and  $E_{breakdown} = 3 \times 10^6 \text{ V/cm}$ .

### 3.4 The Influence of *IM*<sup>5</sup> on the Linearity

#### 3.4.1 Fifth-order Volterra Series Analysis

Although the exponential  $C(V_R)$  relation is very effective in cancelling the thirdorder intermodulation  $(IM_3)$ , and all even distortion products are canceled by the symmetric anti-series varactor configuration, fifth-order intermodulation  $(IM_5)$  is still present. In the following analysis of the fifth-order distortion, we use the same termination conditions at the center tap as for the  $IM_3$  cancellation, i.e.  $Z_c(f_2-f_1) = 0$ , while  $Z_c(f)$  is infinity for all other frequency components. Next, we substitute the  $C(V_R)$ relation from (3.5) into the  $IM_5$  formulation. To simplify the analysis, we assume  $\Delta f \rightarrow 0$  and  $Z_s(s) \rightarrow 0$ , yielding the  $IM_5$  products that appear at the  $IM_3$  frequencies,  $2f_1-f_2$  and  $2f_2-f_1$ , namely:

$$IM_{5} \approx \frac{5}{768} \left( a_{2} \stackrel{\circ}{A} \right)^{4}$$

(3.17)

where  $a_2 = -\varepsilon_s / (eN(x_{low})x_{low}^2)$  is the exponential coefficient of  $C(V_R)$  relation (3.5) and  $\hat{A}$  is the amplitude of the two-tone test signal at the fundamental frequencies. In order to be consistent with our further discussions, we replace  $\hat{A}$  by  $V_{RF\_peak}$ , which represents the peak amplitude of the two-tone input voltage signal. Hence, (3.17) becomes

$$IM_5 \approx \frac{5}{768} a_2^{-4} \left(\frac{V_{RF\_peak}}{2}\right)^4.$$

(3.18)

Based on (3.18), the fifth-order input intercept point  $(IIP_5)$  can be expressed as

$$IIP_{5} \approx 4 \cdot \left(\frac{48}{5}\right)^{1/4} \frac{1}{a_{2}} = \frac{7.04}{a_{2}} .$$

(3.19)

Note that the *IIP*<sub>5</sub> is independent of the applied control voltage at the center pin and only depends on the grading coefficient  $a_2$ , which can be chosen freely to adjust the tuning range. Practical values of  $a_2$  are in the range of  $0.028 \text{ V}^{-1}$  to  $0.54 \text{ V}^{-1}$  (see Table V), yielding *IIP*<sub>5</sub> values of 12 V to 256 V. Since the *IM*<sub>5</sub> drops at the rate of 80 dB per decade, outstanding linearity can be achieved for even modest *IIP*<sub>5</sub> values.

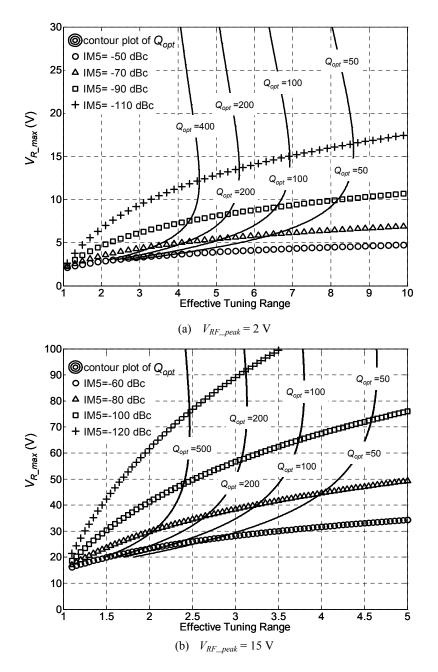

# 3.4.2 Tradeoff between Linearity, Quality factor, $V_{R_max}$ and Effective Tuning Range

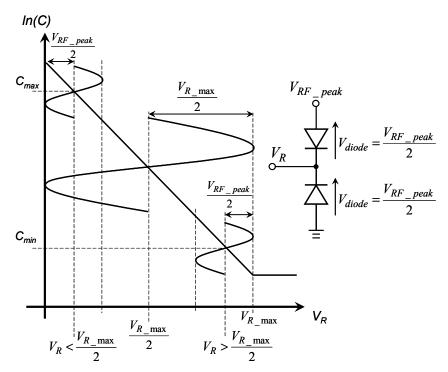

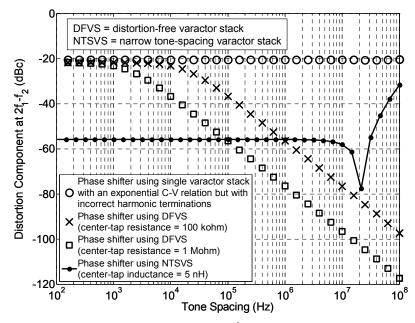

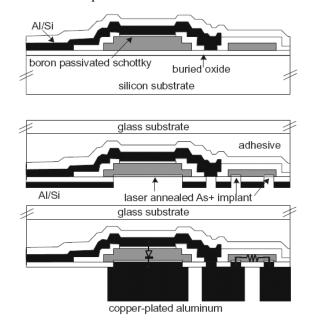

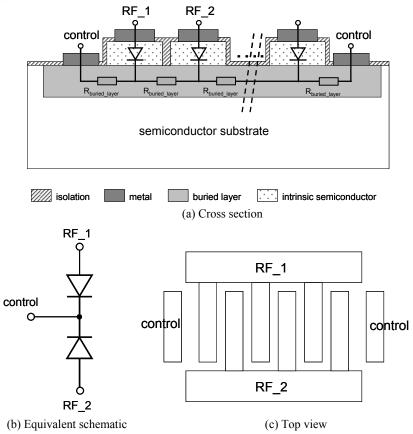

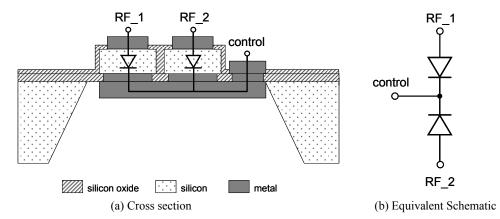

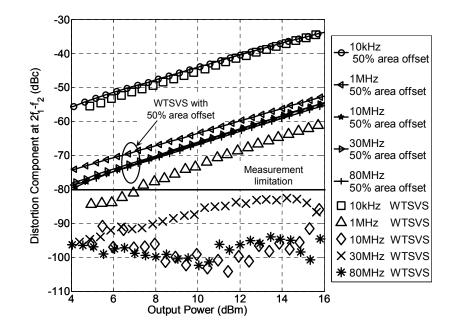

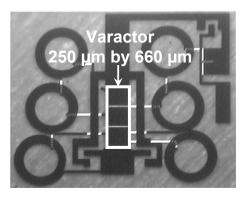

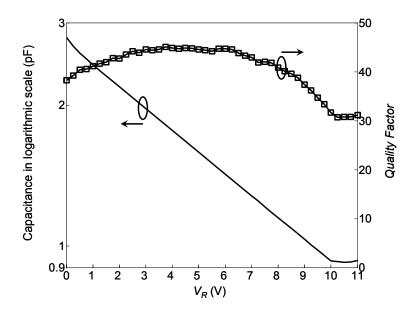

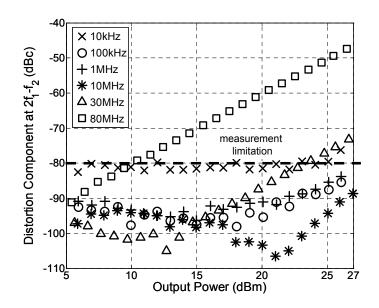

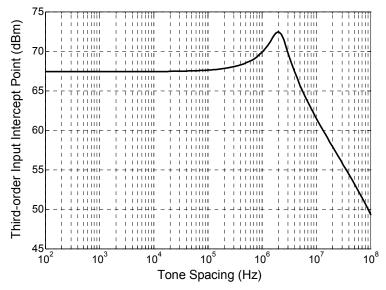

The discussion in Section 3.2 did not account for the signal swing when calculating tuning range limits. In practical situations, the RF voltage swing will reduce the effective tuning range. For these reasons, it is useful to repeat the capacitance tuning range analysis for large-signal operation by including breakdown, forward biasing and linearity constraints.