# Low-Power High-Accuracy Smart Temperature Sensors in CMOS Technology

# André Luiz Aita

893241

Low-Power High-Accuracy Smart Temperature Sensors in CMOS Technology

# Low-Power High-Accuracy Smart Temperature Sensors in CMOS Technology

Proefschrift

TU Delft Library Prometheusplein 1 2628 ZC Delft

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 1 maart 2011 om 15:00 uur

door

# André Luiz AITA

Electrical Engineer and Master of Computer Science Federal University of Rio Grande do Sul, Brazil

geboren te Santa Maria, RS, Brazilië

Dit proefschrift is goedgekeurd door de promotor:

Prof.dr.ir. G.C.M. Meijer

Samenstelling promotiecommissie:

| Rector Magnificus               | voorzitter                                |

|---------------------------------|-------------------------------------------|

| Prof.dr.ir. G.C.M. Meijer       | Technische Universiteit Delft, promotor   |

| Prof.dr. S. Bampi               | Federal University of Rio Grande do Sul   |

| Prof.ir. A.J.M. van Tuijl       | Universiteit Twente                       |

| Prof.dr. J.R. Long              | Technische Universiteit Delft             |

| Prof.dr.ir. A.H.M. van Roermund | Technische Universiteit Eindhoven         |

| Prof.dr.ir. J.H. Huijsing       | Technische Universiteit Delft             |

| Dr.ir. M.A.P. Pertijs           | Technische Universiteit Delft             |

| Prof.dr. P.J. French            | Technische Universiteit Delft, reservelid |

|                                 |                                           |

This work was supported by Universidade Federal de Santa Maria, Brazil and by Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - CAPES, Brazil, grant BEX 1877/03-8.

Printed by PrintPartners Ipskamp, Enschede

ISBN: 978-90-813316-9-2

Keywords: integrated smart temperature sensors, CMOS-compatible substrate PNP transistors,  $\Delta\Sigma$  A/D converters

Copyright ©2011 A. L. Aita. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior permission in writing from the author.

PRINTED IN THE NETHERLANDS

To my wife Letícia. To my parents, Vinício (in memoriam) and Aldonir.

There is a legend about a bird which sings just once in its life, more sweetly than any other creature on the face of the earth. From the moment it leaves the nest it searches for a thorn tree, and does not rest until it has found one. Then, singing among the savage branches, it impales itself upon the longest, sharpest spine. And, dying, it rises above its own agony to outcarol the lark and the nightingale. One superlative song, existence the price. But the whole world stills to listen, and God in His heaven smiles. For the best is only bought at the cost of great pain... or so says the legend.

> The Thorn Birds Colleen McCullough

# Contents

| C | ontei | nts                                                                    | ix |

|---|-------|------------------------------------------------------------------------|----|

| 1 | Inti  | roduction                                                              | 1  |

|   | 1.1   | Smart (temperature) sensors                                            | 2  |

|   | 1.2   | Temperature sensors applications                                       | 2  |

|   |       | 1.2.1 Sensing applications                                             | 3  |

|   |       | 1.2.2 Biomedical and clinical (medical) applications                   | 3  |

|   |       | 1.2.3 Military, industrial and commercial applications                 | 4  |

|   |       | 1.2.4 Domestic appliances                                              | 4  |

|   |       | 1.2.5 Temperature sensors for autonomous systems                       | 4  |

|   | 1.3   | General characteristics of a sensor                                    | 4  |

|   | 1.4   | State-of-the-art of smart temperature sensors                          | 6  |

|   | 1.5   | Design approach for accuracy and low-power                             | 8  |

|   | 1.6   | Motivation and objectives                                              | 8  |

|   | 1.7   | Organization of the thesis                                             | 9  |

| 2 | Ten   | nperature Sensing Fundamentals                                         | 11 |

|   | 2.1   | Introduction                                                           | 11 |

|   | 2.2   | Application-related requirements                                       | 11 |

|   |       | 2.2.1 Other characteristics                                            | 13 |

|   | 2.3   | Temperature sensors                                                    | 14 |

|   |       | 2.3.1 Integrated temperature sensors                                   | 15 |

|   |       | 2.3.2 Platinum (Pt) resistors                                          | 16 |

|   | 2.4   | Bipolar transistors                                                    | 17 |

|   |       | 2.4.1 The ideal $I_D - V_D$ diode characteristic                       | 17 |

|   |       | 2.4.2 The ideal $I_C - V_{BE}$ bipolar transistor characteristic .     | 19 |

|   |       | 2.4.3 The effect of $I_S$ in the ideal $I_C - V_{BE}$ characteristic . | 21 |

|   |       |                                                                        | 22 |

|   |       |                                                                        | 22 |

|   |       |                                                                        | 25 |

|   |     | 2.4.6   | Process spread of $V_{BE}$                                                   | 26   |

|---|-----|---------|------------------------------------------------------------------------------|------|

|   |     |         | 2.4.6.1 Spread of the saturation current $I_S$                               | 27   |

|   |     |         | 2.4.6.2 Spread of the current gain $\beta$                                   | 28   |

|   |     |         | 2.4.6.3 Error due to non-ideal $\beta$ -compensation                         | 29   |

|   |     | 2.4.7   | Effect of variations in the bias current                                     | 30   |

|   |     | 2.4.8   | Other effects                                                                | 32   |

|   |     | 2.4.9   | Bipolar transistors in CMOS technology                                       | 33   |

|   | 2.5 |         | usions                                                                       | 33   |

| 3 | Sen | sor Fre | ont-End                                                                      | 35   |

| 0 | 3.1 |         | luction                                                                      | 35   |

|   | 3.2 |         | art temperature sensor                                                       | 36   |

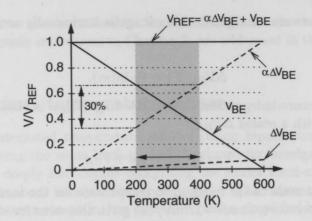

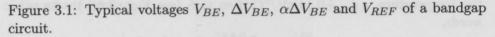

|   | 0.2 | 3.2.1   | Concepts for bandgap references                                              | 36   |

|   |     | 3.2.2   | Ratiometric temperature measurement                                          | 37   |

|   | 3.3 |         | acy requirements and power constraints                                       | 38   |

|   | 0.0 | 3.3.1   | Error and power budgeting                                                    | 39   |

|   |     | 3.3.2   | Temperature reading errors - Errors in $V_{BE}$ , $\Delta V_{BE}$ , $\alpha$ |      |

|   |     | 0.0.1   | and $m$ in the temperature reading $\ldots$                                  | 39   |

|   | 3.4 | The c   | current ratio $m$                                                            | 41   |

|   |     | 3.4.1   | Designing an accurate current ratio $m$                                      | 41   |

|   |     |         | 3.4.1.1 Error due to mismatch in the current sources                         | 41   |

|   |     |         | 3.4.1.2 Error due to mismatch in the current sources                         |      |

|   |     |         | with Dynamic Element Matching                                                | 42   |

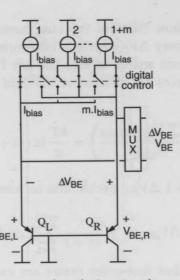

|   |     |         | 3.4.1.3 Error due to finite output impedance                                 | 43   |

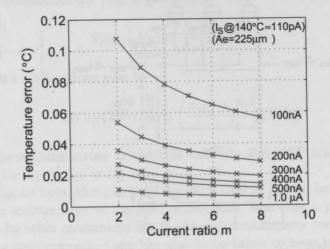

|   |     | 3.4.2   | The current ratio $m$ value $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$     | 44   |

|   |     |         | 3.4.2.1 $\Delta V_{BE}$ Sensitivity                                          | 46   |

|   |     |         | 3.4.2.2 Error due to the saturation current and switch                       |      |

|   |     |         | leakage                                                                      |      |

|   | 3.5 | Error   | due PNP transistors noise (output referred)                                  |      |

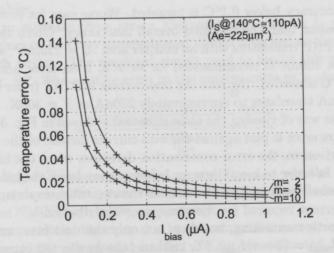

|   | 3.6 | The b   | bias current                                                                 |      |

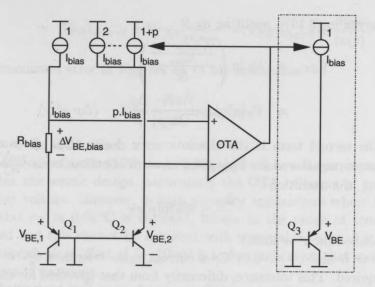

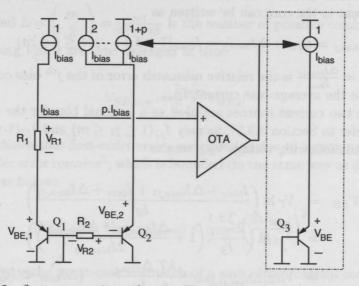

|   |     | 3.6.1   |                                                                              | 52   |

|   |     | 3.6.2   | The bias current and the current ratio $p$ of the bias                       |      |

|   |     |         | circuit                                                                      | 53   |

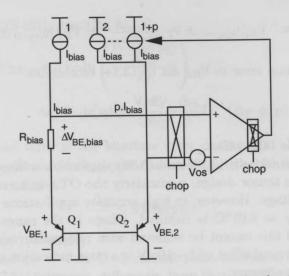

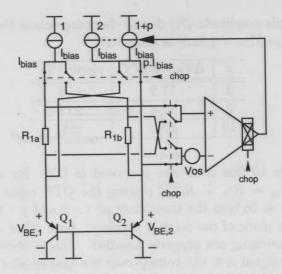

|   |     | 3.6.3   | Offset cancellation - chopping                                               |      |

|   |     | 3.6.4   | Compensation for the finite forward current gain $\beta$                     | 59   |

|   |     | 3.6.5   | Error due to mismatch in the current sources                                 | 60   |

|   |     |         | 3.6.5.1 Error due to mismatch in the current sources                         |      |

|   |     |         | with Dynamic Element Matching                                                |      |

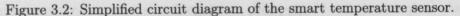

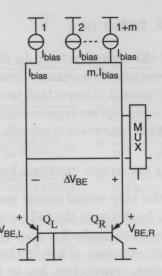

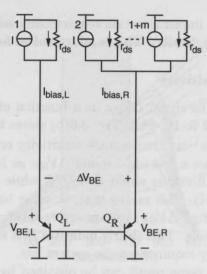

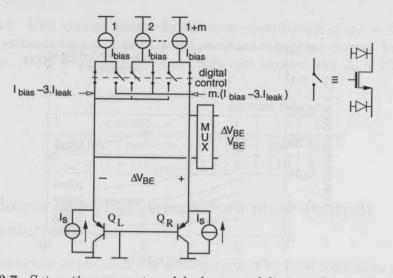

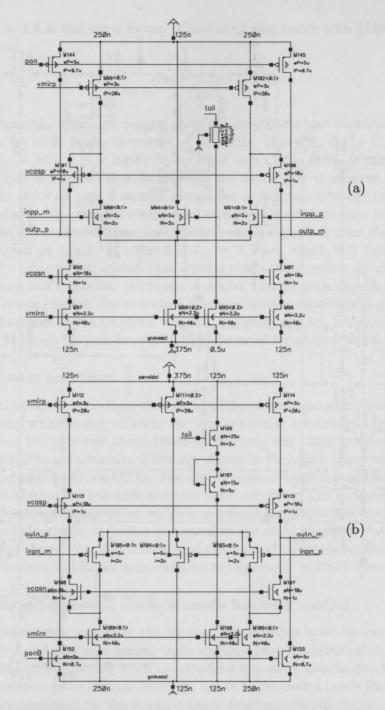

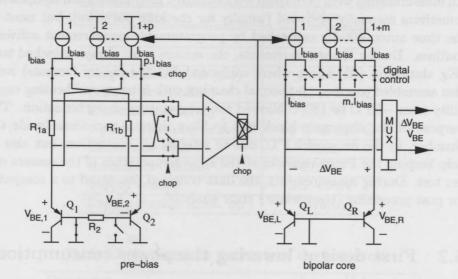

|   | 3.7 | Front   | t-end implementation                                                         |      |

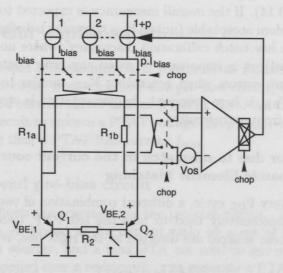

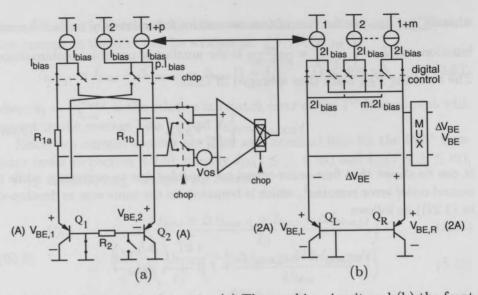

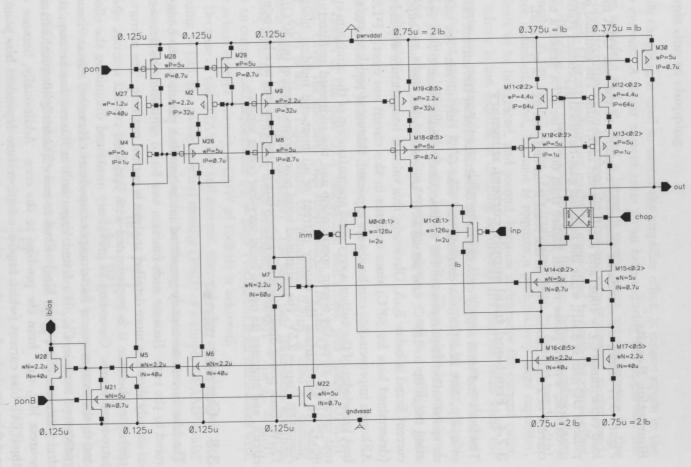

|   |     | 3.7.1   |                                                                              |      |

|   |     | 3.7.2   | Front-end core                                                               | . 64 |

x

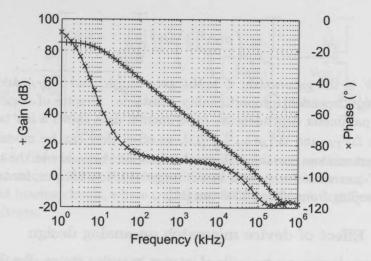

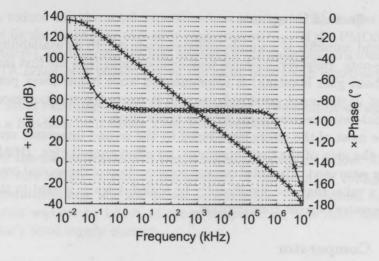

|   |                | 3.7.3              | The bias OTA                                                    | 64  |

|---|----------------|--------------------|-----------------------------------------------------------------|-----|

|   |                | 3.7.4              | Front-end total supply current summary                          | 67  |

|   | 3.8            | Curren             | nt mirror                                                       | 67  |

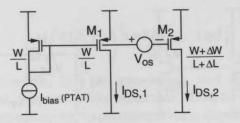

|   |                | 3.8.1              | Device mismatch models                                          | 69  |

|   |                | 3.8.2              | Effect of device mismatch on analog design                      | 70  |

|   |                | 3.8.3              | Current mirroring over temperature                              | 71  |

|   |                | 3.8.4              | Impact of device mismatch on the performance trade-             |     |

|   |                |                    | offs of front-end                                               | 72  |

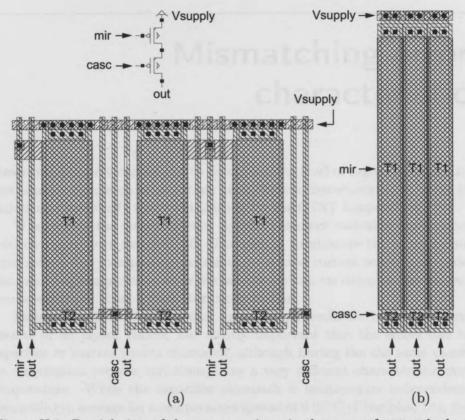

|   |                | 3.8.5              | Current mirror layout                                           | 75  |

|   | 3.9            | Calibr             | ation and trimming                                              | 75  |

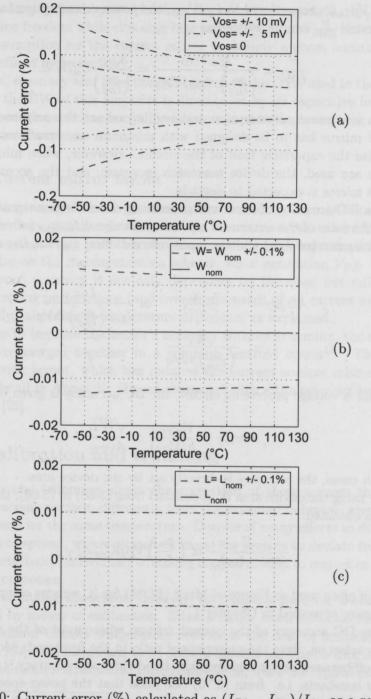

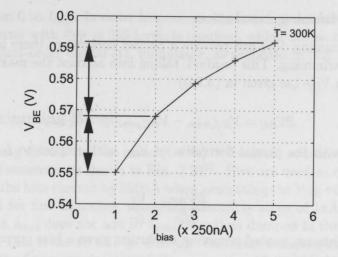

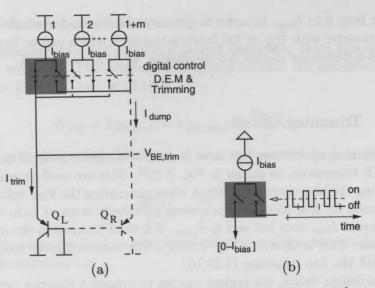

|   |                | 3.9.1              | $V_{BE}$ trimming by PNP bias-current adjusting                 | 76  |

|   |                | 3.9.2              | Trimming capability                                             | 78  |

|   |                | 3.9.3              | Trimming resolution                                             | 80  |

|   |                | 3.9.4              | Bitstream trimming                                              | 80  |

|   |                | 3.9.5              | Trimming circuit                                                | 81  |

|   |                | 3.9.6              | Other trimming methods                                          | 81  |

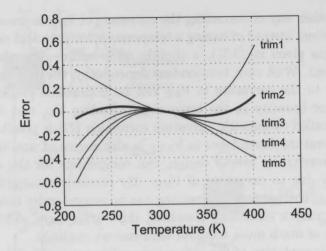

|   | 3.10           |                    | ture correction                                                 | 82  |

|   | 0.20           | 3.10.1             | Curvature correction and trimming                               | 83  |

|   | 3.11           | Conch              | isions                                                          | 84  |

|   |                | Control            |                                                                 | 04  |

| 4 | $\Delta\Sigma$ | A/D C              | Converters - Incremental Operation                              | 87  |

|   | 4.1            |                    | uction                                                          | 87  |

|   |                | 4.1.1              | Requirements                                                    | 88  |

|   |                | 4.1.2              | A/D converter architectures                                     | 89  |

|   | 4.2            | Analog             | g-to-digital (A/D) conversion                                   | 90  |

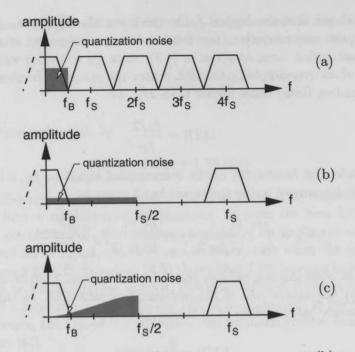

|   |                | 4.2.1              | Sampling and quantization                                       | 91  |

|   |                | 4.2.2              | Oversampling                                                    | 92  |

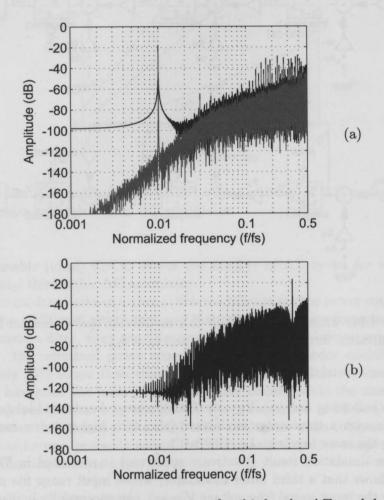

|   |                | 4.2.3              | Noise shaping                                                   | 93  |

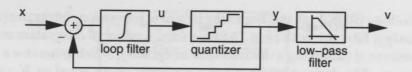

|   |                | 4.2.4              | $\Delta\Sigma A/D$ converters                                   | 95  |

|   |                | 4.2.5              | Incremental operation mode                                      | 95  |

|   | 4.3            | $\Delta \Sigma$ me | odulators                                                       | 96  |

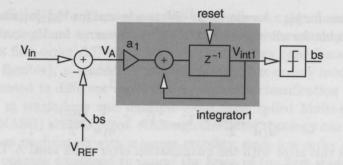

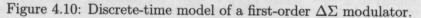

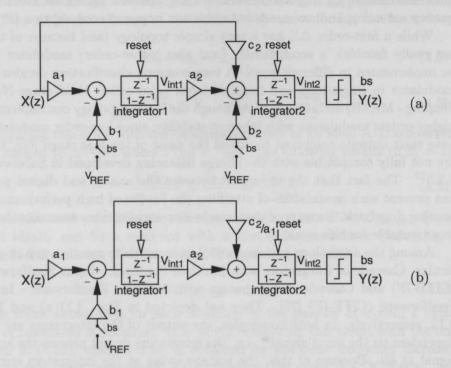

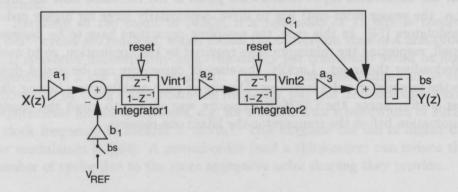

|   |                | 4.3.1              | $\Delta\Sigma$ modulators with discrete-time loop filters       | 96  |

|   |                | 4.3.2              | Current estimation of a $\Delta\Sigma$ modulator                | 97  |

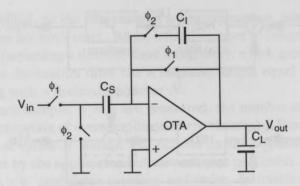

|   |                | 4.3.3              | Charge balancing                                                | 100 |

|   |                | 4.3.4              | Dynamic range extension                                         | 101 |

|   |                |                    | 4.3.4.1 Composition of $V_{TEMP}$                               | 103 |

|   |                |                    | 4.3.4.2 An optimized voltage $V_{TEMP}$                         | 105 |

|   |                |                    | 4.3.4.3 Charge balancing for $V_{TEMP}$                         | 106 |

|   |                |                    | 4.3.4.4 $V_{TEMP}$ implementation trade-off                     | 106 |

|   |                | 4.3.5              | System level decisions when designing $\Delta\Sigma$ modulators | 108 |

|   |                |                    | 4.3.5.1 Single-ended and differential structures                | 108 |

|   |                |                    |                                                                 | 100 |

|     |      | 4.3.5.2 Continuous- and discrete-ti                                           | ime realizations | 109   |

|-----|------|-------------------------------------------------------------------------------|------------------|-------|

|     |      | 4.3.5.3 Modulator Order                                                       |                  | 109   |

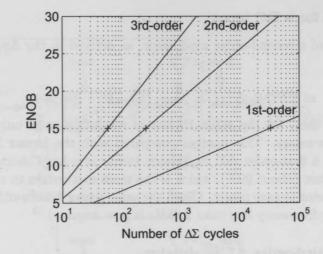

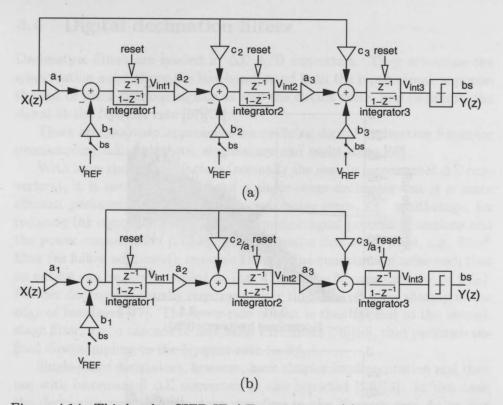

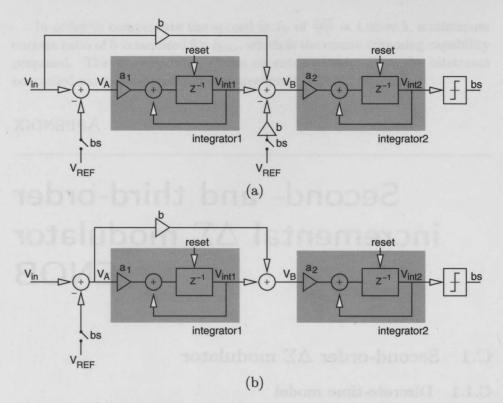

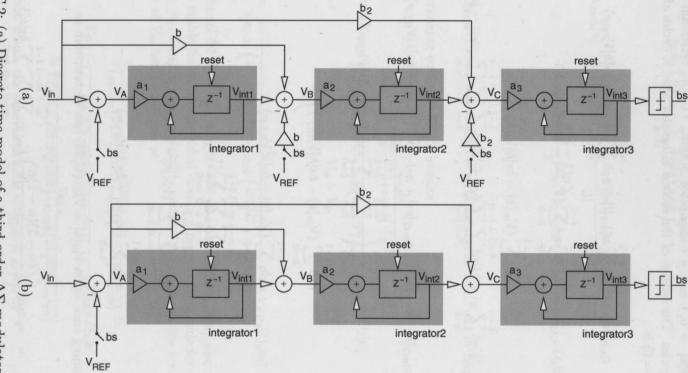

|     |      | 4.3.6 First, second and third-order $\Delta\Sigma$ mo                         | odulators        | 110   |

|     |      | 4.3.6.1 First-order $\Delta\Sigma$ modulator                                  |                  | 110   |

|     |      | 4.3.6.2 Second-order $\Delta\Sigma$ modulate                                  | or               | 114   |

|     |      | 4.3.6.3 Third-order $\Delta\Sigma$ modulator                                  |                  | 117   |

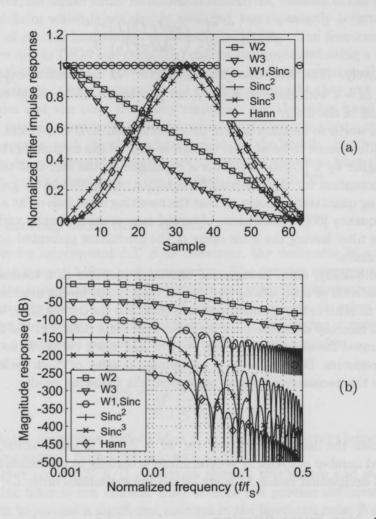

|     | 4.4  | Digital decimation filters                                                    |                  | 121   |

|     |      | 4.4.1 Direct calculation of the digital outp                                  | out              |       |

|     |      | 4.4.2 Filtering using $\operatorname{Sinc}^L$ filters                         |                  | 122   |

|     |      | 4.4.3 Non-linear filtering                                                    |                  | 123   |

|     | 4.5  | Modulator error sources                                                       |                  |       |

|     |      | 4.5.1 Offset error                                                            |                  |       |

|     |      | 4.5.2 Gain error due to capacitor mismate                                     | ch               | 125   |

|     |      | 4.5.3 Error due to non-complete settling t                                    | time             |       |

|     |      | 4.5.4 Thermal noise                                                           |                  |       |

|     |      | 4.5.5 Error due to leakage current                                            |                  |       |

|     |      | 4.5.6 Error due to charge injection                                           |                  |       |

|     | 4.6  | The sampling capacitor                                                        |                  |       |

|     |      | 4.6.1 Minimum size sampling capacitor .                                       |                  |       |

|     |      | 4.6.2 Designing an accurate capacitor - D                                     |                  |       |

|     | 4.7  | Opamp offset cancellation - (CDS) Autozer                                     |                  |       |

|     | 4.8  | System level chopping                                                         |                  |       |

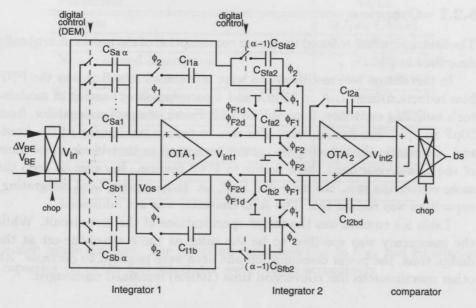

|     | 4.9  | $\Delta\Sigma$ modulator implementation                                       |                  |       |

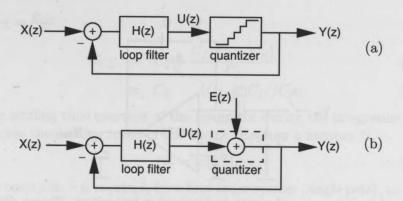

|     |      | 4.9.1 Integrators                                                             |                  |       |

|     |      | 4.9.1.1 First integrator                                                      |                  |       |

|     |      | 4.9.1.2 Second integrator                                                     |                  |       |

|     |      | 4.9.2 Comparator                                                              |                  |       |

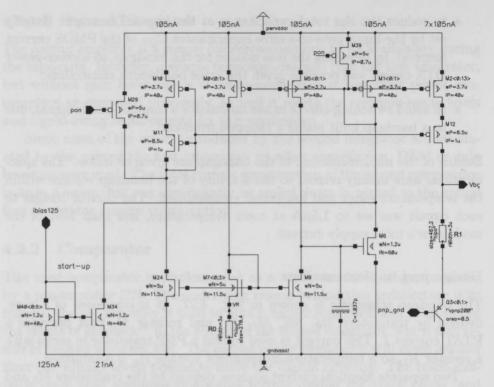

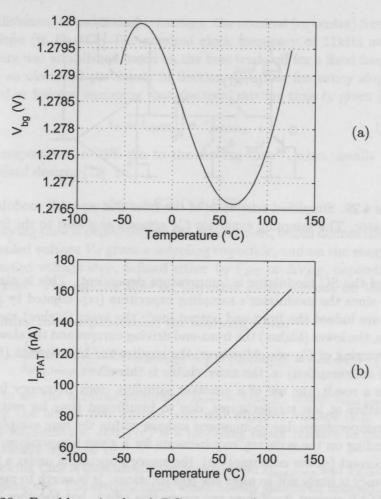

|     |      | 4.9.3 Bandgap                                                                 |                  |       |

|     | 4.10 | PTAT clock frequency                                                          |                  |       |

|     |      | 4.10.1 Implementation of the PTAT clock                                       |                  |       |

|     | 4.11 | Conclusions                                                                   |                  | 154   |

| 198 |      | 21.0 % And Physics of a lower shall be an |                  | 150   |

| 5   |      | alizations                                                                    |                  | 157   |

|     |      | System description                                                            |                  |       |

|     |      | 5.1.1 Measurement description                                                 |                  |       |

|     | 5.2  | First design: lowering the power consumption                                  |                  |       |

|     |      | 5.2.1 Overview                                                                |                  |       |

|     |      | 5.2.2 Implementation                                                          |                  |       |

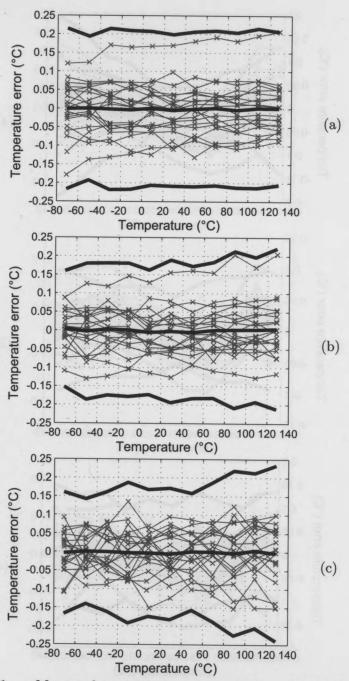

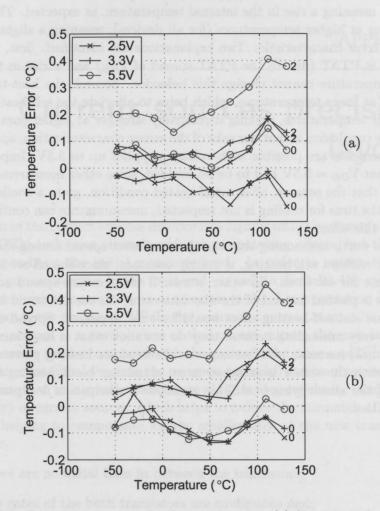

|     |      | 5.2.3 Experimental results                                                    |                  |       |

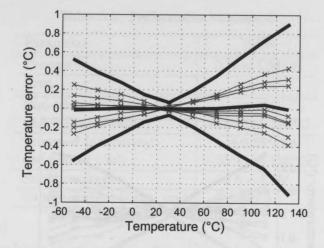

|     |      | 5.2.3.1 Batch calibration results                                             |                  |       |

|     |      | 5.2.3.2 Trimmed results                                                       |                  | . 162 |

### Contents

|   | 5.3  | A mic   | ro-power         | front-end                                        | 165 |

|---|------|---------|------------------|--------------------------------------------------|-----|

|   |      | 5.3.1   | Overvie          |                                                  | 165 |

|   |      | 5.3.2   | Descript         | tion                                             | 165 |

|   |      | 5.3.3   | Experim          | nental results                                   | 165 |

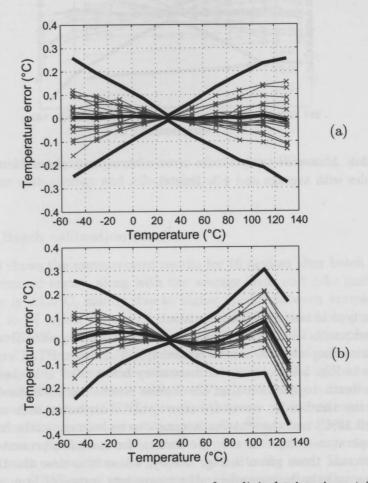

|   |      |         | 5.3.3.1          | Batch calibration                                | 166 |

|   |      |         | 5.3.3.2          | Trimmed results                                  | 166 |

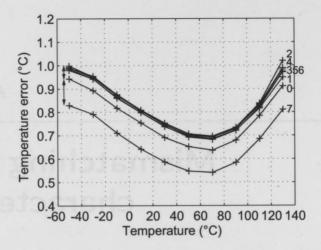

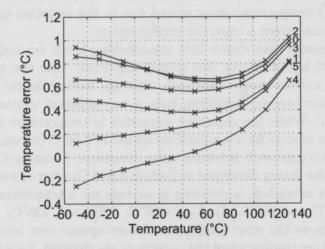

|   |      |         | 5.3.3.3          | DEM of current sources in $V_{BE}$ cycles        | 169 |

|   | 5.4  | A mic   | ro-power         | precision smart sensor                           | 170 |

|   |      | 5.4.1   | Overview         | w                                                | 170 |

|   |      | 5.4.2   | Descript         | tion                                             | 170 |

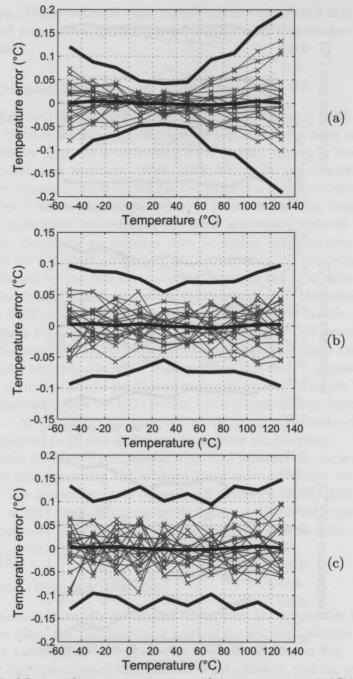

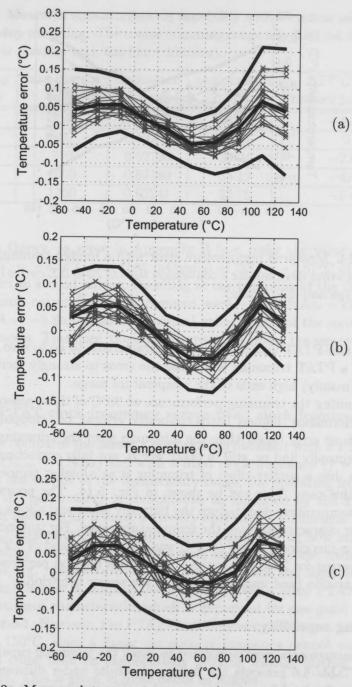

|   |      | 5.4.3   | Experim          | nental results                                   | 171 |

|   |      |         | 5.4.3.1          | Initial characterization                         | 172 |

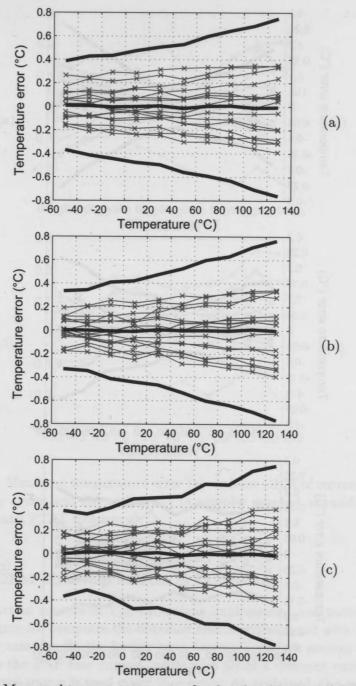

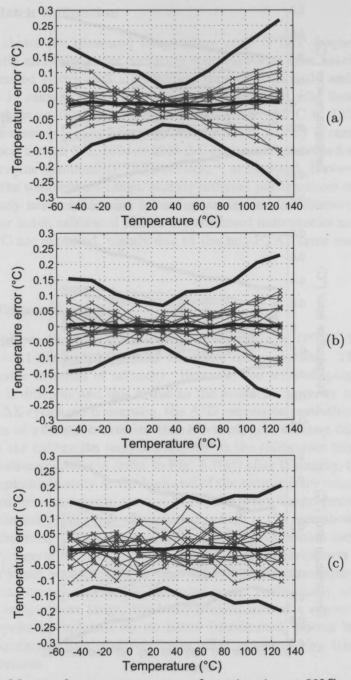

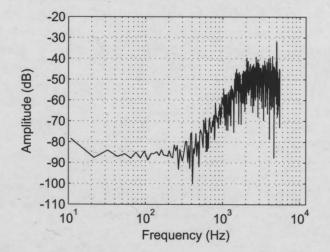

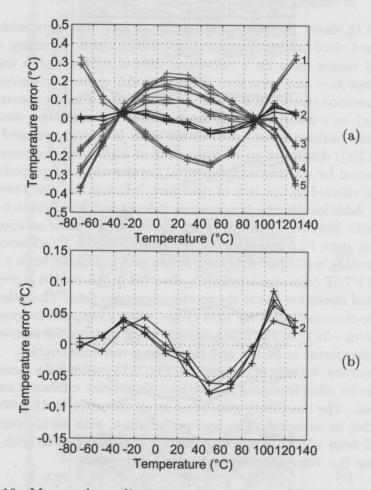

|   |      |         | 5.4.3.2          | Batch calibration results                        | 172 |

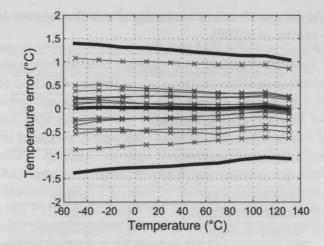

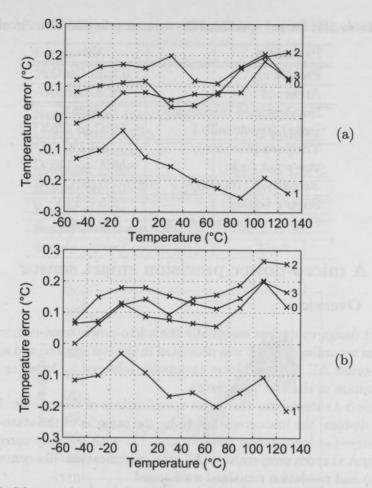

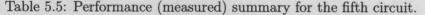

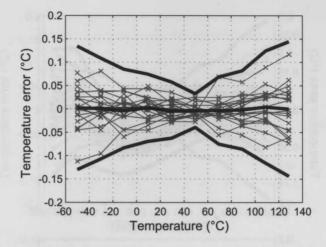

|   |      |         | 5.4.3.3          | Trimmed results                                  | 174 |

|   |      |         | 5.4.3.4          | PTAT clock frequency versus fixed clock fre-     |     |

|   |      |         |                  | quency                                           | 179 |

|   |      |         | 5.4.3.5          | Measurement at 150°C                             | 180 |

|   |      |         | 5.4.3.6          | Chip micrograph                                  | 181 |

|   |      | 5.4.4   | Benchm           | ark                                              | 181 |

|   | 5.5  | Conclu  | usions           |                                                  | 184 |

| 6 | Con  | clusio  | ns               |                                                  | 185 |

|   | 6.1  | Main f  | findings .       |                                                  | 185 |

|   | 6.2  |         |                  | outions                                          | 189 |

|   | 6.3  |         |                  | d perspectives                                   | 191 |

|   |      | 6.3.1   |                  | work                                             | 191 |

|   |      | 6.3.2   |                  | tives                                            | 192 |

|   |      |         |                  |                                                  | 102 |

| A | PN   | P trans | sistors-n        | nismatch effect on $\Delta V_{BE}$               | 195 |

| в | Trin | nming   | capabili         | ity                                              | 197 |

| С | Seco | ond- a  | nd third         | -order incremental $\Delta\Sigma$ modulator ENOB | 199 |

|   | C.1  | Second  | d-order $\Delta$ | $\Sigma$ modulator                               | 199 |

|   |      | C.1.1   | Discrete         | -time model                                      | 199 |

|   |      | C.1.2   | Resoluti         | on - Effective number of bits (ENOB)             | 200 |

|   | C.2  | Third-  |                  | modulator                                        | 202 |

|   |      | C.2.1   |                  | -time model                                      | 202 |

|   |      | C.2.2   |                  | e number of bits (ENOB)                          | 202 |

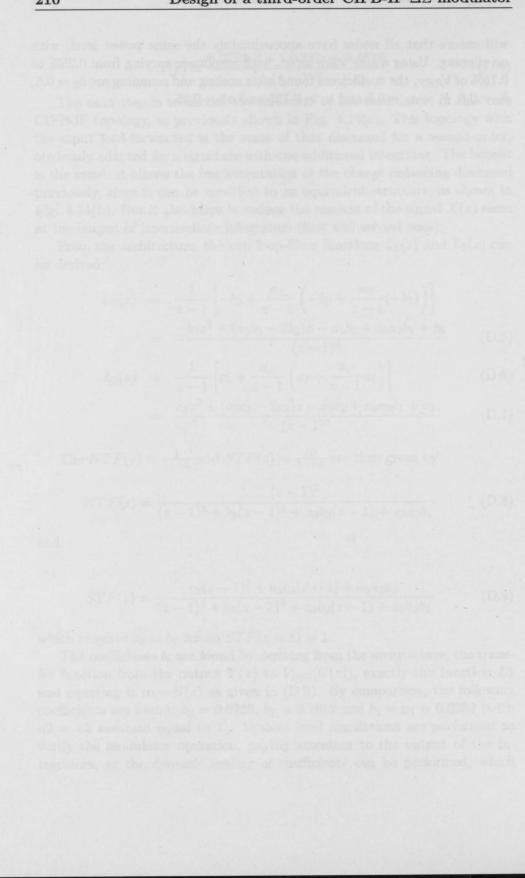

| D | Des  | ign of  | a third-o        | order CIFB-IF $\Delta\Sigma$ modulator           | 207 |

| xi | v                                    | Cor | ntents |

|----|--------------------------------------|-----|--------|

| Е  | Weak inversion operation             |     | 211    |

| F  | Integrator's opamp load capacitances |     | 213    |

| G  | Self-heating                         |     | 215    |

| н  | Current sources precision layout     |     | 219    |

| I  | Mismatching error characteristic     |     | 223    |

| Bi | ibliography                          |     | 225    |

# CHAPTER

# Introduction

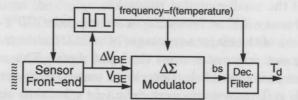

This thesis describes the theory, design and implementation of low-power high-accuracy CMOS smart temperature sensors. While there are several types of temperature sensors, the substrate PNP transistor, which is CMOS-compatible, was elected as the temperature sensor element.  $\Delta\Sigma$  A/D converters on the other hand were the elected architecture for data (temperature) conversion.

These choices, discussed in detail throughout this work, took into account the main goal of this work: the development of a low-power temperature sensor, while having a state-of-the-art accuracy of  $\pm 0.1^{\circ}$ C (after 1-point trimming) over a wide temperature range, i.e. the military range, from  $-55^{\circ}$ C to  $125^{\circ}$ C. Because of the well-known accuracy and power consumption tradeoff, advanced circuits techniques were needed to circumvent the limits set by this trade-off, allowing the establishment of a very high performance temperature sensor under a very low power consumption, below  $65\mu$ W at a supply voltage of 2.5V. In addition, another goal was to design a sensor with an enhanced non-trimmed accuracy (i.e. better than  $\pm 0.5^{\circ}$ C) to be able to reduce costs by omitting the need for individual trimming while providing sufficient accuracy for many applications.

Since the design of temperature sensors is a very mature topic, a lot of effort is required to accomplish a small performance improvement. Furthermore, relatively low frequencies, up to some hundreds of kHz, are typically used in temperature sensors. This may explain why, nowadays, such theme does not seem to arouse interest of many students (when compared to other more fashionable areas)<sup>1</sup>. However, the design of low-power high-accuracy smart temperature sensors poses great challenges and requires indeed a deep

<sup>&</sup>lt;sup>1</sup>Someone may doubt, but this statement is the author's belief.

knowledge of many instrumentation techniques (that in fact can be applied in many other areas). Temperature measurement is thus not only about measuring temperature but applying and developing instrumentation techniques and, why not, turning definitely electronics into art.

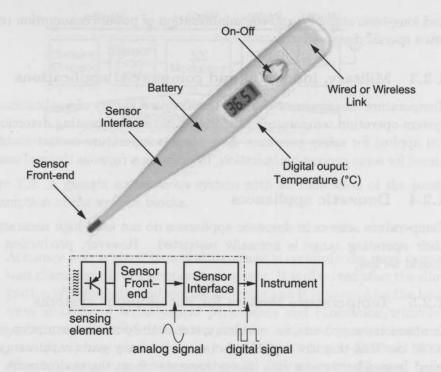

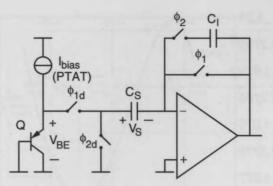

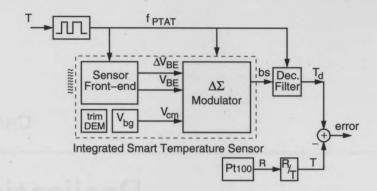

# 1.1 Smart (temperature) sensors

In electronics systems, a sensor can be defined as a device or circuit capable of perceiving some physical quantity, e.g. temperature, movement (speed and acceleration), position, humidity, etc, often translating this physical signal (from different energy domains) to the electrical domain [1]. Because of the analog nature of the physical quantity, the sensor is commonly combined with an analog interface (referred in this work as the sensor front-end). If this sensor is able to provide this result in a digital format, readily readable by a microprocessor or measurement instrument, by means of a data (A/D) converter or some application specific sensor interface<sup>2</sup>, it is then classified as a smart sensor. This is schematically shown in Fig. 1.1.

While the sensor integration is normally difficult with a stand-alone sensor, even if an integrated one, it is straightforward with a smart sensor. This easy connection sensor-processing unit has allowed the implementation of low-cost but fully functional systems (with actuators too). In other words, with smart temperature sensors it is simple to collect and combine data, and based on them to make decisions, providing some type of output.

However, because of technology issues, often it is not simple to make a sensor smart, e.g. the fabrication of a smart temperature sensor for temperatures higher than 300°C requires special IC technology that can stand to such temperatures [2]. However, for an intermediate range like -70°C to 130°C, this is perfectly possible with standard technologies. Problems related to the fact that sensing elements and electronics are put together cannot be forgotten. Among these problems, the interference of the digital part to the analog one is the most common, but other related to stability requirements, size and packaging also exists.

### **1.2** Temperature sensors applications

Temperature and smart temperature sensors are widely applied in many areas. Some of these applications/areas are reported below:

<sup>&</sup>lt;sup>2</sup>The interface can also be a general, low-cost and high-performance interface between sensing elements, named UTI (Universal Transducer Interface) [2].

Figure 1.1: Schematic of a smart sensor. The sensor interface can be either a specific application sensor interface, or an UTI or an A/D converter. The instrument can be either a measurement instrument, a micro-controller or a digital processing unit.

### 1.2.1 Sensing applications

Obviously the primary application of a temperature sensor is temperature measurement, either absolute or relative, or both, simultaneously. But temperature sensors are used also for measurement of other quantities, a process called temperature translation [3]. In addition, because many sensors show some degree of temperature sensitivity (an effect called cross-sensitivity), and because they cannot be shielded against temperature variations, temperature sensors can be used to measure their temperature, so to make some type of compensation possible [4].

### 1.2.2 Biomedical and clinical (medical) applications

Temperature measurement is also important for clinical evaluation. The restricted temperature range certainly eases the design, but the reliability and long-term stability, and the minimization of power consumption require often special design efforts.

### 1.2.3 Military, industrial and commercial applications

Temperature measurement can be identified in a variety of applications, e.g. system-operation temperature tracking or system-overheating detection, often applied for safety purposes. Sometimes temperature measurements are aimed for some process optimization, by creating a rigorous thermal control<sup>3</sup>.

### 1.2.4 Domestic appliances

Temperature sensors in domestic appliances do not need high accuracy and their operating range is normally restricted. However, production costs should be low.

### 1.2.5 Temperature sensors for autonomous systems

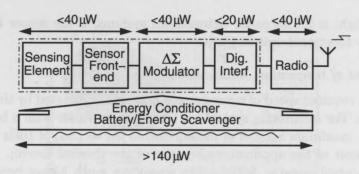

In autonomous systems, i.e. wireless systems, the power consumption should be so low that they are capable to operate for many years with energy supplied from a battery or with energy harvested from the environment. Such systems are becoming more and more important in industry, either in a stand-alone configuration or in sensor networks [5]. Low-power smart temperature sensors are rather suited as one of the fundamental building blocks of such systems<sup>4</sup> and can be operated together with energy scavengers and transmission-efficient radios<sup>5</sup>.

Figure 1.2 shows a typical autonomous system, where a smart sensor (delimited by a dashed square) can be identified. Examples of such autonomous systems are the Tire Pressure Monitoring Systems (TPMS) [6] as well sensor nodes used to implement sensor networks [5].

## **1.3** General characteristics of a sensor

The main characteristics of a temperature sensor<sup>6</sup>, which are often used as design specifications, are summarized below [3][7]:

• Accuracy

<sup>&</sup>lt;sup>3</sup>Such applications sometimes are referred as thermal management applications.

<sup>&</sup>lt;sup>4</sup>Such systems can have an entire processing unit inside, but in most of the cases, some type of sensor, e.g. temperature sensor, is present.

<sup>&</sup>lt;sup>5</sup>The study of radios and energy scavengers is out of scope of this work.

<sup>&</sup>lt;sup>6</sup>These characteristics are also valid for many other sensors.

### 1.3. General characteristics of a sensor

Figure 1.2: A generic autonomous system with an indication of the power consumption of the various blocks.

Accuracy over a given temperature range is certainly the most important characteristic of a temperature sensor. It is obtained after the elimination of systematic and stochastic errors and it is assured by the longterm stability of technological parameters and calibration/trimming procedures. State-of-the-art temperature sensors (reported academic prototypes) have an inaccuracy below  $\pm 0.1^{\circ}$ C from  $-55^{\circ}$ C to  $125^{\circ}$ C after trimming at room-temperature [8] and a batch calibrated (nontrimmed) inaccuracy below  $\pm 0.25^{\circ}$ C from  $-70^{\circ}$ C to  $130^{\circ}$ C [9].

#### • Temperature range

The temperature range is usually referred as the operating range within which the accuracy is guaranteed. Some well-known ranges are the commercial, industrial and military ranges, ranging from 0°C to 85°C, from -40°C to 100°C and from -55°C to 125°C, respectively. The clinical (medical) range is also frequently used and ranges from 35°C to 42°C.

### • Power consumption

In the past, the power consumption was not an important characteristic, probably being much more related to the sensor self-heating than to the power per conversion itself. The main concern was to limit the selfheating, so to be able to measure temperature, accurately. Nowadays, the power consumption may have the same status of accuracy, or, as in the case of some portable battery supplied applications or autonomous systems, more importance at all. Typical power consumption, as given in Fig. 1.2, of newer temperature sensors are below  $140\mu W$ , for accuracy levels as mentioned in the former item accuracy. This value, though, is too large for autonomous systems, if the sensor is not the only functional unit inside it.

• Speed of temperature measurement

The required speed of measurement is normally dictated by the application. For monitoring systems, a temperature sensor with a bandwidth (i.e. maximum number of measurements per second) of 10Hz is enough in most of the applications because of the thermal inertia. However, in control systems, for stability reasons, a much higher bandwidth is often required.

• Adaptability

Adaptability concerns the sensor's ability to adapt itself to the application requirements and constraints while in operation, e.g. reducing the power consumption per conversion (in case of lack of battery energy) by modifying (reducing) the data measurement rate and or measurement speed.

• Cost

The development of temperature sensors with low-cost CMOS technologies, which allows signal conditioning and digital signal processing on the same chip, and availability of a high accuracy without trimming (or at most after a single trimming step) are often two requirements for a low-cost temperature sensor.

• Long-term stability and Electro-Magnetic Susceptibility (EMS)

While the long-term stability characteristic predicts the sensor's accuracy behavior in the long run, Electro-Magnetic Susceptibility or interference robustness refers to the measurement reliability in the presence of any internal<sup>7</sup> or external interference.

### 1.4 State-of-the-art of smart temperature sensors

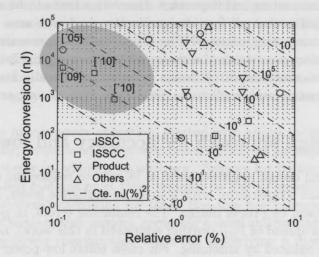

Figure 1.3 presents a temperature sensor performance survey with collected data from 1996 to 2010 [10], where the energy per conversion versus relative error is discussed. A Figure-of-Merit (FOM) given by the energy per conversion (nJ) versus relative error<sup>2</sup> (%)<sup>2</sup>, as defined and presented in [10], is

<sup>&</sup>lt;sup>7</sup>In mixed-signal sensor design, the digital circuitry is source of many spurious signal that may cause a potential interference over the sensitive analog parts of the sensor.

Figure 1.3: Temperature sensor performance (energy/conversion versus relative error) survey from 1996 to half of 2010. Obtained from [10]. Dashed lines indicate constant FOM (energy per conversion (nJ) versus relative error<sup>2</sup>  $(\%)^2$ ). The shadowed area shows the most accurate sensors up to 2010 (the year of publication of these sensors is indicated in square brackets).

used for comparison, what in fact agrees with the FOM presented in [11], as discussed in the Section 3.8.4 of Chapter 3.

Figure 1.3 shows that since 2005, the smart temperature sensor described in [8] (named ['05] in the picture) represents the state-of-the art in respect to accuracy, having it an inaccuracy below  $\pm 0.1^{\circ}$ C from  $-55^{\circ}$ C to  $125^{\circ}$ C (i.e. a relative error<sup>8</sup> of 0.11%). The work presented in [9] (named ['09] in the picture) and also in this thesis has a state-of-the-art accuracy too, since it has the same relative error of [8]. However, it dissipates less, thus meaning a higher performance, i.e. smaller FOM (3 times), as shown in the Figure 1.3.

Figure 1.3 shows that the energy per conversion can be reduced by allowing an increased error in the sensor output. The challenge is, for instance, to keep a certain accuracy level but under a lower power consumption and thus FOM. For instance, the most accurate sensors are in the top-left corner of the picture, (the shadowed area of Figure 1.3), where the energy per conversion is typically high. Very recent works [12][13] (both named ['10] in the picture) report a lower energy per conversion, but at expense of a higher relative error in regard to the state-of-the art [8][9].

<sup>&</sup>lt;sup>8</sup>The relative error is obtained dividing the maximum error in the temperature range by the temperature range, e.g.  $\frac{0.2}{180} = 0.11\%$ .

Another interesting and important observation that can be obtained from the survey [10] is that all four designs in the shadowed area are based on bandgap circuits, using either PNP or NPN transistors, revealing that up to now the bipolar transistor is the choice when designing highly-accurate lowpower temperature sensors. A design approach specifically for this purpose is not fully mature and needs to be developed. This is discussed as follows.

# 1.5 Design approach for accuracy and low-power

The successful design approach used in [8] was to reduce the effect of each of the different temperature error sources to negligible levels, i.e.  $\frac{1}{10}$  of the overall accuracy, by proper design. The remaining errors, in particular that related to the spread of  $V_{BE}$  (further addressed in this work), not avoided by design, were reduced by trimming. For cases where low-power consumption is required too (i.e. the sensor has some specified power constraint), this approach may result in a sensor whose implementation contains some degree of over-design (e.g. bias currents in excess given the accuracy specification).

In this sense, a modified design approach to work with both accuracy and power consumption requirements was proposed and used thoroughly this work. More specifically, in many parts of the system, relations between accuracy and power consumption were derived, and given accuracy requirements, power consumption values were found. In practice, this approach meant keeping most of the error sources bounded to a smaller (but not negligible) level than the required final accuracy (with the associated power saving), assuming that the inaccuracy would still be low, in order to be improved by trimming.

### 1.6 Motivation and objectives

Temperature sensors, as discussed, have many applications. In typical ones, where accuracies of about  $\pm 1^{\circ}$ C are needed, the design of integrated sensors is relatively easy. This is because of the current state of electronics today. However, if higher accuracy is required, the design of temperature sensors can be very challenging, requiring a number of circuit techniques to circumvent the electronics limitation and their non-idealities.

The growing trend in the field of thermal management, mainly started with the microprocessors market for portable computers, but nowadays not restricted to it, increased the demand for integrated temperature sensors and helped for their spread. Yet, pushed by the availability of highly-accurate discrete temperature sensors, like the Pt100 resistors, integrated temperature sensors needed to be accurate too in order to find their market. Nowadays, temperature sensors appear as fundamental circuits, providing means for a safe temperature-controlled operation of a variety of systems.

Smart (with a digital output) temperature sensors came next. Since most of the applications are often based on some digital processor, it is important to provide a highly-accurate and readily-available temperature in the digital format.

The trend in low-power operation, started with autonomous systems, on the other hand, introduced the power consumption as an important specification parameter in addition to accuracy. Sensors for battery-supplied or even battery-less systems must thus dissipate as low as possible, in order to preserve the system's operating life-time. But this has increased the design complexity of temperature sensors, requiring a deep understanding of important accuracy-power consumption trade-offs underlying a more systematic design.

### 1.7 Organization of the thesis

This thesis is organized in six main chapters as follows.

Chapter 2 - Temperature Sensing Fundamentals presents the design background on temperature sensors. The substrate PNP transistor characteristics and behavior are discussed in detail since this transistor is the fundamental building block of the sensor.

Chapter 3 - Front-end presents the design of the analog (sensor) frontend, showing how to generate accurately important voltages like the PTAT voltage  $\Delta V_{BE}$  and the CTAT voltage  $V_{BE}$ . PNP transistors bias currents and current ratios are deeply analyzed in face of accuracy requirements and power consumption constraints.

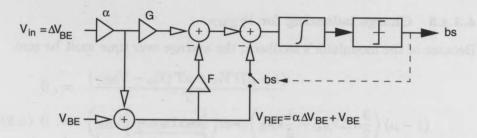

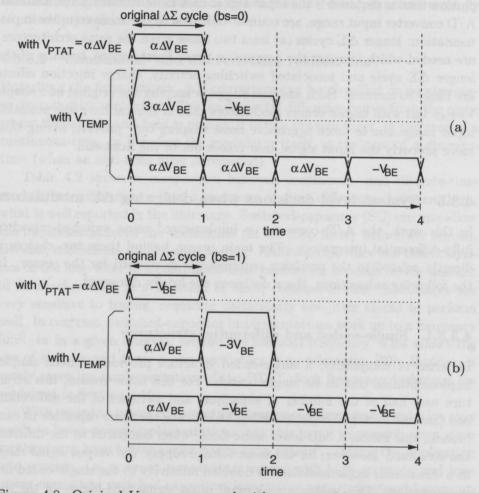

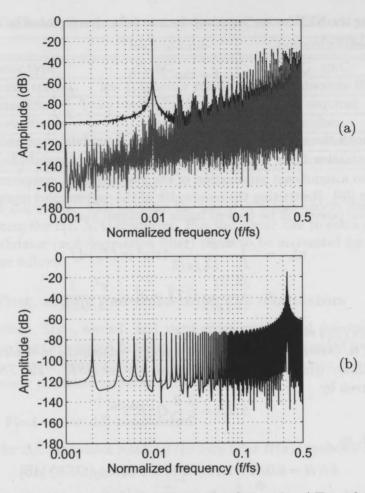

In Chapter 4 -  $\Delta\Sigma$  A/D Converters, the A/D converter of the smart temperature sensor, i.e. the sensor digital interface, is analyzed and designed. This converter processes the front-end analog outputs, i.e.  $\Delta V_{BE}$  and  $V_{BE}$ signals, generating a digital signal, whose value is a digital representation of the temperature. Important accuracy-power consumption tradeoffs are addressed focusing on a low-power though still accurate A/D converter.

In Chapter 5 - Realizations, measurement results of five temperature sensors are presented and analyzed. The last sensor, which is not coincidentally the sensor with best performance, having a batch-calibrated inaccuracy below  $\pm 0.25^{\circ}$ C ( $\pm 3\sigma$ ) from  $-70^{\circ}$  C to  $130^{\circ}$ C, with a total supply current of  $25\mu$ A, is discussed in more details.

The thesis ends with Chapter 6 - Conclusions, where the main findings

and original contributions of this work are given and once more commented.

The Appendix brings some additional text about selected subjects of this work.

# CHAPTER

# Temperature Sensing Fundamentals

# 2.1 Introduction

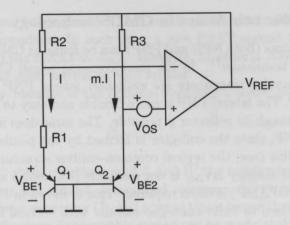

In this chapter most of the fundamental background to on-chip temperature measurement is provided. Frequently used application-related requirements are initially discussed. After, some of the most well-known temperature sensors are described and compared. Because of the particular requirements of this work, the bipolar transistor is chosen as the temperature sensor. Therefore, it is described in more detail, so as to provide enough knowledge about its properties and operating characteristics. This include its behavior as a function of temperature, and the main causes of fluctuation (variation due to spread) in its characteristics, which are particularly important when quantifying sources of measurement errors, topic of the next chapter. Finally, substrate PNP transistors (which are available as CMOS compatible transistors) and a typical band-gap circuit are presented.

# 2.2 Application-related requirements

The design of a sensor, like the design of many other systems, is based on a set of specifications the application requires, often named application-related requirements. In the case of a (temperature) sensor, the most important specification is often the accuracy the sensor has over a given operating (temperature) range. Power consumption is an important specification too and may become the most important one if the system is autonomous or battery supplied, when there is a severe power (and/or energy) constraint. Other

requirements include, bandwidth, type of interface, among others.

### Accuracy and resolution

Accuracy (or altenatively inaccuracy) sets the maximum error in a measuremnt over a given temperature range. In this particular work, an accuracy level of  $\pm 0.1^{\circ}$ C over the entire temperature range is targeted. Resolution, since it refers to the ability to recognize a small change in the input, e.g. temperature variation, is set to some extent smaller than the accuracy (refer to Section 4.1.1 of Chapter 4).

### **Temperature** range

The temperature range is referred as the operating range within which the accuracy is guaranteed. In this work, most of the design efforts were done thinking of the military range, i.e. from  $-55^{\circ}$ C to  $125^{\circ}$ C. In some cases a wider temperature range was also adopted, ranging from  $-70^{\circ}$ C to  $130^{\circ}$ C, as well some measurements done up to  $150^{\circ}$ C.

### Power consumption

The power consumption of a sensor is an important specification, specially when the sensor is thought for some portable battery supplied application or autonomous systems.

In this work, the total sensor power consumption budget was set to below  $75\mu$ W. This value was based on typical power consumption of current low-power temperature sensors. While certain autonomous applications require a much smaller power consumption, this value, given the specified accuracy accuracy level of  $\pm 0.1^{\circ}$ C over 180°C, presents relevant performance increase with respect to the prior art [8].

#### Speed of measurement and bandwidth

A bandwidth of 10Hz (i.e. 10 measurements per second) was set. This bandwidth is enough for most of the applications (whether some applications might require a higher bandwidth, other specifications are often relaxed, e.g. power consumption or temperature range). In particular cases, it is important to have a programmable conversion rate, e.g. given an energy constraint, a conversion rate smaller than the full bandwidth might be appropriate.

### Sensor interface

Smart sensors are required to provide the information they generate in a digital format. An A/D converter is thus often needed. In the case of temperature sensors, where the signal has a very small bandwidth (tens of Hz), oversampled A/D converters, e.g.  $\Delta\Sigma$ s, are preferred. Such data converters have the ability to self-adapt to the application needs, not to mention the relaxed specifications for the analog components [14].

### 2.2.1 Other characteristics

### **Immunity to interference**

Immunity to interference or interference robustness is often required from a sensor.  $\Delta\Sigma$  architectures have one important advantage against their Nyquist-rate counterparts: immunity against digital interference<sup>1</sup>. Because of the oversampling, the effect of any interference (within a  $\Delta\Sigma$  cycle) is attenuated in regard to the full conversion.

### Self-heating

Self-heating refers to the condition when the sensor has its internal temperature increased by its own operation. Since this condition cannot be avoided, self-heating has to be small so to limit temperature measurement errors. In this sense, the most effective way of handling this condition is then by limiting the sensor power consumption to below, for instance, a few hundreds of  $\mu$ W to avoid introducing errors greater than 0.05°C in typical IC ceramic packages [15]. Operating the sensor periodically (i.e. duty-cycled operation as follows) might be another solution to reduce self-heating. However, this will affect the sensor availability.

### **Duty-cycled** operation

Because most of the sensor signals have a very small bandwidth, the sensor can operate duty-cycled [16]. After a measurement, the system is switchedoff. This non-continuous or duty-cycled operation is important mainly in autonomous sensors when the available energy is limited. The main consequences of a duty-cycled operation are:

• energy saving that prevents battery discharge and allows longer operation time;

<sup>&</sup>lt;sup>1</sup>In fact, a property of integrating architectures

- reduction of self-heating effects (as mentioned) and;

- improved compatibility in multiplexed systems.

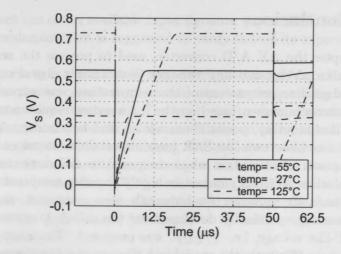

Another consequence of a duty-cycled operation concerns the transient time between the switched-off mode (or sleeping mode) and the operating mode, which is well known as wake-up time. While in this particular work, this time (tens of  $\mu$ s) can be neglected given the low frequencies involved in temperature measurements, it may be of great concern in other cases due to the amount of energy consumed during the wake-up time.

### 2.3 Temperature sensors

In theory, any element with temperature-dependent characteristics can be used to sense temperature. However, such characteristics are not always well-behaved, e.g. linear with temperature and only dependent on temperature, exhibiting no cross-sensitivity. This severely restricts the applicability of many elements as temperature sensors. Nonetheless, a wide range of temperature sensors is still available. The most important ones are [2]:

- transistors (mostly bipolar transistors);

- thermocouples;

- platinum (Pt) resistors;

- thermistors .

A summary with the main characteristics of each one is presented in Table 2.1. Based on these characteristics, given an application and requirements, one can define the most suitable temperature sensor.

Regardless of the type, these sensors are available as individual components, i.e. in discrete form, or built together with integrated circuits, i.e. in integrated form. All types listed in Table 2.1 are usually available in the discrete form, while some only in the integrated form. The reason is that, in general, standard CMOS integration technologies are not fully compatible with materials/procedures required to build certain types of temperature sensors, requiring additional steps, which often increase the production costs.

Discrete platinum resistors (e.g. Pt100) are very stable and because of that were listed as the interpolating temperature standard from 13.9K to  $962^{\circ}$ C according to the International Temperature Scale [17]<sup>2</sup>. Because this

<sup>&</sup>lt;sup>2</sup>More than one Pt resistor is required to provide reasonable accuracy over this wide temperature range.

| Characteristics                                   | Transistors                | Thermo-<br>couples         | Platinum<br>resistors                 | Thermistors               |

|---------------------------------------------------|----------------------------|----------------------------|---------------------------------------|---------------------------|

| Temperature<br>range (°C)                         | medium<br>[-80, 180]       | very large<br>[-270, 3500] | large<br>[-260, 1000]                 | medium<br>[-80, 180]      |

| Absolute<br>accuracy                              | medium                     | no                         | high                                  | high                      |

| Accuracy for<br>small tempera-<br>ture variations | medium                     | high                       | medium                                | medium                    |

| Integrability in<br>standard CMOS                 | yes                        | yes                        | no                                    | no                        |

| Sensitivity                                       | ${ m high} \ (2{ m mV/K})$ | low<br>(1mV/K)             | $\frac{\text{low}}{(0.4\%/\text{K})}$ | $_{ m (5\%/K)}^{ m high}$ |

| Linearity                                         | good                       | good                       | good                                  | strongly<br>non-linear    |

Table 2.1: Characteristics of the main temperature sensing elements. Obtained from [2].

range includes the particular range of interest of this work, i.e.  $-55^{\circ}$ C to  $125^{\circ}$ C, namely the military range, calibrated Pt100 resistors were used to calibrate the integrated sensors described in this thesis.

Thermocouples offer better performance than Pt resistors at higher temperatures, but because of their low cost and high reliability, they also find use in other temperature ranges. The main issue of a thermocouple is that it generates a voltage that is proportional to the difference between the hot and cold junction of the element, providing only a relative temperature measurement. A second absolute temperature sensor is usually required to measure the temperature of the cold junction.

Thermistors are very low cost and very compact in size. They can be also very sensitive, exhibiting thus excellent resolution, but over temperature they present a strong non-linearity behavior, which imposes extra complexity to process the signal.

Transistors are as sensitive as thermistors and have the advantage that the base-emitter voltage is almost linearly related to the temperature.

### 2.3.1 Integrated temperature sensors

Integrated sensors are increasingly becoming preferred since merging the sensor with the processing circuit in the so called smart sensor allows compact and low cost sensors, not to mention an output in a digital format, ready for use.

Thermocouples and transistors are the two best examples of temperature sensors that can be integrated. Although it is possible to make Pt resistors on chips, this is not a standard procedure up to now in CMOS technology, meaning increased fabrication costs. Not to mention that thin-film resistors are not as good as their discrete counterparts [2].

Thermocouples are intrinsically offset-free and certainly the best option when the temperature is higher than transistors can stand (250°C). But the fact that they only measure relative temperature is a serious disadvantage.

Temperature sensors based on thermal diffusivity, named ETFs (Electrothermal Filter) [18][19] can also be successfully integrated. But they have a large power dissipation, due to an internal heating source, and this severely impairs the design of low power sensors. Moreover, there is need for a reference frequency, which is in general not available.

Bipolar transistors (PNPs and NPNs) are thus the most natural option for integration and the most suited temperature sensor if absolute temperature measurement is required and low-power consumption is needed. A reference voltage  $V_{REF}$  is required in this case, but that can be successfully derived from the band-gap voltage  $V_{bg} \approx 1.2V$  of the Silicon at 0K. Adding to this, they are also stable and sensitive, with a reasonably linear behavior.

Although MOS transistors can be used to implement temperature sensors as well as bipolar transistors [20], mutual compensation of mobility and threshold voltage temperature effects is required [21], which adds to design complexity. Without such compensations, the MOS transistor is typically much less accurate.

### 2.3.2 Platinum (Pt) resistors

Platinum resistors (more specifically Pt100 resistors) were used throughout this work as temperature references. They are briefly mentioned in this section for the sake of completeness. A detailed discussion of the properties of thermocouples and thermistors is beyond the scope of this thesis.

The relation between resistance and temperature in Pt resistors is generally expressed as (DIN-IEC 751 Standard ) [2]

$$R(T) = R_{Pt}(T_0)(1 + a_1T + a_2T^2 + a_3T^3 + a_4T^4)$$

where  $R_{Pt}(T_0)$  is the nominal resistance at temperature  $T = T_0 = 0^{\circ}$ C and  $a_i$  the coefficients obtained after the calibration<sup>3</sup>.

<sup>3</sup>The calibration is done at authorized calibration institutes. Different coefficients might be required depending on the temperature range.

Alternatively, the temperature can be expressed as

$$T = (b_0 + b_1 R + b_2 R^2 + b_3 R^3 + b_4 R^4 + \dots + b_i R^i)$$

where R is the measured resistance and  $b_i$  are the inverse coefficients.

## 2.4 Bipolar transistors

The bipolar transistor is the most widely used building block of integrated smart temperature sensors. This is because it provides information, not about the relative, but about the absolute temperature. However, generating, reading and processing this information is usually not simple and often care must be taken. That is why it is important to know the main characteristics of such transistors and to understand their operation. With such knowledge, a proper transistor model can be formulated and used throughout the sensor design. The characteristics of bipolar transistors will be discussed extensively in the following subsections. Luckily, much of the work was already done [22][23][24][15].

### **2.4.1** The ideal $I_D - V_D$ diode characteristic

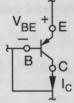

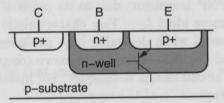

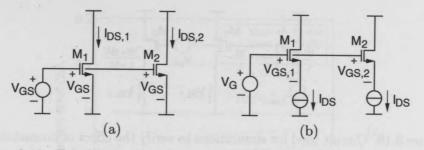

Most temperature sensors make use of the bipolar transistor in a configuration that is well-known as a diode-connected (Fig. 2.1). In this case, the bipolar transistor, a three terminal device, ends up having effectively only two ones, and having an operating behavior very similar to a diode. Because of the configuration, the original PNP junctions of a bipolar transistor behave somewhat like a single PN junction, which is exactly a diode. Before briefly introducing its characteristic in this section, it is important to mention that the discussion in this work, as well in many others, is formulated for a PNP transistor rather than for a NPN, since the best performance bipolar transistors available in most CMOS processes are the vertical (or substrate) PNP transistors (refer to Subsection 2.4.9 for more details). A last remark concerns the sign convention. In order to keep the same convention of former works in this area (see for instance [22]),  $V_{BE}$  and  $\Delta V_{BE}$  nomenclatures are used instead of  $V_{EB}$  and  $\Delta V_{EB}^4$ .

The well-known ideal diode characteristic is given by

$$I_D = I_S \left( \exp\left(\frac{qV_D}{kT}\right) - 1 \right) \tag{2.1}$$

<sup>&</sup>lt;sup>4</sup>For sake of clarity, for a PNP transistor, the emitter to base voltage  $V_{EB}$  (referenced as  $V_{BE}$ ) through out this work is positive, so to set the transistor in its forward-active region, unless otherwise specified.

Figure 2.1: Bipolar transistor (PNP) in a diode-connected configuration.

where  $V_D$  is an external voltage applied to the device (to its p-n junction) while  $I_S$  is the saturation current. When the diode is in forward-bias (and  $V_D \gg \frac{kT}{q}$ ), the term -1 in (2.1) can be neglected:

$$I_D \approx I_S \left( \exp\left(\frac{qV_D}{kT}\right) \right).$$

(2.2)

In a similar way, a voltage drop  $V_D$  that develops across the diode when a bias current  $I_D$  is applied to it is

$$V_D = \frac{kT}{q} \ln\left(\frac{I_D}{I_S}\right). \tag{2.3}$$

Remarkably, if  $I_D$  and  $I_S$  are known, by reading the voltage  $V_D$  is possible to determine the absolute temperature T. Unfortunately,  $I_S$  is strongly process (and temperature, i.e  $I_S(T)$ ) dependent and cannot be determined.

However, if two bias currents  $I_{D1}$  and  $I_{D2} = mI_1$  are applied to two diodes (assumed matched, i.e.  $I_{S1} = I_{S2}$ ), the difference in voltage drop is

$$V_{D2} - V_{D1} = \frac{kT}{q} \ln\left(\frac{I_{D2}}{I_{S1}}\right) - \frac{kT}{q} \ln\left(\frac{I_{D1}}{I_{S2}}\right) = \frac{kT}{q} \ln(m).$$

(2.4)

In this case, it is not a voltage drop  $V_D$  but the difference of two voltage drops that is proportional to absolute temperature. The advantage is that the difference is not dependent on the saturation current or any other process-related parameter. This remarkable result can be used to measure temperature.

However, non-ideal effects not modeled in (2.1) make diodes not really appropriate for accurate temperature measuring [22]. Because (2.1) does not take into account the current due to generation and recombination phenomena in the depletion region of a diode, it is only approximate. Since the latter current has a different temperature dependency than that given in (2.1), the diode current cannot be expressed in a single exponential. In practice, the following approximation

$$I_D \approx I_S \left( \exp\left(\frac{qV_D}{nkT}\right) - 1 \right) \tag{2.5}$$

is used to model the diode current, initially given by (2.1), where n is the so-called non-ideality factor.

The factor n varies from 1, for large forward-bias  $V_D$ , when diffusion dominates, to 2, for low forward-bias, when recombination dominates. With this approximation, the PTAT voltage given by (2.4) ends up depending on n, which is, like  $I_S$ , process dependent. This is hardly acceptable in accurate temperature sensors<sup>5</sup>.

### 2.4.2 The ideal $I_C - V_{BE}$ bipolar transistor characteristic

In a bipolar transistor, the relation between the collector current  $I_C$  and the base to the emitter voltage  $V_{BE}$  has the same form as (2.1). But because of the base terminal, the currents that are generated in the base-emitter junction of a bipolar transistor due to e.g. generation/recombination and reverse injection, as in a diode, are not part of the collector current [23], since the resulting non-ideal components of the emitter current are mainly provided via the base of the transistor [23][22]. This makes the relation  $I_C - V_{BE}$  of a bipolar transistor much more ideal than the  $I_D - V_D$  characteristic of a diode, i.e. n is closer to 1. That is why, despite some equivalence, a bipolar transistor has a superior performance as a temperature sensor when compared to the more simple diode.

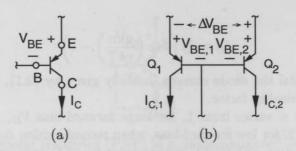

Consider a PNP transistor, like shown in Fig. 2.2(a), in its forward-active region, i.e. with a forward-biased base-emitter junction and a reverse-biased base-collector junction. The collector current  $I_C$  can be written as [25]

$$I_C = I_S \left( \exp\left(\frac{qV_{BE}}{kT}\right) - 1 \right) \tag{2.6}$$

where the saturation current  $I_S$  is given by

$$I_S = \frac{qA_{BE}n_i^2\bar{D}_p}{Q_B} = \frac{kTA_{BE}n_i^2\bar{\mu}_p}{Q_B}$$

(2.7)

where  $A_{BE}$  is the base-emitter junction area,  $n_i$  is intrinsic carrier concentration in the base,  $\bar{D}_p$  is the effective hole diffusion constant,  $\bar{\mu}_p$  in the average hole mobility in the base and  $Q_B$  is the total base doping per unit area<sup>6</sup>.

<sup>&</sup>lt;sup>5</sup>Whether n might exhibit low process variation in a given technology and have its value well characterized, it is preferable to avoid any process dependency in the bias current.

$<sup>{}^{6}</sup>Q_{B}$  is well-known as the Gummel number.

Figure 2.2: (a) Schematic of a PNP transistor and (b) circuit configuration to have a  $\Delta V_{BE}$  voltage.

The Einstein relation  $\mu = \frac{q}{kT} \cdot D_n$  was used to write  $I_S$  in terms of  $n_i^2$  and  $\mu_p$ . Again, if  $V_{BE} \gg \frac{kT}{q}$ , i.e.  $I_C \gg I_S$ , then (2.6) can be simplified to

$$I_C = I_S \left( \exp\left(\frac{qV_{BE}}{kT}\right) \right) \tag{2.8}$$

which is called the ideal  $I_C - V_{BE}$  characteristic. Solving this equation for  $V_{BE}$  results in

$$V_{BE} = \frac{kT}{q} \ln\left(\frac{I_C}{I_S}\right) \tag{2.9}$$

which agrees with the diode equation given in (2.3).

The ideal logarithmic characteristic described in (2.9) shows that a PTAT voltage can be built in the same way as with diodes (and thus used to measure temperature by comparing it with a reference or temperature-independent voltage). Two equal transistors  $Q_1$  and  $Q_2$ , as shown in Fig. 2.2(b), having collector currents  $I_{C,1}$  and  $I_{C,2} = mI_{C1}$ , present a base-emitter voltage difference  $\Delta V_{BE}$  given by

$$\Delta V_{BE} = V_{BE,2} - V_{BE,1} = \frac{kT}{q} \ln(m).$$

(2.10)

This result is remarkable since  $\Delta V_{BE}$  is not dependent of  $I_S$  like  $V_{BE}$  is. This makes  $\Delta V_{BE}$  not dependent on process variation. As mentioned already by [26][27], the  $\Delta V_{BE}$  voltage is then accurate, provided mismatch errors are eliminated.

#### Error due to mismatch in the saturation current $I_S$

If the saturation currents  $I_{S,1}$  and  $I_{S,2}$  of two identically designed PNP transistors are different due to a mismatch between the transistors, then the

20

#### 2.4. Bipolar transistors

voltage  $\Delta V_{BE}$  given in (2.10) is now given (assuming for now no mismatch in the current sources):

$$\Delta V_{BE}(T) = \frac{kT}{q} \ln \left( \frac{\frac{I_{bias,2}}{I_{S,2}}}{\frac{I_{bias,1}}{I_{S,1}}} \right)$$

$$= \frac{kT}{q} \ln \left( m \frac{I_{S,1}}{I_{S,2}} \right).$$

(2.11)

Writing  $I_{S,2} = I_{S,1} \pm \Delta I_S$  results in

$$\Delta V_{BE}(T) \approx \frac{kT}{q} \ln(m) \mp \frac{kT}{q} \ln\left(\frac{\Delta I_S}{I_{S,1}}\right) \qquad (\Delta I_S \ll I_{S,1}). \tag{2.12}$$

The mismatch modifies the ideal  $\Delta V_{BE}$  by the second term in (2.12). The error is proportional to the temperature (PTAT) for a temperature independent  $\frac{\Delta I_S}{I_{S,1}}$ .

#### 2.4.3 The effect of $I_S$ in the ideal $I_C - V_{BE}$ characteristic

The  $\Delta V_{BE}$  voltage is accurate provided mismatch errors are eliminated. Although acceptable for relatively high bias currents, errors are no longer negligible for low bias currents. When the bias current gets small,  $I_S$  cannot be neglected, i.e. the term -1 in (2.6), and the difference  $\Delta V_{BE}$ , initially given in (2.10) becomes

$$\Delta V_{BE} = V_{BE2} - V_{BE1} = \frac{kT}{q} \ln \left( \frac{mI_{C,1} + I_S}{I_{C,1} + I_S} \right)$$

(2.13)

in the case of two transistors with equal saturation currents, i.e.  $I_{S,1} = I_{S,2} = I_S$ .

This result shows unfortunately a  $\Delta V_{BE}$  dependent on  $I_S$  (and now susceptible to process variations), no matter how matched the PNP transistors are nor how accurate the current ratio m is. In fact,  $I_S$  degrades the current ratio m which in turn degrades the accuracy that can be achieved from  $\Delta V_{BE}$  and from the sensor. In order to prevent or limit the effect of  $I_S$ , so an accurate PTAT voltage can be obtained, the collector currents  $I_{C,1}$  and  $I_{C,2}$  have to be significantly larger than  $I_S$  (how large will depend on the accuracy requirements for  $\Delta V_{BE}$ ). Since power reduction is normally achieved by reducing the PNP bias currents, accuracy requirements for  $\Delta V_{BE}$  can severely

limit power-saving attempts<sup>7</sup>. Requirements are much worse at high temperature, since  $I_S$ , as well-known, increases exponentially with temperature (see Section 2.4.5).

#### 2.4.4 The effect of $\beta$ in the ideal $I_C - V_{BE}$ characteristic

The collector terminal of a vertical PNP transistor (available in most CMOS processes) is formed by the p-substrate. Since the substrate is grounded (see subsection 2.4.9), there is no opportunity to bias the bipolar transistor via its collector. In this case, it is the emitter current of a bipolar transistor that is set by a current source, instead of the collector current. This explains why in a diode-connected configuration (with the base also grounded, i.e.  $V_{BC} = 0$ ), the base current has also to be taken into account when determining the base-emitter voltage. Since the emitter current results from the sum of the base and collector currents, the collector current can be written as

$$I_C = I_E - I_B = \frac{\beta}{1+\beta} I_E \tag{2.14}$$

where  $\beta$  is the common-emitter forward current gain, well known and defined as the ratio  $\beta = I_C/I_B$ . This results in a voltage  $V_{BE}$  given by

$$V_{BE} = \frac{kT}{q} \ln\left(\frac{\beta}{1+\beta} \frac{I_E}{I_S}\right) \tag{2.15}$$

The result in (2.15) shows that a bipolar transistor biased through its emitter, even if by an ideal current source, has a  $V_{BE}$  voltage that is dependent on  $\beta$ , i.e. susceptible to process spread. This is particularly important when  $\beta$ is small ( $\beta < 25$ ), which is the case of substrate PNPs in standard CMOS technologies [28][29]. Moreover,  $\beta$  has to be current-independent, so that an accurate emitter-current ratio will result in the same collector-current ratio. These results show that some technique for  $\beta$  compensation will be necessary for such high accuracy applications, since the  $\beta$ -dependency in the base-emitter voltage is a potential cause for low non-trimmed and posttrimmed accuracies. No need to mention that attention must be paid to the power consumption of the circuit used to implement the compensation.

#### 2.4.5 Temperature Characteristic of $V_{BE}$

The temperature characteristic of the base-emitter voltage  $V_{BE}$  given in (2.9) is determined considering the temperature dependence of the saturation current  $I_S$  and the collector current  $I_C$ . Additionally, because  $I_C = \frac{\beta}{1+\beta} \cdot I_E$ ,

<sup>&</sup>lt;sup>7</sup>How severe this limitation is depends on the total current consumption of the sensor with regard to the total bias current of PNPs needed to generate  $\Delta V_{BE}$ .

the temperature dependency of  $\beta$  has also to be taken into account. The analysis of  $I_S$  is carried out by analyzing its components:  $n_i$  and  $\mu_p$ .

The intrinsic minority-carrier concentration  $n_i$  is given by [30]

$$n_i^2 \propto T^3 \exp\left(\frac{-qV_g}{kT}\right)$$

(2.16)

where  $V_g$  is the silicon band-gap approximated by

$$V_g \approx V_{g0} - \alpha T \tag{2.17}$$

where  $V_{g0}$  is the extrapolated band-gap voltage at 0K and  $\alpha$  the linear coefficient of the approximation.

The average hole mobility in the base  $\bar{\mu_p}$  is given by

$$\bar{\mu_p} \propto T^{-n}.\tag{2.18}$$

The substitution of (2.16) and (2.18) in the saturation current given in (2.7), results in<sup>8</sup>

$$I_S(T) = I_{S0}T^{\eta} \exp\left(\frac{-qV_{g0}}{kT}\right)$$

(2.19)

where  $I_{S0}$  and  $\eta = 4 - n$  are constants. Equation (2.19) shows how strongly  $I_S$  depends on temperature, which before hand can lead the reader to think about the effects of such dependency in the sensor performance: while the voltage  $\Delta V_{BE}$  is ideally not sensitive to  $I_S$ ,  $V_{BE}$ , which is used to generate the required reference voltage  $V_{REF}$  needed for temperature measurement (as further explained in Chapter 3), is.

The substitution of (2.19) in (2.8) results in the following collector current expression:

$$I_C = I_{S0} T^{\eta} \exp\left(\frac{q}{kT} (V_{BE} - V_{g0})\right)$$

(2.20)

or, if solved for  $V_{BE}$ ,

$$V_{BE}(T) = V_{g0} + \frac{kT}{q} \ln\left(\frac{I_C}{I_{S0}T^{\eta}}\right).$$

(2.21)

now written explicitly in terms of temperature. i.e.  $V_{BE}(T)$ . Interesting to mention that because  $\frac{I_C}{I_{S0}T^{\eta}} < 1$ , the value of ln is negative, which gives the  $V_{BE}(T)$  a negative temperature coefficient [24], despite of what can be initially misunderstood from (2.9). In this sense, the signal  $V_{BE}$  is complementary to absolute temperature (CTAT).

$<sup>{}^{8}</sup>Q_{B}$  is assumed approximately constant with temperature [23].

**Temperature Sensing Fundamentals**

In practice, the collector current is not constant over temperature but proportional to a power of T. This temperature dependence is introduced by writing  $I_C$  as

$$I_C(T) = I_{C0}T^m, (2.22)$$

where  $I_{C0}$  is a constant and m the temperature exponent, e.g. a constant  $I_C = I_{C0}$  is represented by m = 0 and a PTAT current  $I_C = I_{C0}T$  represented by m = 1. By replacing (2.22) in (2.21) the following results

$$V_{BE}(T) = V_{g0} + \frac{kT}{q} \ln\left(\frac{I_{C0}}{I_{S0}T^{\eta-m}}\right)$$

(2.23)

or, if written as a function of  $V_{BE}$  at a given temperature, e.g.  $V_{BE}(T_r)$  [23] (see [24] for a detailed derivation),

$$V_{BE}(T) = V_{g0} \left( 1 - \frac{T}{T_r} \right) + \frac{T}{T_r} V_{BE}(T_r) - (\eta - m) \frac{kT}{q} \ln\left(\frac{T}{T_r}\right).$$

(2.24)

As earlier found by [23], the expression for  $V_{BE}$  as given above, when using empirical values for  $V_{g0}$  and  $\eta$  according to the basis of physics, is not accurate. This is due to poor approximations used in (2.17) and (2.18). Curiously though, when using  $V_{g0}$  and  $\eta$  as fitting parameters (derived form measured  $V_{BE}$  data), accuracy as good as 0.03K can be found.

For convenience, but also to have a better comprehension of  $V_{BE}$ , often (2.24) is rewritten as the sum of a constant term  $V_{BE0}$  (temperature independent), a linear term aT (proportional to absolute temperature) and a non-linear term nl(T) (the sum of all higher-order terms) [23]:

$$V_{BE}(T) = V_{BE0} + aT + nl(T)$$

(2.25)

where  $V_{BE0}$  is the extrapolation of the tangent at T = 0K given by

$$V_{BE0} = V_{q0} - nl(0), (2.26)$$

a is the slope of the tangent given by

$$a = \frac{V_{BE}(T_r) - V_{BE0}}{T_r - 0K}$$

(2.27)

(in such way that the linear term represents a line tangent to the  $V_{BE}(T)$  curve at  $T = T_r$ ) and nl(T) the  $V_{BE}$  curvature given by

$$nl(T) = (\eta - m)\frac{K}{q} \left[ T - T_r + T \ln\left(\frac{T_r}{T}\right) \right]$$

(2.28)

which is, at T = 0K, equal to

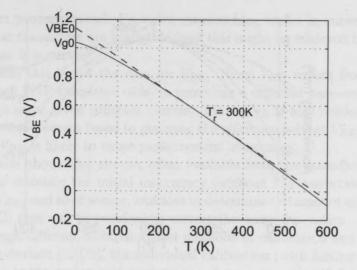

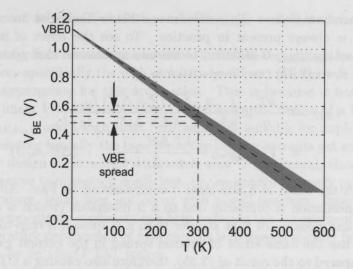

Figure 2.3: The base-emitter voltage  $V_{BE}$  as a function of temperature T. The dashed line shows a linear approximation for  $V_{BE}$  (tangent to the  $V_{BE}$  curve at T = Tr.

$$nl(0) = (\eta - m)\frac{K}{q}[-T_r].$$

(2.29)

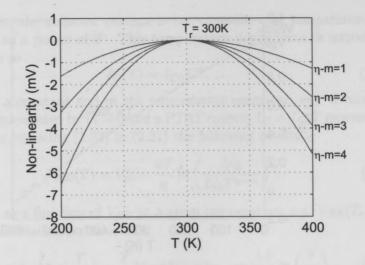

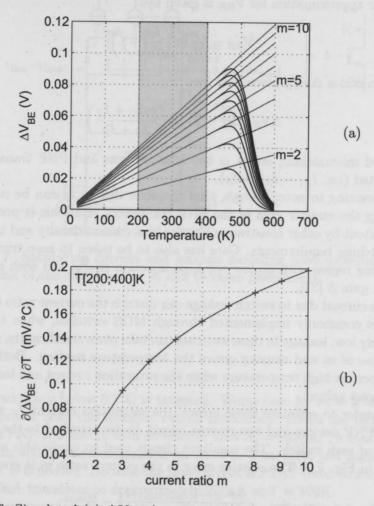

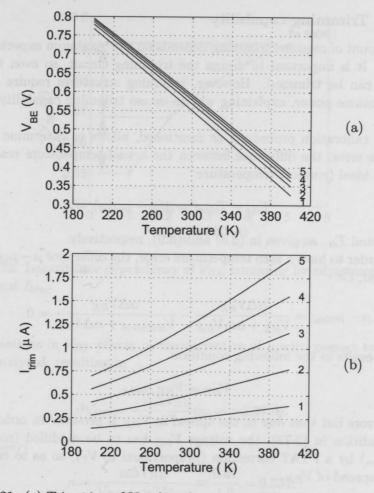

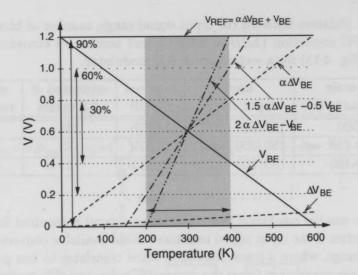

Figure 2.3 shows the base-emitter voltage  $V_{BE}(T)$  as given in (2.25) versus T from 0 to 600K for  $V_{BE0} = 1.15$ V and  $a = -2mV/^{\circ}C$  ( $V_{BE}(T_r = 300K) = 0.54$ V) while the non-linearity nl(T) is plotted in Fig. 2.4 versus T from 200K to 400K for values of  $\eta - m$  from 1 to 4. The curvature of  $V_{BE}$  decreases when the bias current increases faster with temperature, sort of canceling the effect of the saturation current. For instance, the non linearity obtained for  $\eta - m = 3$  (case of PTAT bias current  $I_C$ ) is smaller than for  $\eta - m = 4$  (constant bias current), which indicates that a bias current dependent on temperature can reduce the curvature of  $V_{BE}$ . The curvature amounts to some mV in the range of 200K to 400K for all cases.

#### 2.4.5.1 Temperature Characteristic of Current Gain $\beta$

Because the vertical PNP transistor is biased via its emitter, its collector current is a fraction  $\frac{\beta}{1+\beta}$  of the applied emitter current as given in (2.14), which in turn results in a  $\beta$ -dependent voltage  $V_{BE}$  (see equation(2.15)). Because often  $\beta$  happens to be temperature dependent [25], this has to be accounted when determining the temperature characteristic of  $V_{BE}$ , initially found in (2.15).

Figure 2.4: (b) The non-linearity of  $V_{BE}(T)$  as a function of temperature, for values of  $\eta - m$  from 1 to 4.

In practice, the following expression is used to model  $\beta$  [31]:

$$\beta(T) = \beta_0 \left(\frac{T}{T_r}\right)^{X_{TB}} \tag{2.30}$$

where the nominal current gain  $\beta_0$  and the temperature exponent  $X_{TB}$  are found by fitting the equation to the measured data. The substitution of equation (2.30) in equation (2.15) results in a  $V_{BE}$  with an additional term

$$V_{BE} = V_{BE}(T)|_{\beta = constant} + \frac{kT}{q} \ln\left(\frac{(1+\beta_0)\left(\frac{T}{T_r}\right)^{X_{TB}}}{1+\beta_0\left(\frac{T}{T_r}\right)^{X_{TB}}}\right).$$

(2.31)

This additional term was studied in [22], where simulation results were presented. The adding term is only important for small values of  $\beta$  and large value of  $X_{TB}$ . Unfortunately, this is exactly the case for vertical PNP transistors. Nominal values for  $\beta \approx 22$  and  $X_{TB} \approx 4$  suggests that compensation for finite current gain is necessary when designing sensors for high accuracy. Not to mention the fact that  $\beta$  suffers from process spread, which causes spread to  $V_{BE}$ .

#### **2.4.6** Process spread of $V_{BE}$

Probably the most important characteristic of  $\Delta V_{BE}$  (the PTAT voltage as presented in (2.10) is the fact that for well chosen bias currents it does not

26

#### 2.4. Bipolar transistors

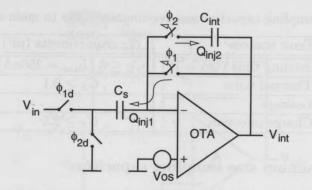

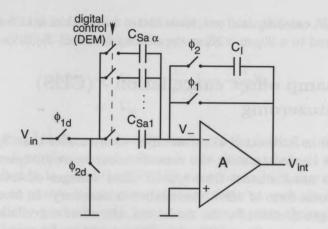

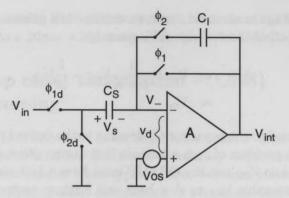

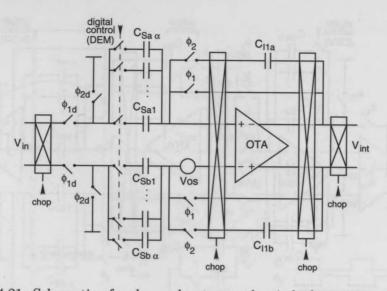

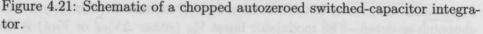

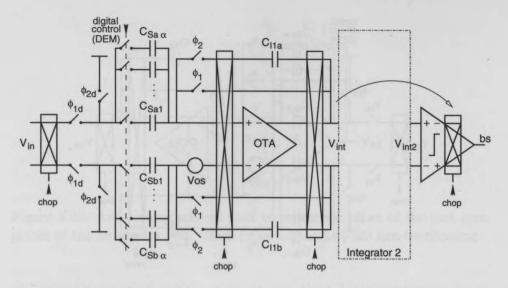

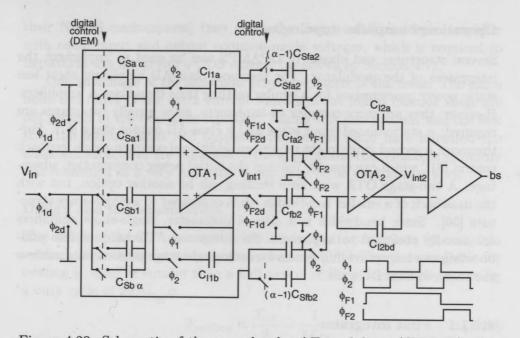

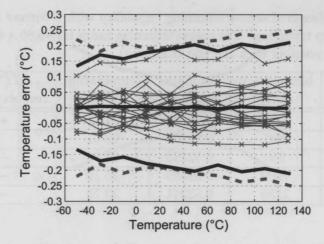

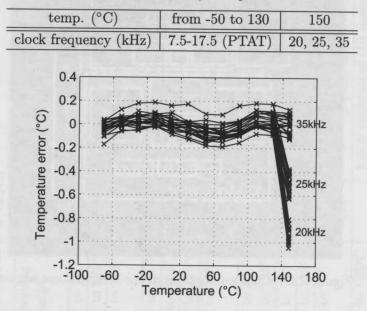

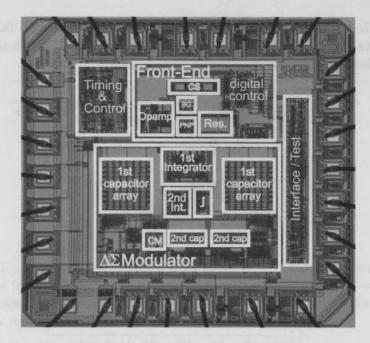

suffer from process spread. Provided mismatching errors in current sources and bipolar transistors are negligible (and this might be achieved by design), this voltage is accurate<sup>9</sup>.