# An Ultra Low Power Fully Integrated Sensor Interface IC for Pacemaker

Reported by:Salim Al-Ahdab

August 24, 2009

Supervisors:

Dr.ir. Wouter Serdijn

Dr.Reza Lotfi

The Faculty of Electrical Engineering,

Mathematics and Computer Science

in Partial Fulfillment of the Requirements

for the Degree of

MASTER OF SCIENCE

in Electrical Engineering

Delft University of Technology

Copyright  $\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model{Copyright}}\@ifnextchar[{\@model$

# Committee member:

Prof.dr. John R. Long

Dr.ir. Wouter A. Serdijn

Dr.Georgi N. Gaydadjiev

Dr.Reza Lotfi

#### Acknowledgment

First, I would like to thank Allah who gives me the strength and patience to finish my Master studies. I would not be able to reach this place only by Allah's will. I greatly appreciate the help and support my parents, Shahama and Khaldoun, offered me. They have been there for me in good times and difficult times. I would not be able to thank them enough for their efforts. I owe my success after Allah to my father who is truly my first teacher. Also, to my mother who taught me how to write my first word in this life.

"The mediocre teacher tells. The good teacher explains. The superior teacher demonstrates. The great teacher inspires" William Ward. My supervisors Dr.ir.Wouter A. Serdijn and Dr.Reza lotfi have inspired me throughout my research. They are not only my supervisor but they are also my mentors. I would like to thank Mr. Rabbani and Ms. Yonet from Lutfia Rabbani Foundation for their care and financial support I would like to thank every person (PhD students and my fellow Master students in The Biomedical Group headed by Dr.ir.Wouter A. Serdijn) who helped me finish my Master thesis. Also, I would like to thank my close friends Moamen, Khaled and Yousef for their support while staying in The Netherlands.

#### Abstract

When the heart does not function properly, an artificial pacemaker is needed to correct the heart beat. However, more functionality at limited budget requires less power per function. Therefore, the power consumption of the pacemaker has to be reduced. The analog to digital converter in the pacemaker consumes the largest amount of power in the front-end, called the sense amplifier. Hence, an ultra low power ADC is . In this work, the IECG signal is filtered by band pass filter 50mHz-100Hz. Then, the signal output of the filter is converted to current by transconductance cell(Gm). The output of the Gm-cell is digitized by a Current Successive Approximation ADC. Circuit Simulation predict the overall system consumes the lowest power,416nW reported when compared with the state of the art.

# Contents

| 1 | Intr | oducti  | ion                                                      | 13 |

|---|------|---------|----------------------------------------------------------|----|

|   | 1.1  | Backg   | round                                                    | 13 |

|   |      | 1.1.1   | Pacemaker & ECG                                          | 14 |

|   |      | 1.1.2   | Weak Inversion CMOS                                      | 16 |

|   | 1.2  | Motiva  | ations                                                   | 20 |

|   | 1.3  | Thesis  | s Outlines                                               | 20 |

| 2 | Sys  | tem A   | rchitecture & Design                                     | 22 |

|   | 2.1  | literat | ure Review                                               | 22 |

|   |      | 2.1.1   | Very low Frequency pass Filter                           | 22 |

|   |      | 2.1.2   | Data Converters                                          | 24 |

|   | 2.2  | System  | n Design and Architecture                                | 27 |

|   |      | 2.2.1   | Filter Design Methodology                                | 27 |

|   |      | 2.2.2   | ADC Design Methodology                                   | 30 |

|   |      | 2.2.3   | System Architecture                                      | 31 |

|   | 2.3  | ADC-    | Matlab Simulation                                        | 33 |

|   |      | 2.3.1   | Linear Current Steering DAC                              | 36 |

|   |      | 2.3.2   | Non linear Tangent Hyperbolic Current Steering DAC $$    | 39 |

|   |      | 2.3.3   | Measuring SQNR with Mismatch                             | 41 |

|   | 2.4  | Concl   | usion                                                    | 46 |

| 3 | Low  | Pass    | Filter Circuit Design (First Stage)                      | 47 |

|   | 3.1  | Very I  | Low Frequency filter & Sub-threshold Two Stage Miller Op |    |

|   |      | Amp     |                                                          | 47 |

|   |      | 3.1.1   | Bandpass Filter Topology                                 | 47 |

|   |      | 3.1.2   | MOS_Pseudoresistor Element                               | 49 |

|   |      | 3 1 3   | leakage Current(mimCap vs nCap & MOS Pseudoresistor)     | 52 |

|   | 3.2 | OTA in Weak Inversion                                               |

|---|-----|---------------------------------------------------------------------|

|   | 3.3 | Noise Analysis & NEF                                                |

|   | 3.4 | Load Calculation                                                    |

|   | 3.5 | Simulation Results                                                  |

|   | 3.6 | Conclusion                                                          |

| 4 | Gm  | -Current Cell (Second Stage) 6-                                     |

|   | 4.1 | Operational Transconductance Amplifier 6                            |

|   | 4.2 | Cell Choice (linearization)                                         |

|   | 4.3 | Simulation Results                                                  |

|   | 4.4 | Conclusion                                                          |

| 5 | Cur | rent Successive Approximation ADC (Third Stage) 75                  |

|   | 5.1 | 8 bit SAR_ADC Architecture                                          |

|   | 5.2 | Current Comparator                                                  |

|   |     | 5.2.1 Comparator Topology                                           |

|   |     | 5.2.2 Circuit Implementation                                        |

|   |     | 5.2.3 Accuracy Test and Dynamic Performance                         |

|   | 5.3 | Non Linear (Tanh) Current Steering DAC                              |

|   |     | 5.3.1 Current Steering DAC Topology                                 |

|   |     | 5.3.2  Weak Inversion low Voltage Current Mirror Topology  .  .  85 |

|   |     | 5.3.3 Circuit Implementation                                        |

|   | 5.4 | Logic Circuits                                                      |

|   |     | 5.4.1 Register Topology                                             |

|   |     | 5.4.2 D-Flip Flop                                                   |

|   |     | 5.4.3 Simulation Results                                            |

|   | 5.5 | Power Calculation and Optimization                                  |

|   | 5.6 | ADC Derformance & Simulations                                       |

|   |     | 5.6.1  | Simulation results                                           | 95   |

|---|-----|--------|--------------------------------------------------------------|------|

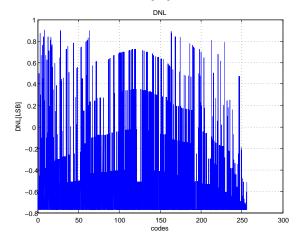

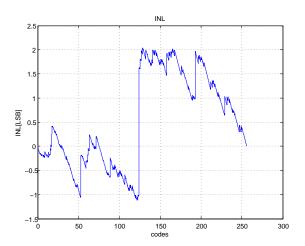

|   |     | 5.6.2  | $Static \ Performance(DNL,INL)  .  .  .  .  .  .  .  .  .  $ | 98   |

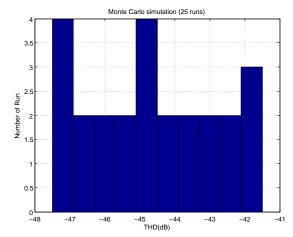

|   |     | 5.6.3  | Dynamic Performance<br>(THD,SNDR,ENOB,FOM)                   | 99   |

|   | 5.7 | Concl  | usion                                                        | 103  |

| 6 | Sys | tem Si | mulations                                                    | 104  |

|   | 6.1 | System | n Simulations in Cadance                                     | 104  |

|   | 6.2 | Monte  | e Carlo and Process Corner Simulation of the Overall System  | n110 |

|   | 6.3 | Concl  | usion                                                        | 111  |

| 7 | Cor | clusio | n                                                            | 112  |

|   | 7.1 | Design | a Summery                                                    | 112  |

|   | 7.2 | Future | e Recommendations & Suggestions                              | 112  |

|   | 7.3 | Design | a Contributions                                              | 113  |

| 8 | App | opendi | x                                                            | 115  |

|   | 8.1 | Matab  | o Code                                                       |      |

|   |     | 115    |                                                              |      |

Bibliography

# List of Figures

| 1  | The four-chamber system of the heart and the excitatory and      |    |

|----|------------------------------------------------------------------|----|

|    | conductive system<br>[1] $\hdots$                                | 13 |

| 2  | Pacemaker inside the patient's' chest[2]                         | 14 |

| 3  | Frequency vs Amplitude for ECG Signal[5]                         | 15 |

| 4  | Region of Operations of a Transistor[7]                          | 16 |

| 5  | $I_{DS}$ vs $I_{DS}$ in Weak Inversion[7]                        | 18 |

| 6  | Drain Current vs sub-threshold slope of Single NMOS $$           | 19 |

| 7  | Drain Current vs sub-threshold slope of Single PMOS              | 19 |

| 8  | Gm-C Bandpass Filter                                             | 23 |

| 9  | Very low Frequency Bandpass Filter using MOS connected Diodes.   | 24 |

| 10 | Flash ADC                                                        | 25 |

| 11 | Pipeline ADC                                                     | 26 |

| 12 | SAR_ADC                                                          | 26 |

| 13 | SNDR versus Sampling Frequency for different ADCs [16] $ \dots $ | 27 |

| 14 | Bandpass Filter Implementing a Miller integrator                 | 29 |

| 15 | Overall System Architecture                                      | 31 |

| 16 | Overall System Architecture with linear DAC                      | 32 |

| 17 | Overall System Architecture with linear Non linear DAC           | 32 |

| 18 | Output of SAR ADC with 0.7V DC input and 8 bit resolution $$ .   | 34 |

| 19 | Output of SAR ADC with DC of 0.8 V and 9 bit resolution          | 35 |

| 20 | Output of SAR ADC with DC of 0.9 V and 12 bit resolution $$      | 35 |

| 21 | Input current vs Thresholds of Linear DAC                        | 37 |

| 22 | Input current vs Thresholds of Linear DAC_Zoom                   | 37 |

| 23 | Input current vs Quantization error of Linear DAC                | 38 |

| 24 | Input current vs Quantization error of Linear DAC_zoom           | 38 |

| 25 | Input current vs Thresholds of Non Linear DAC                    | 39 |

| 26 | Input current vs Thresholds of Non Linear DAC_zoom                                                                  | 40 |

|----|---------------------------------------------------------------------------------------------------------------------|----|

| 27 | Input current vs Quantization error of Non Linear DAC $\ .\ .\ .\ .$                                                | 40 |

| 28 | Input current vs Quantization error of Non Linear DAC_zoom $% \left( 1\right) =\left( 1\right) =\left( 1\right) $ . | 41 |

| 29 | SQNR Histogram of SAR ADC for $0.028 \mu M$ mismatch of the                                                         |    |

|    | linear DAC                                                                                                          | 42 |

| 30 | SQNR Histogram of SAR ADC for $0.039 \mu M$ mismatch of the                                                         |    |

|    | linear DAC                                                                                                          | 43 |

| 31 | SQNR Histogram of SAR ADC for $0.05 \mu M$ mismatch of the lin-                                                     |    |

|    | ear DAC                                                                                                             | 43 |

| 32 | SQNR Histogram of SAR ADC for $0.028 \mu M$ mismatch of the                                                         |    |

|    | Non_linear DAC                                                                                                      | 44 |

| 33 | SQNR Histogram of SAR ADC for $0.039 \mu M$ mismatch of the                                                         |    |

|    | Non_non linear DAC                                                                                                  | 45 |

| 34 | SQNR Histogram of SAR ADC for $0.05 \mu M$ mismatch of the                                                          |    |

|    | non_linear DAC                                                                                                      | 45 |

| 35 | Bandpass Filter Topology                                                                                            | 48 |

| 36 | Gain vs Frequency for the Proposed Bandpass Filter                                                                  | 48 |

| 37 | Comparison Between Simulated Resistances of Different MOS                                                           |    |

|    | Pseudoresistor Designs                                                                                              | 50 |

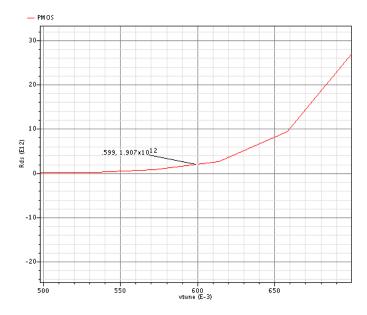

| 38 | Rds vs V<br>tune for PMOS Pseudoresistor by Equ.23 $\ \ldots \ \ldots$ .                                            | 51 |

| 39 | Rds vs V<br>tune for simulated PMOS Pseudoresistor $\ \ldots \ \ldots \ \ldots$                                     | 52 |

| 40 | Two Stage Miller Op Amp                                                                                             | 54 |

| 41 | ${\rm I}_D$ vs Input Voltage Noise of the Bandpass Filter from Equ. 28 $$ .                                         | 56 |

| 42 | Bandpass Filter Circuit Design                                                                                      | 58 |

| 43 | Frequency Response of Bandpass Filter                                                                               | 60 |

| 44 | Input referred thermal noise of Bandpass Filter simulated from                                                      |    |

|    | $50 \mathrm{mHz}$ to 100Hz and calculated by Equ. 31 $\ \ldots \ \ldots \ \ldots$                                   | 60 |

| 45 | Transient analysis @2.5mV input and 2.23Hz Frequency input             | 61 |

|----|------------------------------------------------------------------------|----|

| 46 | Transient analysis @2.5mV and 60Hz Frequency input $\ \ldots \ \ldots$ | 62 |

| 47 | Transient analysis @2.5mV and 45mHz Frequency input $\ .\ .\ .\ .$     | 63 |

| 48 | Gm_Cell                                                                | 64 |

| 49 | Operational Transconductance Amplifier                                 | 65 |

| 50 | Fixed transconductor                                                   | 66 |

| 51 | Fixed Transconductors using CMOS connected diodes $\ \ldots \ \ldots$  | 67 |

| 52 | DC-Output Current                                                      | 69 |

| 53 | DC-Output Current with Error                                           | 70 |

| 54 | Sine wave_Output Current                                               | 71 |

| 55 | gm of Gm block                                                         | 71 |

| 56 | Frequency response of low frequency filter in gm Cell                  | 72 |

| 57 | Noise of Gm from 50mHz to 100Hz calculated by Equ. 31 $$               | 72 |

| 58 | gm_source degeneration transconductors $\dots \dots \dots$             | 73 |

| 59 | SAR_Architecture                                                       | 75 |

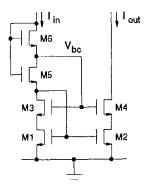

| 60 | Current Comparator by Traff[51]                                        | 77 |

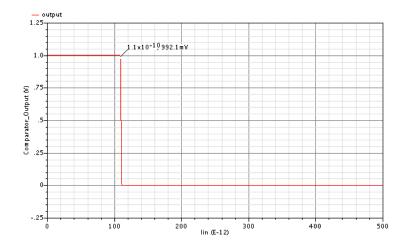

| 61 | Current Comparator                                                     | 78 |

| 62 | Iin vs Output Voltage of Comparator with Iin=100pA $\ \ldots \ \ldots$ | 79 |

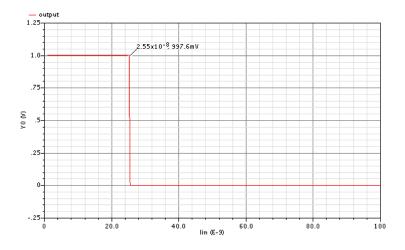

| 63 | Output of Current Comparator with I=25.5nA $\dots$                     | 79 |

| 64 | Iin vs Output Voltage of the Comparator with input current sine        |    |

|    | Wave(200pA)                                                            | 80 |

| 65 | Linear Unary Wighted Control DAC                                       | 81 |

| 66 | Edward's current cell[53]                                              | 82 |

| 67 | Unary Current DAC                                                      | 83 |

| 68 | current_mirror by Bruun[59]                                            | 84 |

| 69 | Current Mirror by Abo                                                  | 85 |

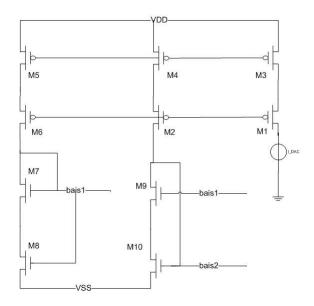

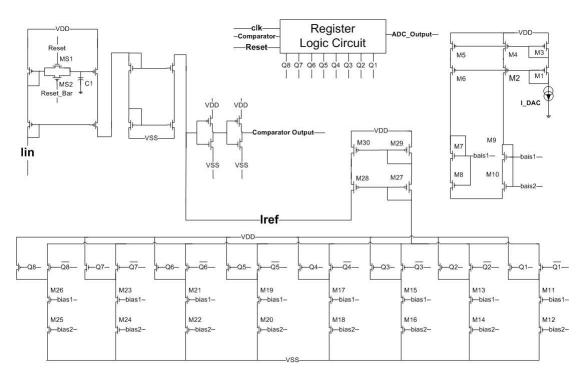

| 70 | Current Successive Approximation ADC                                   | 86 |

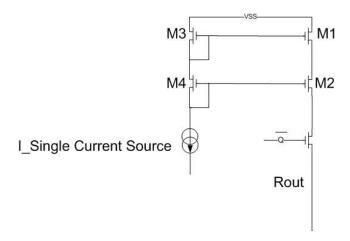

| 71 | Single current source in Unary DAC 8                                             |

|----|----------------------------------------------------------------------------------|

| 72 | Register logic                                                                   |

| 73 | D-Flip Flop by Rabea                                                             |

| 74 | D-Flip Flop                                                                      |

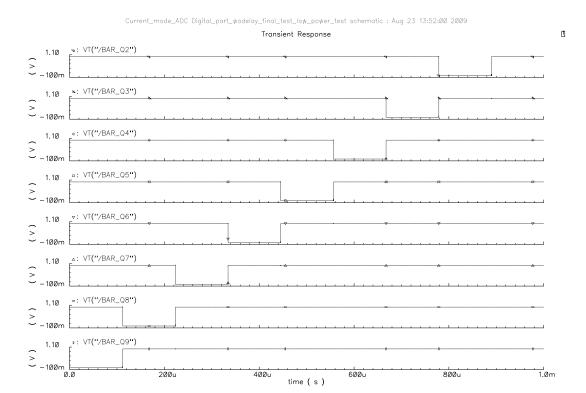

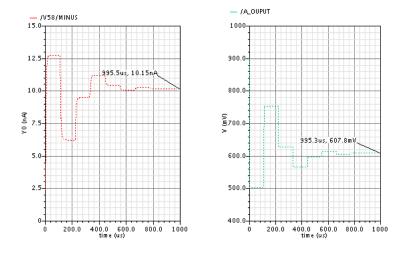

| 75 | Transient output of Upper Shift register of SAR logic Circuit 9                  |

| 76 | Transient output of the lower Shift register of SAR logic Circuit 9              |

| 77 | ADC Output with DC input 9                                                       |

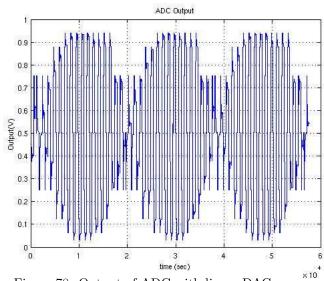

| 78 | Output of ADC with linear DAC                                                    |

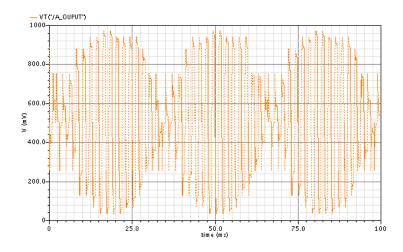

| 79 | ADC_Non linear DAC                                                               |

| 80 | DNL of ADC with non linear DAC                                                   |

| 81 | INL of ADC with non linear DAC                                                   |

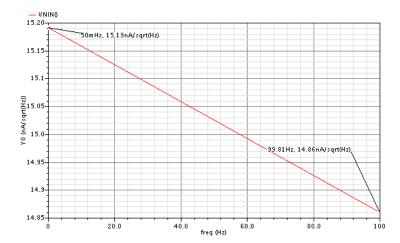

| 82 | Noise of Current Comparator from $50\mathrm{mHz}$ to $100\mathrm{Hz}$ calculated |

|    | by Equ. 31                                                                       |

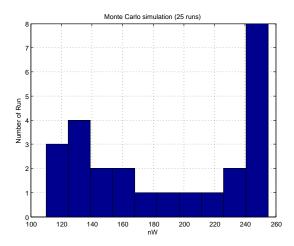

| 83 | Montcarlo Simulation_THD                                                         |

| 84 | Montcarlo Simulation_Total Power                                                 |

| 85 | Overall System                                                                   |

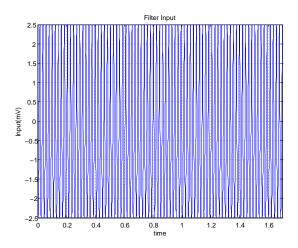

| 86 | Input Voltage                                                                    |

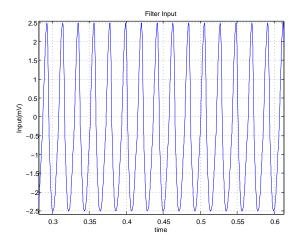

| 87 | Input Voltage_zoom                                                               |

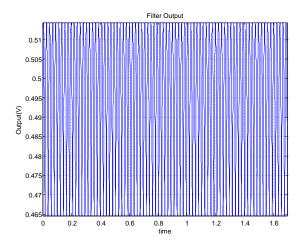

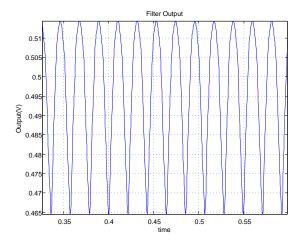

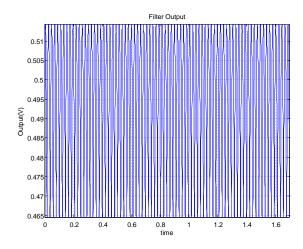

| 88 | Output Voltage of the Bandpass Filter                                            |

| 89 | Output Voltage of the Bandpass Filter                                            |

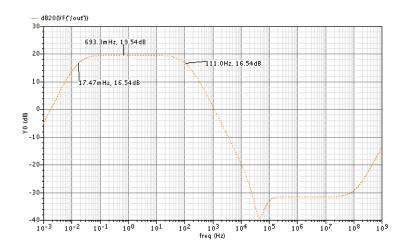

| 90 | Frequency Response of the Filter                                                 |

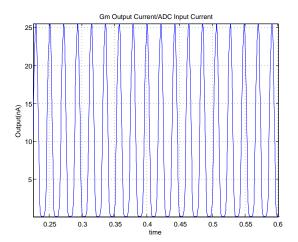

| 91 | Output Current of Gm-Cell                                                        |

| 92 | Output Current of Gm-Cell_zoom                                                   |

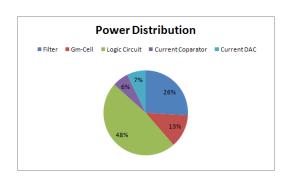

| 93 | System power distributions                                                       |

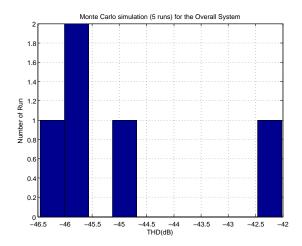

| 94 | System Monte Carlo Simulation_THD                                                |

# 1 Introduction

In this chapter, a background about the functionality of the heart is introduced. An overview of the pacemaker is presented. ECG signal is explained briefly. In order to have good understanding of low power circuit design, different aspects of weak inversion operation of CMOS transistors are explained. Finally, the motivation and outline of the thesis is presented.

## 1.1 Background

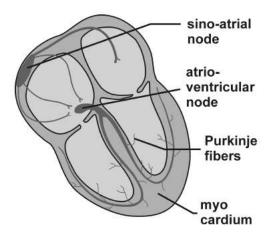

The heart as electrophysiological system controls the speed and rhythm of the heart beat. An electrical signal goes from the top of the heart to the bottom with each heartbeat. In the sinoatrial node (SA node) the cells generats electrical signals with a frequency of about 70 beats/min. These cells (pacemaker cells) directly control the heart rate. The electrical signal is triggering the rhythmic contractions of the heart muscle. The whole heart takes about 100ms to be excited. It takes the heart, at rest ,180ms to conduct from the sinus node to the atrio-ventricular node (AV) as shown in Fig. 1[1].

Figure 1: The four-chamber system of the heart and the excitatory and conductive  $\operatorname{system}[1]$

The Alrio vertical conduction time (AVCT) is controlled by the autonomous nervous system (ANS). If the body goes through physical or emotional stress, the heart rate increases.

#### 1.1.1 Pacemaker & ECG

#### • Pacemaker

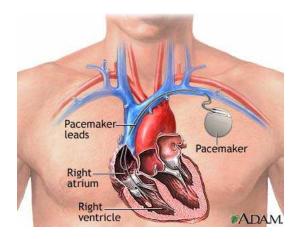

A pacemaker is a medical device that delivers low-energy electrical pulses to correct abnormal the heart beat, via the electrodes connected to the heart muscles, as shown in Fig. 2 [2]. The main functionality of the artificial pacemaker is to regulate the heart rate as the heart's natural pacemaker is too slow or absent [3].

Figure 2: Pacemaker inside the patient's' chest[2]

A pacemaker consists of a battery, usually a lithium battery, processor (generator), wires with electrodes connected to the heart. The generator is placed below the chest wall above the muscles. A metal box contains the battery and the processor. The metal box is fabricated with titanium in order for the body not to be rejected [4].

The processor ,which is a IC, sends the electrical pulses to the heart to correct the beat. The chip is programmed to send the correct type of pulses to the heart. Also, the IC chip records the activity of the heart in order for the doctor or specialist to tune the pacemaker to perform sufficiently depending on the heart rhythm.

#### • ECG

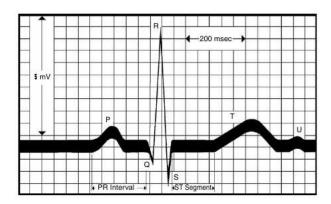

The pacemaker needs to monitor the heart beat in order to supply the right pulls. A recording of a human heart beat is known as Electrocardiograph (ECG) and is shown in Fig. 3 [5].

Figure 3: Frequency vs Amplitude for ECG Signal[5]

The ECG can be measured by placing electrodes on the skin. Electrodes are placed in different sides of the heart in order to measure the different activities of the heart. If there are any damages or abnormal rhythm, the ECG gives clear indication about the overall rhythm of the heart[6].

From Fig. 3, an ECG signal has subsequent waves which are labeled P, Q, R, S and T. The waves originate from the depolarization and repolarization of the muscles in the heart. In this thesis, QRS complex and T wave are considered as required by the pacemaker. The signal which are detected by the electrode are

converted to digital by ADC inside the pacemaker. The Internal ECG signal has frequency-band (50m~100Hz) and amplitude 5mV[5]. To filter the IECG with low noise and an utral low power, transistors have to opearte in weak inversion.

#### 1.1.2 Weak Inversion CMOS

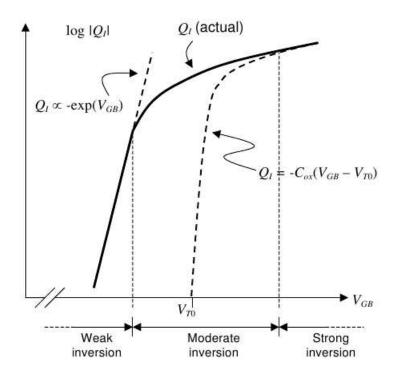

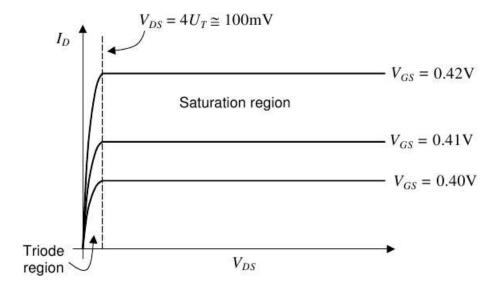

In weak inversion, QI(inversion layer charge) is an exponential function of gate voltage as show in Fig. 4 [7]. Also, QI is much less than the depletion region charge (QB)[7, 8].

Figure 4: Region of Operations of a Transistor[7]

In weak inversion, currents flows by diffusion, not drift, because the channel does not have enough charge to generate a significant electric field which pulls electrons from the source to the drain. Drain current and gm are expressed by Equ. 24,25. The MOSFET in weak inversion behaves very similar to bipolar transistor[7, 8, 9, 10]

$$I_D = \frac{W}{L} I_{DO} \exp\left(\frac{\kappa V g - V s}{V_T}\right) \text{ for } V_{DS} \ge 4V_T \tag{1}$$

Where  $I_D$  is the drain current, W is width, L is length,  $I_{DO}$  is zero-bias current,  $V_g$  is gate voltage, Vs is the source voltage,  $V_T$  is thermal voltage,  $\kappa$  is gate coupling coefficient.

$$g_m = \frac{I_D}{nKT/q} \tag{2}$$

Where K is  $1.38 \cdot 10^{-23}$  J/K (Boltzmann's constant), q is  $1.60 \cdot 10^{-19}$  C (elementary charge), T is temperature, n is sub-threshold slope.

As noticed in Equ. 24,  $I_D$  changed as  $V_{gs}$  increased. Also, gm is function of drain current and n(sub-threshold slope). To keep a MOSFET in saturation  $V_{DS}$  should be greater or equal to  $4V_T$ , approximately 100mV, as shown in Fig. 5 [7].

Figure 5:  $I_{DS}$  vs  $I_{DS}$  in Weak Inversion[7]

To have better understanding of the whole system, an accurate equations of the parasitic capacitance is needed. The parasitic capacitance in weak inversion are calculated as follows[11].

$$C_{qs} = C_{ox} I_f \tag{3}$$

$$C_{ad} = C_{ox} I_r \tag{4}$$

$$C_{gb} = C_{ox.} \frac{n-1}{n} \tag{5}$$

Where  $C_{gs}$  is gate-to-source capacitance,  $C_{gd}$  is gate-to-drain capacitance,  $C_{gb}$  gate-to-bulk capacitance, Cox is the gate oxide capacitance per unit area,  $I_f$  is forward normalized current,  $I_r$  is reverse normalized current and n is sub-threshold slope.

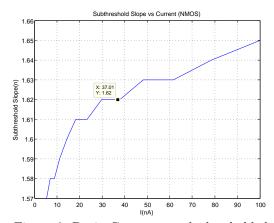

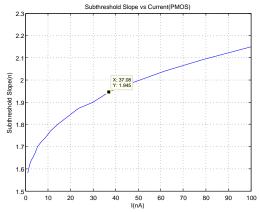

The value of sub-threshold slope(n) varies in different technologies. In this design, n is calculated by simulating single NMOS and PMOS. The fundamental minimum of n is 1. Also, the value of the n depends on the value of the current. The value of n for NMOS and PMOS is plotted in Fig. 6,7. Giving the operation current of the filter of 37nA,  $n_{NMOS}$  is equal to 1.62 and  $n_{PMOS}$  is equal to 1.945. The sub-threshold slope(n) is calculated by Equ. 25.

Figure 6: Drain Current vs sub-threshold slope of Single NMOS

Figure 7: Drain Current vs sub-threshold slope of Single PMOS

As shown in Fig. 6,7, as the current increased the value of n increased.

#### 1.2 Motivations

The life time of pacemaker is approximated to be around 5 to 10 years- an average of seven years [12]. However, more functionality at limited budget requires less power per function. Therefore, the power consumption of the pacemaker has to be reduced. The analog to digital converter in the pacemaker consumes the largest amount of power in the front-end, called the sense amplifier. Also, noise is major concern when an ultra power circuit design is needed. To achieve such low power, transistors operating in weak inversion have to be used. A current SAR ADC is proposed to reduce the power consumption. In this thesis, the input of the pacemaker is filtered and converted to current. The total simulated power consummation is approximately reduced by 50% when compared with the state of the art designs. In addition, because of the current DAC, the size of the pacemaker is smaller than other designs which implement a voltage DAC.

#### 1.3 Thesis Outlines

In this thesis, Chapter 2 introduces the system level design and architecture. A literature review of the state of the art design is presented. Design methodology of the filter and ADC is explained in details. Matlab simulations are performed to show the advantages and disadvantages of the different system level design.

In chapter 3, a bandpass filter circuit is designed. Different topologies are discussed in great details. Noise and power are optimized to get the required performance. Several challenges like leakage and non linearity are presented and solved.

In chapter 4, voltage to current converter is designed using Gm-cell. The output current of the gm is chosen careful to minimized the power. The linearity of the gm is discussed. Different linearization techniques are explained briefly

with necessary simulations.

In chapter 5, the system and circuit design of the ADC is presented. Each block is discussed with all the different design challenges and trade off. Current mirror is presented in great details since it is essential element in the current SAR\_ADC. Statics and dynamics performance are presented by simulation results with Monte Carlo and process corner.

In chapter 6, the whole system is connected to each other and simulated. Monte Carlo and process Conner simulations is performed to test the robustness of the overall system. Comparison between the recent state of the art design is presented.

In chapter 7, a summery of the thesis with future recommendations are introduced. Also, the design contributions are listed as points.

# 2 System Architecture & Design

In this chapter, an over view about the previous works is introduced. literature review about low pass filter and different type of ADC's is explained. Design methodology of the low pass filter and ADC's is explained in details. The system level design of this work is introduced with details about the system parameters. Matlab simulations of the ADC is introduced to verify the system level design performance.

### 2.1 literature Review

In order to construct a bio-signal interface for wearable or implanted biomedical devices, certain system requirements should be meet. Most of the advance system required the output to be digitized for more sufficient processing. The input signal should go through very low frequency pass filter to relax the requirements on the ADC. The main requirements of the ADC is to consume little power to facilitate its integration with low-power digital circuitry.

#### 2.1.1 Very low Frequency pass Filter

A significant amount of research has been dedicated seeking ways to have very low frequency pass filter. The most conventional way to desing a very low frequency pass filter (50mHz~100Hz) is to have RC filter with large capacitor or large resistor which is not practical in low power low noise IC design. Large R and C consumes large amount of power and produc a lot of noise.

Another solution is to implement a Gm-C Filter. As state in the literature, two stage Gm cell are needed to implement a bandpass filter as shown in the Fig. 8 [13].

Figure 8: Gm-C Bandpass Filter

In Fig. 8, two active Gm-C stages has two poles to implement bandpass filter. The low cut off frequency and quality factor are calculated by Equ. 6,7 respectively.

$$\mathbf{Wo} = \sqrt{\frac{\mathbf{g_1}\mathbf{g_2}}{C_1C_2}} \tag{6}$$

$$\mathbf{Q} = \sqrt{\frac{\mathbf{g_1}}{\mathbf{g_2}}} \frac{\mathbf{C2}}{\mathbf{C1}} \tag{7}$$

$W_o$  and Q can be controlled the ration of C2,C1 and g1,g2. However, there are several drawback to the two stage design:

- 1-Complexity.

- 2-Higher power.

- 3-Lower DR.

- 4-Typical tolerances for both C and gm are in the range of +30%.

Finally, MOS connected diodes in parallel with capacitor could be used in the feedback of an amplifier as shown in Fig. 9[14]. More elaborate explanation will be in Chapter 3.

Figure 9: Very low Frequency Bandpass Filter using MOS connected Diodes.

#### 2.1.2 Data Converters

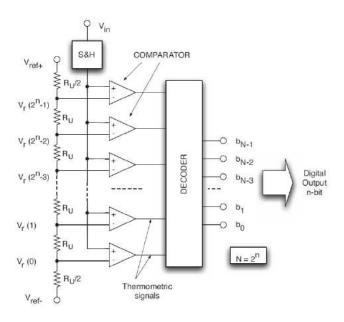

In order to choose the desire type of the analog to digital converter, different types of ADC's have been studied. ADCs can be divided into nyquist-rate sampling and over-sampling converters. For example, Sigma-delta ADCs are used for high bit resolution and demand high clock frequency to over-sample the input signal. The over-sampling ADC consumes large power and requires complex circuitry. Therefore, Sigma-delta is eliminated for this work's requirements. Nyquist-rate ADC converters can be divided into three categories:

- (1) Flash

- (2) Pipeline

- (3) Successive-Approximation

1-Flash ADC uses a voltage ladder with a comparator. At each step of the ladder, the input voltage is compare with a reference voltages. The ladders are implemented by resistors or capacitor. The output of comparators is fed into a digital encoder as shown in the Fig 10. For each additional bit, twice the amount of comparators are needed. Therefore, the power consumption is higher.

As a result, Flash ADC is usually used for low bit resolution and high-frequency applications.

Figure 10: Flash ADC

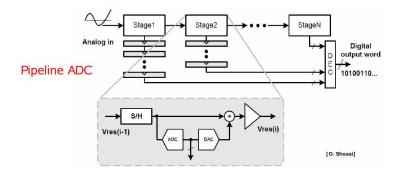

2-Pipeline ADC uses two or more steps of subranging ADC. First, it performs a coarse quantization of the input. Second, it calculates the residue of the first step using DAC and subtractor. Third, it performs a fine quantization on the residue and adds it digitally to the output as shown in the Fig. 11. For each additional bit, one comparator is needed. Therefore, the power consumption would be higher. The power consumption of pipeline is less than Flash ADC. However, pipeline ADC require more design time than Flash ADC. As a result, Pipeline ADC usually used for high bit resolution and high frequency.

Figure 11: Pipeline ADC

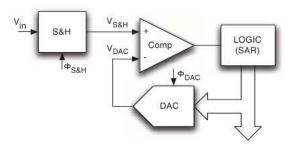

3-Successive Approximation (SAR) performs the conversion over multiple clock periods by exploiting the knowledge of previous bits to compute the next bit. The method aims to reduce the circuit complexity and power consumption using a low conversion rate by allowing one clock period per bit (plus one for the input sampling). The sampled input compared with half of the full scale. Then throughout the clock periods, the next sampled is compared with the output of the DAC. The algorithm is controlled by Logic circuit as shown in Fig. 12[15].

Figure 12: SAR\_ADC

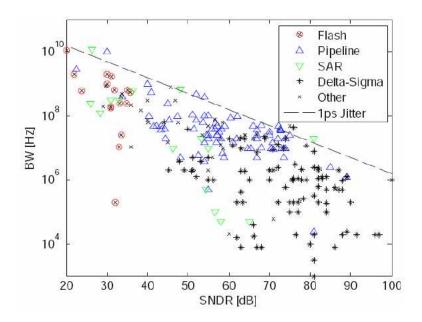

SNDR versus sampling frequency is plotted for different ADCs to know the

trade off as shown in Fig. 13 [16].

Figure 13: SNDR versus Sampling Frequency for different ADCs [16]

# 2.2 System Design and Architecture

Different filter implementations are discussed in this section. Also, different ADC's is explained to meet the requirements of the system. Advantages and disadvantages of two systems designs are discussed as well.

## 2.2.1 Filter Design Methodology

The value of R or C in RC low pass filter should be very big to filter such low frequency(50mHz~100Hz) according to Equ. 9,8.

$$\frac{Output\left(Filter\right)}{Input\left(Filter\right)} = \frac{1}{1+s\tau} \tag{8}$$

$$\mathbf{f_{low}} = \frac{1}{2\pi \mathbf{RC}} \tag{9}$$

For low power low noise, R can not be very big because it would introduce a lot of noise. Also, C can not very big because it consumes a large ship area. For example, to filter an ECG signal, the value of the C would be around 3.2nF with R=1G or  $318G\Omega$  with C=10pF which are not practical in IC.

To solve this problem, the resistance or capacitance should be larger without enlarging the actual value of R or C. There are several methods to amplified capacitance or resistance. First, the gm of the Gm-C cell could be used instead of the R in the RC filter as in Equ. 11,10.

$$\tau = \frac{C}{g_m} \tag{10}$$

$$f_{3dB} = gm/2\pi C \tag{11}$$

gm could be control by the input current. However, as stated in 1.1.1, two Gm-C filter stages are needed to implement bandpass filter[13].

In[17][18], CMOS triode transconductor could produce gm down to hundreds of pA/V. Such transconductor could be used in gm-C filters with cut-off frequencies in the range of Hz and sub-Hz. The gm value is controlled by a transistor size and Vds. However, for the application of the design, filter proposed has relatively a large chip area, high noise, poor THD comparing to other techniques[19].

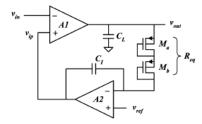

Second, the filter could be implemented by R, MOS Pseudoresistor elements[14], and a capacitor. In [20, 21], the value of the capacitance is amplified by Miller integrator as shown in Fig. 14[20].

Figure 14: Bandpass Filter Implementing a Miller integrator

The Miller integrator is placed within its feedback path where  $A_2$  provides a voltage gain. The active Miller integrator is made from a second amplifier. However, it suffers from input signal variations, non linearity. Also, two active elements are needed to implement the filter which increase the power consumption.

Harrison implements low-noise low-power single-ended operational transconductance amplifier (OTA) with capacitive feedback[14]. The low cut off frequency is calculated by Equ. 12 [14].

$$f_{low} = \frac{1}{2\pi CR - Pseudoresistor} \tag{12}$$

The key point to have a large R-Pseudoresistor is control gate voltage of the CMOS connected diode.

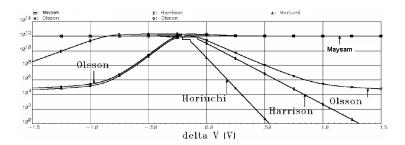

However, the MOS- bipolar resistance in [14] is highly dependent on the output signal level, which results in distortion and low-cutoff frequency variations.

Olsson et al. implemented MOS-bipolar pseudo-resistor by controlling the gate of NMOS pair in weak inversion.[22]. Horiuchi et al. reported gate controlled nFET biased in weak inversion[23]. Parthasarathy et al. presented PMOS connected diode and using the input capacitance of the OTA as the C in the RC low pass filter[21]. In the case of large signals, distortion will oc-

cur due to the degradation of the low frequency gain caused by the decrease of the pseudo-resistor. Mohseni et al. used gate voltage controlled NMOS pseudo-resistors with resistive feedback[24]. Resistive feedback is implemented by trimming laser resistor which is programmed only once. Also the resistive feedback could increase size and power consumption. Ming et al and Wise et al used voltage controlled PMOS NMOS with external circuit[25][26]. In conclusion, implementing a conventional RC filter is not practical and Gm-C cell suffers from low DR and high power . consumption. The Miller integrator suffers from input signal variations, non linearity. Implementing a low pass filter for ECG signal using Pseudoresistor is most suitable for this design.

Full details about the differences in implementing Pseudoresistor and the filter design will be discussed in Chapter 3.

#### 2.2.2 ADC Design Methodology

ADC consumes the largest power in the pacemaker. The ADC required for ECG signal is 8 bit with 1Ks/s[27]. Comparing the different types of ADC in 2.1.2, Successive-approximation ADC consume the lowest amount of power because it does not have Operational Amplifier. Although, it is a low speed ADC, but it satisfied the ECG requirements. Most of the biomedical signals do not require more than 10 bit ADC. As a result, successive-approximation ADCs has recently become very attractive in energy- efficient moderate-resolution/moderate-speed applications[28, 29, 30, 19, 31, 32, 33]. In order to minimize the power as mush as possible, Current Mode Successive Approximation ADC is presented. The idea of current mode ADC is first introduced by Salama [34]. Current SAR\_ADC is used for the fallowing reasons. First, the power consumption is proportional to the full scale current input. A full details analysis of the relationship are discuss in Chapter 5 [35]. Second, the chip area is much less since, no capacitor in sued in the DAC[34]. Current DAC using current sources

would be used. Although, there is constant power dissipation because of the use of constant current sources[36]. However, in weak inversion, the current is very small (nonocurrent) and if the full scale input current is chosen carefully, this effect is minimized.

In the literature, there are two Current Successive Approximation ADC proposed[37, 35]. The current DAC in the Current Successive Approximation ADC could be scaled down easily with technology. Chao et al used an Op-amp in his design which increases the power consumption. In general, there were not enough information or circuit performance in the proposed circuit. Iniewski el al.design consumes one of the lowest power, 560nW, reported in the literature. However, the design suffers from biasing problems in the current mirror which leads to less accuracy especially with very small reference current value. Also, there are numbers of redundant current mirror which can be eliminated to reduce the power and the error. A details analysis of the power consumption ,biasing and the proposed Current SAR is discuss in Chapter 5.

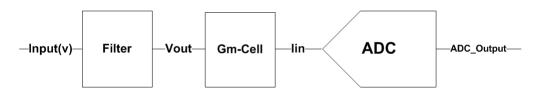

#### 2.2.3 System Architecture

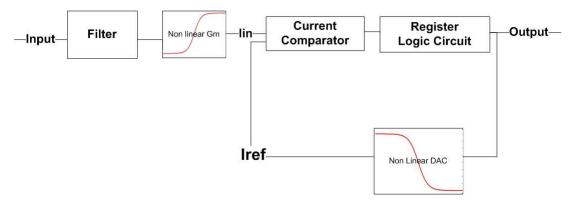

The goal is to design an implanted biomedical devices which filter the signal then digitized it using SAR ADC. In the literature, there are two system which consist of very low frequency pass filter fallowed by Voltage Successive Approximation ADC[19, 33]. The system proposed in this work consist mainly of a bandpass filter fallowed by gm cell to convert the voltage to current then Current SAR\_ADC as shown in Fig. 15

Figure 15: Overall System Architecture

There are two possibility of the proposed system. First, low pass filter fallowed by linearized operational transconductance amplifier fallowed by Current SAR as show in Fig. 16.

Figure 16: Overall System Architecture with linear DAC

Second, bandpass filter fallowed by operational transconductance amplifier without linearization. To solve the non-linearity of the Gm-cell ,non linear tangent hyperbolic current steering DAC inside the Current SAR\_ADC is designed as illustrated in the Fig. 17.

Figure 17: Overall System Architecture with linear Non linear DAC

Matlab simulations of the ADC is perform in sec. 2.3 to show the differences and potentials between the two systems.

#### 2.3 ADC-Matlab Simulation

A more elaborate explanation of the functionality of the conventional SAR ADC in presented in this section using Matlab simulations. Each block of the ADC is modeled by Matlab code. The code could be used for different resolutions and sampling rate. The SAR algorithm could be changed as well. The comparator is modeled as a subtractor. The input of the comparator is the actual output of the Gm block from CADANCE. The quantization level of the DAC are modeled by Equ. 13.

$$Ideal \, Quantization \, Level = \frac{2^{j-1}}{2^{nbit+1}} \tag{13}$$

$$j = 1: nbit (14)$$

Where nbit is the number of bit. j is an incremental number. j presents the number of thresholds. A mismatch in the capacitor or transistors could be introduced by Equ. 15,16.

$$Mismatch = Normalized Mismatch Percentage.Randn$$

(15)

$$Quantization Level - Mismatch = \frac{\left[2^{j-1} + (Mismatch.2^{j-1})\right]}{2^{nbit+1}}$$

(16)

Since the nature of mismatch is random, randn, a Matlab code, returning a pseudorandom, is introduced in Equ. 15. The SAR logic modeled by separate Matlab codes. Input value is compared with the reference value from the DAC. Linear and non linear offset could be introduced in the comparator. SQNR is calculated without windowing as mentioned in Appendix A.

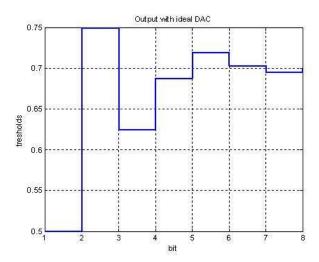

The first testing is performed with ideal conditions. There is no mismatch in the DAC or offset in the comparator. In order to make sure that the MATLAB model is functioning according to the theory, a DC signal of  $0.7\mathrm{V}$  with 8 bit resolution is tested as shown in Fig. 18. In theory,  $0.7\mathrm{~V}$  is compared with  $0.5\mathrm{~V}$ , the difference is greater than 0, then 0.25 is added to  $0.5\mathrm{~V}$ , then the difference between  $0.7\mathrm{~and~}0.75(0.5+0.25)$  is less than 0, then 0.125 is subtracted from 0.75, then the difference between  $0.7\mathrm{~and~}0.625(0.75-0.125)$  is greater than 0. The same algorithm is performed through out the 8 cycles.

Figure 18: Output of SAR ADC with 0.7V DC input and 8 bit resolution

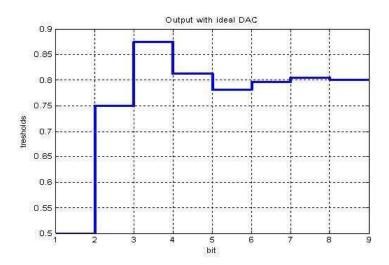

The output of the simulation agrees with the theory as mentioned. The final value is 0.69922 V which is very close to 0.7 V. To make sure that the system is working, different values of DC signal with different number of bit are applied to ADC as shown in Fig.19,20.

Figure 19: Output of SAR ADC with DC of  $0.8~\mathrm{V}$  and 9 bit resolution

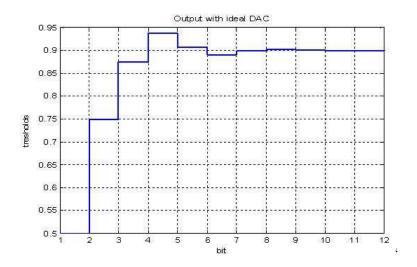

Figure 20: Output of SAR ADC with DC of 0.9 V and 12 bit resolution

The output of both simulations agrees with the theory. The same method of calculating of 0.7V 8 bit is applied to the plots above. Therefore, the MATLAB model is functioning correctly according to the theory.

#### 2.3.1 Linear Current Steering DAC

linear and non linear DAC are tested with actual output of the gm-cell without any linearization techniques. The two system perform an 8 bits ADC without mismatch in the current sources. Then, the simultions are performed with mismatch. The quantization noise and SNR are calculated in all the different conditions. For 8 bit linear DAC the quantization levels is describes in Equ. 17:

$$X_Q = 2^{-n}n = 1..8 (17)$$

Where n is the number of bit. The quantization levels in the current DAC are(1,2,4,8,16,32,64 and 128). Ideally the maximum value of the quantization noise is calculated by Equ. 18:

$$\frac{1}{2}LSB = \frac{I_{Full\ Scale}/2^{N-1}}{2} \tag{18}$$

For 8 bit ADC, 0.5 LSB=0.003906. Also, The ideal SQNR is calculated by Equ. 19:

$$SQNR = [(N * 6.02) + 1.78] dB (19)$$

For 8 bit ADC, The ideal SQNR=49.92dB.

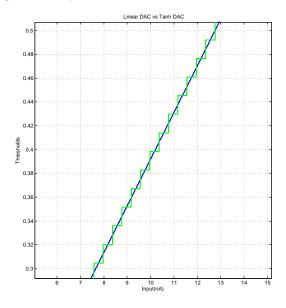

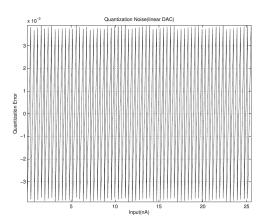

The output of the linear DAC and the Quantization noise is shown in Fig. 21,23.

Figure 21: Input current vs Thresholds of Linear DAC  $\,$

Figure 22: Input current vs Thresholds of Linear DAC\_Zoom

Figure 23: Input current vs Quantization error of Linear DAC

Figure 24: Input current vs Quantization error of Linear DAC\_zoom

From Fig. 21, the output of the DAC is fallowing the input. The  $\frac{1}{2}$  LSB 0.00385 which is very equal to theoretical 0.003906. The SQNR was measured with sine wave input to be 49.8dB which is very close to the theoretical, 49.92 dB.

## 2.3.2 Non linear Tangent Hyperbolic Current Steering DAC

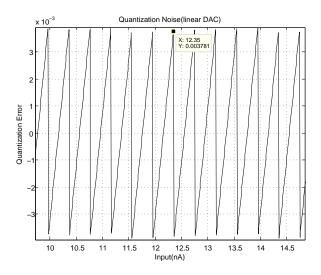

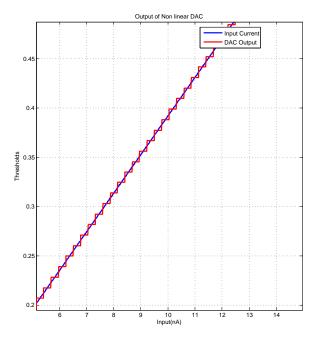

The DAC implements Tangent Hyperbolic because the nature of the non linearity of the gm-cell is Tangent Hyperbolic. The quantization levels in the non-linearity current DAC are [1,2.26,4.1,7.95,16.211,31.8,63.8,127.9]. The output of the linear DAC and the Quantization noise are shown in Fig. 25,27. The non linearity could not be shown easily only if is compared with linear input with linear DAC.

Figure 25: Input current vs Thresholds of Non Linear DAC

Figure 26: Input current vs Thresholds of Non Linear DAC\_zoom

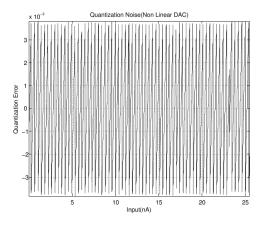

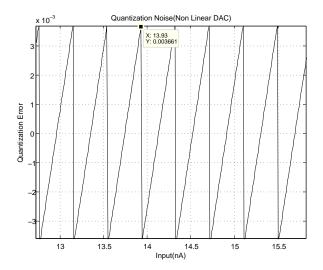

Figure 27: Input current vs Quantization error of Non Linear DAC

Figure 28: Input current vs Quantization error of Non Linear DAC zoom

From Fig. 27, the output of the DAC is fallowing the input. The  $\frac{1}{2}$  LSB 0.00375 which is less than the theoretical value. The SNR was measured with sine wave input to be 50.5 dB which is higher than the theoretical value. As a result, the non linear DAC has lower quantization noise and higher SQNR. The the non linear DAC fallows the sine wave more accurately than the linear DAC. To have a fair judgment, a triangular wave form is tested in both systems. The linear DAC has higher SQNR and lower quantization noise than the non linear DAC .The linear DAC fallows the triangle wave form form more accurately than non linear DAC.

### 2.3.3 Measuring SQNR with Mismatch

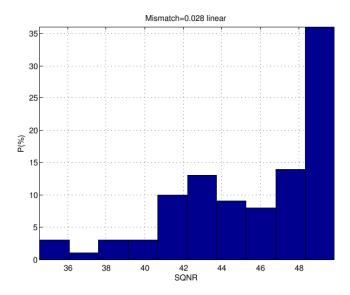

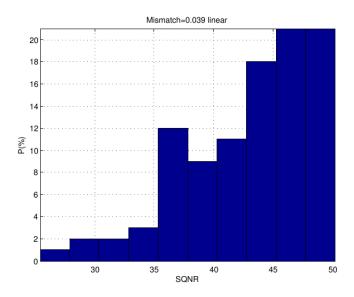

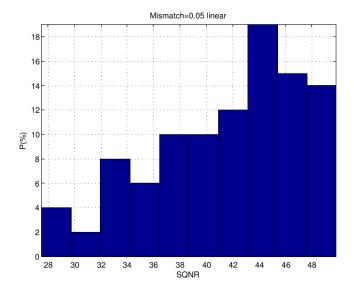

To have more insight about the performance of both systems, different mismatches are applied. The mismatch percentage are taken from the model of IBM  $0.13\mu M$ . The mismatch is applied by Equ. 15. The mismatches,  $\Delta W$ , are  $0.028~\mu M$  (all tolerance are  $3~\sigma$  value),  $0.039\mu M$  (chip mean value) and  $0.05\mu M$  (total tolerance). linear and non linear DAC are simulated simultaneously. His-

togram of the 100 runs is plotted to see how may of the runs falls into a certain value of SQNR as shown in Fig. 29,30,31.

Figure 29: SQNR Histogram of SAR ADC for  $0.028 \mu M$  mismatch of the linear DAC

Figure 30: SQNR Histogram of SAR ADC for  $0.039 \mu M$  mismatch of the linear DAC

Figure 31: SQNR Histogram of SAR ADC for  $0.05 \mu M$  mismatch of the linear DAC

The mean values of the SQNR for linear DAC with the different mismatch is presented in Table. 1.

| $Mismatch(\mu M)$ | SQNR(dB) |

|-------------------|----------|

| 0.028             | 45.5     |

| 0.039             | 43       |

| 0.05              | 41.5     |

Table 1: Compression between simulated SQNR of linear DAC with Mismatch

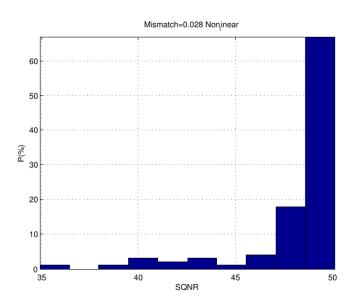

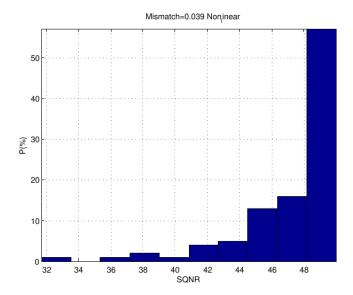

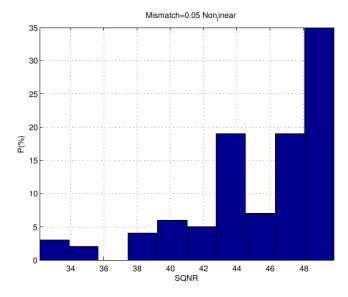

The value of SQNR is degrading at the mismatched increasing. For non linear DAC, the Histogram plots are show in Fig. 32,33,34.

Figure 32: SQNR Histogram of SAR ADC for  $0.028\mu M$  mismatch of the Non\_linear DAC

Figure 33: SQNR Histogram of SAR ADC for  $0.039 \mu M$  mismatch of the Non\_non linear DAC

Figure 34: SQNR Histogram of SAR ADC for  $0.05 \mu M$  mismatch of the non\_linear DAC

The mean values of the SQNR for linear DAC with the different mismatch is presented in Table. 2.

| $Mismatch(\mu M)$ | SQNR(dB) |

|-------------------|----------|

| 0.028             | 48.14    |

| 0.039             | 47.26    |

| 0.05              | 45.33    |

Table 2: Compression between simulate SQNR of Non linear DAC with Mismatch

The value of SQNR is degrading as the mismatched increasing. However, the SQNR of the non linear DAC is higher than linear DAC for the same reasons mentioned in 2.3.2 as shown in Table. 3.

| $Mismatch(\mu M)$ | SQNR(dB)_Non linear | SQNR(dB)_Linear |

|-------------------|---------------------|-----------------|

| 0.028             | 48.14               | 45.5            |

| 0.039             | 47.26               | 43              |

| 0.05              | 45.33               | 41.5            |

Table 3: SQNR Compression between Linear and Non linear DAC

As a result, non linear DAC is implemented in this design because of its performance and ease of implementation of similar non linearity of Gm block.

### 2.4 Conclusion

The input signal of wearable or implanted biomedical devices should go through very low pass filter implemented by MOS-bipolar pseudo-resistor. The resistance could be controlled in different way as mention in sec. 2.2.1. In this work, the bandpass filter used a Pseudoresistor. The voltage output of the filter is converted to current by gm-cell. To have the lowest power possible, current SAR\_ADC is proposed. More details about the linearity of the gm is Chapter 4.

# 3 Low Pass Filter Circuit Design (First Stage)

In this chapter, the characteristics of the very low frequency filter is explained with all the design challenges. The circuit design of the filter and the OTA are introduced with the necessary simulations using CADANCE. Noise and power analysis and optimization are discussed as well.

# 3.1 Very Low Frequency filter & Sub-threshold Two Stage Miller Op Amp

Different filter topology is discussed with different implementations. Comparison between the different implementation is explained in order to meet the requirements of the system. The OTA implementation and characteristics are explained to meet the requirements of the filter. Different challenges such as leakage and noise optimization are discussed. The load calculation is computed to minimize the power consumption.

#### 3.1.1 Bandpass Filter Topology

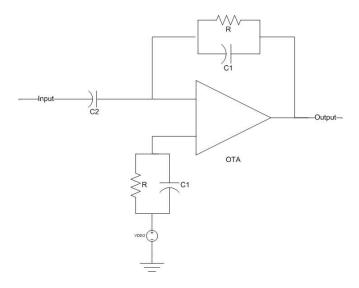

As decided in Chapter 2, the filter should be implemented by Pseudoresistor as show in Fig. 35[14]. The OTA is a two stage Op Amp with miller capasitor as show in Fig. 40.

Figure 35: Bandpass Filter Topology

The low cutoff frequency of the filter is implemented by Pseudoresistor in parallel with capacitor (C1) in feedback. The same configuration of Pseudoresistor and capacitor is placed in positive input of the filter in order to allow the rejection of expected DC potential differences [23].

The frequency response of the proposed filter is show in Fig. 36.

Figure 36: Gain vs Frequency for the Proposed Bandpass Filter

The gain is set to A=20dB. Therefore according to Equ. 20, C2=30pF,C1=3pF.

$$A(gain) = \frac{C_2}{C_1} \tag{20}$$

A larger value could be choosing to reduce the resistance required from the Pseudoresistor. However, a larger metal-insulator-metal capacitor, mimCap, consumes very large chip area. The reason to choose mimCap is explained in sec. 3.1.3. Therefore, the required resistance of the Pseudoresistor with low frequency cutoff of 20 mHz is equal to  $2.65 \text{T}\Omega$  according to Equ. 21. The 20 mHz is chosen to have safe margin and to compensate for any variations as stated in [27].

$$f_{low} = \frac{1}{2\pi CR - Pseudoresistor} \tag{21}$$

The high cutoff frequency set to be equal to 110Hz. The 110Hz is chosen to have safe margin and compensate for any variations as stated in [27]. The high cutoff frequency is calculated by Equ. 22

$$f_{high} = \frac{gm_1}{2\pi A C_{miller}} \tag{22}$$

High frequency cut off is function of the Miller Capacitor. In other design[14],  $f_{high} = \frac{gm_1}{2\pi A C_{Load}}$  is function of Cload which is varying depending of the load.

#### 3.1.2 MOS\_Pseudoresistor Element

MOS\_Pseudoresistor operate in deep triode region creating a small-signal resistance around  $1T\Omega$ . It does not only reduces the area comparing to an

actual R but also gives the chance for reconfigurable filter.

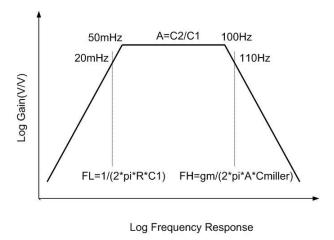

The MOS\_Pseudoresistor is implemented by different methods [22, 38, 21, 25, 20, 23, 14, 33, 26]. As the input changes the resistance changes. In other words, the pole of the filter is changing with the input. The resistance of Pseudoresistor is not linear. However, choosing the gain to be 20dB relaxing the linearity of the resistance as shown in Fig. 37. The magnitude of the ECG input is 5mV with gain of 20dB, the output is 50mV. On the other hand, if the gain is 40dB like most of the designs, the resistance would inter the non linear region which require different effort to linearized the pseudoresistor.

Figure 37: Comparison Between Simulated Resistances of Different MOS Pseudoresistor Designs

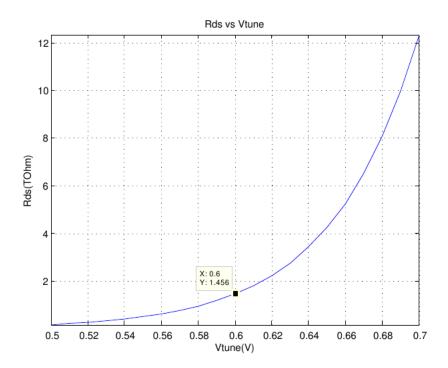

Controlling the Gate of the PMOS by voltages source gives the require resistance without any additional circuit technique. Resistance of the PMOS in weak inversion is calculated by [24].

$$rds \simeq \frac{L}{n C_{ox} W V_{th}} exp(-\frac{Vgs - V_T - n V_{th}}{n V_{th}})$$

(23)

where n is the sub threshold slope factor,  $V_T$  is the transistor threshold voltage,  $V_{th}$  is the thermal voltage. To maintain a high input impedance with the same Vtune, PMOS is chosen since hole mobility is one-half to one-fourth

that of the electron[9]. Two PMOS's in series is chosen to reduce distortion for large output signals[14].

Equ. 23 is plotted to know the value the voltage needed to obtain the required resistance (1.32T $\Omega$ ).

Figure 38: Rds vs Vtune for PMOS Pseudoresistor by Equ.23

As shown in Fig 38, Vtume=0.6V givies a resistance of  $1.456T\Omega$  Rds (Pseudoresistor) is chosen to be little bit higher in order to accommodate for any variations. The PMOS Pseudoresistor is simulated to check if the calculated value from Equ. 23 match the value of simulation as show in Fig. 39.

Figure 39: Rds vs Vtune for simulated PMOS Pseudoresistor

As shown in Fig. 39, as the voltage increased Rds increased which correspond to Equ. 23. The simulated value is  $1.907T\Omega$  which is relatively close the calculated value  $1.456T\Omega$ .

### 3.1.3 leakage Current(mimCap vs nCap & MOS\_Pseudoresistor)

There are two main sources of leakage in the filter design. The gain is set by the ratio of C2/C1. Higher value of capacitor could be implemented by NMOS connected like capacitor, nCap. However, the nCap has high value of leakage current[39]. For  $C_2$ , the leakage goes directly into the input stage. For  $C_1$ , the leakage goes through feedback into the input stage. The same scenario applied to the capacitor connected to the positive terminal. These leakages change the biasing of some of the transistors and change the biasing voltage at the output. For this design mimCap is used.

Second source if leakage is the gate leakage form MOS\_Pseudoresistor in order of 5fA. The leakage current goes through the feedback through the input because of the lower resistance. Then, the leakage current is amplified by second stage. Finally, the leakage comes to the output which will change the biasing voltage which change the frequency response of the filter. To solve this problem, a current buffer in inserted between the input stage and the current mirror to disassociate the voltage nodes. The functionality of the current buffer is explained in sec. 3.2. On the other hand, previous designs[20, 19, 26, 23, 14, 25, 24, 22, 21] have used large technology process which do not suffer from gate leakage.

### 3.2 OTA in Weak Inversion

In weak inversion saturation ID is independent from Vds and gm is function of ID as in Equ 24,25[10].

$$I_D = \frac{W}{L} I_{DO} \exp(\frac{qVgs}{nKT})$$

(24)

Where  $I_D$  is the drain current, W is width, L is length,  $I_{DO}$  is zero-bias current,  $V_T$  is thermal voltage, K is  $1.38 \cdot 10^{-23}$  J/K (Boltzmann's constant), q is  $1.60 \cdot 10^{-19}$  C (elementary charge), T is temperature, n is sub-threshold slope.

$$gm = \frac{I_D}{nKT/q} \tag{25}$$

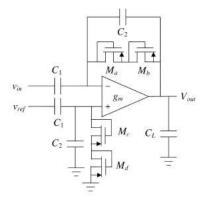

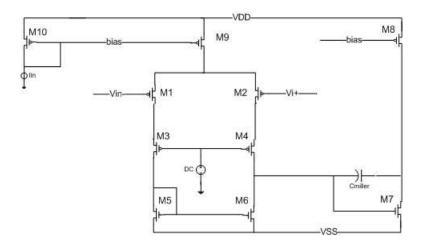

The circuit design of the OTA is show in Fig. 40. The OTA consists of two stages. The circuits operates in weak inversion with all the transistor in saturation(Vds>100mV).

Figure 40: Two Stage Miller Op Amp

PMOS input is chosen because it has lower flicker noise [9, 8]. PMOS has lower flicker noise because the channel is further in distance from the interface which is less affected by interface trap. M3-M4 creates current buffer-cascode which reduce the offset due to leakage and 2nd harmonic distortion. The value of the DC voltage connected to M3 and M4 is 70mV. The miller capacitor,14pF, is used to have more control over the high frequency filter since the gain bandwidth is function of Cmiller according to Equ. 26[40].

$$GB = \frac{I_{D1}}{(nKT/q)C_{Miller}}$$

(26)

## 3.3 Noise Analysis & NEF.

The input referred noise of the whole system depends on the noise of the front-end amplifier. Therefor, analyzing and optimizing the noise of the filter is very essential to reduce the noise of the overall system. Generally, having

Av=10=20dB, input-reference noise of the whole system could be roughly estimated by Equ. 27.

$$Input \, reference \, noise \, power = Power \, Noise_{Filter} + \frac{Power \, Noise_{gm}}{Av^2} + \frac{Power \, Noise_{ADC}}{gm^2 \, Av^2}$$

$$(27)$$

Where gm is the gm of the Gm block and Av is the gain. Setting Av(gain)=10, the second and third terms could be eliminated. Therefore, the input-reference noise is dominating by noise of the filter. The input referred thermal noise of the filter is given by Equ.28. The noise is simplified to be function of ID.

$$Vin = \sqrt{\frac{8K I_D \left(nKT/q\right)^2}{I_D^2}}$$

(28)

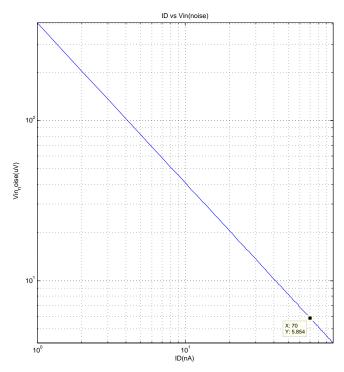

The current noise has to be taken into account as well. The higher the value of the input Capacitor(C2) the lower the current noise at the input. Equ. 28 is plotted to know the optimum point of current operation. As shown in Fig. 41, as the current increases, the noise decreases. However, the filter should be power limited. Choosing the power consumpation to be around 100nW and , gives a noise value around  $5.854\mu V$ .

Figure 41:  $I_D$  vs Input Voltage Noise of the Bandpass Filter from Equ. 28

Since the flicker noise is the dominate source of noise, Noise Efficiency Factor (NEF) is needed. NEF takes into account diffrent factor like BW and total current. The noise efficiency factor (NEF) is first introduced in [41].

$$NEF = V_{ni,rms} \sqrt{\frac{2 Itot}{\pi V_{th} 4KT BW}}$$

(29)

where Vni,rms is the input-referred rms noise voltage, Itot is the total amplifier supply current, and BW is the amplifier bandwidth in hertz. Ideally, NEF is equal to 1. However, in weak inversion more accurate model for shot noise is taken into account. The NEF is calculated by Equ. 30 [8].

$$NEF = \sqrt{\frac{4}{k}} \simeq 2.9 \tag{30}$$

Where I total=2 ID,  $\kappa$ , gate coupling coefficient, is typically equal to 0.7 . NEF=2.9 is the theoretical NEF limit for an amplifier, assuming current mirror ratios of unity. The noise bandwidth is very critical to determine the NEF. The input-reference noise could drastically decreases if the QRS bandwidth(50m~30Hz) is only filtered as in [19]. The input refer noise of this design is calculated differently than other designs. The output square noise voltage is divided by the square bandpass gain. Then, the result of division is integrated over bandwidth,50mHz~100Hz. The noise is calculated by Equ. 31.

$$Noise = \int \left(\frac{V_{Noise-Out}}{Av}\right)^2 \tag{31}$$

Where Av is the Bandpass gain. Noise of this design is 5.4  $\mu V$  and NEF=3.33 which is close to the theoretical limit 2.9.

### 3.4 Load Calculation

Calculating the require output current of the filter minimized the power consumption. Also, there should be enough current to drive the load (gm-Cell). In addition, having gm-cell after the amplifier would have lower Cload than ADC immediately after the filter. The filter characteristics is derived to calculate the require output current as in Equ. 32,33,34.

$$\frac{\text{Vo}}{\text{Vin}} = \frac{R \frac{1}{C_2 S}}{\frac{R + \frac{1}{C_2 S}}{\frac{1}{C_1 S}}} = -\frac{\frac{R}{1 + SRC_2}}{\frac{1}{C_1 S}}$$

(32)

$$|A(j\omega)| = \frac{RC_1\omega}{\sqrt{1+\omega^2R^2C_2^2}}$$

(33)

$$\mathbf{Iout} = \frac{\mathbf{V}_{\text{biasing}} \left(1 + \omega \,\mathbf{R} \,\mathbf{C}_2\right)}{R} \tag{34}$$

W=100Hz,R=2.65T $\Omega$ ,C=3pF and Vbiasing=0.5V  $\Longrightarrow$ Iout=0.3nA. However, Iout is chosen to be little bit higher to make sure that the load would have

sufficient current. M5 and M6, in Fig, 40, is optimized to deliver the required lout to reduce the power consumption.

## 3.5 Simulation Results

The sizing of the transistors is critical for achieving low noise, low power as mentioned before. The temperature is set to 37.0C, temperature of the human Body. The filter operates in weak inversion. The process technology used is  $0.13\mu m$ . The circuits is shown below in Fig. 42.

Figure 42: Bandpass Filter Circuit Design

The sizes of the transistors are giving below in Table. 7.

| Devices      | $M_1, M_2, M_3, M_4$ | $M_5,M_6$ | $M_7$ | $M_8$ | $M_{9}, M_{10}$ | $M_{11}, M_{12}$ | $M_{13}$ | $M_{14}$ |

|--------------|----------------------|-----------|-------|-------|-----------------|------------------|----------|----------|

| $W/L(\mu M)$ | 25/20                | 20/20     | 1/10  | 3/10  | 0.31/20         | 100/0.12         | 13/3     | 6/3      |

Table 4: Devices Sizes

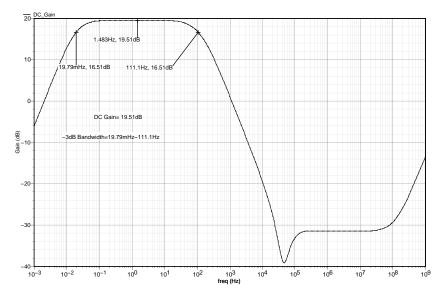

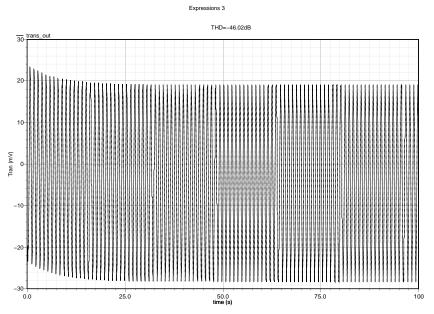

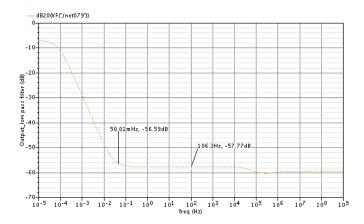

The frequency response, input referred thermal noise calculated by Equ. 31 and transient analysis at 2.5mV are simulated as shown in Fig. 43,44,45. From the simulations results, BW is 20m~111Hz and DC gain of 19.51dB. The noise which is simulated from 50mHz to 100Hz equals to  $5.4\mu V$ . The THD is 0.5%. The performance of the filter is in Table. 5. Also, a comparison between the different work is in Table. 12.

| Parameter                        | Simulation       |

|----------------------------------|------------------|

| $V_{DD}$                         | 1V               |

| $I_{Supply}$                     | 30n              |

| Gain                             | 19.51 dB         |

| BW                               | 20m~111Hz        |

| THD@ 2.5mV &2.23Hz*              | -46.02dB (0.5%)  |

| Input referred noise(50mH-100Hz) | $5.39\mu V$      |

| NEF                              | 3.3              |

| Power Consumption                | $108\mathrm{nW}$ |

<sup>\*</sup>Geometric mean of the BW.

Table 5: Simulated Performances of the Bandpass Filter

Expressions 1

Figure 43: Frequency Response of Bandpass Filter

The noise in Fig. 44, is simulated from  $50\mathrm{mH}$  to  $100\mathrm{Hz}$ .

User: salim Date: Mar 9, 2009 Time: 6:23:08 PM GMT+01:00

6 noise

100.5Hz, 5.482x1Q=6

100.5Hz, 5.482x1Q=

Figure 44: Input referred thermal noise of Bandpass Filter simulated from  $50 \mathrm{mHz}$  to  $100 \mathrm{Hz}$  and calculated by Equ. 31

User: salim Date: Mar 9, 2009 Time: 6:30:57 PM GMT+01:00

Figure 45: Transient analysis @2.5mV input and 2.23Hz Frequency input

The output signal starts to maintain constant value after 10 second. This behaviour caused by non zero derivative at the input step.

| Parameter                                      | Design in[14] | sign in[14] Design in[25] Design in[33] |                  | Design in[33]   | This work       |  |

|------------------------------------------------|---------------|-----------------------------------------|------------------|-----------------|-----------------|--|

| $V_{DD}(v)$                                    | ±2.5          | ±1.7                                    | 1                | 1               | 1               |  |

| Process Technology $(\mu m)$                   | 1.5           | 1.5                                     | 0.35             | 0.35            | 0.18            |  |

| Mid-band Gain(dB)                              | 39.5          | 39.3                                    | 40.2             | 45.6/49/53.5/60 | 19.51           |  |

| BW(Hz)                                         | 0.025~7.2K    | 0.015~4K                                | 0.003~245        | 0.05~262        | 20~111          |  |

| Input referred noise( $\mu V$ ) 2.2 (0.5~50kH) |               | 3.6 (20~10KHz)                          | 2.7 (0.05~250kH) | 2.5 (0.05~31Hz) | 5.39(0.05m~100) |  |

| NEF                                            | 4             | 4.9                                     | 3.8              | 3.26            | 3.3             |  |

| Power Consumption(W)                           | $80\mu$       | $27.2\mu$                               | 333n             | 104n            | 108n            |  |

Table 6: Performance Comparison between this work and recent works

From the Table. 12, this work has the smallest technology which means the highest gate leakage form the Pseudoresistor. However, it has similar noise to [19]. Although, the noise in [19] is  $2.5\mu V$  which is lower than this design. However, the noise bandwidth of [19] is less by a factor of 1/3 than this work.

The reduced bandwidth in [19] reduced the noise. Moreover, NEF is almost the same which is more accurate measure of the noise.

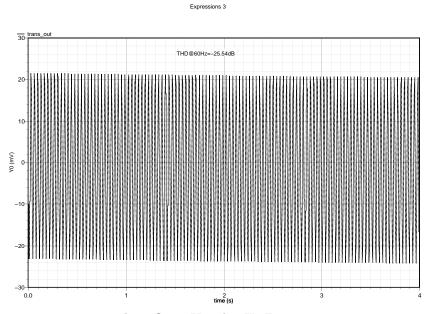

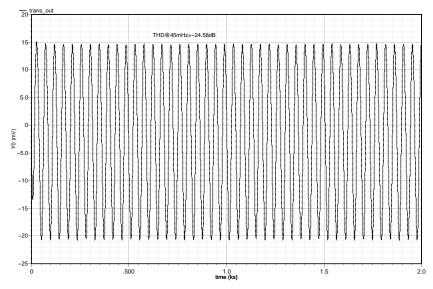

Also, the THD is simulated at the coroners of the frequency response of the filter. At 2.5 mV with frequency of 45 mHz and 60 Hz, the THD is 5.89% and 5.28% respectively. The main reason for the higher THD is the non linearity of the amplifier itself.

User: salim Date: Mar 9, 2009 Time: 6:41:20 PM GMT+01:00

Figure 46: Transient analysis @2.5mV and 60Hz Frequency input

Expressions 3

Figure 47: Transient analysis @2.5mV and 45mHz Frequency input

## 3.6 Conclusion

Bandpass filter is implemented using two Stage Miller Op Amp operating in weak inversion. The low cut-off frequency filter is implemented by pseudoresistor in parallel with capacitor. The high cut-off frequency is function of miller capacitor. The gain is set in way to relax the pseudoresistor and still maintain very low noise of the overall system. The gate leakage of the pseudoresistor is solved by current buffer. Metal-insulator-metal capacitor, mimCap, is chosen to set the gain and to eliminate the leakage and maintain a linear capacitance. The noise and power are optimized. The overall performance of the filter is very similar to the sate of the art design[19].

# 4 Gm-Current Cell (Second Stage)

In this chapter, the functionality of the Gm-cell is explained. The output current is calculated and simulated. Different linearization techniques are discussed to have general understanding of the trade-off.

## 4.1 Operational Transconductance Amplifier

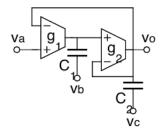

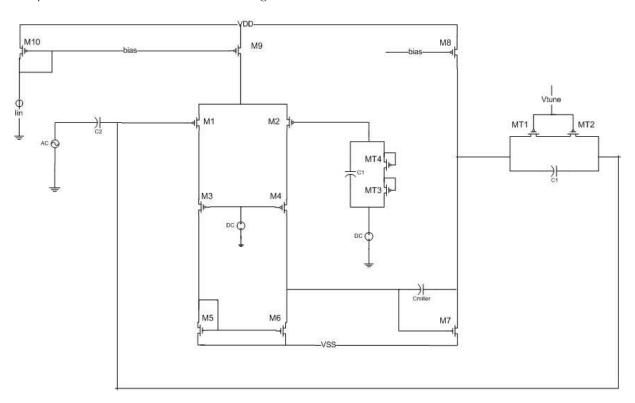

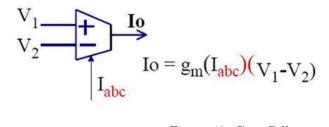

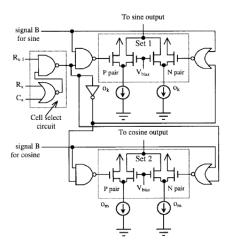

The output of the bandpass filter needs to be converted to current since current SAR ADC is used. Gm-cell is implemented as shown in Fig. 48[42, 43].

Figure 48: Gm Cell

The output current which is the full scale current input to the ADC would decides the power consumption of the current ADC as discussed. The relationship between power and full scale input current will be explained in Chapter 5. The input voltages has DC value of around 500.4mV. The amplitude of the input signal to the filter is 5mV. Then, with gain=20dB, the output is 50mV. Iout set to be 25.5nA depending on the reference current (100pA) in the current ADC. The value of the gm is calculated by Equ. 35 [13].

$$Iout = gm(V_1 - V_2) \tag{35}$$

Where Iout=25.5nA,  $V_1=550mV, V_2=500mV,$  then gm=0.51 $\mu A/V.$

The output of the filter is feed to the negative input of the gm and to the positive input through very low frequency filter as shown in Fig. 49. The low

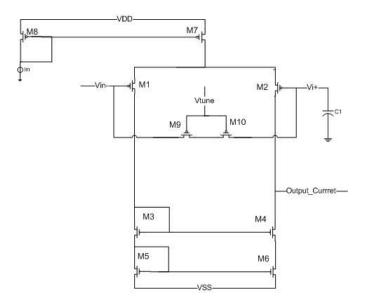

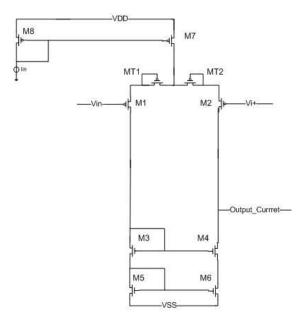

frequency filter is very similar to the one in the bandpass filter. The value of the resistance is increased to make sure that the DC component, 500.4m, is passed only. A cascode current mirror is implemented for OTA to make sure that all the transistor are in saturation and the current is mirrored accurately. The characteristic of the non linearity of the gm is hyperbolic tangent. There are different linearization techniques as discuss in sec.4.2.

Figure 49: Operational Transconductance Amplifier

The low pass frequency filter is implemented by M9,M10 AND C1. M9 and M10 are sized in way to produce the required resistance.

## 4.2 Cell Choice (linearization)

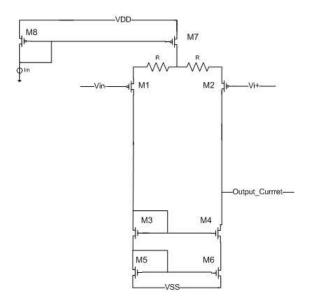

Several method of linitization is explained in [13, 44, 43]. Edgar mentioned three way of linearization.(a) attenuation, (b) nonlinear terms cancellation, and (c) source degeneration. Source degeneration is explained briefly here. Source degeneration transconductors using resistor to increase linearity. The resistor

are placed in the differential bair as shown in Fig. 50.

Figure 50: Fixed transconductor

According to Equ.37,36 to reduce the Gm, R has to be increased which leads current to increases to maintain higher loop gain and similar value of output current. The increase in current increases the power consumption[44]. However, to have ultra low power design, the gm should consume the lowest amount of power. In addition, even after adding the resistor, the gm would not be completely linear.

$$I = \frac{gm V}{1 + gm R} \tag{36}$$

$$Gm = \frac{gm}{1 + gm R} \tag{37}$$

For low noise design, the resistor would be implemented by CMOS connected diodes as shown in Fig. 51. The diodes would have voltage drop across them which reduces the linearity furthermore more.

Figure 51: Fixed Transconductors using CMOS connected diodes

Many other designs could linearize the gm. However, most of these designs would consume more power and would not have completely linear [13, 44, 42]. Simulation results of the source degeneration is provided in sec.4.3.

In this design, a conventional operational transconductance amplifier is used without any liniziation techniques in order to have the lowest power consumption of the gm-cell. The non linearity of the gm is compensated for by non linear current DAC.

### 4.3 Simulation Results

The temperature is set to 37.0C, temperature of the human Body. The gm-cell operates in weak inversion. The process technology used is  $0.13\mu m$ . For measurement purposes, a constant voltage is placed at the output to obtain the required current . The voltage scours has to keep equal voltage across the current mirror. Vconstant is calculated by Equ. 4.3.

$$V_{constant} = V ds_{3+} V ds_{5} (38)$$

The input voltage of the ADC is setting the output voltage of the Gm block. Input voltage of the ADC has to be supply the required voltage, Vconstan.

The sizes of the transistors are giving below in Table. 7. The sizes of the gm-cell is chosen to be close to the first stage of the OTA to minimize the noise. The total power consumption of the Gm-cell is 53.03nW.

| Devices      | $M_1,M_2$ | $M_3, M_4M_5, M_6$ | $M_7$ | $M_8$ | $C_3$    | $R_{filter}$ |

|--------------|-----------|--------------------|-------|-------|----------|--------------|

| $W/L(\mu M)$ | 80/20     | 40/20              | 6/3   | 7.6/6 | 3.056 pF | $3T\Omega$   |

Table 7: Devices Sizes

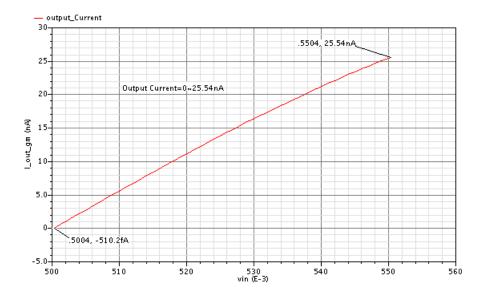

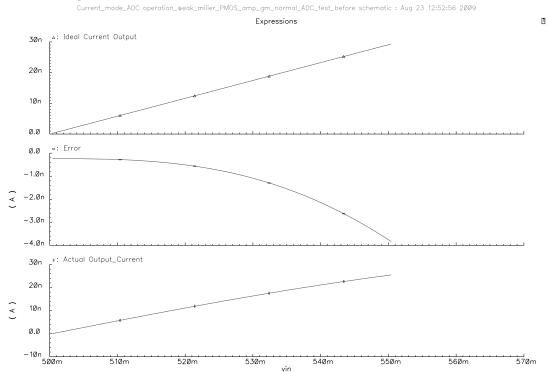

The DC output current of the gm is plotted in Fig. 52. The value of the current is  $\simeq 0\sim25.52$ nA as required. Since the sizes of the transistor is relatively big, the mismatch is minimized. As a result, the non linear current output maintain almost constant value with mismatched.

Figure 52: DC-Output Current

In Fig. 52, the LSB of the non linear output current is very close to linear current. The ideal output current is calculated by taking the derivative of the actual output current at biasing voltage of the filter. Then, the result of the derivative is multiplied by the full input voltage swing of the Gm block as in Equ. 39. Also, the difference between the actual output current and ideal current is calculated in Equ. 40.

$$Ideal\,Output\,Current = \left[\frac{dv}{dx}_{v=0.5}(Output\,Current) * Input\,Voltage\right] \quad (39)$$

$$Current Error = [Input Current - Ideal Output Current]$$

(40)

The ideal, actual and error current are plotted to understand the nature of the

## error as show in Fig. 53. The error is around 15%.

Figure 53: DC-Output Current with Error

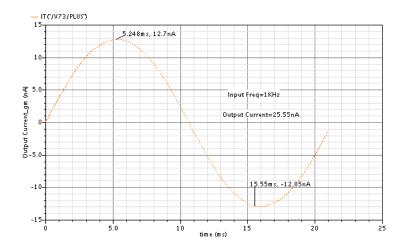

The gm block is tested with sine wave to check if the output current match the DC-output current as shown in Fig. 54. The Full scale of the current is 25.55nA which is very close the DC output current.

Figure 54: Sine wave\_Output Current

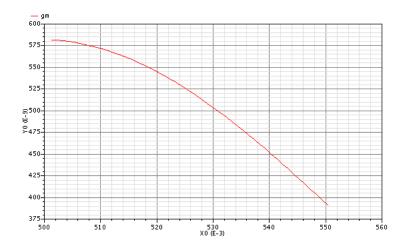

From Fig. 55, it is noticeable that the gm is not completely linear in the range of interest( $475\sim525$ mV).

Figure 55: gm of Gm block

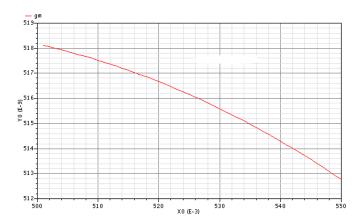

The frequency response of the filter in gm is plotted in Fig. 56. The  $50 \mathrm{mHz}$  is

attenuated by 56.6 dB in order to make sure that the DC component is passed only.

Figure 56: Frequency response of low frequency filter in gm Cell  $\,$

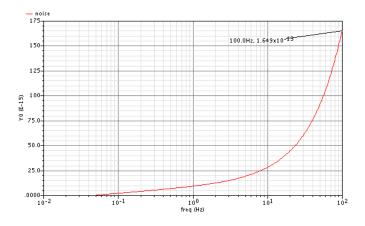

The noise of the gm-cell is simulated and refer to the filter input by Equ. 31 as shown in Fig. 57. The noise is negligible 164.9fV.

Figure 57: Noise of Gm from 50mHz to 100Hz calculated by Equ. 31

The performance of the non linear Gm block at Process Corner is listed in Table. 8.

| Process Corner | Full Scale Output Current(A) |

|----------------|------------------------------|

| TT             | 25.54n~-510.4f               |

| FF             | 25.15n~-219.6p               |

| SS             | 25.37n~133.8p                |

| FS             | 24.57n~-295.1p               |

| SF             | 26.46n~79.3p                 |

Table 8: Process Corner Simulations of Gm block

The full scale output current of FS and SF deviates the most form the full scale output current (25.54nA~510.4fA) at typical corner. The performance could be enhance by optimizing the circuit at these corner.

The gm of the source degeneration transconductors is shown in Fig. 50. The gm is more linear than the conventional gm. The power consumption is 195nW which is almost four time higher than the conventional gm. The high power consumption match the theory in Equ. 36. In addition, as shown in Fig. 58, the gm is not completely linear.

Figure 58: gm\_source degeneration transconductors

### 4.4 Conclusion

Gm-cell is implemented to convert the voltage output of the filter to a current. The value of the current is decided by the full scale current of the ADC. The output of the filter feed to the positive and negative input of the gm. A very low frequency filter is implemented to pass the DC component. Since the gm of the Gm-cell is not linear, different liberalization techniques is introduced in the literature. Source degeneration is investigated. This design is implementing conventional OTA without linearization techniques to reduce the power. The linearity is solve by non linear current DAC in the ADC.

# 5 Current Successive Approximation ADC (Third Stage)

In this chapter, The architecture of the SAR ADC is presented with the different design aspects. Each block of the ADC (comparator, SAR register and DAC) are explained with simulations results. Statics and dynamics performance of the ADC are presented with Monte Carlo simulations.

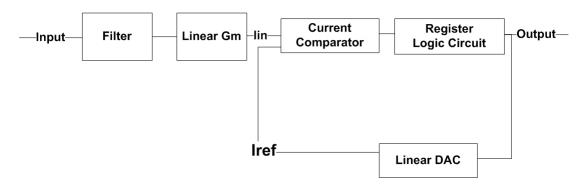

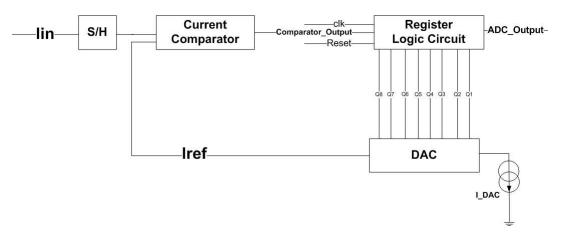

## 5.1 8 bit SAR\_ADC Architecture

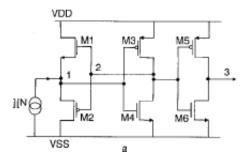

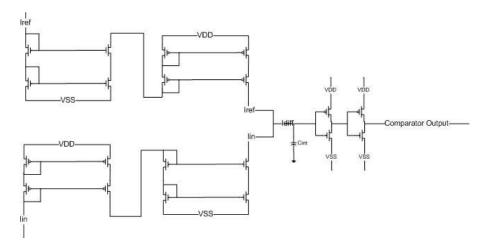

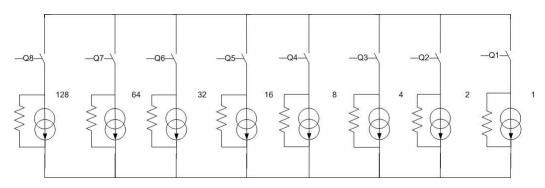

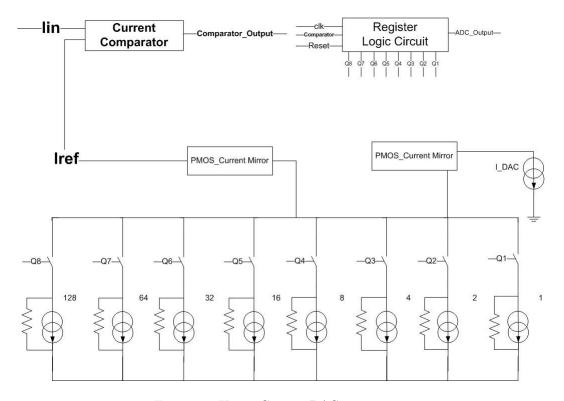

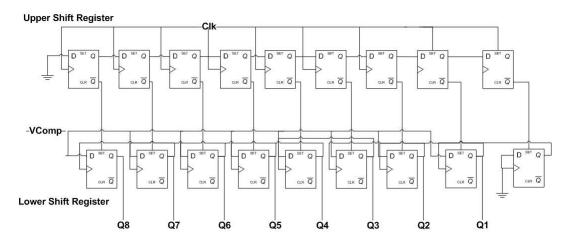

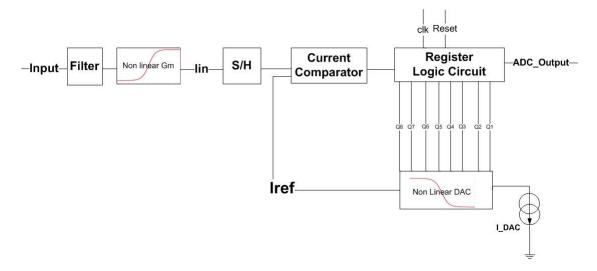

As stated in Chapter 2, there are only two previous design of current SAR[37, 35]. In this design, a 8 bit with 1KS/s current SAR ADC consists of current sample and hold, current comparator, current DAC, register logic circuit and current mirrors. An system level design is shown below Fig. 59.

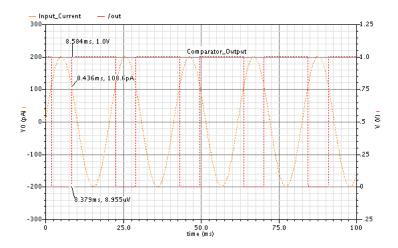

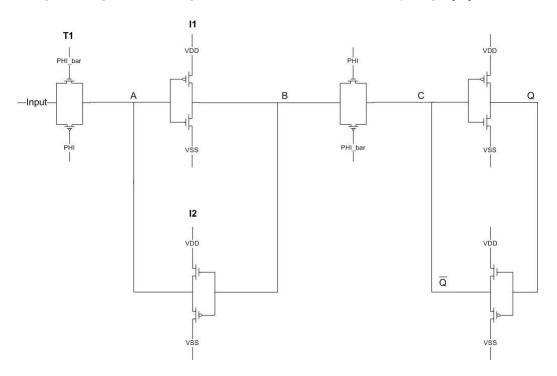

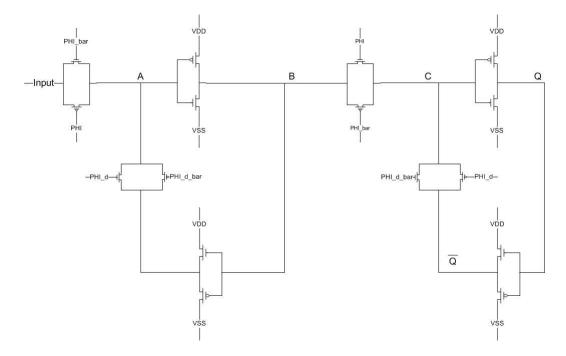

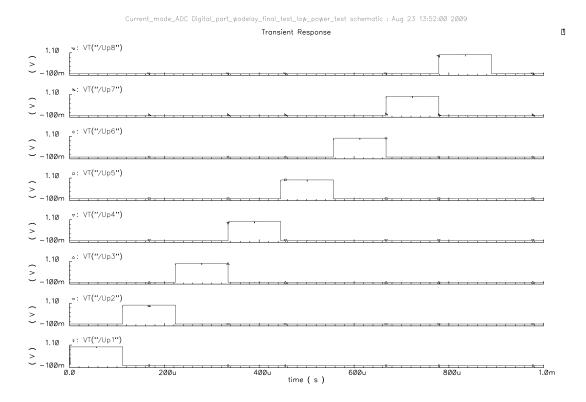

Figure 59: SAR Architecture