### A load-modulation digital data link for miniature ultrasound probes

by

Mengxin Yu

November 28, 2019

to obtain the degree of Master of Science in Microelectronics at the Delft University of Technology,

Student number:4749006Thesis committee:Dr.ir. Michiel PertijsElectronic Instrumentation Laboratory, TU DelftDr. Fabio SebastianoDr.ir. Andre BosscheElectronic Instrumentation Laboratory, TU DelftDr. Taehoon KimElectronic Instrumentation Laboratory, TU Delft

### ABSTRACT

Miniature ultrasound probes, such as intravascular ultrasound (IVUS) probes, are valuable diagnostic tools and provide image guidance during minimallyinvasive interventions. As more ultrasound transducer elements are built into such probes to improve image quality and frame rate, it becomes increasingly difficult to accommodate the cables needed to connect these elements to an imaging system. Among several reported cable-count reduction approaches, in-probe digitization of the received echo signals is a promising solution, as it allows digital data-link techniques to be leveraged to minimize cable count.

This work takes a previously-developed application-specific integrated circuit (ASIC) for an IVUS probe as a starting point. This ASIC employs a load-modulation datalink to transmit digitized echo signals of one element via a single micro-coaxial cable at o.6 Gb/s. This thesis extends this work to multi-bit per-symbol signalling to increase the data rate, allowing the echo signals of multiple elements to be combined into one cable. First, the measured performance of the existing ASIC is compared to simulation results, showing the need for an S-parameter based cable model to faithfully reproduce the measured performance. Based on this simulation model, load modulation with a maximum of three bits per symbol and a maximum symbol rate of 600 MHz is investigated. The trade-off between data-transmission conditions and bit-error rate is investigated and gives a general idea about how fast the data rate can be.

An experimental setup is proposed to experimentally validate the performance of multi-bit load-modulation data links. For this, a prototype chip has been designed that includes a multi-bit load-modulation circuit and interfaces with an FPGA that provides test data. The chip has been taped out in a TSMC 0.18 um HV CMOS technology. Post-layout simulation shows that the prototype is able to generate a data rate of 1.6 Gb/s when there are two bits per symbol at the symbol rate of 800 MHz. Compared to the 0.6 Gb/s of the previous design, this is a substantially higher data rate.

Keywords: Intravascular ultrasound, one cable, load modulation, data rate.

### ACKNOWLEDGEMENTS

I am deeply grateful to all the people I have met over the past two years. This work could not have been done without their help and support.

I am grateful to my supervisor, Dr.ir. Michiel Pertijs for his patience, guidance and help. I have learned a lot from him about the way of analyzing and the serious working attitude. I would like to thank him for the great effort he has made to help me find a way out and head for design. Also, I would like to thank him for helping me debugging just before the tape-out. His kindness and patience really has provided me a lot of help to go through the tough year.

Next, I would like to thank my daily supervisor, Taehoon Kim, for his continuous help and encouragement in the past year. Every time I came into trouble, he always shared with me his knowledge. Also, his support and understanding really made me get out of mentally trouble a lot.

Also, I would like to thank Zhao, Mingliang, Douwe, Jae-Sung, Yannick, Peng and Eunchul, who have given me support and valuable support over the past few years. It was so nice that everyone was willing to share their experience and wish to discuss with me.

I am grateful to Zu-Yao, a kind technician in this group for his support in Cadence. The breakdown of Cadence really drove me crazy and it was Zu-Yao who always gave me help quickly and made simulation possible.

I would like to express my thank to Joyce as well. Her organization of group events really made me have some good memories in some stressing periods.

I would like to thank all the master students in EI group, Miao, Daguang, Qiyou, Xianglong, Arvind, Shardul, Matheus, Efraim and Rishabh. It was a nice time to support each other and work on challenging projects together.

I am lucky to have met a lot of nice friends in Delft over the last two years, Mengya, Zhen, Yuxuan, Jingchun, Chongchong and Shiyu. The time with you has been the most precious here. Your support and encouragement made me keep going.

Special thanks belong to my parents, who have always supported and believed me over the past 24 years. No matter how terrible I am, they are always willing to stand by me and encourage me. It is really nice to have them in my life and hope that someday, they can be proud of me.

Mengxin Yu Delft, November 2019

### CONTENTS

| 1 | INTE | RODUCTION 1                                                     |

|---|------|-----------------------------------------------------------------|

|   | 1.1  | Background                                                      |

|   | 1.2  | Prior Art                                                       |

|   | 1.3  | Motivation                                                      |

|   | 1.4  | Design Objectives                                               |

|   | 1.5  | Thesis Organization                                             |

| 2 | CAB  | LE-COUNT REDUCTION TECHNIQUES 7                                 |

|   | 2.1  | Analog Cable-Count Reduction                                    |

|   |      | 2.1.1 Beamforming                                               |

|   |      | 2.1.2 Frequency-division Multiplexing                           |

|   |      | 2.1.3 Time-multiplexing                                         |

|   | 2.2  | Digital Cable-Count Reduction                                   |

|   | 2.3  | Digital Data Link Techniques                                    |

| 3 | EXIS | STING ASIC WITH LOAD-MODULATION DATA LINK 17                    |

|   | 3.1  | Introduction to Existing ASIC with Load-modulation Data Link 18 |

|   | 3.2  | Measurement of Existing ASIC with Load-modulation Data          |

|   |      | Link                                                            |

|   | 3.3  | RLCG Cable Model         22                                     |

|   | 3.4  | S parameter-based Cable Model                                   |

| 4 | EXP  | ERIMENTAL SETUP FOR EVALUATION OF LOAD-MODULATION 27            |

|   | 4.1  | Choice of Cable                                                 |

|   | 4.2  | Analysis of Load-modulation Data Link                           |

|   |      | 4.2.1 Single-bit per Symbol                                     |

|   |      | 4.2.2 Two-bit per Symbol                                        |

|   |      | 4.2.3 Three-bit per Symbol                                      |

|   | 4.3  | Complete Architecture with Load-modulation Data Link 37         |

|   | 4.4  | Load-modulation Data Link with Multi-bit per Symbol Sig-        |

|   |      | nalling                                                         |

| 5 | LOA  | D-MODULATION TEST ASIC 41                                       |

|   | 5.1  | System Description                                              |

|   | 5.2  | Load Modulation                                                 |

|   |      | 5.2.1 Thermometer Coding 43                                     |

|   |      | 5.2.2 Resistive Degeneration                                    |

|   |      | 5.2.3 Die Area Optimization                                     |

|   | 5.3  | Data-rate Doubling                                              |

|   |      | 5.3.1 Ideal Data-rate Doubling Circuit                          |

|   |      | 5.3.2 Overlapping Clock                                         |

|   |      | 5.3.3 Synchronization                                           |

|   |      | 5.3.4 Delay Cell                                                |

|   | 5.4  | Layout                                                          |

| 6 |      | ULTS AND CONCLUSIONS 57                                         |

|   | 6.1  | Post-layout simulation                                          |

|   |      | 6.1.1 3-bit per symbol signalling                               |

|   |      | 6.1.2 2-bit per symbol signalling                               |

|     | 6.1.3  | 1-bit per symbol signalling 6 | 4 |

|-----|--------|-------------------------------|---|

|     | 6.1.4  | Return-to-zero Transmission   | 5 |

| 6.2 | Concl  | usion                         | 6 |

| 6.3 | Future | e work                        | 7 |

### LIST OF FIGURES

| Figure 1.1  | Normal and partly blocked blood vessel                          | 2  |

|-------------|-----------------------------------------------------------------|----|

| Figure 1.2  | Timing diagram of a typical transmit and receive cycle          | 2  |

| Figure 1.3  | Illustration of 1D array and 2D array                           | 3  |

| Figure 1.4  | One example of the block diagram of the IVUS imag-              |    |

|             | ing system with more cables for transmission                    | 4  |

| Figure 1.5  | One example of the block diagram of the IVUS imag-              |    |

|             | ing system with four cables for transmission $\ldots$ .         | 4  |

| Figure 2.1  | Simple signal transmission through coaxial cable                | 8  |

| Figure 2.2  | Signal transmission through coaxial cable                       | 8  |

| Figure 2.3  | Signal transmission for multiple signals                        | 9  |

| Figure 2.4  | Signal processing architecture with beamforming for             |    |

|             | ultrasound imaging system                                       | 10 |

| Figure 2.5  | Block diagram of analog orthogonal frequency-division           |    |

|             | multiplexing                                                    | 11 |

| Figure 2.6  | Block diagram of a time-multiplexing system                     | 12 |

| Figure 2.7  | Architecture of receive electronics with digitization           | 13 |

| Figure 2.8  | A block diagram of a data link with serialization               | 14 |

| Figure 2.9  | A block diagram of a data link with load modulation .           | 14 |

| Figure 3.1  | The block diagram of an IVUS imaging system with                |    |

|             | load-modulation data link                                       | 18 |

| Figure 3.2  | Circuit diagrams of (a) clock and data recovery; (b)            |    |

|             | the continuous-time comparator; (c) associated time             |    |

|             | diagram                                                         | 19 |

| Figure 3.3  | Timing diagram of the comparator                                | 19 |

| Figure 3.4  | Block diagram and waveforms of the load modulation              |    |

|             | data link                                                       | 20 |

| Figure 3.5  | Measured waveform of the existing ASIC                          | 21 |

| Figure 3.6  | Illustration of equivalent impedance                            | 21 |

| Figure 3.7  | Waveform of (a) chip side of normal measurement (b)             |    |

| <b>T!</b> 0 | system side of normal measurement                               | 22 |

| Figure 3.8  | Simplified system for simulation                                | 23 |

| Figure 3.9  | Control signals generated with Verilog A model                  | 23 |

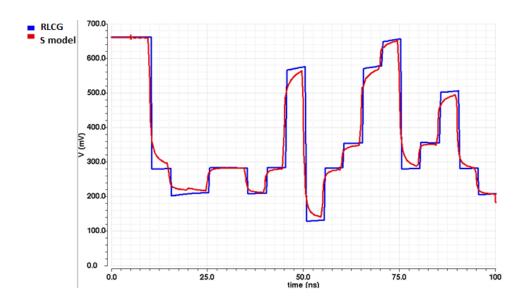

| Figure 3.10 | Corresponding waveforms at <i>Vin</i> and <i>Vout</i> for RLCG  |    |

| <b>T</b> .  | model                                                           | 24 |

| Figure 3.11 | Corresponding waveforms at <i>Vin</i> and <i>Vout</i> for S pa- |    |

| <b>T</b> '  | rameter model                                                   | 25 |

| Figure 3.12 | Corresponding $V_{out}$ for 1m and 2m cable                     | 25 |

| Figure 4.1  | $S_{12}$ of four types of cables                                | 28 |

| Figure 4.2  | Schematic of 2-bit per symbol transmission with an              |    |

| <b>F</b> :  | interval of 80 mV                                               | 29 |

| Figure 4.3  | Output waveforms of AWG 48 and AWG 42 at the                    |    |

|             | symbol rate of 500 MHz                                          | 29 |

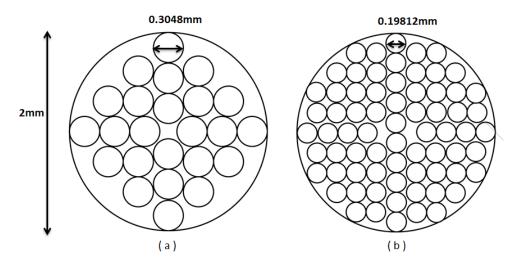

| Figure 4.4  | Illustration of (a) AWG 42 and (b) AWG 46 or AWG 48 accommodated in a catheter with a 2-mm diameter 31                                                                                                                                                           |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.5  | Schematic of 1-bit per symbol transmission with an                                                                                                                                                                                                               |

| Figure 4.6  | Output waveform at the symbol rate of 600 MHz for                                                                                                                                                                                                                |

| rigure 4.0  | 1-bit per symbol transmission                                                                                                                                                                                                                                    |

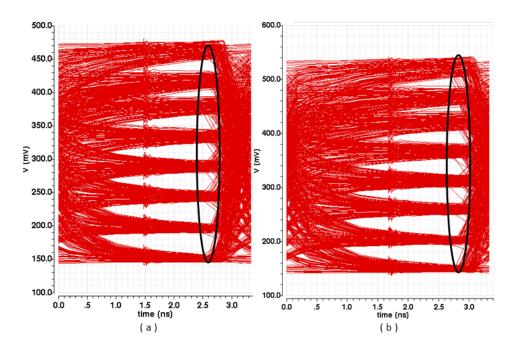

| Figure 4.7  | Eye diagram at symbol rate of (a) 200 MHz (b) 600                                                                                                                                                                                                                |

| 0 17        | MHz and (c) 1.2 GHz                                                                                                                                                                                                                                              |

| Figure 4.8  | Output waveforms from an S parameter-based model<br>and a RLCG-based model for 2-bit per symbol at the<br>symbol rate of 500MHz                                                                                                                                  |

| Figure 4.9  | Schematic of 2-bit per symbol transmission with an interval of 50 mV                                                                                                                                                                                             |

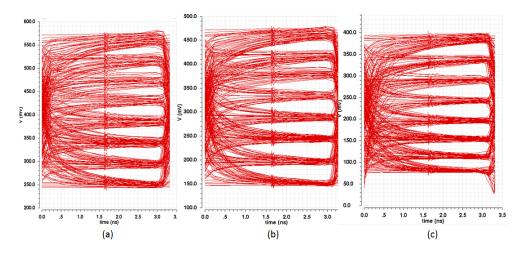

| Figure 4.10 | Eye diagram at the symbol rate of (a) 200 MHz with a 50 mV interval (b) 300 MHz with a 50 mV interval (c) 600 MHz with a 50 mV interval (d) 200 MHz with an 80 mV interval (e) 300 MHz with an 80 mV interval and (f) 600 MHz with an 80 mV interval for a 2-bit |

|             | per symbol signalling                                                                                                                                                                                                                                            |

| Figure 4.11 | Schematic of 3-bit per symbol transmission with an interval of 80 mV                                                                                                                                                                                             |

| Figure 4.12 | Output waveforms with S parameter model and RLCG model for 3-bit per symbol at the symbol rate of 200MHz 36                                                                                                                                                      |

| Figure 4.13 | Eye Diagram of a 3-bit per symbol signalling with an interval of 80 mV at the symbol rate of (a) 200 MHz and (b) 300 MHz                                                                                                                                         |

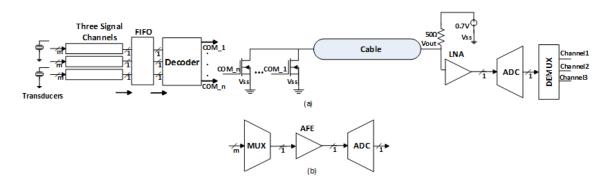

| Figure 4.14 | (a) A complete system architecture with load-modulation data link (b) A block diagram of a signal channel 38                                                                                                                                                     |

| Figure 4.15 | Architecture of a load-modulation data link with multi-                                                                                                                                                                                                          |

| 0 1 9       | bit per symbol signalling 38                                                                                                                                                                                                                                     |

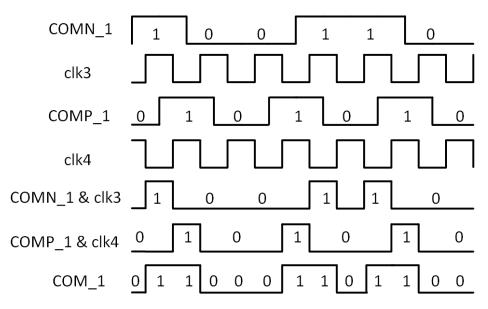

| Figure 4.16 | Timing diagram of data-rate doubling                                                                                                                                                                                                                             |

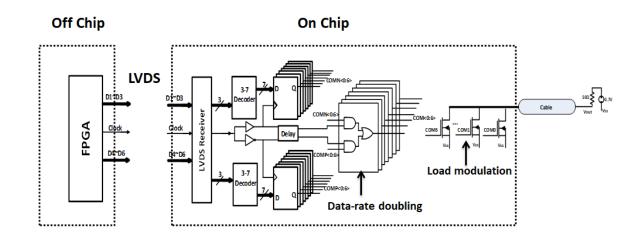

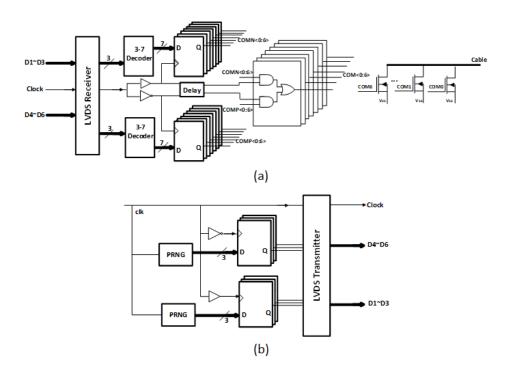

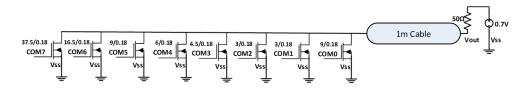

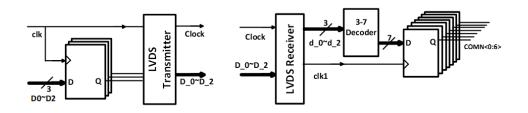

| Figure 5.1  | A block diagram of (a) the on-chip circuitry and (b)                                                                                                                                                                                                             |

| <b>T</b> '  | the FPGA                                                                                                                                                                                                                                                         |

| Figure 5.2  | Schematic of 3-bit per symbol transmission with ther-<br>mometer coding                                                                                                                                                                                          |

| Figure 5.3  | Schematic of 3-bit per symbol transmission with one-                                                                                                                                                                                                             |

|             | hot coding 44                                                                                                                                                                                                                                                    |

| Figure 5.4  | <i>V<sub>out</sub></i> of schematics with one-hot coding and thermome-                                                                                                                                                                                           |

|             | ter coding at the symbol rate of 333 MHz 45                                                                                                                                                                                                                      |

| Figure 5.5  | <ul><li>(a) Gate driver for one-hot coding structure data link</li><li>(b) Gate driver for thermometer coding structure data</li><li>link</li></ul>                                                                                                              |

| Figure 5.6  | <ul><li>(a) Driving signals of transistors with one-hot coding</li><li>(b) Driving signals of transistors with thermometer</li></ul>                                                                                                                             |

|             | coding                                                                                                                                                                                                                                                           |

| Figure 5.7  | Schematic of a 3-bit signalling with resistive degener-<br>ation                                                                                                                                                                                                 |

| Figure 5.8    | Eye diagram of schematics with an interval of (a) 40 mV (b) 50 mV (c) 60 mV and (c) 70 mV at the symbol |

|---------------|---------------------------------------------------------------------------------------------------------|

|               | rate of 250 MHz                                                                                         |

| Figure 5.9    | Eye diagram of schematics with an interval of (a) 50                                                    |

| 0 57          | mV and (b) 60 mV at the symbol rate of 300 MHz 49                                                       |

| Figure 5.10   | Eye diagram of schematics with levels (a) in the upper                                                  |

| 0 5           | side (b) in the middle and (c) in the lower side at the                                                 |

|               | symbol rate of 300 MHz                                                                                  |

| Figure 5.11   | Implementation of a load-modulation data link with                                                      |

| 0 0           | an interval of 50 mV                                                                                    |

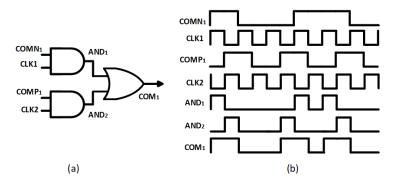

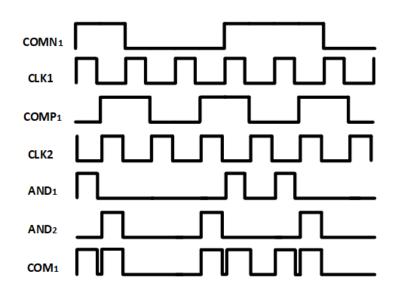

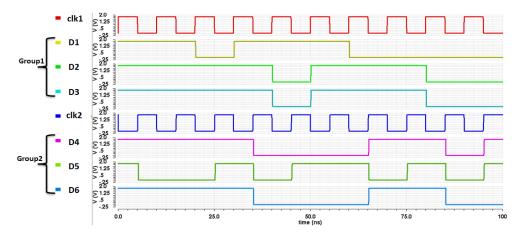

| Figure 5.12   | (a) Logic cells of data-rate doubling and (b) Timing                                                    |

|               | diagram of data-rate doubling                                                                           |

| Figure 5.13   | Timing diagram of data-rate doubling with non-overlapping                                               |

|               | clocks                                                                                                  |

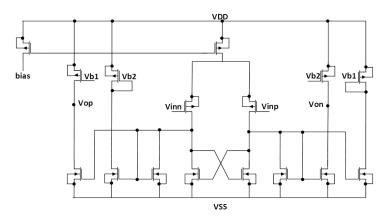

| Figure 5.14   | Circuit of LVDS receiver                                                                                |

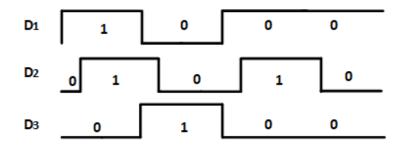

| Figure 5.15   | Three data streams with some delay at the input of                                                      |

|               | 3-7 decoder                                                                                             |

| Figure 5.16   | A synchronization structure                                                                             |

| Figure 5.17   | Inputs of FlipFlop                                                                                      |

| Figure 5.18   | Timing diagram of clocks with delay                                                                     |

| Figure 5.19   | Timing diagram of a clock with delay over $\frac{1}{2}t$ 54                                             |

| Figure 5.20   | Clock without a delay cell and clock with a delay cell . 55                                             |

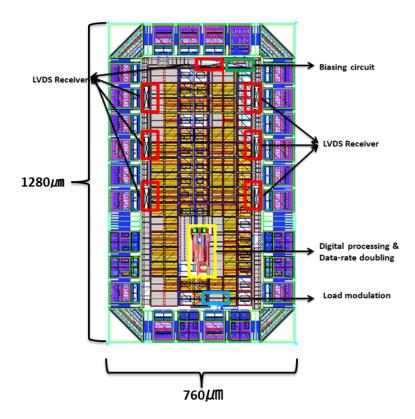

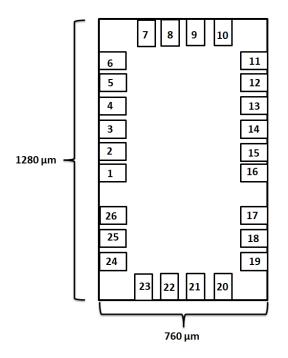

| Figure 5.21   | Layout diagram                                                                                          |

| Figure 5.22   | Pad ring arrangement 56                                                                                 |

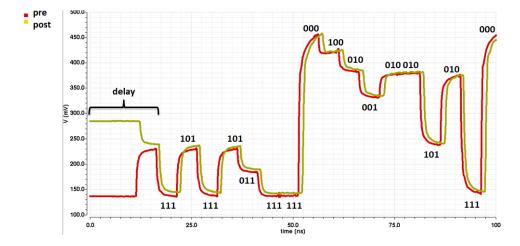

| Figure 6.1    | Random number generation                                                                                |

| Figure 6.2    | Comparison between pre-layout and post-layout sim-                                                      |

|               | ulation at the symbol rate of 200 MHz 59                                                                |

| Figure 6.3    | Eye diagram of 3-bit signalling at the symbol rate of                                                   |

|               | 200 MHz                                                                                                 |

| Figure 6.4    | Eye diagram of 2-bit signalling at the symbol rate of                                                   |

|               | 300 MHz with a 50 mV interval                                                                           |

| Figure 6.5    | Eye diagram of 2-bit signalling at the symbol rate of                                                   |

|               | 800 MHz with a 50 mV interval                                                                           |

| Figure 6.6    | Eye diagram of 2-bit signalling at the symbol rate of                                                   |

|               | (a) 300 MHz and (b) 800 MHz with an 100 mV interval 63                                                  |

| Figure 6.7    | Eye diagram of 1-bit signalling at the symbol rate of                                                   |

| <b>T'</b> ( 0 | 600 MHz                                                                                                 |

| Figure 6.8    | One example eye diagram of 2-bit RTZ transmission                                                       |

| <b>F</b> '    | at the symbol rate of 600 MHz                                                                           |

| Figure 6.9    | Eye diagram of 2-bit NRZ transmission at the symbol $r_{1}$                                             |

|               | rate of (a) 300 MHz and (b) 600 MHz 66                                                                  |

### LIST OF TABLES

| Table 3.1 | 42 AWG coaxial cable parameters                                  | 23 |

|-----------|------------------------------------------------------------------|----|

| Table 3.2 | Voltage change comparison between RLCG model and                 | -  |

|           | measurement                                                      | 24 |

| Table 3.3 | Voltage change comparison between two models and                 |    |

|           | measurement                                                      | 25 |

| Table 4.1 | Thermometer coding for 2-bit per symbol transmission             | 30 |

| Table 4.2 | Diameters of different cables                                    | 30 |

| Table 4.3 | Comparison of $V_{range}$ and $V_{interval}$ at different symbol | -  |

|           | rates with the interval of 80 mV                                 | 33 |

| Table 4.4 | Comparison of $V_{range}$ and $V_{interval}$ at different symbol |    |

|           | rates                                                            | 35 |

| Table 4.5 | Thermometer coding for 3-bit per symbol transmission             | 35 |

| Table 5.1 | One example of thermometer coding with seven con-                |    |

|           | trol signals                                                     | 43 |

| Table 5.2 | One-hot coding for 3-bit per symbol transmission                 | 44 |

| Table 5.3 | Comparison of voltage levels at 800 mV supply volt-              |    |

|           | age                                                              | 47 |

| Table 5.4 | Comparison of intervals between expected situations              |    |

|           | and real situations                                              | 49 |

| Table 5.5 | Descriptions of pads                                             | 56 |

| Table 6.1 | Input code and their corresponding voltage values for            |    |

|           | 3-bit per symbol signalling                                      | 59 |

| Table 6.2 | BER at several symbol rates for 3-bit per symbol sig-            |    |

|           | nalling                                                          | 60 |

| Table 6.3 | Power consumption distribution at several symbol rates           |    |

|           | for 3-bit per symbol signalling                                  | 60 |

| Table 6.4 | Input code and their corresponding voltage values for            |    |

|           | 2-bit per symbol signalling                                      | 61 |

| Table 6.5 | Power consumption distribution at several symbol rates           |    |

|           | for 2-bit per symbol signalling                                  | 62 |

| Table 6.6 | Power consumption at several symbol rates with dif-              |    |

|           | ferent intervals                                                 | 63 |

| Table 6.7 | Input data and their corresponding voltage values for            |    |

|           | 1-bit per symbol signalling                                      | 64 |

| Table 6.8 | Power consumption distribution at several data rates             |    |

|           | for one-bit per symbol signalling                                | 65 |

| Table 6.9 | Power consumption at different data rates for differ-            |    |

|           | ent bits per symbol                                              | 67 |

# 1 INTRODUCTION

#### 1.1 BACKGROUND

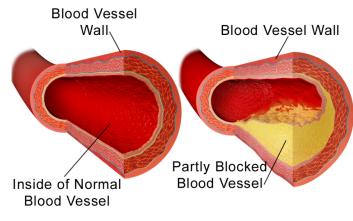

Intravascular ultrasound (IVUS) imaging has played an important role in understanding atherosclerotic diseases in human beings [1]. It helps acquire an image of the vascular wall in Figure 1.1 and atherosclerotic plaques, which makes it easier for doctors to understand the atherosclerosis process and thus decide the proper treatment [2].

Figure 1.1: Normal and partly blocked blood vessel[2]

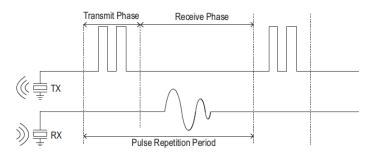

IVUS technology utilizes a miniature ultrasonic transducer at the tip of a catheter that is sent into the coronary arteries [3][4][5]. The transducers here are responsible for the pulse-echo measurement and can be divided into two categories by function: transmit and receive. Its timing diagram can be described in Figure 1.2. First, the transducers can be excited by electrical signals. At the same time, it converts these electrical signals to mechanical vibrations, during which the ultrasound waves are generated in transmit mode. Then, these ultrasound waves can be transmitted to target tissues and reflected inside the body. The echo signals can be reflected back to transducers where detectable electrical signals are generated. After that, these signals will be transmitted through a cable in the catheter to the imaging system where the imaging information will be transferred.

Figure 1.2: Timing diagram of a typical transmit and receive cycle [6]

Over the past few years, many efforts have been applied to acquire a more complete image of the blockage of the vessel in front of the catheter tip. Among them, there are two approaches to 3D imaging. On one hand, a mechanically-rotating single-element transducer is applied [7][8]. During

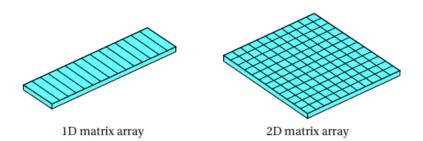

the working period, the transducer is excited at different angles to acquire the image information at the corresponding point respectively. However, it is hard to implement because it is highly dependent on a reliable rotating system. Also, it is expensive in manufacturing and slow in speed. On the other hand, the catheter can employ a transducer array at the tip of it [9]. In this case, several transducers can be excited at the same time and due to the array placement 1.3, image information at several points can be acquired at the same time. With the fixed transducers, the image can be more accurate, more time-saving and less expensive. Also, it eliminates the use of the rotation system. However, although the catheter-based IVUS ultrasound imaging has many advantages in terms of image integrity, the cable count remains a problem because of the catheter diameter limitation.

Figure 1.3: Illustration of 1D array and 2D array [10]

Also, for this catheter-based system, there is a need for a higher frame rate, especially during the surgeries. With an increased frame rate, more real-time imaging would be possible, which helps doctors conduct the surgery more precisely and reduces motion artifacts [11].

### 1.2 PRIOR ART

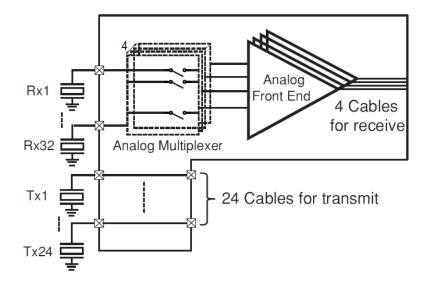

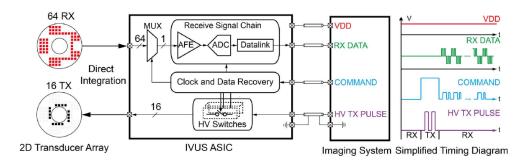

As mentioned above, transducer-array based IVUS imaging systems have the advantages that they eliminate the rotating system and are comparatively cheaper, which makes them popular among research. Several systems have been proposed in [12][13] already and some products are on the market, such as the Philips Eagle Eye Platinum digital IVUS catheter [14]. Shown in Figure 1.4, a block diagram of an example IVUS imaging system is presented [15].

In this system, there are 32 transducers for receive and 24 transducers for transmit both in an annular placement. Each transmit element is connected to a cable while the 32 receive elements are divided into four groups and then connected to four 8-1 multiplexers and buffer amplifiers. With a transimpedance amplifier in the signal channel, the information is transmitted in an analog way through the cable. Thus, in this system, there are 24 cables for transmit, 4 cables for receive and some additional cables responsible for the power supply and control signals. In terms of further miniaturization

Figure 1.4: One example of the block diagram of the IVUS imaging system with more cables for transmission [15]

and cost reduction, cable-count reduction is desirable.

Figure 1.5: One example of the block diagram of the IVUS imaging system with four cables for transmission[16]

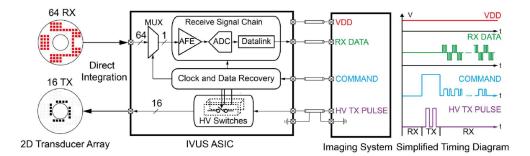

To make it more suitable for IVUS application, several efforts have been applied to further reduce the number of cables in the IVUS imaging system. In [16], only four cables are applied. As shown in Figure1.5, there are 64 receive elements and 16 transmit elements. For the transmit elements, instead of connecting to the cables respectively, all the transducers are connected in a multiplexed fashion to one cable and driven by a pulser on the system side. Additionally, a 64-1 multiplexer is applied to interface with the 64 receive elements rather than 8-1 multiplexers. With only one signal channel, it digitizes the signal first and sends the digitized signal to the system by load modulation. It helps achieve an effective data rate of 600 Mb/s. Also, with a modulation scheme, only one cable takes responsibility for digital signals controls.

Although the cable count is much reduced to 4, the 64-1 analog multiplexer does reduce the frame rate a lot. Acoustic pulses are transmitted using 16 TX elements and 64 RX elements receive their echo signals and digitize them

in 64 successive pulse-echo sequences. Thus, the total of 1024 ( $16 \times 64$ ) pulse-echo cycles are needed for a full synthetic-aperture image.

### 1.3 MOTIVATION

In terms of the limited catheter diameter in practical applications, it is necessary to reduce the cable count in IVUS ultrasound imaging systems. Although the cable count is successfully reduced to 4 [16], it utilizes an analog 64-1 multiplexer followed by only one signal channel. It is time-consuming to process the signal and transmit the data one by one, which limits its frame rate.

To reduce the cable count and make the system more real-time, the goal of this thesis is to further increase the data rate with only 4 cables. Additionally, in terms of its application in diagnosis and treatment, signals acquired at the system side should be decoded to represent the origin information accurately. Bit error rate (BER) can be introduced to describe its data accuracy.

Furthermore, although more emphasis is on IVUS imaging systems, cablecount reduction techniques discussed in this thesis can be more widely applicable. It can be valuable for other probes with cable-count limitation, including intracardiac echography (ICE) and transesophageal echocardiography (TEE).

### 1.4 DESIGN OBJECTIVES

In this project, several echo signals from the receive transducers should be locally digitized rather than being processed in an analog way because local digitization brings more possibility of data processing.

Also, in terms of power consumption, load modulation is more attractive than serialization and active drivers when only one cable is used for data transmission. Thus, an application-specific integrated circuit (ASIC) is proposed to investigate a load-modulation data link that can be capable of sending the digitized echo signals of multiple channels using only one micro coaxial cable.

Besides, the use of multi-level signalling to encode multiple bits per symbol will be investigated. Thus the relationship between the accuracy of data transmission and transmission conditions can be acquired. With different symbol rates or bits per symbol, its BER might be different.

An experimental setup is proposed based on a test ASIC and an FPGA. It can be used to characterize the relationship between data accuracy and transmission mode (non-return-to-zero and return-to-zero) and the trade-off between symbol rates and bits per symbol.

To conclude, a test ASIC with load-modulation data link is to be developed to achieve a data rate higher than 600Mb/s through one cable and reflects optimum transmission condition.

### 1.5 THESIS ORGANIZATION

The thesis presents steps to propose an architecture to further increase the data rate through one cable and present the specific data-link part. In this chapter, the need for the IVUS ultrasound imaging system with reduced cable count and high data rate has been introduced.

Chapter 2 discusses the possible ways to reduce the cable count in a broader ultrasound imaging system field and motivates the use of load modulation for a digital data link for ultrasound echo signals in miniature powerconstrained devices.

Chapter 3 focuses on the existing ASIC with load-modulation data link and introduces a simulation model that enables us to reproduce the measured data link signals in simulation with good agreement.

Chapter 4 proposes a setup for evaluation of a next-generation load modulation data link with multi-bit per symbol signalling. Specifications of such signalling will be defined.

Chapter 5 shows the realization of the load-modulation test ASIC, mainly focusing on the load-modulation circuit and the data-rate doubling circuit.

Chapter 6 will provide the results of the trade-off between symbol rate and bits per signal in terms of data accuracy based on post-layout simulation. Also, it concludes the thesis and proposes ideas for future work.

## 2 CABLE-COUNT REDUCTION TECHNIQUES

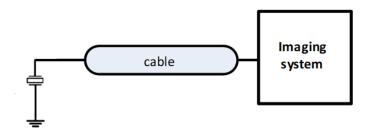

As is mentioned in Section 1.1, the echo signals captured by receive transducers will be converted into electrical signals. In Figure 2.1, the analog signal can be directly transmitted through a coaxial cable to a imaging system. However, it leads to the cable impedance mismatch and thus causes reflections and signal attenuation. Matching networks tend to be used to deal with the impedance mismatch but they are very big.

Figure 2.1: Simple signal transmission through coaxial cable

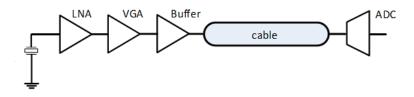

With the need for miniaturisation and robust signals, several signal processing processes have been implemented on-chip. An example of a single signal channel is shown in Figure 2.2. In this single-channel, the echo signals are captured by the analog front end (AFE) first. It mostly consists of a low noise amplifier (LNA) and a variable gain amplifier (VGA). The low noise amplifier is used as the first stage to interface with the echo signal with enough gain. It helps in attenuating noise from following stages. For the VGA, it is used to compensate for the propagation attenuation to generate a uniform signal amplitude versus time. Furthermore, with the purpose of the characteristic impedance match of the cable, a buffer or cable driver is required.

Figure 2.2: Signal transmission through coaxial cable

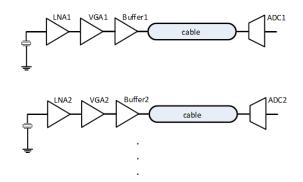

To get a more complete image and eliminate the need for a complex rotating system, a transducer-array is applied [9]. It means more echo signals should be processed and transmitted through the cable. Although each receive transducer can be applied to the signal channel respectively in Figure 2.3, the cables cannot be accommodated by the catheter due to its limited diameter.

Thus, with the increased number of transducers, ways to reduce the cable count should be explored to make it suitable for application.

Figure 2.3: Signal transmission for multiple signals

In this chapter, both digital cable-count reduction and analog cable-count reduction methods will be discussed. Their original ultrasound imaging application might be transesophageal echocardiography (TEE) or intracardiac echocardiography (ICE), but the discussion will show whether it can be applied to the IVUS field. Also, once the cable-count reduction method is decided, the reason for increasing the data rate with load modulation will be motivated.

### 2.1 ANALOG CABLE-COUNT REDUCTION

The electrical signal captured from the transducer or processed after the AFE is inherently an analog signal. Thus, it is natural to consider reducing the cable-count in the analog domain.

Over the past years, beamforming, frequency-division multiplexing (FDM) and time-multiplexing have been successfully applied to reduce the cable count.

### 2.1.1 Beamforming

Beamforming plays an important role when there are a large number of transducers at the tip of the catheter. Although it can work in the transmit process as well as receive process, in terms of emphasis on signal processing, beamforming in receive process is explored.

When there are a lot of receive transducers, it is impossible to connect each of them to the cable directly. Thus, these transducers can be divided into several sub-arrays and with the proper delay, echo signals from transducers in the same sub-array can be combined by means of a delay-and-sum operation and then sent to the cable together, resulting in the reduction of cable count.

In [17], a signal processing architecture with beamforming technology is proposed to reduce the cable count. This technique has been applied in various research prototypes [18][19] as well as in commercial probes.

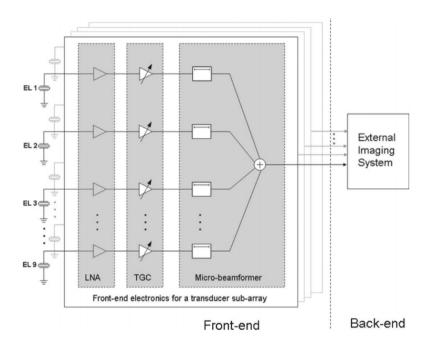

Figure 2.4: Signal processing architecture with beamforming for ultrasound imaging system [18]

Shown in Figure 2.4, nine transducers are combined as a sub-array and connected to an AFE respectively. After that, each of them is connected to the micro-beamformer cell to get the corresponding delay. This micro-beamformer consists of a programmable analog delay line (PADL) and a V/I converter. The PADL can generate delay from 40 ns to 280 ns with an increase of 40 ns each step while the converter brings convenience to the summation of the signals in the current mode. It eliminates the need for a summing amplifier and makes it more power-efficient.

For a large number of receive transducers, beamforming technology can greatly help reduce cable count. However, the sub-array beamforming does influence its frame rate and image quality.

#### 2.1.2 Frequency-division Multiplexing

Analog orthogonal frequency-division multiplexing is the main signal processing technique to reduce the cable count here. When two information signals are mixed with a sine wave and a cosine wave of the same frequency respectively, these two signals are transferred to a certain frequency and added together. The final expression be can be expressed as follows:

$$X(w) = m_1(w) \times \cos(w_0) + m_2(w) \times \sin(w_0)$$

Thus, these two signals can be combined to reduce cable count from two to one. In the following demodulation process, when a sine wave of the same frequency is applied, the information signal  $m_2$  can be acquired after a low-

pass filter. The mathematical process is shown below:

$$X(w) \times \sin(w_0) = (m_1(w) \times \cos(w_0) + m_2(w) \times \sin(w_0)) \times \sin(w_0)$$

$$X(w)\sin(w_0) = \frac{1}{2}m_1(w)\sin(2w_0) + \frac{1}{2}m_2(w) - \frac{1}{2}\cos(2w_0)$$

After the low-pass filter, the information signal  $m_2$  remains only. It applies to signal  $m_1$  as well when a cosine signal wave is applied.

Figure 2.5: Block diagram of analog orthogonal frequency-division multiplexing [20]

In [20], the signal channels are increased to 8 and the working process including analog orthogonal frequency-division multiplexing can be expressed in Figure 2.5. The four carrier frequencies are 40MHz, 80MHz, 120MHz and 240MHz respectively and it successfully reduced the cable count responsible for signal transmission from eight to one. However, it requires more cables for clock and it suffers from cross-talk and cable non-idealities.

The frequency-division multiplexing is suitable for low-pass inputs. However, it might be difficult to work well in IVUS imaging field because of the band-pass characteristic of ultrasound signals. Also, to remain one-cable data transmission, more signals will be transmitted at the same time, which makes it difficult to leave out the influences of cross-talk and cable nonidealities.

### 2.1.3 Time-multiplexing

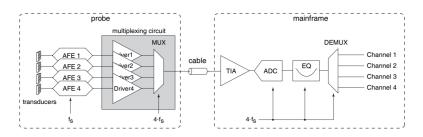

Normally, in a time-multiplexing ultrasound imaging system, like a system in Figure 2.6, several echo signals are processed by AFEs first and then sent to the sampling block with the sampling frequency  $f_s$ . After that, these signals will be sent into a high-frequency multiplexer and transmitted to the cable one by one.

In [21], echo signals from four transducers are sent to LNA and TGA first and after that, there are four sampling-capacitor arrays (SCA), which sample these analog signals at 25MHz. However, the four phase-shifted release clocks of SCAs are different. Thus, with the help of drivers, the converted currents are sent into the cable at four different time points and its sampling rate can be 100 MHz. However, the release clock limits the number of possible transducers and thus limits the data rate.

Figure 2.6: Block diagram of a time-multiplexing system [21]

However, this time-multiplexing system heavily replies on equalization on the system side to correct for the cable bandwidth limitation and its transmissionline effect. This increases complexity but limits the channel-to-channel crosstalk that can be achieved.

### 2.2 DIGITAL CABLE-COUNT REDUCTION

Several works have been reported to reduce the cable count digitally. The main idea behind this is to digitize the signals on-chip first with an ADC.

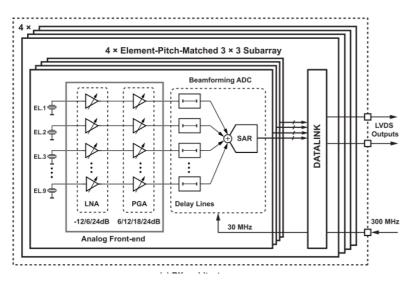

In [19], in terms of a large number of transducers, the idea of beamforming is applied first. Its architecture is presented in Figure 2.7. Each echo signal is processed by the LNA and TGA first and then it will be sent to a delay-line based micro-beamformer that combined the echo signals of a sub-array of  $3\times3$  elements. However, after that, the signal is not sent into the driver directly as in [17]. Instead, they are added and digitized by a SAR ADC in the charge domain. In this case, four digital signals are acquired. With the following serialization, only one cable is responsible for data transmission. Thus, an overall channel-count reduction of 36 ( $4\times3\times3$ ) is achieved.

Also, in [16], an ADC is applied after the AFE to digitize the signal directly, allowing for robust data transmission.

Figure 2.7: Architecture of receive electronics with digitization[19]

However, it consumes more die areas when there is an ADC after each AFE for digitization. Thus, the number of signal channels is limited.

### 2.3 DIGITAL DATA LINK TECHNIQUES

Compared to the analog cable-count reduction methods, digitization makes signals more robust against noise, interference and cross-talk. Considering the comparatively fewer receive transducers in an IVUS imaging system, digital cable-count reduction methods are a good candidate although ADCs might consume some die area. More importantly, with these digital signals, it brings more possibility for data processing on-chip to further reduce the cable count. In the following, ways of data processing are discussed.

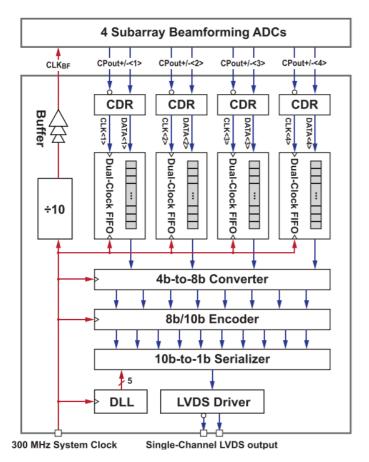

First, serialization [19] has been applied to transmit the output of several digital signals to the cable one by one. A block diagram of a data link with serialization is shown in Figure 2.8. The four differential digital signals are converted into the single-bit mode with a clock-data-recovery circuit.

However, although the data-stream can be 1.5Gb/s, it requires a very accurate high-speed clock and a buffer. Also, it occupies a huge die area, which makes it difficult to transfer this technique to IVUS application.

To reduce its power consumption, post beamforming[10] can be applied in the signal processing. However, it results in a reduced imaging frame rate.

Second, load modulation [16] has been applied to transmit digital outputs through a cable by means of a variable equivalent resistance. With different input digital signals, the equivalent resistance value changes simultaneously. With the  $50\Omega$  characteristic impedance at the load side, it eliminates the power-hungry buffer. Also, it generates a voltage divider, which makes it

Figure 2.8: A block diagram of a data link with serialization [19]

possible to detect the changing voltage.

Figure 2.9: A block diagram of a data link with load modulation [16]

In Figure 2.9, the output of an asynchronous SAR ADC [16] is used directly to drive a load-modulation data link. With this differential signal, it controls two transistors respectively and thus generates three different voltage levels at  $V_{out}$ . Based on the voltage level, corresponding input data can be recovered at the system side. With this simple load modulation architecture, it generates 600Mb/s data rate without an accurate DLL and a power-hungry cable driver. Also, with an increased number of transistors, it can generate more voltage levels and thus increase the bits per symbol, which helps increase the data rate.

Besides, in terms of the multi-level signal transmission through a cable, several digital signals can be converted by a digital-to-analog converter (DAC). However, it brings circuit complexity. Worse still, it requires a cable driver or a buffer to match the cable characteristic impedance, which consumes more power on-chip. With the purpose of IVUS application, power-consumption on-chip should be as low as possible.

In this case, multi-level signalling by load modulation is more suitable for a digital data link in IVUS ultrasound systems. First, it eliminates the need for an additional cable driver, which reduces power consumption. It makes it more suitable for the low-power application. Also, in terms of circuit complexity, it is comparatively easier and gives a quick insight into the data transmission through one cable. Additionally, it transmits more than one bit per symbol. Although symbol rate is limited by the limited cable bandwidth, multi-bit per symbol can help increase data rate.

## 3 EXISTING ASIC WITH LOAD-MODULATION DATA LINK

### 3.1 INTRODUCTION TO EXISTING ASIC WITH LOAD-MODULATION DATA LINK

The availability of an existing ASIC [16] with local digitization and loadmodulation data link helps to further explore the potential of such a data link for miniature ultrasound probes. The architecture is discussed below.

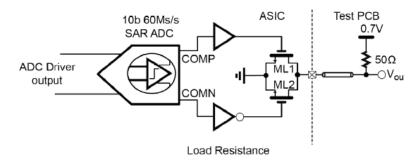

Figure 3.1: The block diagram of an IVUS imaging system with load-modulation data link [16]

In Figure 3.1, the 16 TX transducers are controlled and excited by on-chip high-voltage switches that route a HV signal generated at the system side, and the remaining 64 RX transducers are interfaced with a 64-1 analog multiplexer and an analog front end. These processed signals are connected to a SAR ADC, which transforms analog signals into digital ones. This ADC generates two differential outputs for one data.

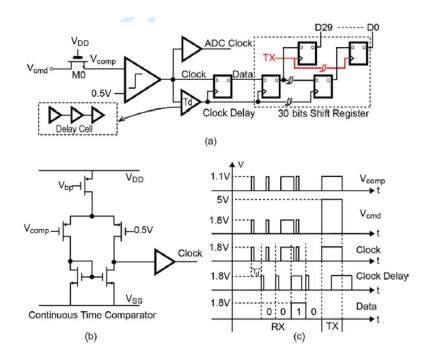

The clock extracted from the command signal eliminates an external clock and its working principle is shown in Figure 3.2. The command signal is processed by NMOS transistor *M*0 first, followed by a continuous-time comparator. The comparator turns the signal into proper logic levels. At the rising edge, the resulting signal triggers the ADC and it working frequency is 60 MHz.

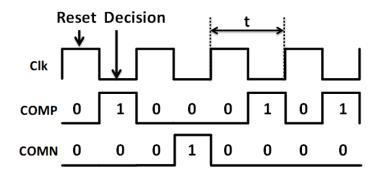

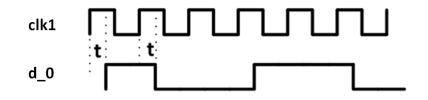

Also, with its clock generated from an asynchronous SAR logic, the differential outputs both generate a zero between two data. The SAR logic provides two phases: 'reset' and 'decision'. Each phase is around 0.5*t* and its timing diagram is presented in Figure 3.3. *COMP* and *COMN* are the differential outputs of the comparator.

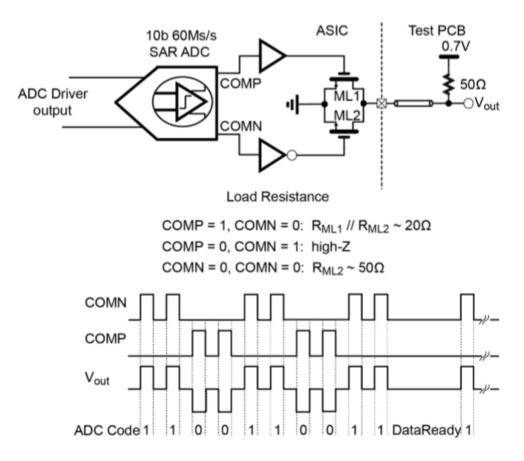

Then, the 10-bit ADC output is transmitted through one cable. Decided by registers, t in Figure 3.3 is less than 1.6 ns. Thus, between every 10 bits signals, there is a relatively long return-to-zero stage. Shown in Figure 3.4, with a buffer and an inverter, the two comparator outputs of the ADC are connected to two NMOS transistors *ML*1 and *ML*2 respectively to act as control signals. The resistance of the two transistors changes with these control signals. Thus, it can generate three different voltage levels when it is observed at  $V_{out}$ . Each voltage level (around 200 mV, 700mV and 350 mV) can represent its corresponding ADC output information: '0', '1' and 'return-

Figure 3.2: Circuit diagrams of (a) clock and data recovery; (b) the continuous-time comparator; (c) associated time diagram [16]

Figure 3.3: Timing diagram of the comparator [16]

to-zero". Also, due to the comparator clock, there is a return-to-zero stage, which helps distinguish two adjacent signals. It brings convenience in the decoding process.

Through load modulation, the digitized signals can be transmitted serially through only one cable in a power-efficient and simple way. Decided by the ADC specifications, the data rate is 600 Mb/s. However, 64-1 multiplexer does influence its frame rate. To acquire its image information more quickly, One possible way is to replace the multiplexer with 32-1 or smaller ones but it requires at least doubling the data rate without the increase of cable count. Multi-bit per symbol signalling can be a good choice to increase the data rate with one cable for a faster frame rate when the same technology (180 nm) is applied. Thus, to explore signal transmission through cables, the cable specification should be further analysed.

Figure 3.4: Block diagram and waveforms of the load modulation data link [16]

### 3.2 MEASUREMENT OF EXISTING ASIC WITH LOAD-MODULATION DATA LINK

In this section, the measurement result of the existing ASIC is presented first, followed by a discussion about its features.

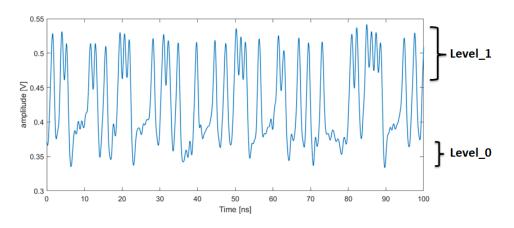

With a proper setup, the waveform at the system side is captured through an oscilloscope and processed by MATLAB on a PC. In this setup, the ASIC and the oscilloscope are connected with an active probe, YOKOGAWA PBA2500. Its -3dB bandwidth is 2.5 GHz, which ensures the proper transmission for this system. However, the bandwidth of the oscilloscope (YOKOGAWA DL9710L) is 1 GHz only and it might filer out the signals because due to the return-to-zero stage, the waveform frequency is 1.2 GHz.

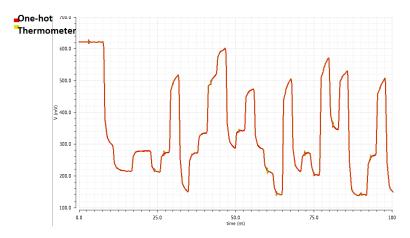

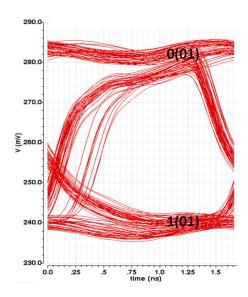

Shown in Figure 3.5, signals among *Level*\_0 and *Level*\_1 should represent o and 1 respectively. Taking the return-to-zero stages into consideration, there should be three fixed voltage levels. Signals representing o should have the same amplitude. However, for *Level*\_0, although it can be distinguished from the other two voltage levels, there are some variations in amplitude. For one bit per symbol, it requires three voltage levels only, including two information levels and one transition level. Certain variations can be acceptable when intervals of each two are obvious. However, it might be a problem

for multi-bit per symbol because there are more voltage levels closer to each other when the supply voltage at the system side remains same.

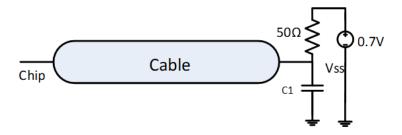

Figure 3.5: Measured waveform of the existing ASIC

There are some potential explanations for these variations. One possible reason is reflections due to impedance mismatch. This mismatch may come from impedance resistor or the parasitic effect generated from the two interfaces of the coaxial cable, where parasitic capacitance and inductance can influence the equivalent impedance seen from the system side, in Figure 3.6. In this case, there is another parasitic capacitance C1 at the system side. It is in parallel with 50  $\Omega$  and it results in the change in equivalent impedance. Due to the transmission effect, it will cause impedance mismatch and lead to reflection. Another possibility is that the cable itself causes these variations.

Figure 3.6: Illustration of equivalent impedance

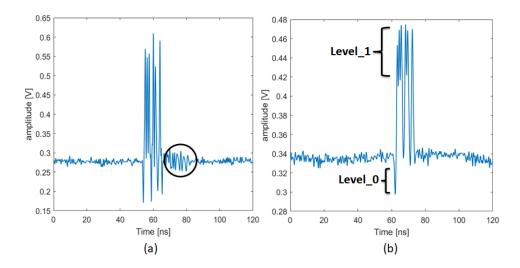

Thus, to find out the reason behind the variations, a test experiment is carried out. It aims to test whether there is obvious reflections caused by impedance mismatch. In this measurements, with a reduced clock frequency from FPGA, the interval time between two 10-bit signals is increased, which helps observe reflections. A passive probe, YOKOGAWA 701943, is applied and its bandwidth is around 500MHz.

In Figure 3.7, there are some reflections appearing at the chip side and due to signal transmission through the cable, it takes 10 ns for reflections from signals at the system side to appear at the chip side again. In this case, these

Figure 3.7: Waveform of (a) chip side of normal measurement (b) system side of normal measurement

reflections should take around another 10 ns to arrive at the system side to influence signals. However, there are not obvious changes in amplitude after the wave of a 10-bit signal. At the same time, for signal waves at the system side, there remain obvious variations at the very beginning.

Also, in Figure 3.7, obvious noise is observed during the intervals. It is generated by the oscilloscope itself. The peak-to-peak noise can be 42 mV when the probe is short-connected. To get a cleaner waveform, an oscillo-scope with a lager bandwidth should be applied for measurement.

Thus, as discussed above, although there exit reflections, obvious variations can appear at the beginning when reflections cannot influence its waveform in Figure 3.5. Impedance mismatch will cause variations but it is not the dominant cause. Based on the previous assumptions, it may come from the coaxial cable itself. To investigate the load-modulation data link with one cable transmission, a reliable cable model should be applied.

### 3.3 RLCG CABLE MODEL

In [16], a 1.5-meter 42 AWG coaxial cable is applied for measurement. This type of cable can be modeled as a transmission line model and its parameters are presented in Table 3.1.

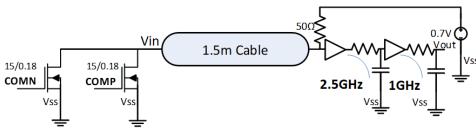

These parameters can be applied in the Spectre multi-conductor transmission line model for simulation to mimic the reflection measurement in 3.2. The simplified simulation test bench is shown in Figure 3.8.

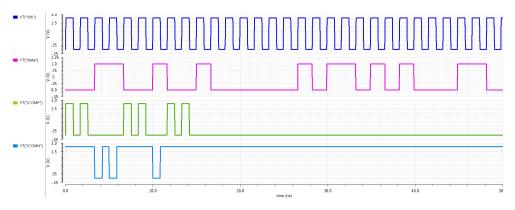

COMP and COMN are control signals from outputs of the ADC comparator, in Figure 3.4. They are generated by a Verilog A model in simulation. The corresponding control signals are presented in Figure 3.9. Also, to take

|                                 | AWG 42 |

|---------------------------------|--------|

| <b>R(</b> <i>Ohm</i> <b>/m)</b> | 7.5    |

| C(pF/m)                         | 110    |

| L(nH/m)                         | 275    |

| G(nS/m)                         | 660    |

| Attenuation(dB/m)               | 0.7    |

Table 3.1: 42AWG coaxial cable parameters [22]

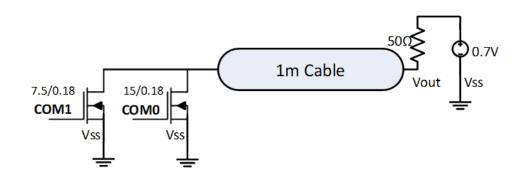

Figure 3.8: Simplified system for simulation

the bandwidth limitation of the active probe and the oscilloscope into consideration, two low-pass networks are connected in series and their -3dB bandwidth is 2.5 GHz and 1 GHz respectively. However, for this simplified system, it excludes some parasitic effects and control signals are ideal.

Figure 3.9: Control signals generated with Verilog A model

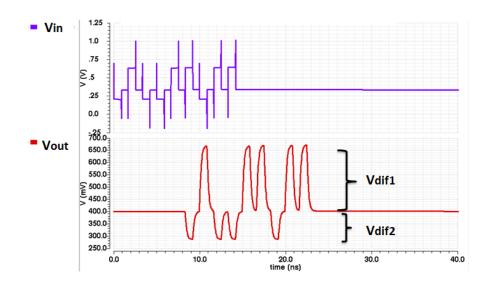

The corresponding  $V_{chip}$  and  $V_{out}$  are shown in Figure 3.10. For the voltage observed from the chip side, there is no reflection and for the same voltage level at the system side, there is no variation.

Also, when the waveforms of both measurement and simulation results are compared, the voltage intervals between two levels are different. The difference can be summarized in Table 3.2. Although some non-idealities like parasitic capacitance are excluded, the differences should not be too obvious.

Thus, for the RLCG model, it is too ideal to represent model function during signal transmission and it cannot predict the variations correctly.

Figure 3.10: Corresponding waveforms at Vin and Vout for RLCG model

Table 3.2: Voltage change comparison between RLCG model and measurement

|                        | Simulation | Measurement |

|------------------------|------------|-------------|

| $V_{dif1}/\mathbf{mV}$ | 270        | 175         |

| $V_{dif2}/\mathbf{mV}$ | 120        | 50          |

### 3.4 S PARAMETER-BASED CABLE MODEL

A measured S parameter file can be applied in 'n2port' instance in Cadence for simulation. Compared with the RLCG model, they are both extracted from measurement, but RLCG model ignores its frequency-dependent performance. However, the limitation of the S parameter model is that only a one-meter cable measurement result is available and its accuracy is highly dependent on the measurement process.

In order to mimic load modulation performance in Figure 3.4, the same test bench in Figure 3.8 is applied. Also, two 'n2port' instances are put in series to compensate for the length difference although it might bring more attenuation.

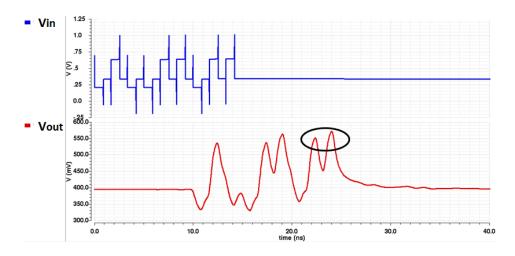

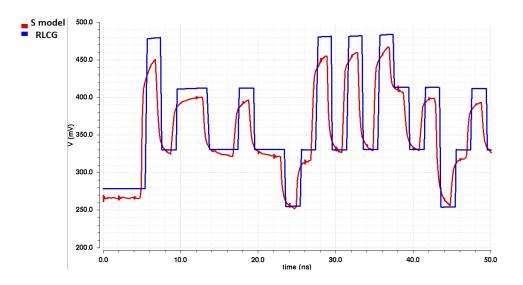

Shown in Figure 3.11, at the chip side, there is some small reflection. Also, at the system side, there are not obvious reflections. For the same voltage level, there are some variations. These are in agreement with measurement.

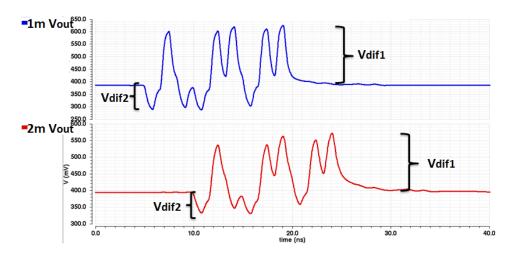

To further explore the reliability of this S parameter-based cable model, another simulation with 1m cable is done to help get a rough idea about the 1.5-meter cable transmission situation. The simulation results are shown below.

From the simulation result in Figure 3.12, it shows that with the increase of cable length, the delay time increases and the attenuation effect of the cable

Figure 3.11: Corresponding waveforms at Vin and Vout for S parameter model

Figure 3.12: Corresponding V<sub>out</sub> for 1m and 2m cable

is more severe. Although there might be some parasitic components that affect its waveform, the cable is the main reason for amplitude loss.

Also, some variations can be observed. Even when the two low-pass filter networks are removed, the variations remain. For the wave after the 9-bit signal, it is almost flat and it shows that, reflection will not lead to an obvious change in signal amplitude. Thus, the cable is responsible for the variations as well.

In Table 3.3, although the 1.5-meter S parameter-file is missing, it provides a rough value of  $V_{dif1}$  and  $V_{dif2}$  respectively. Compared to those from RLCG

|                 | 0 0 | 1   | Simulation-RLCG |     |

|-----------------|-----|-----|-----------------|-----|

| $V_{dif1}$ /mV  | 236 | 170 | 270             | 175 |

| $V_{dif2}$ /mV) | 100 | 60  | 120             | 50  |

Table 3.3: Voltage change comparison between two models and measurement

model simulation result, S parameters-based simulation results are closer to the practical measurement results. What's more, in [16], the frequency of signals is even a bit higher than 600 MHz. It means the signals will suffer more attenuation, which will make the simulation result closer to measurement result.

# 4 EXPERIMENTAL SETUP FOR EVALUATION OF LOAD-MODULATION

In this chapter, several types of cables are discussed first to choose a more suitable one for this project. With the chosen type of cable, the specifications of the data link part can be derived. In this case, a complete architecture with load-modulation data link will be proposed. Furthermore, a simplified ASIC architecture with multi-bit per symbol signalling will be shown to help reduce project complexity and a rough experimental setup will be described to evaluate the load-modulation data link by comparing the data rate and its corresponding BER number.

#### 4.1 CHOICE OF CABLE

As discussed in Chapter 3, an S parameter-based cable model is more practical to predict cable performance in simulation including inter-symbol interference and attenuation. To ensure high-quality signal transmission, types of cables should be explored to choose a more suitable one for this project.

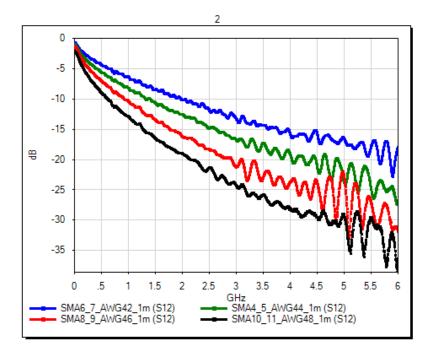

Four types of micro-coaxial cables commonly used in catheters are considered: AWG 42[22], AWG 44[23], AWG 46[24], AWG 48[25]. The comparisons are based on their characteristic frequency-dependent attenuation and data rate per cross-sectional area.

**Figure 4.1**:  $S_{12}$  of four types of cables

Figure 4.1 represents the measured relationship between transmission coefficients and frequency for four types of cables respectively. First, all their coefficients decrease with frequency. This complicates high-speed signal transmission because the attenuation effect becomes more severe and brings difficulty to decoding over a certain symbol rate. If there is only one bit per symbol, the achievable data rate will be limited in terms of data accuracy.

Second, compared to the other three types of cables, cable AWG 42 suffers the least attenuation at all frequencies, which is only half of the attenuation of cable AWG 48. This feature makes AWG 42 a better candidate for 1-bit signal transmission, but at the expense of a larger diameter.

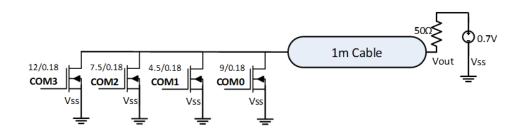

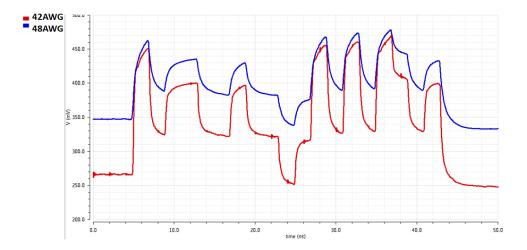

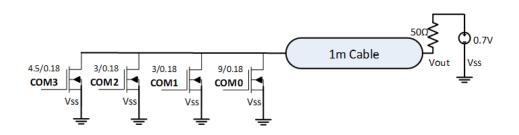

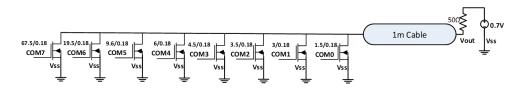

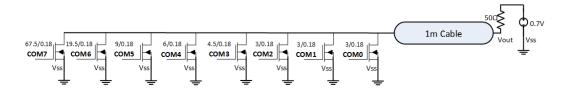

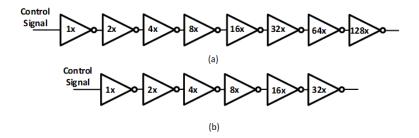

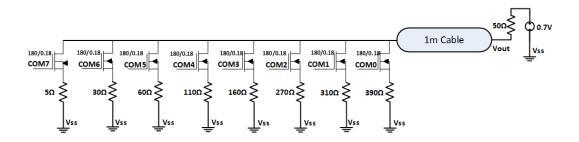

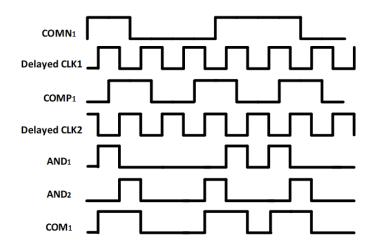

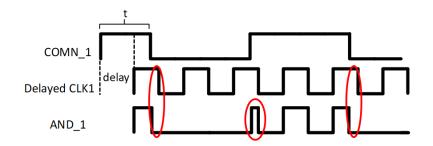

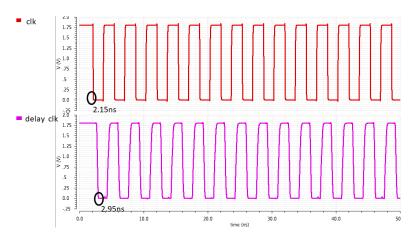

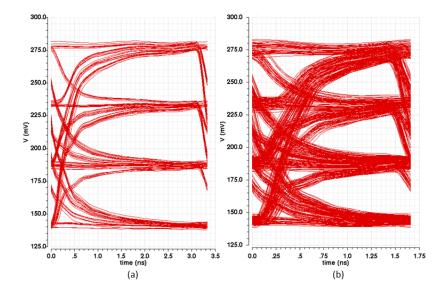

Furthermore, multi-bit per symbol transmission can be explored and the schematic of 2-bit load modulation transmission is shown in Figure 4.2. Ideally, there should be four fixed levels. The sizes of these transistors are chosen to ensure that each interval between two levels is around 80 mV. Thermometer coding is applied and Table 4.1 illustrates its control logic. Figure 4.3 shows the simulated waveforms at *V*<sub>out</sub> when AWG 48 and AWG 42 are applied respectively. Although the two waveforms at *V*out are similar, the intervals between two adjacent voltage levels are different because of their different frequency-dependent attenuation. The average voltage interval of AWG 48 is 40 mV and that of AWG 42 is 60 mV at the symbol rate of 500 MHz under the same load-modulation structure. The larger voltage difference between two levels makes it easier to decode input data and allows some non-idealities like noise, which makes AWG 42 more suitable for multi-bit per symbol transmission as well.

Figure 4.2: Schematic of 2-bit per symbol transmission with an interval of 80 mV

Figure 4.3: Output waveforms of AWG 48 and AWG 42 at the symbol rate of 500  $\rm MHz$

| Input Data | COM <sub>3</sub> | COM2 | COM1 | СОМо |

|------------|------------------|------|------|------|

| 11         | 1                | 1    | 1    | 1    |

| 10         | 0                | 1    | 1    | 1    |

| 01         | 0                | 0    | 1    | 1    |

| 00         | 0                | 0    | 0    | 1    |

Table 4.1: Thermometer coding for 2-bit per symbol transmission

Table 4.2: Diameters of different cables[22][23][24][25]

|                     | AWG 42 | AWG 44 | AWG 46 | AWG 48 |

|---------------------|--------|--------|--------|--------|

| diameter <b>/mm</b> | 0.3048 | 0.2667 | 0.1981 | 0.1981 |

The voltage intervals can be increased with changed transistor sizes or increased supply power. However, it consumes more power and die area.

On the other hand, when these cables are applied in ultrasound imaging systems for signal transmission, the number of cables is limited by the available cross-sectional area because of different cable diameters. Table 4.2 presents outer diameters of four cables. It shows the diameter of cable AWG 42 is around 50 percent larger than that of cable AWG 48 or cable AWG 46. For a certain cross-sectional area, accommodated cable counts are different and it leads to different data rates per cross-sectional area.

To compare data rate per cross-sectional area, a catheter with a 2-mm diameter is given. Figure 4.4 illustrates that around 24 AWG 42 can be accommodated in the given area while for AWG 46 or AWG 48, the possible cable count can reach 70, which is almost triple the cable count of AWG 42. However, in Figure 4.1, it can be found that, given acceptable attenuation, the corresponding frequency of AWG 42 is twice that of AWG 46 and triple that of AWG 48. For example, when the attenuation of -15dB is acceptable, the working frequency of AWG 42 can be 3.5 GHz, while that of AWG 48 is 1.2 GHz and that of AWG 46 is 1.7 GHz. Assuming that all the cables are used for signal transmission, AWG 46 would transmit more data per cross-sectional area, followed by AWG 42 and AWG 48. However, it is challenging to integrate many cables together and if each cable is linked to a signal channel, it consumes too much die area and may lead to a power consumption problem. Thus, although AWG 46 may achieve the highest data rate per cross-sectional area among these four types of cables, AWG 42 is more practical.

Thus, AWG 42 is chosen for this project because of its best transmission capacity per cable among the four candidates. Second to AGW 46, AWG 42 can achieve a comparatively high data rate per cross-sectional area as well.

Figure 4.4: Illustration of (a) AWG 42 and (b) AWG 46 or AWG 48 accommodated in a catheter with a 2-mm diameter

### 4.2 ANALYSIS OF LOAD-MODULATION DATA LINK

As discussed in 4.1, cable AWG 42 is selected for this project about a multi-bit per symbol signalling because of its best transmission capacity per cable and its second highest data rate per cross-sectional area. To decide appropriate specifications of the load-modulation data link, inter-symbol interference should be further analyzed. Otherwise, it would be difficult to choose an appropriate threshold voltage in the decoding process when there are huge variations.

#### 4.2.1 Single-bit per Symbol

The analysis starts with 1-bit per symbol transmission and the schematic is shown in Figure 4.5. The expected interval between two adjacent levels is 80 mV.

Figure 4.5: Schematic of 1-bit per symbol transmission with an interval of 80 mV

The simulated waveform at  $V_{out}$  is presented in Figure 4.6. It can be seen that the waveform associated with a given bit is always influenced by its preceding bit. For example, Point B and Point D represent the same data '1'

but their amplitudes are different. Point D is 375 mV and it is higher than Point B (372 mV). Taking their previous signals into consideration, Point C (310 mV) is higher than Point A (307 mV). Thus, inter-symbol interference leads to variations.

Figure 4.6: Output waveform at the symbol rate of 600 MHz for 1-bit per symbol transmission

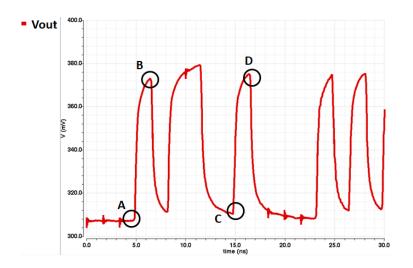

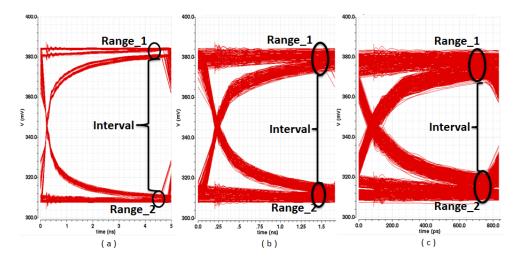

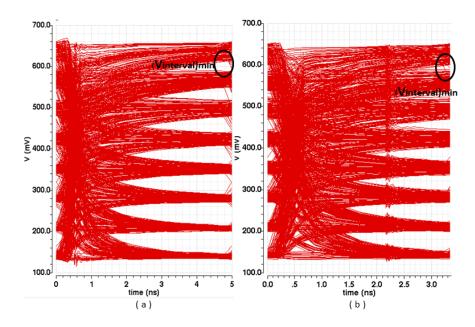

Its eye diagrams at several symbol rates are presented in Figure 4.7.  $V_{range}$  describes average variation range of these two level and  $V_{interval}$  represents the interval between two levels.

Figure 4.7: Eye diagram at symbol rate of (a) 200 MHz (b) 600 MHz and (c) 1.2 GHz

Table 4.3 shows  $V_{range}$  and  $V_{interval}$  for this 1-bit per symbol transmission when the expected interval is around 80 mV. It can be found that, with an increased symbol rate, inter-symbol interference is more severe and it causes more obvious variations for the same voltage level. A larger variation range results in a smaller interval between two levels. However, with an increased signal period, the influence of the previous symbol can be reduced and the signal can be closer to its expected voltage level.

| Symbol rate (GHz) | Data rate (Gb/s) | V <sub>range</sub> (mV) | V <sub>interval</sub> (mV) |

|-------------------|------------------|-------------------------|----------------------------|

| 0.2               | 0.2              | 4                       | 68                         |

| 0.6               | 0.6              | 10                      | 56                         |

| 1.2               | 1.2              | 15                      | 45                         |

**Table 4.3:** Comparison of  $V_{range}$  and  $V_{interval}$  at different symbol rates with the interval of 80 mV

#### 4.2.2 Two-bit per Symbol

The influence of a multi-bit per symbol signalling remains to be explored. A 2-bit per symbol transmission structure is shown in Figure 4.2. The voltage difference between two levels is around 80 mV.

To judge output waveform accuracy, the RLCG-based simulation result is applied to set as a reference first to give a quick idea about what the ideal waveform should be like. The rough comparison is shown in Figure 4.8. It shows that, the corresponding simulated results with a RLCG-based model and an S parameter-based model share a similar waveform.

Figure 4.8: Output waveforms from an S parameter-based model and a RLCGbased model for 2-bit per symbol at the symbol rate of 500MHz

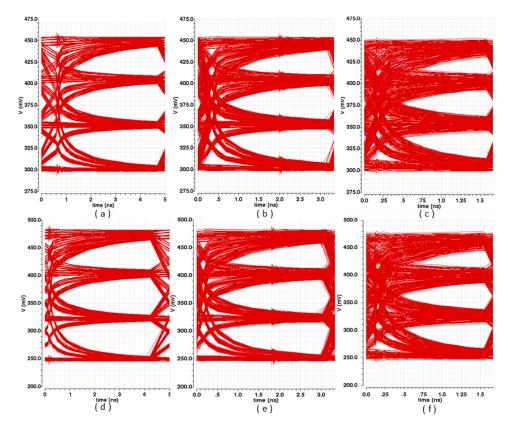

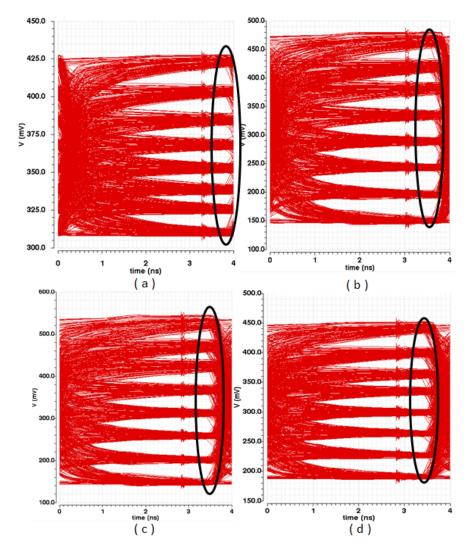

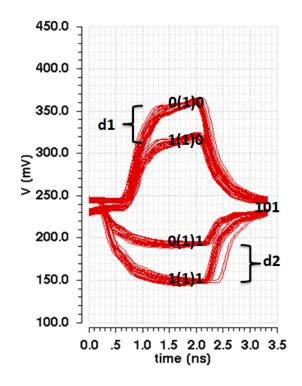

In Figure 4.8, the red line represents the output waveform with an S parameterbased cable model and the four voltage levels are between 250 mV and 450 mV. At this time, there are two bits per symbol. The sizes of transistors can be changed and the new schematic in Figure 4.9 can generate an interval of 50 mV between each two levels. The eye diagrams of these two structures at several symbol rates are presented in Figure 4.10. More  $V_{range}$  and  $V_{interval}$  at different symbol rates are summarized in Table 4.4.  $V_{range}$  describes the average range of variations for different voltage levels while  $V_{interval}$  describes the average interval.

Figure 4.9: Schematic of 2-bit per symbol transmission with an interval of 50 mV

**Figure 4.10:** Eye diagram at the symbol rate of (a) 200 MHz with a 50 mV interval (b) 300 MHz with a 50 mV interval (c) 600 MHz with a 50 mV interval (d) 200 MHz with an 80 mV interval (e) 300 MHz with an 80 mV interval and (f) 600 MHz with an 80 mV interval for a 2-bit per symbol signalling

In Table 4.3, although intervals between two levels are different,  $V_{range}$  increases with the symbol rate. However, with a larger interval, inter-symbol interference is more severe and it leads to a larger variation. Also, the relationship between voltage levels and inter-symbol interference can be ac-

|                   |                  | 80 mV                   | interval                   | 50 mV                   | interval                   |

|-------------------|------------------|-------------------------|----------------------------|-------------------------|----------------------------|

| Symbol rate (GHz) | Data rate (Gb/s) | V <sub>range</sub> (mV) | V <sub>interval</sub> (mV) | V <sub>range</sub> (mV) | V <sub>interval</sub> (mV) |

| 0.1               | 0.2              | 7                       | 70                         | 5                       | 46                         |

| 0.2               | 0.4              | 14                      | 59                         | 8                       | 40                         |

| 0.3               | 0.6              | 18                      | 55                         | 11                      | 35                         |

| 0.5               | 1                | 24                      | 45                         | 16                      | 29                         |

| 0.6               | 1.2              | 26                      | 43                         | 17                      | 27                         |

Table 4.4: Comparison of V<sub>range</sub> and V<sub>interval</sub> at different symbol rates

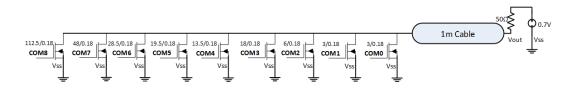

Table 4.5: Thermometer coding for 3-bit per symbol transmission

| Input Data | COM1 | COM2 | COM <sub>3</sub> | COM <sub>4</sub> | COM <sub>5</sub> | COM6 | COM <sub>7</sub> |

|------------|------|------|------------------|------------------|------------------|------|------------------|

| 111        | 1    | 1    | 1                | 1                | 1                | 1    | 1                |

| 011        | 1    | 1    | 1                | 1                | 1                | 1    | 0                |

| 101        | 1    | 1    | 1                | 1                | 1                | 0    | 0                |

| 001        | 1    | 1    | 1                | 1                | 0                | 0    | 0                |

| 110        | 1    | 1    | 1                | 0                | 0                | 0    | 0                |

| 010        | 1    | 1    | 0                | 0                | 0                | 0    | 0                |

| 100        | 1    | 0    | 0                | 0                | 0                | 0    | 0                |

| 000        | 0    | 0    | 0                | 0                | 0                | 0    | 0                |

quired from Table 4.4 and Table 4.3. Considering the condition of an 80 mV interval, with increased voltage levels, variations increase at the same symbol rate. Thus, more voltage levels lead to more severe inter-symbol interference. This relationship also indicates the possibility that, to achieve a certain data rate, a 2-bit per symbol signalling can be better than a 1-bit signalling because the symbol rate of the 2-bit signalling is half of that of the one-bit signalling. With the same expected interval, the 2-bit signalling generates a larger  $V_{interval}$  and it allows for the existence of non-idealities like noise, which increases transmission accuracy.

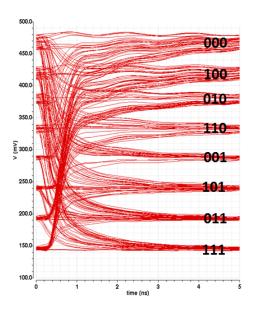

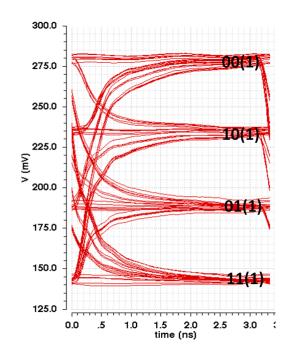

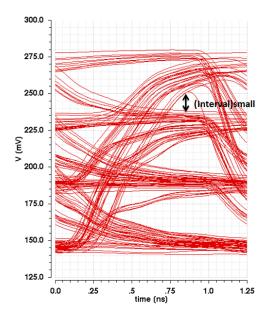

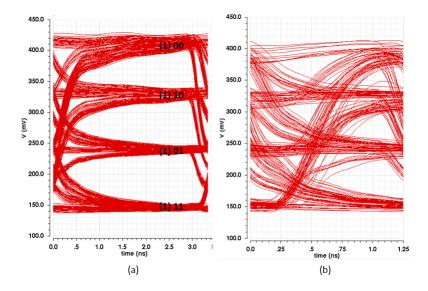

### 4.2.3 Three-bit per Symbol