Circuits and Systems Mekelweg 4, 2628 CD Delft The Netherlands http://ens.ewi.tudelft.nl/

# M.Sc. Thesis

## The Impact of Low-Power Design Methodology on Digital Libraries

## Ahmad Hamdy Elsayed

## Abstract

In recent years, exciting new low-power design methods have been introduced, such as: multiple supply voltages, body bias techniques and power shut-off. In order to use these low power design methods, strict requirements for both libraries and tools are needed. An additional challenge is the introduction of more accurate characterization models for newer technologies (current source models like ECSM and CCS). This has made the task of library checking a serious issue that needs to be automated.

The main part of this thesis presents a checker tool that is used to verify the consistency of the different library formats (views) in standard cell libraries. The layout consistency checker in our tool checks the consistency of the layout of pins between GDSII and LEF library views; we devised a new algorithm, *Grid Formation and Centre Inclusion*, for this checker. The tool also verifies the pin consistency and availability of cells across other library formats, such as: Verilog and Liberty. The tool was tested using different technology libraries (such as 90nm and 40nm), provided by different vendors (such as GLOB-ALFOUNDRIES); multiple interfacing errors were caught using our library checker tool.

A second part at the end of the thesis shows experiments with some of the low-power design techniques used during the design of a digital block, using -for implementation- standard cells from one of the libraries that have been checked with the library checker tool. Benefits of using these techniques are evaluated and trade-offs are discussed. Power-Shut Off (PSO) design technique proved to be the most effective in reducing power consumption, with power savings that reached 20%.

Faculty of Electrical Engineering, Mathematics and Computer Science

**Delft University of Technology**

## The Impact of Low-Power Design Methodology on Digital Libraries

## THESIS

# submitted in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE

in

## Computer Engineering

by

Ahmad Hamdy Elsayed born in Cairo, Egypt

This work was performed in and sponsored by:

NXP Semiconductors Eindhoven

In collaboration with:

Circuits and Systems Group Department of Microelectronics & Computer Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

**Delft University of Technology** Copyright © 2012 Circuits and Systems Group All rights reserved.

## Delft University of Technology Department of Microelectronics & Computer Engineering

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "The Impact of Low-Power Design Methodology on Digital Libraries" by Ahmad Hamdy Elsayed in partial fulfillment of the requirements for the degree of Master of Science.

Dated: 21 September 2012

Chairman:

prof.dr.ir. A.J. van der Veen

Advisors:

dr.ir. Nick van der Meijs

dr.ir. Michel Berkelaar

Committee Members:

dr.ir. Zaid Al-Ars

ir. Eric Seelen

dr.ir. Philippe Soulard

In recent years, exciting new low-power design methods have been introduced, such as: multiple supply voltages, body bias techniques and power shut-off. In order to use these low power design methods, strict requirements for both libraries and tools are needed. An additional challenge is the introduction of more accurate characterization models for newer technologies (current source models like ECSM and CCS). This has made the task of library checking a serious issue that needs to be automated.

The main part of this thesis presents a checker tool that is used to verify the consistency of the different library formats (views) in standard cell libraries. The layout consistency checker in our tool checks the consistency of the layout of pins between GDSII and LEF library views; we devised a new algorithm, *Grid Formation and Centre Inclusion*, for this checker. The tool also verifies the pin consistency and availability of cells across other library formats, such as: Verilog and Liberty. The tool was tested using different technology libraries (such as 90nm and 40nm), provided by different vendors (such as GLOBALFOUNDRIES); multiple interfacing errors were caught using our library checker tool.

A second part at the end of the thesis shows experiments with some of the low-power design techniques used during the design of a digital block, using -for implementationstandard cells from one of the libraries that have been checked with the library checker tool. Benefits of using these techniques are evaluated and trade-offs are discussed. Power-Shut Off (PSO) design technique proved to be the most effective in reducing power consumption, with power savings that reached 20%. This project would not have been possible without the support of many people. I wish to thank, first and foremost, my supervisor dr.ir. Michel Berkelaar who offered me all the support and advice throughout my thesis, and guided me through difficult times to get this thesis work done in the best possible shape. I would also like to offer my sincerest gratitude to my mentors at NXP Semiconductors: ir. Eric Seelen , dr.ir. Philippe Soulard and dr. Ananta Majhi, who were abundantly helpful and offered me invaluable assistance, guidance and support throughout the whole thesis work.

Special thanks go to the people at NXP, who did not hesitate to help me, offering their valuable advice. I would like to thank Hans van Walderveen for his help and explanations about layer mapping between GDSII and LEF. Special thanks go also to Theo Beelen for his valuable discussions and feedback about the algorithm for the layout consistency checker. I also thank Andries van der Veen for his valuable help and discussions about the redhawk library format and the proper implementation of its checkers.

Deepest gratitude is also due to Matthias Koefferlein, the developer of the tool "Klayout - Layout Viewer and Editor", for his keen help in the conversion of binary GDSII files into readable ASCII format, and also his help in flattening the hierarchy of cells in GDSII format to match the flat hierarchy in LEF.

I would also like to convey thanks to Bob Stein (who is now an independent consultant specializing in hyper-useful user interfaces) for his help and valuable information about solving the Point-In-Polygon (PIP) problem during the implementation of our layout consistency checker algorithm.

I would like to thank prof.dr.ir. A.J. van der Veen , dr.ir. Nick van der Meijs , dr.ir. Zaid Al-Ars , ir. Eric Seelen and dr.ir. Philippe Soulard for their valuable time spent in my thesis defence committee.

I would also like to express my sincerest gratitude to NXP semiconductors for hosting this thesis work at its facilities in Eindhoven. The cheerful environment and friendly attitude of everyone in the company helped me a lot to adapt to the new city and environment during my stay in Eindhoven for the thesis period.

Finally I am truly and sincerely thankful for my family for supporting me every step of the way on continuing my studies in Delft University of Technology. Special thanks goes to my father, who has always encouraged me to do my best during my studies, and encouraged me on continuing my studies abroad despite his illness, but sadly he will not be able to enjoy the results with me for he passed away towards the middle of my thesis work. I dedicate this thesis work to him.

Ahmad Hamdy Elsayed Delft, The Netherlands 21 September 2012

| Abstract v<br>Acknowledgments vii |      |        |                                                           |    |  |  |   |

|-----------------------------------|------|--------|-----------------------------------------------------------|----|--|--|---|

|                                   |      |        |                                                           |    |  |  | 1 |

|                                   | 1.1  | Motiva | ation                                                     | 1  |  |  |   |

|                                   |      | 1.1.1  | Low Power in System on Chip (SoC) designs                 | 1  |  |  |   |

|                                   |      | 1.1.2  | Wide Range of Applications                                | 2  |  |  |   |

|                                   |      | 1.1.3  | Effective Low Power Management                            | 3  |  |  |   |

|                                   | 1.2  | •      | t Sketch                                                  | 4  |  |  |   |

|                                   | 1.3  | Thesis | Overview                                                  | 5  |  |  |   |

| <b>2</b>                          | Low  | -Powe  | r Design                                                  | 7  |  |  |   |

|                                   | 2.1  |        | ower Design Techniques                                    | 9  |  |  |   |

|                                   |      | 2.1.1  | Power Shut Off (PSO)                                      | 9  |  |  |   |

|                                   |      | 2.1.2  | Multiple Supply Voltage (MSV)                             | 12 |  |  |   |

|                                   |      | 2.1.3  | Multiple Threshold Voltage                                | 13 |  |  |   |

|                                   |      | 2.1.4  | Dynamic Voltage & Frequency Scaling (DVFS)                | 13 |  |  |   |

|                                   |      | 2.1.5  | Other Low-Power Techniques                                | 14 |  |  |   |

|                                   | 2.2  | Standa | ard Cell Library Views                                    | 14 |  |  |   |

|                                   | 2.3  |        | tency Across Different Library Views                      | 15 |  |  |   |

|                                   | 2.4  |        | ary                                                       | 16 |  |  |   |

| 3                                 | Libı | arv C  | heckers                                                   | 17 |  |  |   |

|                                   | 3.1  |        | sted Approaches                                           | 17 |  |  |   |

|                                   |      | 3.1.1  | Using Cadence's Abstract Generator Tool                   | 17 |  |  |   |

|                                   |      | 3.1.2  | Implementing an Independent Tool                          | 18 |  |  |   |

|                                   | 3.2  | Checke | ers Implemented                                           | 18 |  |  |   |

|                                   |      | 3.2.1  | Cell Name Consistency Checker                             | 19 |  |  |   |

|                                   |      | 3.2.2  | Cell Availability Checker                                 | 20 |  |  |   |

|                                   |      | 3.2.3  | Pin Consistency Checker                                   | 20 |  |  |   |

|                                   |      | 3.2.4  | Layout Consistency Checker                                | 20 |  |  |   |

|                                   | 3.3  | Prepar | ations for the tool                                       | 21 |  |  |   |

|                                   |      | 3.3.1  | Converting GDS Binary Files into Readable ASCII Files     | 21 |  |  |   |

|                                   |      | 3.3.2  | Converting Redhawk Binary Files into Readable ASCII Files | 22 |  |  |   |

|                                   |      | 3.3.3  | Building Parsers                                          | 22 |  |  |   |

|                                   |      | 3.3.4  | Building Layer Mapper for the Layout Consistency Checker  | 23 |  |  |   |

|                                   |      | 3.3.5  | Miscellaneous Checker options                             | 23 |  |  |   |

|                                   | 3.4  | Result | S                                                         | 24 |  |  |   |

|                                   |      | 3.4.1  | Cell Name Consistency Checker                             | 24 |  |  |   |

|                                   |      | 3.4.2  | Cell Availability Checker                                 | 25 |  |  |   |

|                                   |      | 3.4.3  | Pin Consistency Checker                                   | 25 |  |  |   |

|              | 3.5             | 3.4.4    Run time    26      Summary    26                                                                                                     |  |  |  |  |  |

|--------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 4            | Lay             | ayout Consistency Checker Algorithm                                                                                                            |  |  |  |  |  |

|              | 4.1             | Problem Formulation                                                                                                                            |  |  |  |  |  |

|              | 4.2             | Explored Algorithms                                                                                                                            |  |  |  |  |  |

|              |                 | 4.2.1 Corner Points' Inclusion                                                                                                                 |  |  |  |  |  |

|              |                 | 4.2.2 Polygon Overlap and Area Subtraction                                                                                                     |  |  |  |  |  |

|              |                 | 4.2.3 Crossing Points and Centre Inclusion                                                                                                     |  |  |  |  |  |

|              | 4.3             | Implementation Algorithm: Grid Formation and Centre Inclusion 32                                                                               |  |  |  |  |  |

|              | 1.0             | 4.3.1 Steps of the algorithm                                                                                                                   |  |  |  |  |  |

|              |                 | 4.3.2 Ray Casting Algorithm for PIP problem                                                                                                    |  |  |  |  |  |

|              |                 | 4.3.3 Implementation: Sneak peek                                                                                                               |  |  |  |  |  |

|              |                 | 4.3.5       Implementation: Sheak peek       50         4.3.4       Testing Examples       36                                                  |  |  |  |  |  |

|              |                 |                                                                                                                                                |  |  |  |  |  |

|              | 4 4             | 0                                                                                                                                              |  |  |  |  |  |

|              | 4.4             | Results                                                                                                                                        |  |  |  |  |  |

|              | 4.5             | Summary $\ldots \ldots 40$                          |  |  |  |  |  |

| <b>5</b>     | Low             | -Power Design Techniques Experiment 41                                                                                                         |  |  |  |  |  |

|              | 5.1             | Power Techniques Used                                                                                                                          |  |  |  |  |  |

|              | 5.2             | Design Description                                                                                                                             |  |  |  |  |  |

|              |                 | 5.2.1 Baseline Design                                                                                                                          |  |  |  |  |  |

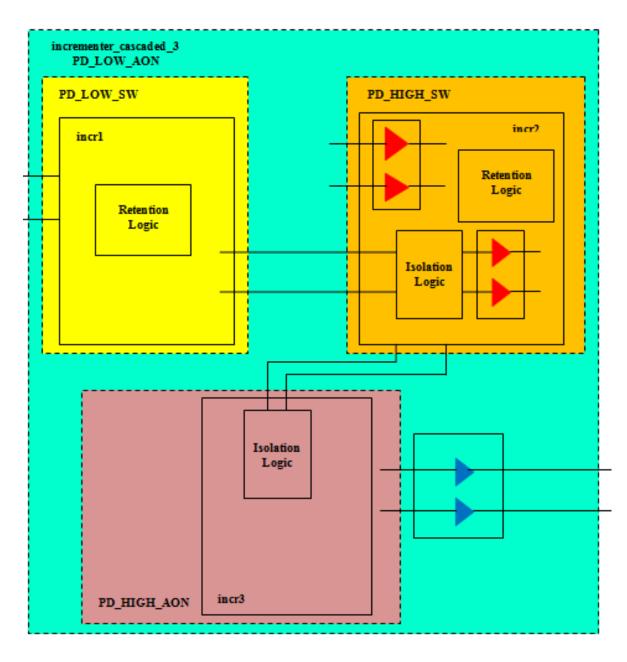

|              |                 | 5.2.2 Using PSO low-power technique                                                                                                            |  |  |  |  |  |

|              |                 | 5.2.3 Using MSV low-power technique                                                                                                            |  |  |  |  |  |

|              |                 | 5.2.4 Using PSO and MSV low-power techniques                                                                                                   |  |  |  |  |  |

|              | 5.3             | Libraries used for Implementation                                                                                                              |  |  |  |  |  |

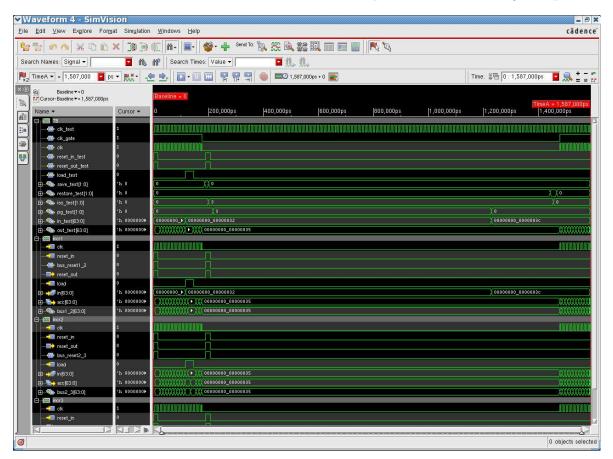

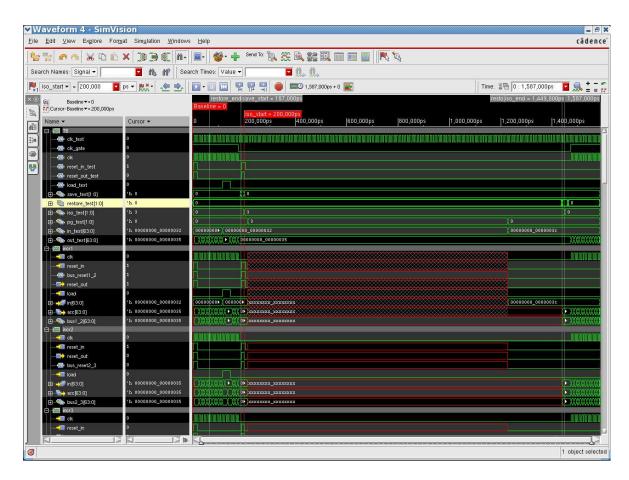

|              | 5.4             | Test Vectors                                                                                                                                   |  |  |  |  |  |

|              | 5.5             | Experimental Results                                                                                                                           |  |  |  |  |  |

|              | 0.0             | 5.5.1 Baseline Results                                                                                                                         |  |  |  |  |  |

|              |                 | 5.5.2 PSO Results                                                                                                                              |  |  |  |  |  |

|              |                 | 5.5.3 MSV Results                                                                                                                              |  |  |  |  |  |

|              |                 |                                                                                                                                                |  |  |  |  |  |

|              | FC              |                                                                                                                                                |  |  |  |  |  |

|              | 5.0             | Comparison with Baseline                                                                                                                       |  |  |  |  |  |

|              |                 | 5.6.1 Baseline VS PSO                                                                                                                          |  |  |  |  |  |

|              |                 | 5.6.2 Baseline VS MSV $\ldots$ 62                                                                                                              |  |  |  |  |  |

|              |                 | 5.6.3 Baseline VS PSO+MSV $\ldots$ 63                                                                                                          |  |  |  |  |  |

|              | 5.7             | Recommendations for the Efficient Usage of Low-Power Techniques 64                                                                             |  |  |  |  |  |

|              | 5.8             | Summary $\ldots \ldots \ldots$ |  |  |  |  |  |

| 6            | Con             | Conclusion 67                                                                                                                                  |  |  |  |  |  |

|              | 6.1             | Summary 67                                                                                                                                     |  |  |  |  |  |

|              | 6.2             | Future Work                                                                                                                                    |  |  |  |  |  |

| $\mathbf{A}$ | Test            | bench Code 69                                                                                                                                  |  |  |  |  |  |

| Bi           | Bibliography 72 |                                                                                                                                                |  |  |  |  |  |

|              | 12 12           |                                                                                                                                                |  |  |  |  |  |

| $1.1 \\ 1.2$                                                                          | SoC Power Density                                                                                              | $2 \\ 3$                                                                                               |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6 \\ 2.7$                                       | Dynamic power in CMOS                                                                                          | $7\\8\\10\\11\\12\\12\\16$                                                                             |

| 3.1                                                                                   | Block diagram of the Library Checker tool                                                                      | 19                                                                                                     |

| $\begin{array}{c} 4.13 \\ 4.14 \\ 4.15 \end{array}$                                   | Grid Algorithm - Testing Example 2                                                                             | $\begin{array}{c} 29\\ 30\\ 31\\ 31\\ 32\\ 33\\ 34\\ 34\\ 35\\ 37\\ 37\\ 37\\ 38\\ 38\\ 38\end{array}$ |

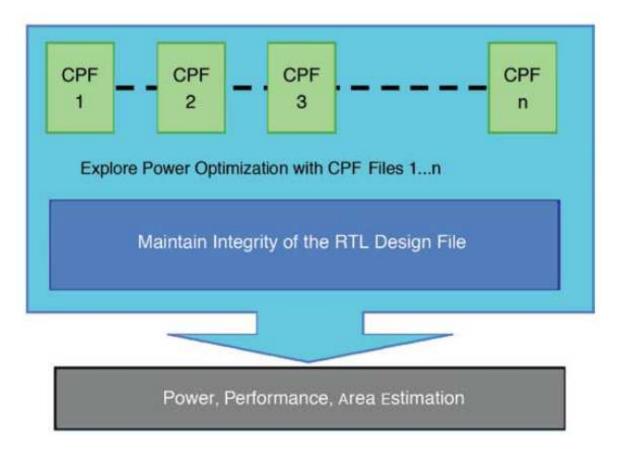

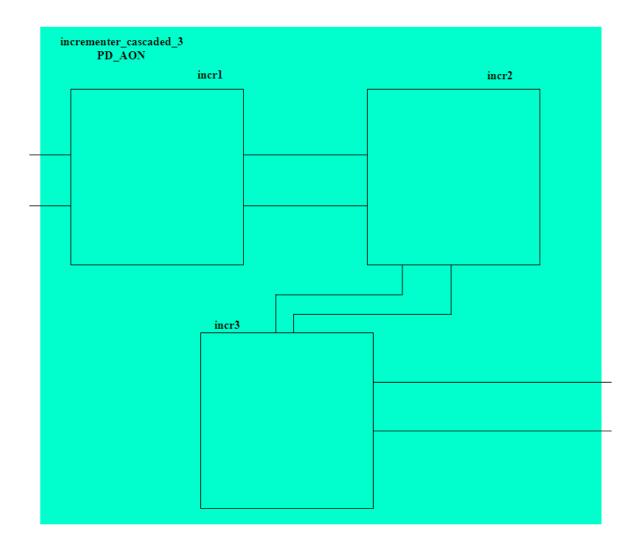

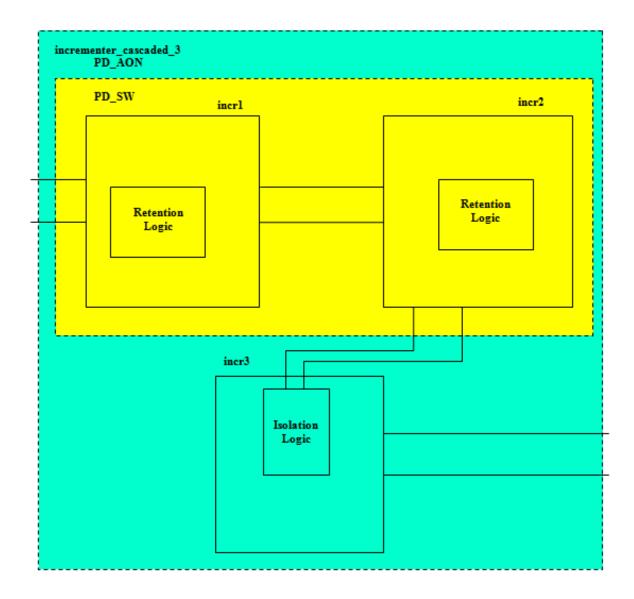

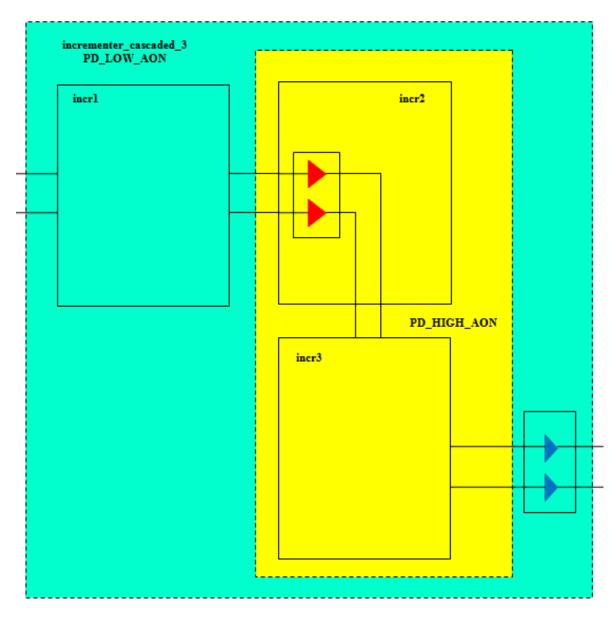

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12$ | CPF-enabled flow: Power is connected in a holistic manner Exploring power intent with CPF while preserving RTL | $\begin{array}{c} 42 \\ 43 \\ 45 \\ 46 \\ 48 \\ 49 \\ 51 \\ 52 \\ 53 \\ 57 \\ 58 \\ 59 \end{array}$    |

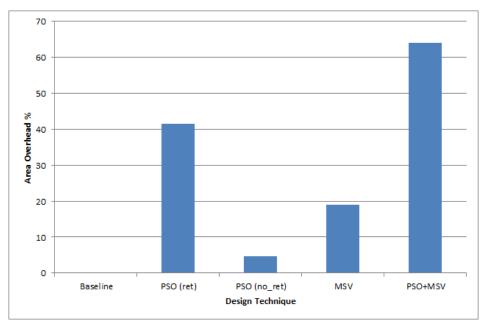

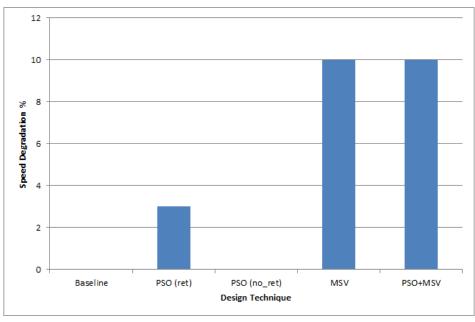

| 5.13                                                                                  | Total energy consumption in different designs                                                                  | 60<br>61                                                                                               |

| 5.1 | Incrementer design organization in PSO     | 46 |

|-----|--------------------------------------------|----|

| 5.2 | Incrementer design organization in MSV     | 47 |

| 5.3 | Incrementer design organization in PSO+MSV | 49 |

| 5.4 | Baseline Power Results                     | 54 |

| 5.5 | PSO (using retention) Power Results        | 55 |

| 5.6 | PSO (using no retention) Power Results     | 55 |

| 5.7 | MSV Power Results                          | 55 |

| 5.8 | PSO+MSV Power Results                      | 56 |

|     |                                            |    |

1

In this chapter, we give an introduction about the importance of low-power design in our life these days, and how reducing the power reflects on our daily use of electronic products. We also give an overview about how the rest of this thesis work is organized and presented.

## 1.1 Motivation

Battery operated devices (cell phones, tablets, laptops) have an increasing demand on energy. And despite the efforts that have been made in researching new battery technologies to cover this demand, the need for low-power designs became a necessity, since battery capacity doubles approximately every 10 years according to Jan Rabaey [1] (that is 3-7% every year depending on the introduction of new technologies); and such growth lags behind *Moore's law* (which demands doubling the computational complexity every 18 months), and the resulting need for more energy resources to feed those hungry devices. The computational density of these devices, and hence their power usage (for computations and cooling), is of growing importance.

From a design perspective, energy usage can be optimized at different levels of abstraction starting from the system and RTL description level, reaching to the circuit level. Major gains can be achieved in reducing energy and power consumption of devices at each level of these levels; and due to the importance of low-power design, considering the direct impact it has on individuals (battery life) and industries (cooling costs), design for low-power is becoming increasingly important in the IC-design industry, making it a key competitive metric in this field, beside the usual metrics such as the performance (throughput, latency and frequency) and costs (area and packaging), which have been traditionally grabbing the major portion of attention of the designers.

## 1.1.1 Low Power in System on Chip (SoC) designs

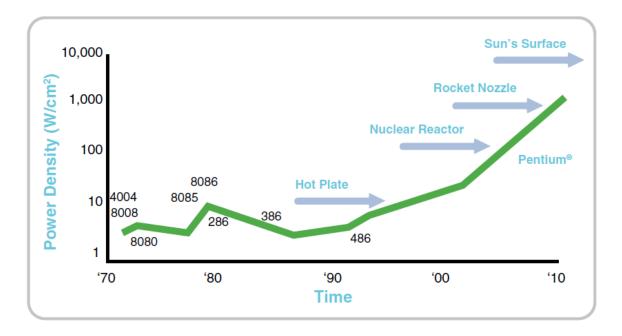

From the previous discussion in Section 1.1, we can see that managing energy is one of the most important concerns nowadays. As the power density of SoC increases at such an alarming rate (as revealed by Figure 1.1), power management has become one of the major design concerns in SoC design. This has been pointed out by Fred Pollack of Intel as early as 1999 in his keynote at MICRO-32 [2].

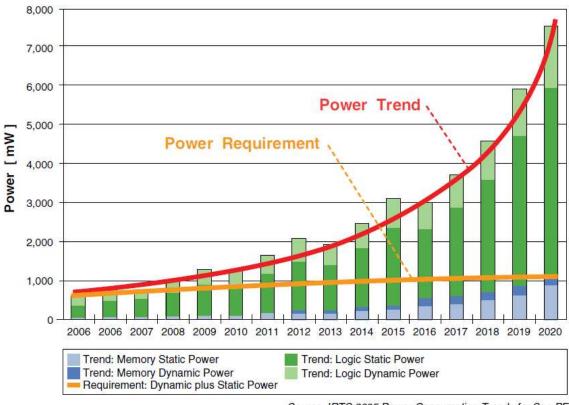

There is an increasingly widening gap between the power density trend and the power design requirements, as illustrated in Figure 1.2. Aveek Sarkar from *Apache Design Solutions Inc.* explains this figure in his article "An RTL to GDSII approach for low power design: A design for power methodology" [3] as follows: the red curve illustrates the increasing levels of power that a design generates to meet advanced func-

Figure 1.1: SoC Power Density. Courtesy Intel Corporation [2]

tionality needs (assuming no low power approaches are used), versus the yellow curve that bounds the maximum power consumption allowed in such systems (as specified by power budgets for these systems to achieve operational and standby power targets). This wide gap represents a huge problem for the designers of electronic products (wired and wireless) nowadays. The graph also shows that more design efforts should be directed towards managing power, which will certainly have a direct impact on engineering productivity, as it impacts schedules and risks for meeting deadlines and keeping pace with the fast moving demands of the market.

#### 1.1.2 Wide Range of Applications

The explosive growth of applications depending mainly on batteries also made power management an inevitable must. Quoting *Silicon Integration Initiative Inc. (Si2)* in their book "A Practical Guide to Low-power Design" [4]: today's portable products are expected not only to be small, cool, and lightweight, but also to provide extremely long battery life; and even wired communications systems must pay attention to heat, power density and low-power requirements. Jan Rabaey [1] mentioned that in the year 2000, 400 Millions of personal computers worldwide were being used, which was assumed to consume 0.16 Tera kWh per year, the power equivalent to 26 nuclear power plants; and this needed over 1 Giga kWh per year just for cooling. He also talked about centralized data centres, and explained (quoting Luis Barosso from Google) that the cost of a data centre is determined solely by the monthly power bill, not by the cost of hardware or maintenance. This bill results from both the power dissipation in the electronic systems and the cost of removing the dissipated heat –that is, air conditioning. All of this further proves that power management is becoming a necessity for wired electronics as

Source: IRTS 2005 Power Consumption Trends for Soc-PE

Figure 1.2: IC power trends: actual vs. specified. [3]

much as it is a must for wireless electronics. Si2 also categorizes the products requiring low-power management in their book [4] as follows:

- 1. Consumer, wireless, and handheld devices: cell phones, personal digital assistants (PDAs), MP3 players, global positioning system (GPS) receivers, and digital cameras.

- 2. Home electronics: game consoles for DVD/VCR players, digital media recorders, cable and satellite television set-top boxes, and network and telecom devices.

- 3. Tethered electronics such as servers, routers, and other products bound by packaging costs, cooling costs, and Energy Star requirements supporting the Green movement to combat global warming.

#### 1.1.3 Effective Low Power Management

Many power reduction efforts have been targeting low levels of abstraction in the design (circuit level); this has been sufficient for a number of years, since managing power at low abstraction levels has been paying off, reducing the power within acceptable limits; however, an effective power and energy management for a System-on-Chip must start at earlier stages of the design, as early as the system and design-architecture phases. Standard cell methodology plays an important role in implementing designs with mostly digital-logic features. As explained by Wikipedia [5], "cell-based methodology (the general class to which standard cells belong) makes it possible for one designer to focus on the high-level (logical function) aspect of digital design, while another designer focuses on the implementation (physical) aspect".

In order to be able to apply low-power design techniques (some of which are discussed in later chapters), standard cells have to be adapted to enable this application, and also new cells (such as retention and isolation cells, which are discussed later in more details) have to be added to the old standard cell libraries. Caution must be paid in making sure that standard cells have consistent descriptions and interfaces across all library formats (discussed in later chapters) present in the standard cell library, since any inconsistency that may exist across any of those library views can cause serious troubles for chips, ones that might not even be discovered until the chip is already put into production, and then the costs for fixing the design flaw resulting from the inconsistency across library views would be enormous (not to mention losing credibility of design companies at their customers). All this creates the need for developing *Library Checker* tools, which will make sure all library views of standard cells are consistent, to avoid the risk of design flaws for something that can be fixed in advance.

## 1.2 Project Sketch

The main contribution of this thesis work will be in the field of standard cell library checking. Due to the huge size of standard cell libraries, and the new libraries frequently produced following new process technologies, the process of checking these libraries manually became an impossible task, and this raised the need for automated tool that does the job. This will be the primary part of this thesis work -building an automatic tool which will check the different views of libraries and make sure those views are all consistent for all the standard cells in those libraries, and report any missing cells or attributes or any inconsistency that might be found. A number of library views (explained more in Section 2.2) have been checked for consistency, namely:

- GDSII

- LEF

- Liberty

- Verilog

- Netlist (CDL)

- Redhawk (APL)

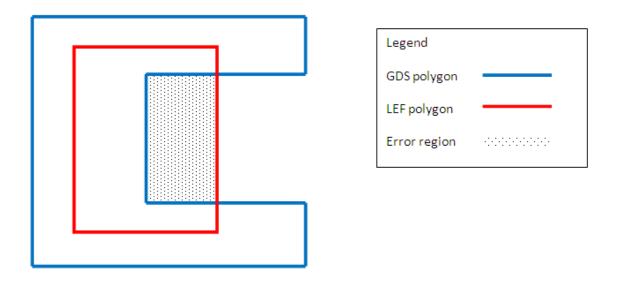

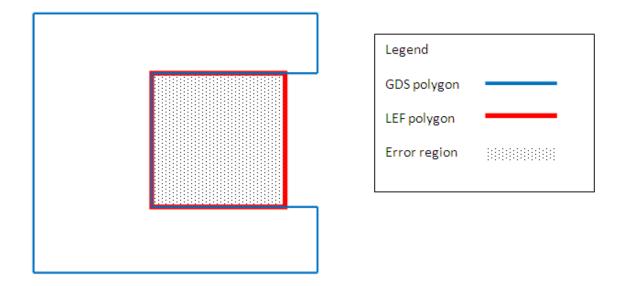

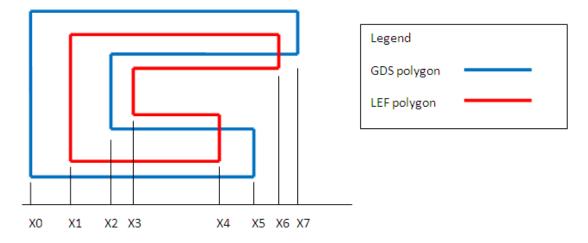

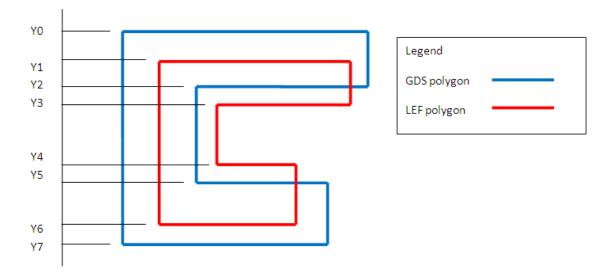

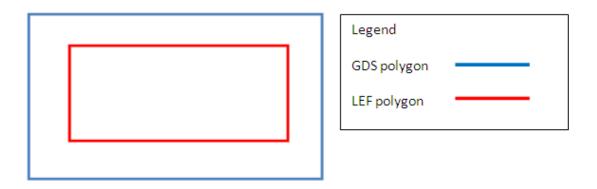

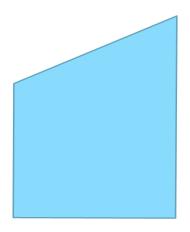

The most important and the highest weight checker is the layout-consistency-checker (LEF-GDSII checker), since it requires a lot of file manipulation and the development of a new algorithm to compare geometrical shapes. This checker (as will be discussed

in more details in Chapter 3 & Chapter 4) mainly checks the consistency and matching of the layout of pins in the two formats: LEF and GDSII. What we need to do for checking the consistency of layers between LEF and GDSII is to check that all of the polygons representing the layout of each pin in LEF are completely included inside the corresponding GDSII polygons for each layer of each pin in each standard cell. The approach for such a checker (from algorithm to implementation) is presented and discussed. A second part of the thesis work employs some of the standard cells (checked by the checker) from one of the recent standard cell libraries in a simple low-power incrementer design, using two of the most common low-power design techniques, and comparing the power figures with the baseline design (the one that does not use any lowpower design techniques), in order to assess the effectiveness of these cells in achieving the low power intents described by the low-power techniques used.

## 1.3 Thesis Overview

The organization of the report is as follows: some background about the most common low-power design techniques and different library views is given in Chapter 2. Chapter 3 discusses the approaches suggested to implement the *Library Checker* tool, and some details about preparations for this tool; it also talks more about the different types of checkers implemented in the *Library Checker* tool, and results from running the tool on existing standard cell libraries. Chapter 4 presents the algorithm for implementing the Layout Consistency Checker. Chapter 5 summarizes the low-power incrementer design experiment, using actual standard library cells (checked by the *Library Checker* tool) to assess the effectiveness of low-power techniques in reducing power consumption, and the ability of these standard cells in achieving low-power design intents and properly implementing low-power techniques. At the end, conclusions and possible future work are discussed in Chapter 6. In order to be able to reduce the power consumption in designs, we have to be aware of the sources of power dissipation. Equation (2.1) shows the main factors contributing to power dissipation. This equation reveals the main components of the *total power* dissipation in CMOS SoCs as: *dynamic power* and *leakage power*.

$$Power = P_{switching} + P_{short-circuit} + P_{leakage}$$

(2.1)

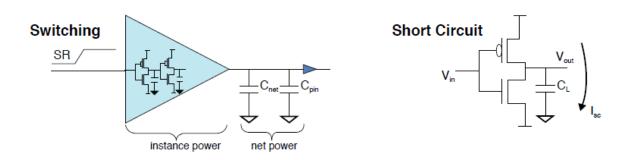

Dynamic power is mainly the sum of switching power and short-circuit power. The former comes from charging or discharging of internal gate capacitances and net capacitances, and thus it depends mainly on the switching activity, switching frequency, supply voltage and effective capacitance, as shown in (2.2); while the latter is dissipated as a result of the instantaneous short-circuit connection between the supply voltage and the ground at the switching-time of the gate, and thus depends on the switching activity, the switching frequency, the supply voltage and the amount of short-circuit current, as shown in (2.3). Figure 2.1 illustrates the two components of dynamic power consumption in CMOS.

$$P_{switching} = \alpha \times f \times V_{dd}^2 \times C_{eff} \tag{2.2}$$

$$P_{short-circuit} = \alpha \times f \times V_{dd} \times I_{sc}$$

$$\tag{2.3}$$

where  $\alpha$  is the switching activity, f is the switching frequency,  $V_{dd}$  is the supply voltage,  $C_{eff}$  is the effective capacitance and  $I_{sc}$  is the average short-circuit current during switching.

Figure 2.1: Dynamic power in CMOS. Source: A Practical Guide to Low-Power Design [4]

As for the leakage power, this basically depends on the supply voltage  $V_{dd}$ , the threshold voltage  $V_{th}$  and the sizing (W/L) of the transistor; this can be observed in (2.4), which represents the value of the subthreshold leakage current for a MOSFET

device (as explained in [6]), the most important component contributing to leakage in CMOS.

$$I_{SUBTH} = I_0 \times e^{\frac{V_{gs} - V_{th}}{nV_T}} \times [1 - e^{\frac{-V_{ds}}{V_T}}]$$

(2.4)

where  $I_0 = \frac{W \times \mu_0 \times C_{ox} \times V_T^2 \times e^{1.8}}{L}$ ,  $V_T = \frac{K \times T}{q}$  is the thermal voltage,  $V_{th}$  is the threshold voltage,  $V_{ds}$  and  $V_{gs}$  are the drain-to-source and gate-to-source voltages respectively. W and L are the effective transistor width and length, respectively.  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the carrier mobility and n is the subthreshold swing coefficient and is given by:  $n = 1 + \frac{C_D}{C_{OX}}$  (according to [7]), where  $C_D$  is the depletion channel region capacitance per unit area.

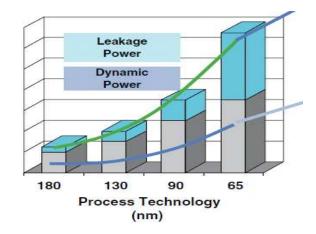

With the shrinking geometrics of process technologies, power management becomes a must for all designs of 90nm and below. At these small geometrics, leakage current becomes of great importance as it becomes comparable with switching currents, which makes it a primary source of power dissipation in CMOS. This is illustrated in Figure 2.2.

Figure 2.2: Process technology vs. leakage and dynamic power. Source: A Practical Guide to Low-Power Design [4]

In order to be able to reduce power consumption in SoCs, we have to tackle each of the aforementioned parameters of each component contributing to the different types of power consumption. Low-power design techniques work mainly on reducing one or more of these parameters, in order to reduce the two components of power consumption, dynamic and leakage. Keep in mind that leakage currents are becoming of growing importance (with the developments in process technology and the shrinking geometrics of CMOS with each new process technology), which makes low-power design techniques targeting leakage increasingly important at such small geometrics. We will present some of the common low-power design techniques in the rest of this chapter, along with some definitions for the different views in standard cell libraries, which contain the cells helping to put those low-power design techniques in action.

The organization of the chapter is as follows: some common Low-Power Design Techniques are presented in Section 2.1. Next, important Standard Cell Library Views are explained in Section 2.2. Afterwards, the importance of *consistency* across different library views, and the impact of inconsistencies on the design cycle are discussed in Section 2.3. Finally, a summary of the chapter is presented in Section 2.4.

## 2.1 Low-Power Design Techniques

As discussed in the introduction, reducing power consumption requires targeting one or more parameters constituting the different components contributing to the total power consumption in a SoC design. In this section we discuss some of the most important low-power techniques, along with the parameters they tackle.

## 2.1.1 Power Shut Off (PSO)

This low power technique is considered the most effective in reducing power consumption of the design, and it can be applied at early stages of the design (as early as the RTL level). It allows the designer to completely shut down certain blocks (that are not in use for a certain period of time) in the design in order to save their power consumption, and consequently, this technique greatly reduces the static (leakage) power consumption, targeting the  $V_{th}$  parameter.

Having a good idea about the activity figures of instances and functional blocks inside the design, designers can divide the design into different power domains according to their activity, and can completely switch off any of these power domains (whenever they have no activity), which will drastically reduce the power consumption of the design. Specific power-down and power-up sequences (which are explained shortly) need to be followed in order to guarantee the correct functionality of the design when using this low-power technique. Incorrect power-up/down sequences are the main cause for failures in low-power SoC designs. Power sequences must be aggressively verified by verification engineers in order to make sure the design functions properly during power down periods (with the powered-down switchable power domains), and also that the design continues to function as expected on powering up the switchable power domains in the design.

Deploying this low-power design technique requires the usage of special low-power cells, all of which should be readily available in the standard cell library. These are discussed in the following part, along with the correct power-down & power-up sequences for correct functionality of the design.

## 2.1.1.1 Power Switch Cells (Power Gates)

In a design with power switching, either header or footer type power switch cells are required to supply power for cells that can be powered down. A header type cell connects the power rail (VDD) to the power pins of the cells. A footer type cell connects the ground rail (VSS) to the ground pins of the cells. An enable signal controls the connection of the switch to the respective power or ground rail.

The number of power switch cells inserted into the design must be properly chosen during design time to satisfy IR drop and current density requirements of the design, since an excessive number of power switch cells will waste the silicon area (and consequently increase the cost of the chip), and also a small number of switch cells might cause a big amount of rush current (the maximum, instantaneous input current drawn by an electrical device when first turned on [8]) to flow through the switches at power-up. Obviously, there will be some power overhead for the insertion of this kind of cells in a low-power design because these cells need to be always-on, which is another reason why careful insertion of these cells should be taken into consideration during design. The insertion of such cells also adds some area overhead to the design, and more verification efforts in order to ensure their correct operation in switching the power on & off.

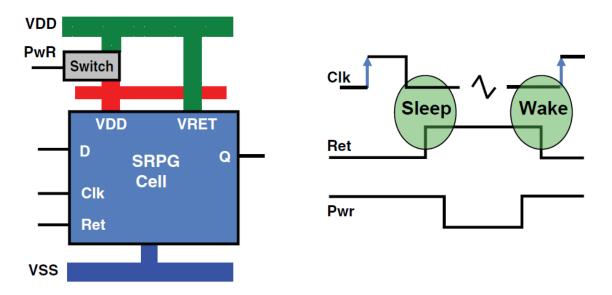

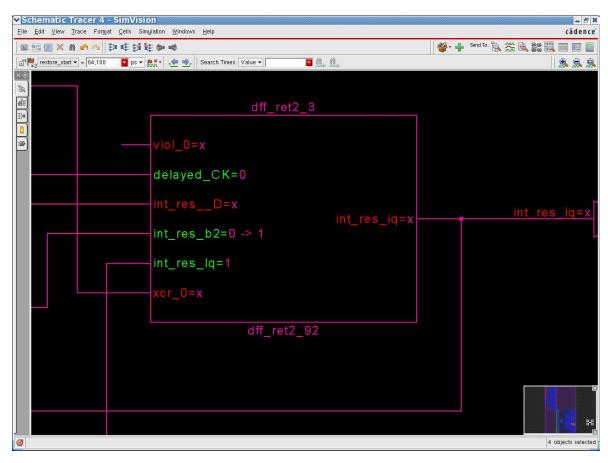

#### 2.1.1.2 Retention Cells

Retention flops are sequential cells that can hold their internal state when the primary power supply is shut down, and that can restore the state when the power is brought back up. These cells are used (replacing normal flops in the design) in order to save the state of the design before going into power down (sleep) mode, so that we can restore the same state of the design after waking up from the sleep mode, and continue the normal operation of the design without affecting its functionality.

A key area of verification in the design cycle is to make sure that this kind of flops are actually retaining the state during power down periods, and are correctly restoring those states at power-up of their respective switchable domains. It is worth mentioning also that this type of cells requires a secondary power supply to be used during power down periods, so as not to lose their state when the primary power supply is shut-off. This is simply illustrated in Figure 2.3.

The insertion of retention cells also has the drawback of adding some power (since they need to be always powered-up) and area overhead to the design, and also needs a great deal of effort for verifying their correct operation when integrated within the design.

Figure 2.3: State Retention Power Gating. Source: A Practical Guide to Low-Power Design [4]

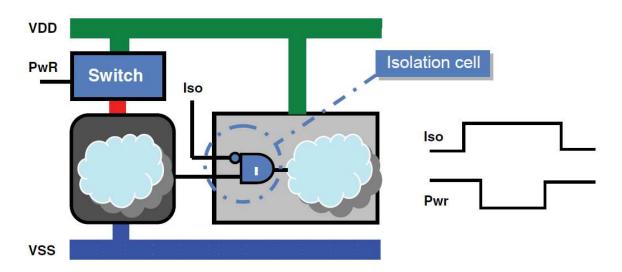

#### 2.1.1.3 Isolation Cells

These are special cells required at the interface between blocks which are shut-down and always-on blocks to prevent floating states of unpowered signals from propagating from a power domain that is powered-down to a power domain that remains on. They clamp the outputs of power-down blocks to a known voltage. These cells can be placed in always-on or switchable regions, and the enable signals of the isolation cells are necessary to isolate floating inputs. Clamp values might be 1,  $\theta$  or *latch* (retaining the final value on the latch before isolation) state. The location where the isolation cells are placed (source or destination block) is usually provided by the standard cell library vendor. Figure 2.4 illustrates a simple example for the usage of an isolation cell. The same arguments (like the ones discussed previously for power-switch and retention cells) for deployment costs also hold here for isolation cells.

Figure 2.4: Isolation cell and Power Gating. Source: A Practical Guide to Low-Power Design [4]

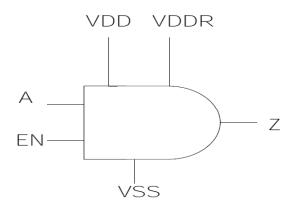

#### 2.1.1.4 Always-On Cells

Always-on cells are cells that remain active even if the main power for the block where they are placed is switched off. This is done through the use of a backup power rail (VDDR in Figure 2.5). These cells are useful for the cases of signals that need to be always active, regardless of the activity of their respective power domains (like reset signals passing through an instance in a switchable power domain and feeding a successive instance in an always-on power domain).

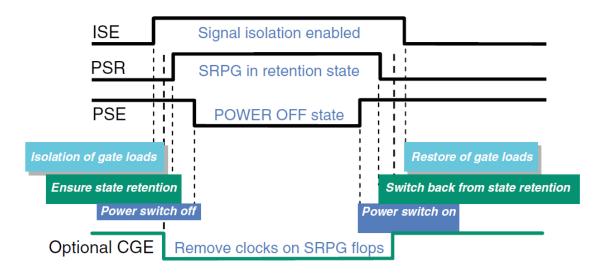

#### 2.1.1.5 Power Cycle Sequence

As we mentioned before, for a correct operation of a design using this low-power design technique, a certain sequence must be followed during the power-down and power-up phases. For power-down, the general sequence followed is: first activating isolation

Figure 2.5: Always-On Cell

(in order to preserve the outputs of switchable power domains at expected values, and prevent floating values from propagating to non-switchable power domains); next, state retention is activated to preserve the states of key control registers in the design that are required to be restored at power-up; and finally power shut-off, as shown in Figure 2.6. For the power-up cycle, the reverse sequence needs to be followed. This way we guarantee the power cycle sequence will complete without any disturbances in the functionality of the design.

Figure 2.6: Power-down/up sequence. Source: A Practical Guide to Low-Power Design [4]

#### 2.1.2 Multiple Supply Voltage (MSV)

In this technique, the design has more than one static voltage source and each domain is assigned the lowest voltage that still makes timing; thus this low-power design technique targets the  $V_{dd}$  parameter. The reduction in the supply voltage has a

squared effect in reducing the dynamic (active) power consumption (as can be observed from (2.2)) and also contributes greatly in reducing the leakage power. However, scaling down the supply voltage has a down-side on degrading the performance, that's why designers use different supply voltages for different parts of the chip depending on their performance requirements, and thus the name: "Multiple Supply Voltage". For the correct application of this low-power design technique, we also need to use special type of low-power cells to guarantee the correct functionality of the design, and in this case, we only need to use *Level-Shifter* cells.

#### Level-Shifter Cells

In a multi-voltage design, a level shifter is required where a signal crosses from one power domain having a certain supply voltage to another one having a different supply voltage. The level shifter operates like a buffer or an inverter with one supply voltage at the input and a different supply voltage at the output. Thus, a level shifter converts the voltage of the signal from one level to another, in order to save the logical value of the signal.

These cells have three categories, namely: up (shifting from low to high voltage), down (shifting from high to low voltage) and up/down level shifters. The placement of these level-shifter cells (whether in the source or the destination power domain) also depends on the constraints imposed by the library-vendor.

#### 2.1.3 Multiple Threshold Voltage

Scaling down the threshold voltage of transistors has a great impact on lowering the delay in CMOS circuits. However, scaling down  $V_{th}$  is accompanied with an exponential increase in the sub-threshold leakage currents. To tackle the problem of high leakage, dual (or multiple)  $V_{th}$  techniques have been proposed. Low- $V_{th}$  cells are used on the critical path of signals where speed is of great concern, while high- $V_{th}$  cells are used on the non-critical paths. That is why standard cell libraries' vendors have to provide libraries that have cells with different threshold voltages. Designers mainly rely on synthesis tools for choosing the suitable  $V_{th}$ -cells from the available multi-threshold library-cells in order to achieve the area and performance targets, while minimizing power dissipation. This technique works on reducing the leakage power, targeting the parameter  $V_{th}$ .

#### 2.1.4 Dynamic Voltage & Frequency Scaling (DVFS)

Dynamic voltage frequency scaling (DVFS) reduces the power in the chip by scaling down the voltage and frequency when peak performance is not required. Thus, this technique mainly aims at reducing dynamic power consumption, and a bit of leakage power consumption, targeting mainly f and  $V_{dd}$  parameters. A design using DVFS can be seen as a special case of an MSV design operating in multiple design modes.

• In a pure MSV design different portions of the design operate on different voltages and these portions remain operating at their respective operating voltage.

• In a DVFS design, in addition some portions can dynamically change to other voltages depending on the design mode or can even be switched off.

Consequently, a DVFS design must satisfy different constraints in different design modes. DVFS designs require variable power supply(ies) that can generate the required voltage levels with minimal transition energy losses and a quick voltage transient response. When scaling the voltage, the frequency must be scaled accordingly to meet signal propagation delay requirements. A power scheduler is usually used to compute the appropriate frequency and voltage levels needed to execute the various applications.

## 2.1.5 Other Low-Power Techniques

Multiple other low-power design techniques exist in the continuous efforts of reducing the power consumption of SoC designs. Some of them are:

- Clock Gating: in which clock signals are disabled at specific times where there is no activity to reduce the dynamic power consumption, targeting the parameter *α*.

- Body Biasing: substrate is biased to a voltage different from  $V_{dd}$  in PMOS, and to a voltage different from  $V_{ss}$  in NMOS, in order to reduce the leakage power consumption targeting the parameter  $V_{th}$ .

- Operand Isolation: whenever data-path elements are not active, prevent it from switching using an enable signal. This reduces the dynamic power consumption, targeting the parameter  $\alpha$ .

## 2.2 Standard Cell Library Views

It can be easily observed from the previous discussion in Section 2.1 that deploying low-power design techniques requires some adaptations of standard libraries. These adaptations include the addition of new low-power cells (like retention, isolation, and level-shifter cells). Adaptations also include changing the modelling of some cells to achieve low-power, such as: changing the cell-drive strength and supply/bias pin modelling. Standard Libraries have many different views for describing the different attributes of cells. The following section gives more information about the different library views in standard libraries.

- Graphic Database System (GDSII) Format: a binary file format representing planar geometric shapes, text labels, and other information about the layout in hierarchical form. In standard libraries, GDSII files are used to describe the layout of each layer for each pin of the cell.

- Library Exchange Format (LEF): includes the abstract of cells and the rules for routing, but no information about the internal netlist of the cells.

- Liberty Format: liberty is the gate-level modelling technology; an open industry standard for longer than a decade, the liberty library format is used as the library model exchange for timing, noise, power and test behaviour.

- Verilog Format: is most commonly used in the design, verification, and implementation of digital logic chips at the RTL level of abstraction.

- Netlist (CDL) Format: usually conveys connectivity information and provides nothing more than instances, nets, and some attributes (such as 'W' & 'L' of transistors).

- RedHawk (APL) Format: a binary file format that provides an integrated environment for analysing power, noise and reliability issues in SoC designs.

## 2.3 Consistency Across Different Library Views

Different library views have to be consistent in their description and specification of standard cells. Such consistency is represented in checking the following conditions:

- Existence of cells: All functional cells must be present in all library views (formats).

- Consistency of cell names: Each cell must have the exact same name (case-sensitive) across all formats

- Consistency of pin-interface of each cell: Each cell must have the same pin-count and exact pin-names in all library formats; also the modelling of pins (pin type, direction, etc..) must be consistent for each cell across all library formats.

- Matching layout geometrics of pins for each cell: Geometrics of each layer of each pin in each cell has to be matching in formats describing the layout of cells (basically LEF & GDSII formats)

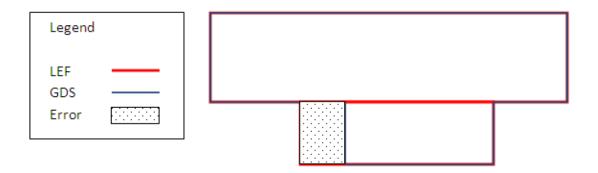

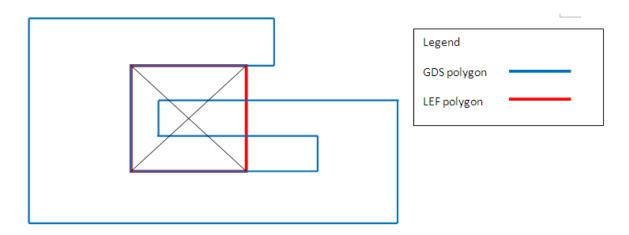

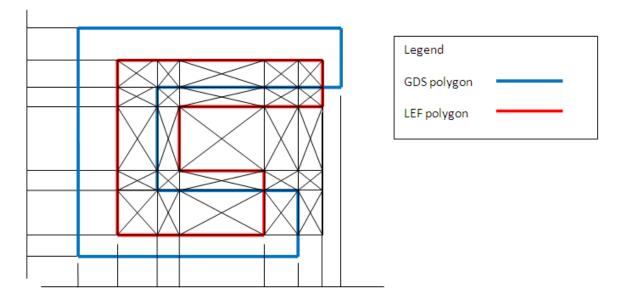

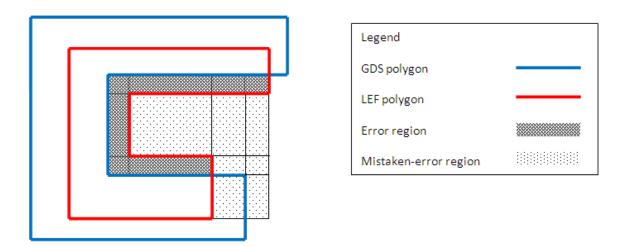

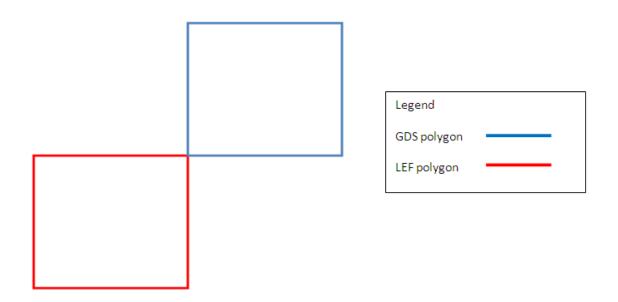

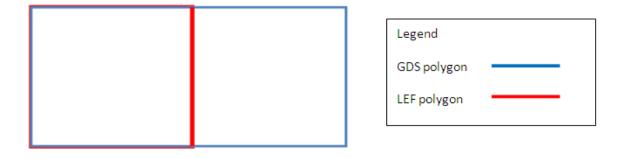

Inconsistencies across the different library views might cause errors during the design cycle at different abstraction levels. Figure 2.7 shows a mismatch in the layout of a standard cell that was caught by our library checker tool; this kind of mismatches can cause serious routing problems. Some of these library-inconsistency problems might not even be caught during verification, and might leak into a design that is already put into production; this might cause the chip to fail when used by the customers, causing a potential loss of reputation and credibility for design companies.

Absence of body-bias pin modelling caused a big design company two major failures last year. In that case there were two different always on cells, one with a separate well for the *PMOS* transistors and another with abutted well. Due to the lack of bias modelling, design tools could not distinguish between the two, and picked (based on smaller area) the wrong one, effectively making the bias pin operate in forward mode around 0.6 volts, creating too much leakage current. So the designer tried to design a low leakage design using low power design techniques, ending up with a design that was actually leaking way more; and this came as a result of lack of consistency of cells' pin-interface. From this discussion, we conclude that the need for a library checker is crucial; one thing that saves a lot of effort hunting for bugs in the design due to inconsistencies in the libraries. And due to the huge and ever-increasing size of libraries, these checkers need to be automated in order to be run directly to check the consistency of libraries provided from library vendors in a simple run. And this reveals the importance of the job done here in this thesis work.

Figure 2.7: Example layout mismatch in one of the libraries checked by our tool

## 2.4 Summary

Various low power design techniques were introduced in this chapter. The deployment of these low-power design techniques requires certain adaptations for standard libraries. A brief overview about the most important library views (formats) was introduced. In the end, the importance of the consistency of the different library formats was discussed, which calls for an immediate action implementing an automated tool to do the librarychecking job, which is the core of this thesis work. The previous discussion in Section 2.3 reveals the importance of verifying the consistency of the description and modelling of standard cells in the different library views. This verification process needs to be automated, the reason for which is the huge size of standard libraries. This initiated the idea for building our *Library Checker*, which is the core of this thesis work, and the main topic of the rest of this chapter and the next one as well.

The organization of the chapter is as follows: an overview about the studied approaches for implementing the Library Checker tool is given in Section 3.1, followed by different types of checkers implemented in the tool given in Section 3.2. Preparations for the tool from manipulating files to building parsers and similar issues are discussed in Section 3.3. Some results from running the checkers are presented in Section 3.4. It is worth mentioning here that this chapter does not discuss the algorithm used for the *Layout Consistency Checker*; this will be discussed in the following chapter -Chapter 4, since this part is of great importance and contains a lot of details. Results for running the *Layout Consistency Checker* are also presented in the following chapter. This chapter ends with a summary about what has been discussed in Section 3.5.

## 3.1 Suggested Approaches

The most important part of the checker tool is the *Layout Consistency Checker*; that's why all the initial thoughts and brainstorming ideas about the implementation of the tool were directed towards finding the best solution to do the layout consistency job between LEF & GDSII. These thoughts are briefly discussed in this section.

## 3.1.1 Using Cadence's Abstract Generator Tool

The first idea that popped in mind when brainstorming about the layout checker was to make sure that this work is not already implemented, and to see if there is a working solution that is readily available already, which could be incorporated inside our Library Checker tool. Doing some research, we came to know about *Virtuoso Abstract Generator* [9] provided by Cadence Design Systems as a part of their tool *Virtuoso Layout Suite*. This tool (as described in the manual) "is a library modelling tool that lets you create abstracts for standard cells, macro blocks, and IOs from detailed layout information in Library Exchange Format (LEF), Design Exchange Format (DEF), and Graphics Design Station II (GDSII) Stream formats". A first look at this looked like it was the proper tool for the job. So we first decided to try this path, which will save us the pain of implementing a new tool that does the job that Cadence's tool does already. However, we found multiple issues when comparing the LEF file produced from *Abstract Generator* and the original LEF file of the library, the most critical of which has to do with discrepancies in the geometry of layers for the power and ground pins between the two files. We tried to tweak the tool's options in order to know the reason for which these differences appeared, but then we decided to drop this path for the following reasons:

- 1. This solution will mainly depend on a tool provided by Cadence, the licence for which is not free, and needs to be purchased from Cadence.

- 2. The dependency of a big part of our Library Checker tool (the *Layout Consistency Checker*) on a non-open-source tool limits the ability for further/special developments, manipulations or enhancements for the tool.

- 3. The complication of usage of *Virtuoso Abstract Generator* as an intermediate step for the implementation of our Library Checker tool was not satisfying.

- 4. Discrepancies of geometries of layers between original LEF and the LEF generated from *Abstract Generator* would not give correct errors about mismatching geometries, and consequently produce bugs which reduce the reliability of the tool.

## 3.1.2 Implementing an Independent Tool

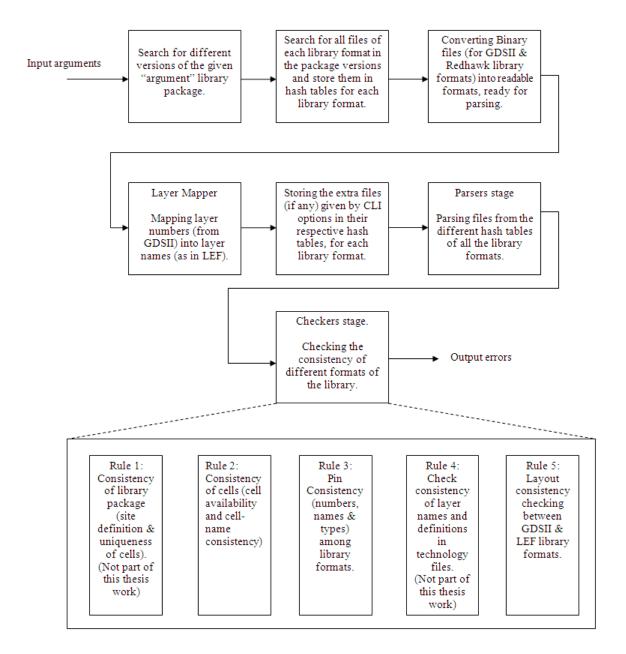

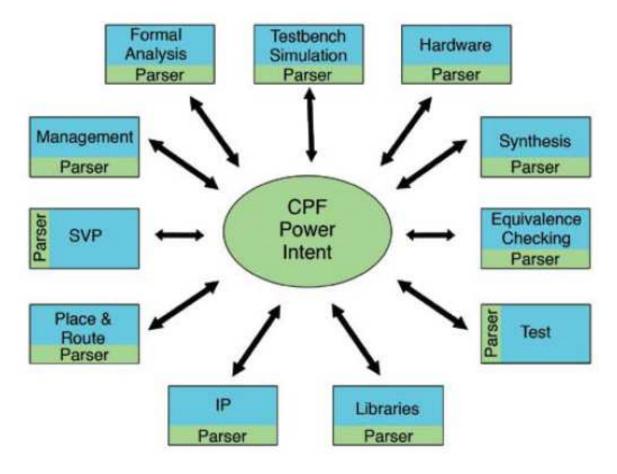

After dropping the direction of using the *Abstract Generator* for checking the consistency of the layout of cells, and getting no good results from further searches for finding a solution to do the layout-consistency-checking job, we decided that implementing the whole tool ourselves will be the best option; especially that there has been already some development in-house (at NXP) for the basis of the *Library Checker* tool, which came as a great aid afterwards in completing our tool. The tool's input arguments should be the path (relative or absolute) to the library package that needs verification, and may also include some optional miscellaneous arguments (discussed in more details in Section 3.3.5). Output of the tool should be a list of errors for the inconsistencies revealed in the library package being checked. Different parts of the *Library Checker* tool are illustrated by the block diagram in Figure 3.1. Numbering the rules of the checker plays an important role in grouping similar errors, and displaying them consecutively (according to the rule number), for better categorization of the output errors of the checker.

## 3.2 Checkers Implemented

The *Library Checker* tool needs to verify the consistency of standard libraries through the verification of the different conditions mentioned in Section 2.3. Based on these conditions, we built various checkers, as explained in the following section. The checkers (as well as the whole tool) are built in Tcl [10], to extend the part of the checker already developed in-house at NXP.

Figure 3.1: Block diagram of the Library Checker tool

#### 3.2.1 Cell Name Consistency Checker

This checker verifies the consistency of the names of different cells across the different views of the standard cell library. In each library view, each cell is given a unique name that gives a hint about the functionality of the cell. This name must be exactly matching to the corresponding name in other library views, including the case-match of the cell name, since a case-mismatch in the cell name will be reported as missing cells by design tools, a scenario that has been reported by designers at NXP for cells having a name-case-mismatch in some standard cell library formats. For each cell in

each view, the checker searches for the same exact name of the cell (case-sensitive) in all other library views; if the exact name was not found, the checker then relaxes the condition and checks that the name does not exist in a different *case*; if the name was found in a different *case*, the checker reports an error that there is a case-mismatch for this cell, and reports which library views have the defect. Otherwise (if the cell name was not found, even with a mismatching case), nothing is displayed. Cell-availability is checked in a separate checker (explained in Section 3.2.2) due to error-tagging purposes (grouping similar errors under the same error-tag to be displayed together).

## 3.2.2 Cell Availability Checker

This checker is very similar to the previous one. It checks the availability of functional cells in all the different library formats. For each cell in each library format, the checker first checks the availability of the same cell (with the exact same name) in all other library formats. If the cell was not found in a specific format, the checker then checks that the name of the cell does not exist in a mismatching-case (to make sure that the cell really does not exist), and if that last check gave positive results, the cell is reported missing in that specific library format where it does not exist.

## 3.2.3 Pin Consistency Checker

This checker verifies the pin-interface of all cells in the library. It basically carries out the following checks:

- 1. Verifying matching number of pins for each cell across all library formats.

- 2. Verifying matching names (exact names) of each pin in each cell across all library formats.

- 3. Verifying the consistent modelling of pins across different library formats. This is done through verifying that supply pins, bias pins, and signal pins have the same functionality and direction in all definitions of the same cell in all the different library formats.

Any pin for any cell that is found missing in any of the library formats is reported along with the name of its respective cell, the library format that has this discrepancy, the version of the library and the library package name. Any modelling inconsistency found (for example a pin defined as a supply pin in one library format, but defined as a signal pin in another) is reported as well.

## 3.2.4 Layout Consistency Checker

Each cell has a number of pins, each of which has a number of layers describing its layout, along with the geometries (coordinates) of these layers. LEF & GDSII are the only two library formats that have this piece of information. This checker verifies matching layouts of cells between the two library formats: LEF & GDSII. This checker is the most important part of our tool, and consumed much time and effort during the

development of the tool. It also contains a lot of details, and that's why it will be further discussed separately in Chapter 4.

# 3.3 Preparations for the tool

In order to be able to build the checkers discussed in Section 3.2, we needed to capture important information such as cell names, names of the pins for each cell and the layout information of each of those pins for each cell in the library. These pieces of information are the basic building blocks upon which the checkers mainly rely to verify the consistency of different library formats. For this purpose, multiple *parsers* were built to help capturing this important information. Some library formats (GDSII and Redhawk) required even some pre-processing in order to convert them into readable formats. All of these details are discussed in the following section.

It is worth mentioning here that the parsers and the checkers and all intermediate file manipulation were built in Tcl, the reason for which was to extend a part of the library checker that has been built already in-house at NXP, and also Tcl's ability to store arrays as hash tables, which was really useful in storing different cells' information which were used by the checkers.

## 3.3.1 Converting GDS Binary Files into Readable ASCII Files

GDSII files are normally binary files. In order to be able to parse those, we had to find a way to convert those binary files, into some readable format, for which a parser could be easily built. Multiple tools were found that do the job, some of which are mentioned below:

- 1. GDS Utilities 1.3, from GB Research [11]. But this solution was dropped because the tool is not free (a licence needs to be purchased), and also the solution works only for the *Windows* platform.

- 2. OwlVision GDSII Viewer [12]. This solution is free, and can be run on all platforms; however it was also dropped for the reason that not all of the GDSII records are supported.

- 3. Glade (GDS, LEF And DEF Editor) [13]. This one was not used because it was more of a *Graphical User Interface* (GUI) tool that is hard to be used in a *Command Line Interface* (CLI).

- 4. LayoutEditor [14]. This one was not used because it was more of a *Graphical User Interface* (GUI) tool that is hard to be used in a *Command Line Interface* (CLI).

- 5. KLayout High Performance Layout Viewer And Editor [15]. This one was found the best tool because it is a free tool that works on all platforms, and could be easily used in the CLI mode. It also produced the most readable output ASCII code representing the GDSII binary files, which made constructing the parsers for reading this output ASCII code really easy.

And thus, we settled on using klayout to do the conversion step from Binary-GDSII into ASCII-GDSII. In order to be able to do this conversion step from within our tool (without having to invoke klayout's user interface), we extracted (with the help of klayout developers) an executable file from the installation package of klayout that can be used directly from within our Tcl scripts to do the conversion.

We also faced another problem in the representation of filler cells in the output ASCII code resulting from klayout's conversion process. Filler cells are used to maintain the Nwell continuity in the standard cell and to fill the gaps in the rows of the standard cell. In the output GDSII-ASCII from klayout, these cells are represented as arrays of an additional smaller cell that is defined implicitly in klayout, but not defined in LEF. So we needed to get rid of those arrays, and get a single definition for the filler cells, to match that in LEF. And this required some tweaking to the source code of klayout in order to produce a definition similar to that in LEF, with no additional cells, and with no arrays. The tweaking was done (with the help of klayout developers) and we managed to produce a definition for filler cells, that corresponds to the one in LEF, which made the job much easier for the layout-checker in verifying the match in the layout for filler cells, between LEF and GDSII.

## 3.3.2 Converting Redhawk Binary Files into Readable ASCII Files

Redhawk is also a library format whose files need some manipulation in order to be parsed easily. Redhawk files are also available in binary format, yet luckily enough, there exists a utility named "aplreader" which can convert binary redhawk files into ASCII files that can be easily parsed afterwards.

#### 3.3.3 Building Parsers

As we previously mentioned in this section's introduction, building parsers for the different library formats is a must in order to facilitate the process of capturing the information required by the checkers in order to do their job. For this purpose, different parsers have been built. Liberty and Verilog (and partly the LEF) parsers were already built by people at NXP, and those have been reused in our tool. The contribution of this thesis work is in building the following parsers:

- 1. LEF parser: this captures the geometries of layers of each pin in the cell, and the names of the different pins in the cell, and stores them in a hash table for each cell in the library.

- 2. GDSII parser: this one parses the GDSII-ASCII file, which is output from the klayout conversion process. It mainly captures the same information as that captured in the LEF parser, for the checker to check the matching between the geometries of pins of the same cell, between LEF and GDSII formats.

- 3. CDL parser: it parses the information about the available pins, and their names from the netlist of each cell.

- 4. Three Parsers for APL Redhawk: these are the *CURRENT*, *CAPACITANCE* & *PWC* parsers; each provides different information about the cell behaviour under

different operating conditions, and each has a different format for the APL file, and that's why we had to build a different parser for each of the three types. The information captured is mainly the names of the pins of each cell in the library (along with the name of the cell), to check the pin-interfacing and the availability of cells and their consistent naming with the rest of the library formats.

#### 3.3.4 Building Layer Mapper for the Layout Consistency Checker

In the GDSII library format, layers (metal, poly-silicon, etc..) are represented as *layer* numbers plus datatype numbers, while text layers are represented as *layer numbers* plus texttype numbers. But this is not the case for the LEF library format, in which layers are represented by their names directly. And hence some mapping was required, in order to translate the layer numbers in GDSII into layer names as in LEF. The mapping file is provided by the library vendor, and has a standard format. A Layer Mapper is built within our tool, which reads in the mapping file provided by the tool vendor, and translates the layer numbers and data/text type from GDSII into layer names (matching those in LEF), so that we can carry out the verification and matching process by the checker.

#### 3.3.5 Miscellaneous Checker options

Some options are also added to the tool for more convenience of usage. One example of these options is the ability to specify certain files to be taken into consideration in the verification process of the library. Normally, the user only specifies the name of the library package(s), and the tool then searches all the versions of the package for all the files of different library formats, in order to be parsed and checked for consistency. But for example, if the library provided by the vendor is missing a certain file that is found at a different location, then these options (built for all library formats that are being checked in the tool) will allow the user to specify the path for that missing file, and then it will be accumulated with the list of files already in the library package, and checked for consistency as well with the rest of the library formats. These options are as follows:

- 1. <-lef "lef\_files">: to specify extra LEF files.

- 2. <-gds "gds\_txt\_files">: to specify extra GDSII files.

- 3. <-liberty "lib\_files">: to specify extra liberty files.

- 4. <-verilog "ver\_files">: to specify extra verilog files.

- 5. <-cdl "cdl\_files">: to specify extra netlist files.

- 6. <-rehawk\_cap "redhawk\_capacitance\_files">: to specify extra redhawk-capacitance files.

- 7. <-redhawk\_cur "redhawk\_current\_files">: to specify extra redhawk-current files.

- 8. <-redhawk\_pwc\_files">: to specify extra redhawk-pwc files.

Another example of extra options is the one that provides the capability to skip checking certain directories for consistency. This option is provided as: <*skip\_directories* "comma-separated-directory-list">. This option is mainly implemented in order to overcome some memory problems that we faced while running the checker on some libraries; the checker complained that there is a memory overflow problem, because of the huge size of the libraries. The important thing is that some of the directories in the library package were just duplications of other files, but with some variations in operating conditions or modelling style, and had nothing to do with the interface description (the main target of our library checker tool). An example for these is liberty files, which have multiple duplications, such as: ECSM, CCS and SI. This option is practical in these cases; we can check those duplicate files sequentially (one at a time, depending on their directories) with the rest of the library formats, in order to overcome the memory problems; and consequently, we implemented this option in order to avoid a potential tool-crash, and to provide a work-around for the memory problem, in case this was a limitation in the run-environment.

# **3.4** Results

As we pointed out previously in this chapter's introduction, the results for running the *Layout Consistency Checker* are presented in the next chapter, along with the algorithm used for implementing this checker.

Here we present some of the results we obtained from running the different types of checkers on the latest *GLOBALFOUNDRIES* 40nm Low-Power (GF40LP) library.

## 3.4.1 Cell Name Consistency Checker

Following is a snippet of the errors produced by this checker:

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_TIE0\_G\_1' in LEF has a name case mismatch with redhawk\_CAP ('seh\_tie0\_g\_1') !

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_TIE0\_G\_1' in LEF has a name case mismatch with redhawk\_PWC ('seh\_tie0\_g\_1') !

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_TIEDIN\_G\_1' in LEF has a name case mismatch with redhawk\_CAP ('seh\_tiedin\_g\_1') !

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_TIEDIN\_G\_1' in LEF has a name case mismatch with redhawk\_PWC ('seh\_tiedin\_g\_1') !

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_DCAP16' in LEF has a name case mismatch with redhawk\_CAP ('seh\_dcap16') !

ERROR 2-2 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_DCAP16' in LEF has a name case mismatch with redhawk\_PWC ('seh\_dcap16') !

Here, we tag the error resulting from this checker with the tag "2-2"; this tagging helps to group similar errors in one place, which is already done by the tool, grouping similar errors and displaying them at once following their error tag. The error shows the mismatch between LEF and Redhawk formats in the naming of some cells (mainly case-mismatch). This error has been causing troubles to designers with design tools complaining about the absence of these cells in redhawk format, because the tools expect the exact same name in all library formats. The error mentions the package (library name) and the version ( $GF40LP\_gf40npkhdst/a02p4$ ), and the expected cell name (for example SEH\_DCAP16 in LEF), and the wrong cell name (seh\_dcap16 in redhawk). This helps the designer to easily spot this kind of errors, and report them to the library vendor or fix them himself as a workaround.

#### 3.4.2 Cell Availability Checker

Here is a snippet of the errors produced by this checker:

ERROR 2-1 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_RAIL3T16' exists in LEF but not in GDS ERROR 2-1 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_RAIL3T16' exists in LEF but not in redhawk\_CAP ERROR 2-1 Package 'GF40LP\_gf40npkhdst/a02p4' Cell 'SEH\_RAIL3T16' exists in LEF but not in redhawk\_PWC

As we can see, we tag the error resulting from this checker with the tag "2-1". The error shows the existence of some filler cells only in the LEF library format, and their absence in other formats (GDSII and some redhawk formats where this kind of cells are expected to be available). The error mentions the package (library name) and the version  $(GF40LP_gf40npkhdst/a02p4)$ , the cell that has the error  $(SEH_RAIL3T16)$ , and the formats having the problem (GDS and redhawk in this example).

#### 3.4.3 Pin Consistency Checker

Following is a snippet of the errors produced by this checker:

ERROR 3-1 Library package 'GF40LP\_gf40npkhdet/a02p3' Bias pin 'VBP' of cell 'EEH\_DCAP1' in LEF is not found in Liberty

ERROR 3-1 Library package 'GF40LP\_gf40npkhdet/a02p3' Bias pin 'VBP' of cell 'EEH\_DCAP1' in LEF not found in GDS

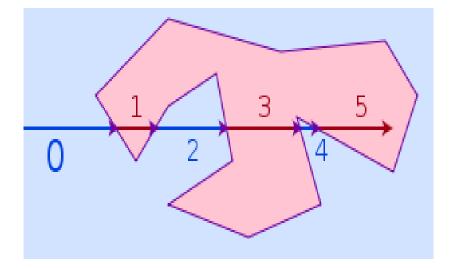

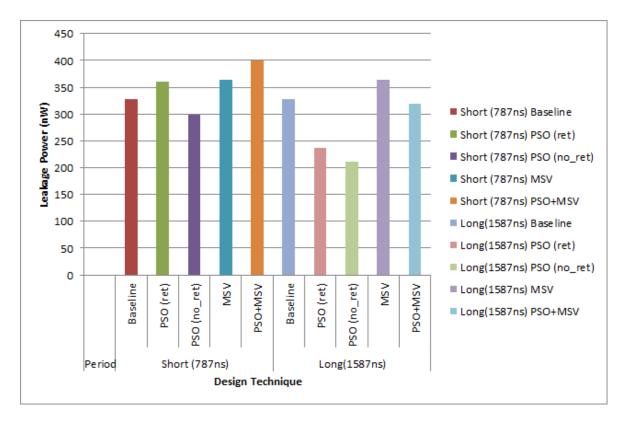

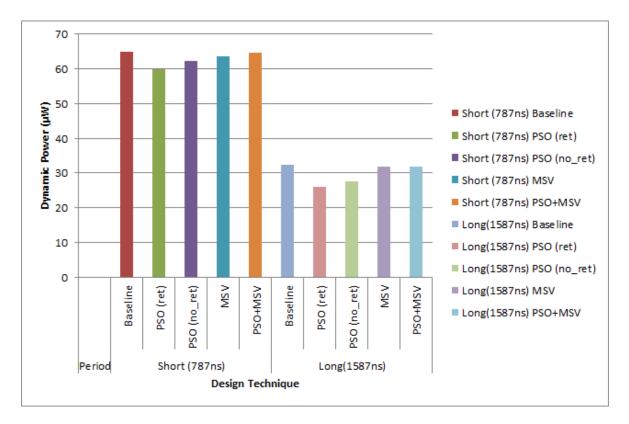

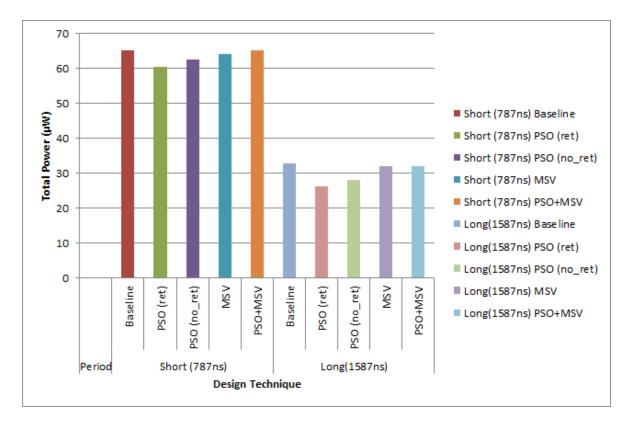

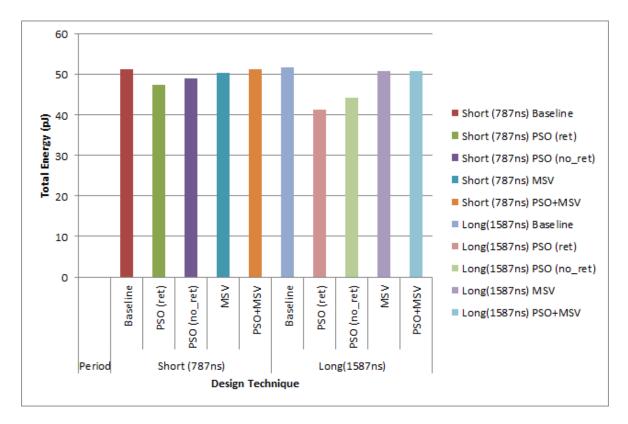

ERROR 3-1 Library package 'GF40LP\_gf40npkhdet/a02p3' Bias pin 'VBN' of cell 'EEH\_DCAP1' in LEF is not found in Liberty