# MSc THESIS

## An Incremental VON-Based Debug System for Commercial FPGA Architecture

Roshan Kumar Gupta

#### Abstract

Electronic companies are increasingly using field-programmable gate arrays in various domains such as application acceleration, complex digital designs or ASIC prototyping. The Verification phase holds a significant place in the FPGA design development process. A key challenge during verification is observability. This is defined as the ability to view all internal states of a circuit. Due to poor observability, a significant portion of designer's effort is spent in this phase, specifically performing the debugging task. A common solution to improve observability is using embedded logic analyzers (ELA) that inserts trace-buffers into the design to record on-chip signal values. When on-chip memory is used for observation it is termed as trace-buffers. This approach has limitations such as slow debug cycles, pre-determining the signals to be traced or using logic resources on FPGA.

This work proposes a new debug system for improving the observability while overcoming the limitations of ELAs. The proposed debug system extends a recent technique referred as virtual overlay network (VON) for commercial FPGA device. This network can be perceived as built on top of initial circuit mapping and multiplexes all circuit signals to the on-chip memory for observation. It overcomes the limitation of commercial debug tools based on ELAs. We investigate the factors that influence the performance of VON for Xilinx Virtex, as it constitutes the core of debug system. We demonstrate that a new bit-stream to program the FPGA connecting hundreds of signals to the on-chip memory can be generated in less than 630 seconds, during debug cycle, for a fairly large circuit having normal re-compilation time of more than 5 hours. The proposed system proves to be a promising way of improving observability and potentially reducing the debug turn time with zero area overhead. Currently, the system is limited to work with Xilinx Virtex family of devices.

CE-MS-2015-09

## An Incremental VON-Based Debug System for Commercial FPGA Architecture

#### THESIS

# submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### EMBEDDED SYSTEMS

by

Roshan Kumar Gupta born in Patna, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

### An Incremental VON-Based Debug System for Commercial FPGA Architecture

#### by Roshan Kumar Gupta

#### Abstract

Electronic companies are increasingly using field-programmable gate arrays in various domains such as application acceleration, complex digital designs or ASIC prototyping. The Verification phase holds a significant place in the FPGA design development process. A key challenge during verification is observability. This is defined as the ability to view all internal states of a circuit. Due to poor observability, a significant portion of designer's effort is spent in this phase, specifically performing the debugging task. A common solution to improve observability is using embedded logic analyzers (ELA) that inserts trace-buffers into the design to record on-chip signal values. When on-chip memory is used for observation it is termed as trace-buffers. This approach has limitations such as slow debug cycles, pre-determining the signals to be traced or using logic resources on FPGA.

This work proposes a new debug system for improving the observability while overcoming the limitations of ELAs. The proposed debug system extends a recent technique referred as virtual overlay network (VON) for commercial FPGA device. This network can be perceived as built on top of initial circuit mapping and multiplexes all circuit signals to the on-chip memory for observation. It overcomes the limitation of commercial debug tools based on ELAs. We investigate the factors that influence the performance of VON for Xilinx Virtex, as it constitutes the core of debug system. We demonstrate that a new bit-stream to program the FPGA connecting hundreds of signals to the on-chip memory can be generated in less than 630 seconds, during debug cycle, for a fairly large circuit having normal re-compilation time of more than 5 hours. The proposed system proves to be a promising way of improving observability and potentially reducing the debug turn time with zero area overhead. Currently, the system is limited to work with Xilinx Virtex family of devices.

| Laboratory<br>Codenumber | : | Computer Engineering<br>CE-MS-2015-09  |

|--------------------------|---|----------------------------------------|

| Committee Members        | : |                                        |

| Advisor:                 |   | Stephan Wong, CE, TU Delft             |

| Chairperson:             |   | Stephan Wong, CE, TU Delft             |

| Member:                  |   | Arjan van Genderen, CE, TU Delft       |

| Member:                  |   | Arjan Palm, EGD, ASML Netherlands B.V. |

| Member:                  |   | Rene van Leuken, CAS, TU Delft         |

Dedicated to my family and friends

## Contents

| List of Figures  | vii  |

|------------------|------|

| List of Tables   | ix   |

| List of Acronyms | xi   |

| Acknowledgement  | xiii |

| 1        | Intr           | oduction                                | 1  |  |  |  |

|----------|----------------|-----------------------------------------|----|--|--|--|

|          | 1.1            | Context                                 | 1  |  |  |  |

|          | 1.2            | Motivation                              | 2  |  |  |  |

|          | 1.3            | Problem statement and contribution      | 3  |  |  |  |

|          | 1.4            | Approach                                | 4  |  |  |  |

|          | 1.5            | Thesis Overview                         | 6  |  |  |  |

| <b>2</b> | Bac            | kground and Related Work                | 7  |  |  |  |

|          | 2.1            | Scan and Trace Based Technique          | 7  |  |  |  |

|          | 2.2            | Incremental CAD                         | 8  |  |  |  |

|          | 2.3            | VTR CAD Flow                            | 9  |  |  |  |

|          |                | 2.3.1 Architecture Description Language | 9  |  |  |  |

|          |                | 2.3.2 Verilog-To-Routing (VTR)          | 10 |  |  |  |

|          | 2.4            | VTB                                     | 11 |  |  |  |

|          | 2.5            | Virtual Overlay Network                 | 11 |  |  |  |

|          |                | 2.5.1 Network Matching                  | 13 |  |  |  |

|          | 2.6            | Commercial Trace IPs                    | 14 |  |  |  |

|          | 2.7            | Related Work                            | 15 |  |  |  |

|          | 2.8            | Conclusions                             | 17 |  |  |  |

| 3        | Arc            | hitecture description of Virtex-6       | 19 |  |  |  |

|          | 3.1            | Virtex-6 FPGA Overview                  | 19 |  |  |  |

|          | 3.2            | CLB Tiles                               | 20 |  |  |  |

|          | 3.3            | Interconnect Resources                  | 21 |  |  |  |

|          | 3.4            | Block RAM                               | 23 |  |  |  |

|          | 3.5            | Conclusions                             | 23 |  |  |  |

| 4        | Implementation |                                         |    |  |  |  |

|          | 4.1            | Using RAM for trigger and trace         | 26 |  |  |  |

|          | 4.2            | QuickTrace                              | 27 |  |  |  |

|          |                | 4.2.1 Overlay                           | 28 |  |  |  |

|          |                | 4.2.2 Match                             | 30 |  |  |  |

|                       |       | 4.2.3 Collapse                             | 30 |  |  |

|-----------------------|-------|--------------------------------------------|----|--|--|

|                       | 4.3   | Proposed debug system                      | 30 |  |  |

|                       | 4.4   | Conclusions                                |    |  |  |

| <b>5</b>              | Res   | ults                                       | 33 |  |  |

|                       | 5.1   | Methodology                                | 33 |  |  |

|                       |       | 5.1.1 Metrics                              | 34 |  |  |

|                       |       | 5.1.2 Test Platform and Benchmark circuits | 35 |  |  |

|                       | 5.2   | Critical-Path Delay (CPD)                  | 36 |  |  |

|                       | 5.3   | Runtime Overhead                           | 38 |  |  |

|                       | 5.4   | Network Connectivity                       | 40 |  |  |

|                       | 5.5   | Trace and trigger Match                    | 43 |  |  |

|                       | 5.6   | Match Runtime                              | 47 |  |  |

|                       | 5.7   | Debug Turn Overhead                        | 48 |  |  |

|                       | 5.8   | Conclusions                                | 48 |  |  |

| 6                     | Cor   | nclusion                                   | 51 |  |  |

|                       | 6.1   | Summary                                    | 51 |  |  |

|                       | 6.2   | Conclusion                                 | 53 |  |  |

|                       | 6.3   | Future Work                                | 55 |  |  |

|                       |       | 6.3.1 Implementation enhancements          |    |  |  |

|                       |       | 6.3.2 Research opportunities               | 56 |  |  |

| Bi                    | bliog | graphy                                     | 61 |  |  |

| List of Definitions 6 |       |                                            |    |  |  |

# List of Figures

| $1.1 \\ 1.2$ | Normal VTR Flow   Proposed VTR Debug flow                                                                       | $5 \\ 6$        |

|--------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| 2.1          | Typical Xilinx ISE flow that can be used incrementally                                                          | 9               |

| 2.2          | Existing incremental flow                                                                                       | 12              |

| $2.3 \\ 2.4$ | Incremental Debug flow using Virtual overlay network                                                            | 12<br>13        |

| 95           | trace-buffers                                                                                                   | 13<br>14        |

| $2.5 \\ 2.6$ | Point-to-point network using dedicated multiplexers                                                             | $14 \\ 15$      |

| 2.0<br>2.7   | Union of signal trees: each having a trace pin as root                                                          | $15 \\ 15$      |

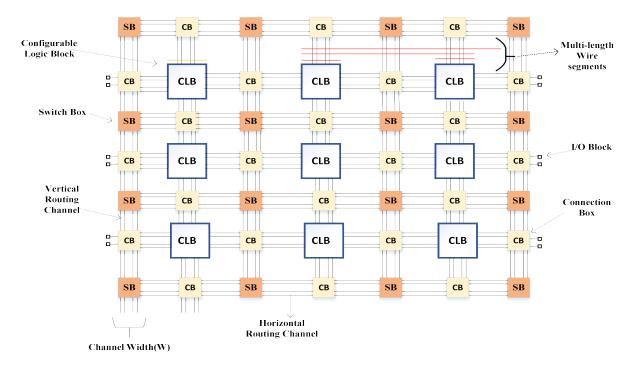

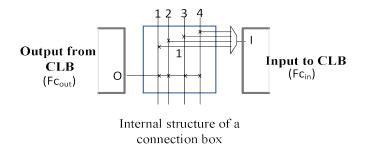

| $3.1 \\ 3.2$ | Internal structure of FPGA showing CLBs, CB, SB and routing resources<br>Internal structure of a connection box | $\frac{22}{22}$ |

|              |                                                                                                                 |                 |

| 4.1          | Proposed debug system                                                                                           | 31              |

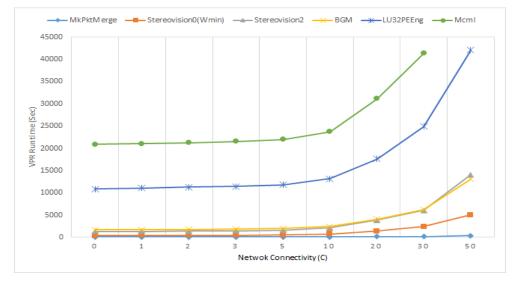

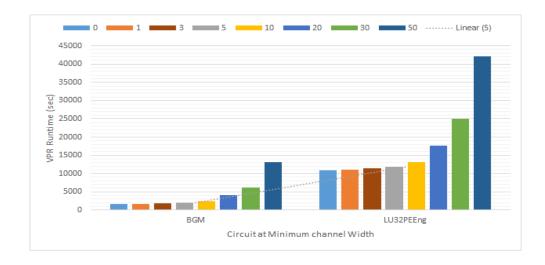

| 5.1          | Runtime Overhead: total VPR Runtime for embedding the overlay Network; $C = 0$ indicates baseline runtime       | 38              |

| 5.2          | Runtime Overhead: For Bgm and LU32PEeng benchmark; $C = 0$ indicates baseline runtime                           | 39              |

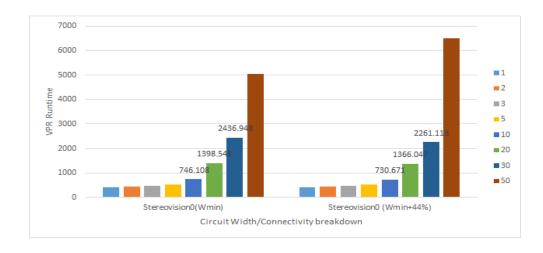

| 5.3          | Runtime when extra routing slack is introduced: Stereovision0                                                   | 40              |

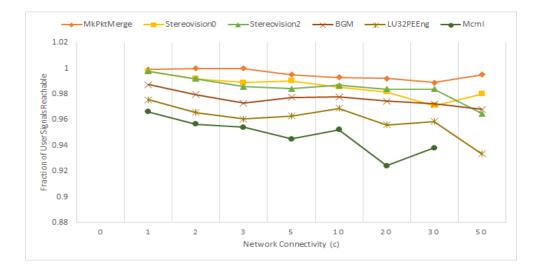

| 5.4          | Fraction of user signals reachable at varying C; Circuit signals normal-                                        | 10              |

|              | ized to their absoulute number for each benchmark                                                               | 40              |

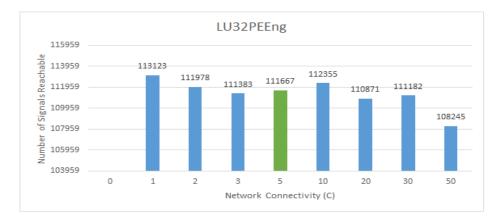

| 5.5          | Fraction of user signals reachable for LU32PEEng at C; Green bar indi-                                          |                 |

|              | cates signal reachability with no change in critical-path delay                                                 | 41              |

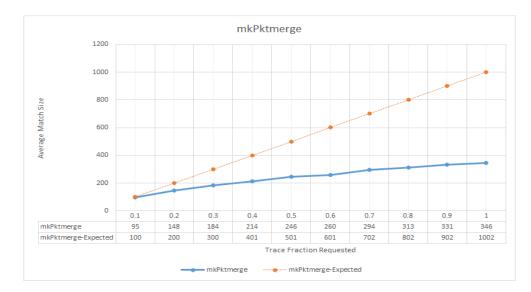

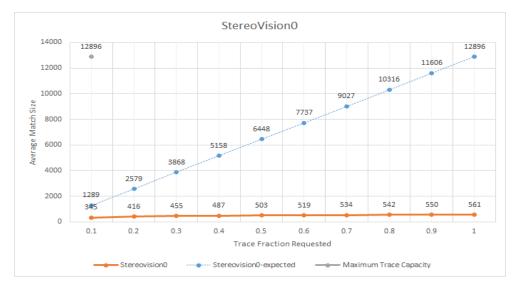

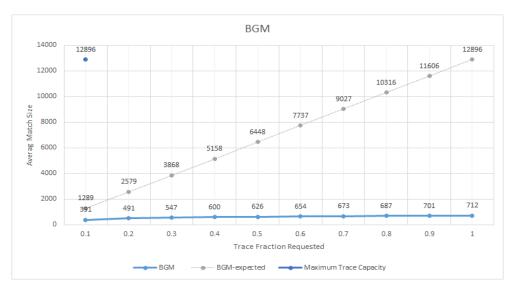

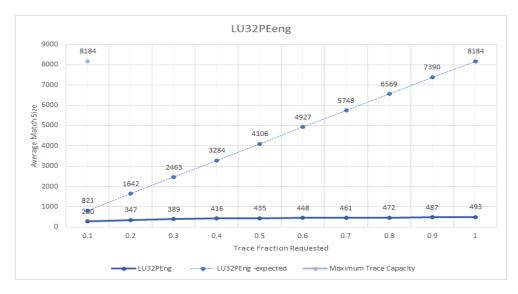

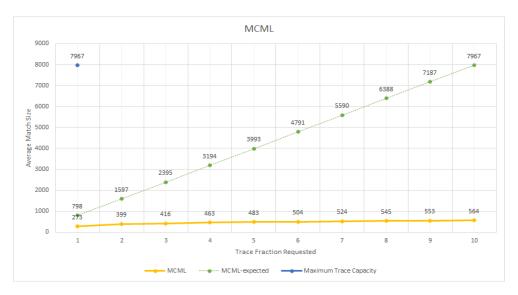

| 5.6          | Trace match size for mkPktmerge                                                                                 | 43              |

| 5.7          | Trace match size for Stereovision0                                                                              | 44              |

| 5.8          | Trace match size for Stereovision2                                                                              | 45              |

| 5.9          | Trace match size for Bgm                                                                                        | 45              |

| 5.10         | Trace match size for LU32PEeng                                                                                  | 46              |

| 5.11         | Trace match size for Mcml                                                                                       | 46              |

| 5.12         | Runtime to select a different set of signal (match) and re-configuring the                                      |                 |

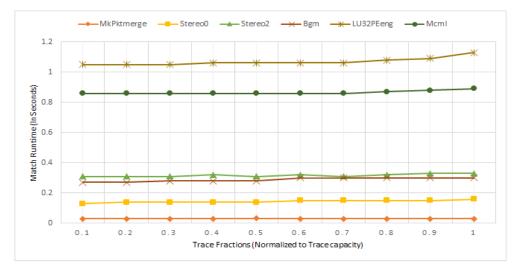

|              | overlay network                                                                                                 | 47              |

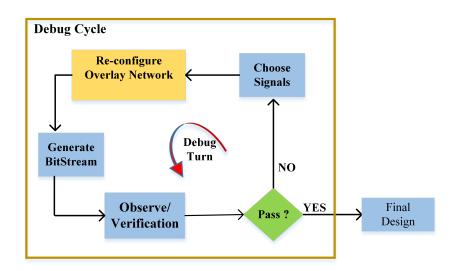

| 5.13         | Debug-cycle: cycle may be repeated multiple times                                                               | 49              |

# List of Tables

| 3.1 | Architecture parameters used as per Xilinx Virtex-6 FPGA                  | 21 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Based on Xilinx Virtex-6 LXT-FF1156 Device-Package Combination            | 23 |

| 5.1 | Benchmark resource usage                                                  | 33 |

| 5.2 | Effect of overlay network on critical-path delay(ns) at different network |    |

|     | connectivity (C) as compared with base delay                              | 37 |

| 5.3 | Debug time overhead for one debug turn (In Seconds)                       | 48 |

## List of Acronyms

- **ASIC** Application Specific Integrated Circuit

- ASML Advanced Semiconductor Materials Lithography

- ${\bf BLE} \ {\rm Basic \ logic \ element}$

- **CAD** Computer aided design

- **VON** Virtual Overlay Network

- FPGA Field Programmable Gate Array

- IC Integrated Chips

- **ELA** Embedded Logic Analyzers

- **VTR** Verilog-to-routing

- I/O Input/Output

- ${\bf RAM}\,$  Random access memory

- ${\bf DSP}$  Digital signal processing

- $\mathbf{VTB}$  VTR-to-bitstream

- ${\bf MWBM}\,$  Maximum Weighted Bipartite Matching

- $\mathbf{VPR}$  Versatile Pack and Route

- ECO Engineering Change Order

- ${\bf LUT}\,$  Look Up Table

- **PIP** Programmable Interconnect Points

- ${\bf TB}\,$  Trace Buffer

- **ADL** Architecture Description Language

## Acknowledgement

This Master Thesis constitutes the final part of my study program required to obtain a degree of Master of Science in Embedded Systems at Delft University of Technology, The Netherlands. During the first year of my master's program I learned that it is very important to have industrial experience along-with theoretical expertise and hence, I decided to pursue my master thesis at ASML while having a strong focus on academic research.

In the beginning, I was presented with a raw idea and was asked to develop it. I took the complete ownership of the initial idea, developed it further and worked towards finding a solution for it. The topic involved working on the lower abstract layers of the FPGA design aids & architecture technologies with complete focus on every related aspect of it. I felt challenged and motivated by the amount of work, detailed knowledge and complexity involved, and the fact that it have the potential to directly impact the FPGA development process. During the entire duration of my master thesis I was exposed to scientific fields that I had no previous experience, had the opportunity to remarkably improve my scientific skills and gained the ability to independently pursue a research work.

I would like to express deepest gratitude to my supervisor at university, Stephan Wong, and at company, Arjan Palm for guiding me throughout the thesis project with their expertise & experience. During my meetings with both of them, I was shown the right path to do research, apply critical thinking and how to manage the complete work. Next, I would like to thank Mr. Paul van der Heijde for believing in me and offering the graduation project. I would also thank, Arjan van Genderen, for regularly discussing the topic in detail and provide feedback throughout the project. I would also like to extend my thanks to Rene van Leuken for being the external member in my thesis committee.

Many thanks goes to all my fellow colleagues Arnica Ajay Agarwal, Razvan Nane, Anthony Brandon, Dan, Mike, Anupama, Komal and rest of the people from EGD group at ASML and CE Dept. at TU Delft for their ideas, reviews & feedbacks.

Last but not least, I would like to thank my family and especially my brother who provided the financial support for my master studies and their mental support throughout my entire study period.

Roshan Kumar Gupta Delft, The Netherlands December 9, 2015

# 1

This thesis describes the design and implementation of a debug system for FPGA verification that reduces the debugging time and improves observability. This chapter provides an introduction to the problem. It begins with the context in which the work originated and afterwards, we discuss the motivation for an incremental trace-based debug system. We refer to incremental compilation as the possibility to independently run individual stages of a tool that compile circuit designs for FPGAs. Subsequently, we discuss the problem statement that is researched in this thesis and the contributions made by this work. The approach section discusses the methodology adopted to analyze the problem statement. Finally, the overview of the rest of the work is given.

#### 1.1 Context

Moore's law is one of the important laws of digital electronics that have contributed towards world economic growth during previous decades. IBM has recently shown a 7nm prototype chips containing approximately 20 billion transistors with four times more performance. With such an advancement in technology, today's Application Specific Integrated Circuit (ASIC) and Field Programmable Gate Arrays (FPGA) are bound to become more complex. Recently, electronic companies have started to increasingly use FPGAs in various domains such as application accelerators, implementing complex digital designs or for FPGA prototyping of ASIC designs. Since FPGAs are used extensively, it is critical for the digital designs implemented on these devices to function properly otherwise the consequences could be costly or even life-threatening. The previous statement and the growing complexity of digital designs exemplifies the need for design verification. Incidents like the Intel FDIV bug are evidence to the same.

Recently, FPGA prototyping is increasingly used for ASIC verification, that is, the method to prototype the ASIC design on FPGA for hardware verification and early software development. Verification is an important phase of the design development since it drives the time, cost and quality of the complete FPGA product development. It is equally important and follows the same procedure whether it is performed for specific FPGA design methodology or during the use of FPGA as prototyping platform.

A worldwide study conducted by Wilson research group, commissioned by Mentor Graphics in 2014 shows that 45% [1] of the industry used FPGA prototyping for IC verification and this is expected to sharply increase with the newer FPGAs having larger gate counts. FPGA platforms are a considerate choice for verification as they are faster than logic simulation in terms of maximum design frequency with higher design coverage. While still costing much less than an ASIC prototype fabrication with almost no lead time compared to the waiting time for the tapeout. [2] shows that IBM engineers reported that full chip-level testing using a multi-FPGA prototype is 100,000 times faster than software

simulation which emphasize the use of FPGAs for the mentioned purpose. Moreover, todays FPGA designs have grown in complexity with 56% [1] of FPGAs containing one or more embedded processors along with complex network-on-a-chip interconnect. Out of the total FPGA project time, 46% [1] is spent on verification as of 2014. The average mean time spent by an FPGA design engineer (in an FPGA project team composed of development and verification engineers) doing just verification is 51% [1] and verification engineers are spending 43% [1] of their time specifically on debugging tasks.

A key requirement during any verification procedure concerning FPGAs is observability, that is, the ability to view all internal states of the circuit, analogous to the ability of software debugger to view the values of variables. Observability is key to verifying behavior and track down bugs in circuit design. However, limited or no observability of internal signals is an inherent drawback of FPGAs. It causes the internal signals to be brought out through the I/O pins of FPGA for observation. These I/O resources are limited and depends on the physical size of the device. Unlike simulators that can provide full observability into all the circuit signals, FPGAs can provide only a small subset to be observed through the I/O pins. During debugging it is imperative to observe any signal instead of just observing handful of signals through the I/O pins.

A common solution for increasing observability is to use embedded logic analyzer (ELA) tools based on the trace-based approach of inserting trace-buffers into the circuit design and connecting signals to them for observation. Trace buffers are formed of on-chip memory elements that record the history of the subset of internal signals connected to them during circuit operation. This history is then used to analyze the state of the circuit signals to perform debugging tasks and can further be extracted for offline analysis. Although, ELAs provide more observability than a standard logic analyzer that can only observe the I/O pins, they have several limitations. Providing new and efficient ways of increasing the observability can be perceived as one of the key technologies required. In the context of overcoming the limitations of ELAs thereby improving observability within FPGAs, this work has been carried out.

#### 1.2 Motivation

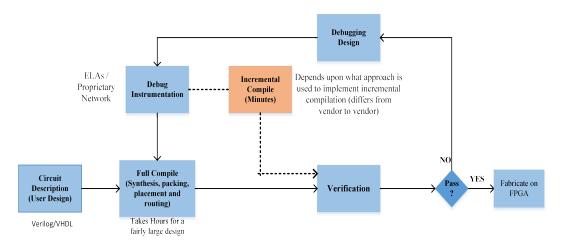

A number of commercially available standard debugging tools are offered by FPGA vendors based on the concept of ELAs. These tools use the on-chip memory as tracebuffers and add probes directly to the RTL design to make specific signal available for observation via trace-buffers but suffers from following limitations.

- 1. ELAs require extensive LUT and memory resources on the FPGA to implement debug instrumentation, this limits their performance in case enough FPGA resources are not present. It can be termed as area overhead of using ELAs.

- 2. The signals that a designer wishes to observe must be pre-determined during the insertion of debug instrumentation, that is, before the circuit is operational and the nature of the bug known. This means that many debug cycles may be required to observe different subsets of signals to track down the bug. A debug cycle is the complete process of selecting a different combination of circuit signal, long place-and-route times of changing probes to observe them and re-synthesize the design

to program the FPGA again. The time taken to perform one such cycle is termed as debug turn time. With the increasing complexity of the designs, debug turn times tends to be in hours that hugely affects the debug productivity. Incremental routing can be used to connect these ELAs without a complete recompile but are still slow and requires the entire design to be loaded into the memory [3] [4] [5].

3. The ELAs may influence the initial mapping and timing characteristics of the circuit being instrumented thereby hiding potential bugs.

These limitations are also recognized by the FPGA designers at Advanced Semiconductor Materials Lithography (ASML) where this work has been carried out. ASML is a high-tech company that builds lithography machines for manufacturing chips being a world leader in its domain. FPGAs are solely used in their machines to implement various functionality. Since designers at ASML use standard debugging tools, they also felt limited by their drawbacks during FPGA design development. Hence, a debug system is wished for that can reduce the debug turn time, have no area overhead and improves observability of internal signals by connecting hundreds of them to debug instrumentation with-in FPGA. Such a system will be able to address the more general problem of overcoming the limitations of ELAs thereby improving the observability as well as serving the need of such a system specific to designer's at ASML.

The purpose of this work is to propose and demonstrate a debug system that overcomes the existing limitations of ELAs by using a technique called virtual overlay network (VON). This network is incrementally built on top of existing physical mapping of a placed-and-routed FPGA design, multiplexing all the circuit signals to trace-buffers and can be merged together with the physical mapping of circuit during debugging. It can be perceived as a virtual mesh layer on top of existing design and hence is referred as virtual overlay network and is further explained in Section 2.5 of next chapter. The next section describes the problem statement that will be researched in this work and highlights the contributions.

#### **1.3** Problem statement and contribution

The virtual overlay network (VON) technique is only known to be demonstrated on a hypothetical FPGA architecture with simplifying assumptions. Therefore, it is imperative to implement it for a realistic architecture, evaluate its performance and to know its feasibility towards using it as a core technique in an debug system. A realistic FPGA architecture can be best represented by a commercially available device. Xilinx Virtex family of FPGA devices represent a comprehensive generation of FPGA architecture and is used for the purpose of this work. The insights gathered from this work then can serve as a prototype to design and build a complete system that overcomes the limitation of embedded logic analyzer thereby improving observability. The problem statement of this thesis is:

For a commercial FPGA architecture (like Xilinx Virtex family), what will be the performance of a virtual overlay network based debug system?

To answer this question, we first need to extend this technique for such an FPGA architecture and build a debug system using a CAD flow that allows open access to its different stages such as packing, placing or routing. Afterward, we need to identify and measure the factors that influence the performance of debug system. Such a debug system will consists of various stages. It will take a circuit's HDL description and will generate bit-stream to program the device. It will be realized using a open-source CAD flow known as VTR [6]. Performance of this tool for a commercial architecture and generation of a valid bit-stream after the insertion of this instrumentation that can be used to program the device is demonstrated.

The work described in this thesis has the following unique characteristics:

- 1. It extends the recently proposed virtual overlay network for a commercial architecture.

- 2. A new debug flow that can generate bit-stream for a commercial architecture alongwith debug instrumentation.

Consequently, the contribution of this work is to extend and demonstrate the feasibility of a recently proposed (Overlay network) trace-based approach on a commercial architecture and implement a debug system based on it. These unique characteristics are not found in any other approach. It also overcomes the limitations of ELAs mentioned in previous section that are based on trace-based approaches by using incremental compilation method (described in Section 2.2). Implementation details and associated challenges of realizing this work for Xilinx Virtex-6 FPGA are described in the implementation section. The new debug flow developed to do this work are the first to demonstrate the capability on a realistic device and suggest ways to improve on the limitations of ELAs. Along with the unique characteristics, it contributes towards answering the following questions:

- 1. What is the impact of an overlay network on the critical path delay?

- 2. Is the overlay network approach suitable enough for a commercial architecture?

- 3. How much runtime saving can be made during debug cycle?

The methodology adopted to achieve the contributions and to carry out the research on problem statement, mentioned above is discussed in the next section.

#### 1.4 Approach

In order to realize such a debug system, we reviewed existing and recently proposed techniques to ascertain the possibility of coming up with a solution that is feasible and meets the requirements. The virtual overlay network [7] is identified as having the potential to address above mentioned problems. Similar to commercial trace-based ELAs, this technique utilizes trace-based approach to incrementally embed a network on top of existing circuit mapping while reclaiming on-chip memory as trace-buffers. It is demonstrated as a tool known as QuickTrace [7]. The proposed debug system extends this tool for a commercial architecture. It enable the designers to run the design live on FPGA, record the history and extract the information from the trace buffers with techniques like device read-back [8] for offline analysis. Logic on the chip can be used as a trigger to control the trace buffers. This system only makes use of the resources that are left after the initial placement and routing of the user circuit, virtually having zero area overhead. The selection of signals can be deferred till the actual time of debugging and does not require the designer to make a pre-selection during the initial circuit compilation. It significantly reduces the debug turn time required to change the set of signals that are connected to the trigger and trace unit. This is accomplished by embedding the overlay network over the initially placed-and-routed design. Whenever a new set of signals need to be observed, only the embedded network needs to re-configured.

The Quicktrace is promising enough to be one of the key technologies in its domain but is only demonstrated on a theoretical architecture with simplifying assumptions. That makes it important to demonstrate its working on a commercial architecture. This work evaluates the performance of this approach on a Xilinx Virtex-6 commercial FPGA [9] found on ML605 evaluation kit. The Virtex 6 FPGA is a realistic, commercial and complex FPGA architecture as compared with the hypothetical architecture.

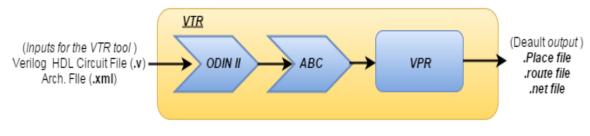

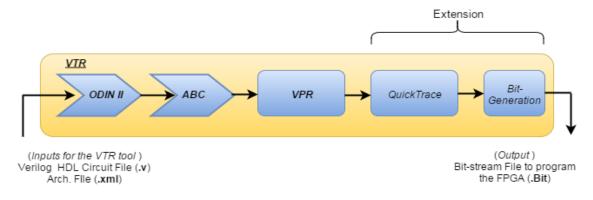

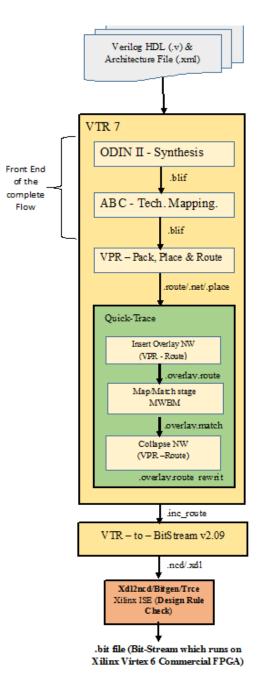

The VTR CAD flow [6] is used for the realization of the proposed debug system. This CAD flow is distributed over multiple intermediate stage to synthesize, pack, place and route the verilog user circuit with respect to the FPGA architecture and is shown in Figure 1.1. It is an open source CAD flow that provides independent access to its individual stages for easy modification of its core algorithms to facilitate CAD and FPGA research whilst it does not have the capability to generate a bit-stream for actual FPGA devices. This CAD flow is modified to implement the debug system as shown in Figure 1.2 by adding two more intermediate stages making it possible to generate bit-stream with debugging instrumentation for commercial architecture.

Figure 1.1: Normal VTR Flow

The output from the VPR stage is used to incrementally insert the debug instrumentation, that is, embedding the overlay network that adds new routing to the initial route solution connecting circuit signals with trace buffers while preserving initial un-instrumented routing during the QuickTrace stage. Then this debug instrumented routing is subjected to physical design rules via Xilinx DRC, and upon successful pass, bit-stream is created that can be programmed on a physical device (in this case Virtex-6 FPGA) during the bit-generation stage. The new tool flow, proposed in Figure 1.2 lever-

ages the functionality of different tools used to realize it. We further explain these tools in the background section.

Figure 1.2: Proposed VTR Debug flow

The results, challenges and involved work of using this approach and proposed flow may differ between FPGA architectures, especially in contrast with theoretical architectures. Currently, the debug system only supports the Xilinx Virtex-6 family of devices, but it is possible to extend it for other family/generation of devices with minimal effort. Nevertheless, this could be used on any FPGA where it is possible to augment the debug instrumentation along with existing circuitry.

#### 1.5 Thesis Overview

The remainder of the thesis is structured as follows: Chapter 2 describes the background and related work, explaining the different concepts required to understand this work such as VTR or trace-based approach, as well as related work that highlights the difference between this work and similar work. Chapter 3 explain the modeling of Virtex-6 via Architecture description language. Chapter 4 describes the implementation, explaining the complexities involved while using a commercial architecture in conjunction with VTR that limits exploration of different features present on them, an extension of VON and the proposed debug system. Further, Chapter 5 elaborates about the methodology and metrics used to perform the experiments and reports the obtained results. Chapter 6 contains the conclusion of thesis and also suggests future work with which this work can be extended and/or refined. The sections below state the topics in detail that will help the reader to understand better, the work presented in this thesis. Section 2.1 describes the scan and trace-based approach of FPGA debug and advantages of the latter over former. Section 2.2 explains about the incremental compilation for FPGA CAD tools. Sections 2.3, 2.4, and 2.5 explains about the VTR and VTB tools respectively. Section 2.3 also describes the architecture description language used within the VTR CAD flow in order to model the Xilinx Virtex-6 FPGA. Rest of the sections describes about virtual overlay network and commercially available debugging tools. Section 2.7 highlights the differences between this work and other similar works. Finally, Section 2.8 concludes the chapter.

#### 2.1 Scan and Trace Based Technique

Observability of the internal signals in a FPGA can be improved by using scan or tracebased techniques. Scan-based approach captures the state of memory elements of FPGA for observation by serially shifting it out via scan chains over an I/O pin or an interface such as JTAG. All the memory elements on the chip, that is, flip-flops and embedded memory blocks contains the values which represent the state of the FPGA. This technique relies on architectural features like device read back in FPGAs or by connecting internal flip-flops sequentially so that their data can be serially shifted out when triggered by a control signal. This can be implemented using general purpose soft logic [10], although it can provide complete visibility into the state of flip-flops in the design, it requires the circuit to be halted before scan-out with prohibitive area and delay costs. Reference [10] showed that average overhead for full scan is 84% additional area and Reference [11] reported that viewing each flip-flop using device read back can take 2 to 8 seconds. For using this technique, the circuit needs to halt for every clock cycle if we want to observe values of memory elements for every clock cycle, which immensely increases the debug time.

The trace-based technique is another method that functions by leveraging the presence of embedded memory blocks on an FPGA. It utilizes a portion of the embedded memory resources, using it as trace buffers to record a small subset of the internal circuit values during normal device operation. These trace buffers controlled by a trigger, connected to the signals to be traced are pre-inserted into the circuit before compilation. They record a window of the history as circuit operates in real-time. In FPGAs with readback capability, the data in trace-buffers can be extracted for offline analysis. This approach does not require the circuit to halt, has very less area and delay cost, provides capability to test the system with real-time stimulus over the former approach. Xilinx Chipscope Pro, Altera SignalTap II and Synopsys identify [5] [12] [13] as examples of such trace based debugging tools, also referred as trace-based IPs. These tools also have disadvantages such as time-consuming re-compilation if the designer wishes to change the set of signals being observed, limited by the on-chip memory resources, may influence the initial placement and routing of the circuit.

This work focuses on the trace-based approach and tries to improve on the drawbacks of commercial trace IP offerings by extending the virtual overlay network for a commercial architecture.

#### 2.2 Incremental CAD

To program a circuit onto a FPGA, different types of CAD tools are used depending on the designer's preference. Examples of such CAD tools are Xilinx ISE tool flow, Altera Quartus tool which are commercial offerings or VTR project being an open source project. The entire CAD process to implement a circuit onto a FPGA consists of the following steps [?]:

- 1. Synthesis/Logic Optimization Performs multilevel minimization of the boolean equations to optimize area, delay or both.

- 2. Technology mapping Transforms the boolean equations into a circuit of FPGA logic blocks as well as performs area or delay optimizations.

- 3. Packing and Placement Packs the related logic blocks together and selecting the specific location for each logic block onto the FPGA while optimizing for the wire length.

- 4. Routing Physically connecting the placed logic blocks with the routing resources such as wires, connection or switch box etc., distributed inside an FPGA to form the interconnect fabric.

On an abstract-level all these tools have synthesis, technology mapping, pack and place and routing as intermediate stages within the tool flow and are implemented by stage-specific tool-sets. Each tool is unaware of the complexity or implementation of the other and the mechanism for linking them together, but they have a cyclic dependency and there is a strong interaction between them. For the sake of simplicity, only the idea of incremental CAD flow is mentioned and not explained since it is not the focus of this work. Often a design under goes many iterations even after being implemented on the FPGA. To eliminate the need for full design recompilation, that is, end-to-end from the synthesis stage to the routing stage in case of any change, the tool needs to perform incremental design modifications instead of starting from scratch. Local changes to the design can be encapsulated as changes for a specific stage and a re-run of only that stage is needed to implement the change. This independent re-running of only specific stages is known as incremental flow, although they still need to be feed with same input file as used in default case. For example, if only the synthesis stage is required to run for modification then it will be called incremental synthesis, likewise incremental routing and/or placement. The benefit of this idea is that it lets the designer save significant amount of development time. Reference [15] explains about the challenge, benefits and ways of achieving this idea. For the present day, tools mentioned above do implement incremental compilation at their own level of abstractions, varying from open source to vendor-specific. Figure 2.1 shows the Xilinx ISE tool and outline the different parts of the tool that can be independently used.

Figure 2.1: Typical Xilinx ISE flow that can be used incrementally

#### 2.3 VTR CAD Flow

To understand the CAD flow, an initial introduction of the architecture description language and BLIF netlist is presented in the next sections and then the CAD flow is explained in the subsequent section.

#### 2.3.1 Architecture Description Language

The FPGAs physically contain several resources on them such as I/O blocks, RAMs, complex logical blocks consisting of LUTs or flip-flops and routing infrastructure. With the increasing complexity, density and efficiency of the FPGAs, these blocks undergo change as well with every new generation of devices. For example, complex logic blocks may consist of more number of smaller components called primitives or they may have different Look-up table (LUT) configurations. The Open source CAD tools lack the ability to target complex commercial architectures. This limits the researchers, who do not have the capability to explore new avenues relative to these new architectures because of the proprietary nature of commercial CAD tools and FPGA architecture. Moreover it is not always possible to physically realize a new FPGA architecture just for experimental purposes. Hence, a language is developed that can model any type of hypothetical or real FPGA architecture, purely for research purposes.

An Architecture Description language (ADL) [16] can precisely express different types of blocks and interconnects present on a FPGA at different complexity/hierarchy level, described in extensible markup language (XML) file format. The designer can describe complex logic blocks with arbitrary internal routing structure using this language, it permits arbitrary levels of hierarchy within the logic block, that is, a logical block can be defined as a block within top level complex block and so on. It can define different configurations of a block within the architecture which can represent different functionality and relevant portion of interconnects. It also models the timing specifications of the primitives and interconnects. This language provide the means to forward the FPGA research by letting the designer describe hypothetical architectures and experiment with new ideas. The architecture file used as input to VTR along with Verilog circuit is written using this language. More information about this language with examples can be found in reference [17].

#### 2.3.2 Verilog-To-Routing (VTR)

The VTR tool is an open source CAD flow for synthesizing verilog circuits onto hypothetical FPGA architectures. It is a world-wide collaborative project involving multiple research groups to provide a complete, flexible, robust and open-source framework for conducting FPGA architecture & CAD research and development. The CAD flow takes a verilog hardware description of digital circuits, and a xml file describing the target architecture as it's input in the beginning and then elaborates, synthesizes, packs, places and routes the circuit as per the input architecture and performs timing & power analysis [18] . The VTR v7.0 CAD flow is the base tool upon which this work is built upon and hence the description helps the reader better understand the context.

It comprises of three core tools as shown in Figure 1.1:

- ODIN II [19] responsible for Verilog elaboration and front-end hard-block synthesis, it takes in the Verilog circuit, interprets and converts the Verilog syntax into logical netlist targeting the soft-logic on the FPGA while other constructs into 'hard logic' blocks on the FPGA and outputs a BLIF [20] netlist.

- ABC [21] is used for technology independent logic synthesis and technology mapping of logic onto LUTs and flip-flops. It takes the BLIF netlist from ODIN II as input and performs on the soft-logic part of the BLIF.

- Third and last tool in the flow is VPR [22] that performs physical synthesis and timing analysis. It takes in the BLIF netlist from the previous stage and the architecture file (.xml) as input. Afterwards, packs, places and routes the circuit. It generates three output file namely .net, .place and .route files. It performs all the physical optimization of the logic primitives into the complex logic and other blocks mentioned in the architecture file. Subsequently, it also performs the timing analysis, area and power estimation [6]. The VPR implements a timing-driven packing and routing algorithm with lot of enhancements as compared to its previous releases such as support for carry chains.

While using the VTR flow, it is possible to run individual stages and analyze the output. For example, to only use the VPR tool, the user has to create the BLIF netlist and describe logical block in the FPGA architecture description file. The user can even run the individual stages within VPR i.e. only packing, placement or routing, but needs to provide the appropriate input for that stage. The complete VTR CAD flow can be treated as an important contribution towards advancing the FPGA architecture and related CAD flow research and development.

#### 2.4 VTB

VTR-to-Bitstream (VTB) [23] is an open source extension of the VTR CAD flow that takes a Verilog input and architecture description file of a commercial FPGA and produces a routed netlist which is converted into a valid bit-stream after running Xilinx Design rule check that can be programmed onto a Xilinx Device. The author's intention behind developing this tool was to present a unique comparison between the quality of results generated by the academic and commercial CAD flows [23], but for the purpose of this work, we will use it to generate the bit-stream for a physical Xilinx device, and also to investigate that whether the routing of debug instrumented circuit confirms with the physical design rules of Xilinx or not.

The VTR CAD flow is developed to target hypothetical FPGA architectures and hence, the VPR is capable of only producing simple routing networks relative to commercial CAD flows supporting only horizontal and vertical routing tracks symmetric across both channels. For a commercial architecture this is different which also supports diagonal and L-shaped wires. VTB bridges this gap by extracting the routing graph from Xilinx device database and stitching it with the graph produced by VPR and it is possible to do so because the VPR's router can work with routing graphs generated externally till it satisfies the graph requirements; xdlrc2vpr tool within VTB performs the previous step. VPR then normally produces .net, .place and .route files using this routing graph which is then processed by RapidSmith [24] to generate a single textbased human-readable Xilinx Design File (XDL) which captures all LUT masks taken from BLIF netlist, packing and all net connections from .net file and placement sites on FPGA from .place file. Another internal tool called route2xdl is used to add routing switches (PIPs) to the previously generated XDL. As a last step, the XDL is used to generate the NCD file via the xdl2ncd tool (part of ISE tool flow [25] which is used as input for generating the bit-stream using Bitgen tool (Again, part of ISE tool flow). The complete flow is known as VTR-to-Bit-stream [23] as it provides a path from using the packed, placed and routed circuit to generate valid bit-stream.

#### 2.5 Virtual Overlay Network

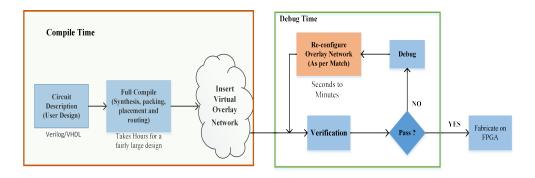

There are several concepts which have been proposed to improve the observability within a FPGA and are mentioned in the related work. One such concept is virtual overlay network proposed by Hung and Wilton [26] that holds the potential of providing software simulator like observability for FPGA as hypothesized by the authors. The details of this virtual overlay network is explained below as it forms the base of this work. As compared with the incremental debug flow Figure 2.2, the authors have proposed a debug flow which comprises of two stages as in Figure 2.3:

• Compile time - After the normal circuit compilation, i.e., packing, placement and routing, the virtual overlay network is embedded into the un-instrumented circuit that incurs a one time overhead of embedding the network. This runtime overhead varies depending on the size of circuit.

Figure 2.2: Existing incremental flow

• Debug time - For the purpose of debugging, the embedded network can be reconfigured to connect the designer's choice of signals to the trace buffers for observation. The network can be re-configured several times and within minutes. The concept behind this network is explained in the rest of the section.

Figure 2.3: Incremental Debug flow using Virtual overlay network

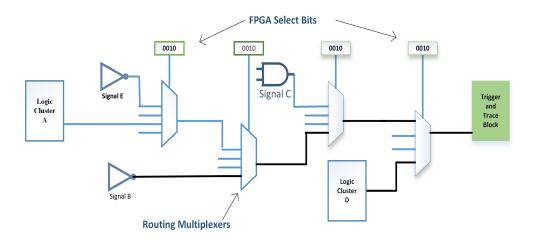

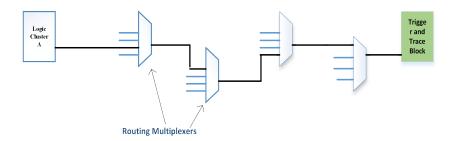

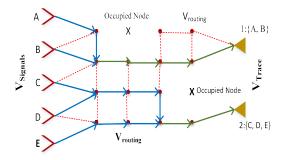

The virtual overlay network in Figure 2.4 depicts multiplexs all on-chip signals to all trace-buffer pins via routing multiplexers, in contrast to a point-to-point network in between a on-chip signal source and a specific trace-buffer pin using dedicated routing multiplexers as shown in Figure 2.5. FPGAs are highly re-configurable given the presence of abundant routing multiplexers; this network is built using these multiplexers left after the initial circuit routing, at the same time reducing the area overhead of debug instrumentation. Building this overlay network is treated as a routing problem which can be represented as a routing resource graph G(V,E), where  $V = V_{signals} \cup V_{routing} \cup V_{trace}$ and  $E = \text{set of unused routing tracks between these vertices; } V_{signals} = \text{set of all traceable}$  circuit signals,  $V_{routing}$  = set of unused routing multiplexer and  $V_{trace}$  = set of tracebuffer inputs. For better understanding, an example is depicted in Figure 2.6. Here all the signals can be routed to either of two trace-buffer inputs for observation. Each routing multiplexer can have a fan-in of more than one. This allow the multiplexing of signals, where a designer can observe any single signal in circuit, and a limited selection of any two signal, as defined by the Cartesian product of two signals sets. For example, {A,B} x {C,D,E} = {AC, AD, AE, BC, BD, BE}. A routing solution like this can be treated as a disjoint union of trees, where each tree is rooted at a trace-buffer input and leaves being the circuit signals that it connects. Such an arrangement allow signal selections to be made for each trace-buffer input irrespective of other trace-buffer input, differentiating it from general routing resource graph and allowing more accessibility to circuit signals.

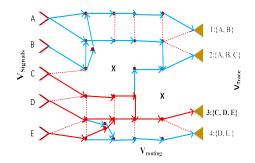

The network can be further modified as graph G'(V', E'), where  $V' = V_{signals} \cup V_{trace}$ , and E' = set of edges showing the connectivity between a signal and trace pin. It is also possible for a signal to be a leaf of multiple trees while occupying few more routing multiplexers and increasing the flexibility of observing any combination of two signals, as depicted in Figure 2.7. So, to summarize the virtual overlay network is built on top of existing circuit connections, using routing multiplexers to create new connection in order to forward the signals from their source to multiple trace-buffer input pins for observation and can be configured during debug time merge with the existing routing.

#### 2.5.1 Network Matching

During debug-time the designer's choice of signal is routed to a trace-buffer input pin. But it introduces an assignment problem, that is, which signal to connect to which tracebuffer pin, to maximize the chances of observing different combinations of signals. This assignment problem can be solved by further treating the virtual overlay network as a bipartite graph  $G'(U_b, V_b, E_b)$ . It is a graph whose vertices can be divided into two disjoint sets independent of each other, every edge connects a vertex in one set with a vertex in

Figure 2.4: Virtual overlay network multiplexing circuit signals to all the available tracebuffers

another set and edges must not exist between the vertexes of same set. Now, substituting  $U_b = V_{Signals}$  - set of all circuit signals,  $V_b = V_{trace}$  - set of all trace buffer inputs and  $E_b = E'$  - set of edges which represent the network connectivity between two vertices. A matching of graph  $G_b$  represents a subgraph that has none of its edges sharing a common vertex. A maximum matching is the largest such subgraph that can be formed. With this property it is very convenient to decide which signal to forward to each trace pin: given that each trace pin can only support one connection, hence each node in  $V_{trace}$  must have at most one edge. The maximum number of edges that can exist is the minimum number of the cardinality of either vertex sets. Such maximum matching algorithm returns a best effort partial assignment, but optimal where the maximum number of signals possible are forwarded over the network for observation. In some scenarios, designer may wish to specifically observe some signals or trigger signals, then these preferences can be encoded by adding weights W to each edge of the bipartite graph and using a weighted version of the maximum matching algorithm, which returns largest matched subgraph possible having maximum sum of all weights on matched edges; This variant is termed as maximum weighted match algorithm. By using the above explained algorithm, select bits for each of routing multiplexers can be computed and programmed on the device using either static or dynamic-partial reconfiguration. For further details, please refer to [7].

#### 2.6 Commercial Trace IPs

As mentioned earlier, trace based techniques utilize embedded memory on the FPGA as trace buffers to record a small subset of internal signal state during normal device operation. Almost all the trace IPs in the commercial market uses this technique, examples of them are Xilinx Chipscope Pro [12], Altera SignalTap II [5] and Synopsys Identify [13]. This section briefly explains these tools. Trace IP from Xilinx, Chipscope Pro requires the designer to choose the signals as well as the debug core to be inserted before implementation. Trigger & trace signals can be changed incrementally using FPGA editor. Although Xilinx support partial re-configuration that allows to skip a full re-compile. This feature has limitations while using the Chipscope Pro and may also require extra

Figure 2.5: Point-to-point network using dedicated multiplexers

Figure 2.6: Union of signal trees: each having a trace pin as root

Figure 2.7: Overlay network: signal tree for trace-input 3 is highlighted in red

design effort of running a separate program.

SignalTap II from Altera tries to exploit the incremental compilation by partitioning the design and in case tries to re-compile only that partition instead of complete design. It also requires the designer to make the signal selection and core insertion before implementation but is more integrated than ChipScope. Both the tool use partitioning, core insertion and signal selection before compilation.

Synopsys Identify provides the observability in FPGA at RTL level and adds the debug instrumentation into the circuit before compilation. It gives the flexibility of changing the signal without a full re-compile. Since, the instrumentation is added before compilation, it have certain area overhead and changes the initial pattern of circuit. This work tries to demonstrate that how these limitations can be re-solved and is further explained in related work section.

#### 2.7 Related Work

As mentioned above, the challenge of improving observability while debugging in FPGA can be overcome by using either scan or trace-based techniques. The trace-based approach has an advantage over scan-based while incremental CAD should be used that helps in avoiding time critical compilation stages. This work proposes a new incremental debug flow based on virtual overlay network that enhances the observability within FPGA. This debug flow is based on VTR CAD flow and has the ability of generating valid bit-stream for Virtex-6 devices. Incremental synthesis/routing techniques allow faster re-compilation and preserve the placement and route of the design under test. Adding debug instrumentation after the original circuit compilation avoids influence on initial placement and routing thereby preserving as much of the original solution as possible while adding debugging functionality. There is often unused logic and routing resources like embedded memory or routing multiplexer leftover after initial circuit placement on a FPGA, which can be reclaimed incrementally and used for implementing debug instrumentation. With incremental approach, full re-compilation can be avoided, allowing faster debug cycles and changes in the debug instrumentation as depicted in Figure 2.2.

Reference [4] proposes instrumenting FPGA bit-stream, with debugging hardware

to improve debugging productivity. They inserted unconnected embedded logic analyzers prior to placing and routing, and afterwards modified the bit-stream at low level to connect the ELA with trace signals. They also described that how this process can be automated using JHDL, JBits or JRoute, however it may not scale up for observing thousands of signals, requires design effort of changing bit-stream for every ELA and significant area overhead due to pre-inserting trace-buffers. Poulos, et al. [27] also proposed bit-stream modification to improve debug productivity. They connected signals of interest to the routing muxes, modifying the design prior to synthesis, muxes forwarded the signals to the FPGA I/O pins where it can be observed via external logic analyzer, and if it is wished to observe different signal. Then bit-stream modification can change what is forwarded through routing muxes. This approach does not use any trace buffer but do influence the placement and routing of initial circuit, introduces area overhead, and exposes the designer to error prone process of changing individual bits in bit-stream.

Incremental trace buffer insertion and its limitations by Hung and Wilton [3] [28] proposed how trace-buffers can be inserted into design. The trace-buffers only observe without modifying the functionality of the design under test and trace signals can be routed to any trace buffer input for observation. Reference [29] described a method to reclaim spare FPGA resources for debug instrumentation and used automated signal selection techniques [30] [31] to connect influential signals with trace buffers. Although they all differ from this work that no such concept of embedding a network was explored here but it did identify these uniques features of trace-buffers and reclaiming left-over resources. Most similar to this work is commercial tool Tektronix Certus [32], which implements a non-blocking proprietary observation network built out of general purpose logic to observe a large subset of signals, during initial circuit compilation. This network can be collapsed to observe a small subset of signal during runtime. Another product namely, Altera SignalProbe [33] uses ECO techniques to multiplex up o 256 signals to each reserved I/O pin for external analysis. This work differs in that, it does not use general purpose logic for inserting debug instrumentation and does not require preselection of signal.

This work expands on and demonstrates an application of the work done by Hung, et al. [7] that holds the potential of being a efficient trace IP. They implemented the concept of virtual overlay network for a hypothetical architecture and encapsulated it as a tool named Quicktrace using VTR CAD flow. It was a extension of their own work [26]. It used a hypothetical architecture with simplified assumptions. They found that it is possible to trace 80-90% signals while reclaiming left-over resources with debug turn time within minutes. They hypothesized that there was no reason why their techniques would not work on commercial FPGA devices but did not verify the same. Moreover, the results presented in the paper were not obtained with practical cases. In this work, the feasibility and performance of QuickTrace is demonstrated on a commercial Xilinx Virtex-6 FPGA and expanded to generate a valid bit-stream, so that a complete debug path using VTR CAD flow can be realized. The VTR CAD flow in conjunction with VTB tool is used to map the circuit onto an FPGA, incrementally insert the debug instrument and generate the bit-stream. With this work, it is being shown how the limitations of ELAs and observability of the FPGAs can be improved and implemented for other physical FPGAs. All the related projects were published after 2013, which highlights that the present thesis deals with currently open research problems and recent engineering work.

#### 2.8 Conclusions

This chapter presents the different concepts and technologies necessary to understand the rest of the thesis. It begins with a brief explanation of the scan and trace-based approach. It highlights the fact that trace-based approaches are better than scan-based approaches in terms of faster debugging time with less area overhead. Afterward, it details about the incremental CAD flow that makes it possible to independently run individual stages of the tool thereby saving compilation time. Subsequently, the VTR CAD flow and architecture description language is explained that forms the base of the debug system proposed in this thesis. VTR only understands the architecture description written in XML format of an FPGA in order to know the properties of FPGA device being and then perform tool execution. Subsequently, the concept of virtual overlay network explains that how we can embed a flexible network on top of existing place-and-routed circuit design, multiplexing circuit signals to trace buffers that can be merged together onto the existing mapping when debugging is required. The network connectivity describes about the flexibility of such a overlay network. We have used this particular concept to build the debug system.

Finally, this chapter also outlines the differences between this thesis and related/similar works. It briefly describes the commercial trace IPs as well. The commercial trace IPs requires the designer's to pre-select the trace signals, extensively uses FPGA resources and have long debug cycles. We can follow from the earlier discussion on related work that the use of overlay network for commercial architecture is unique and the debug system based on it overcomes the limitations of commercial trace IPs like Chipscope or SignalTap. This chapter describes the architectural parameters of Xilinx Virtex-6 family of devices that are translated into a XML format using architecture description file. The VTR tool is not capable of generating a bit-stream for any FPGA architecture because it does not have a device database of supported FPGA architecture (unlike other proprietary FPGA CAD tools like Quartus or Vivado) that contains detailed information about different properties and associated parameters of devices used to implement the circuit. The reason for this lack in functionality of VTR is that, its a open source tool that is mainly used for FPGA architecture and CAD research, and there is no such device database for hypothetical architectures that are used for experiments. Hence, a architecture description language is used instead to model and describe the FPGA architecture being used. The VTR takes in this description as an input, extract information about the FPGA device and perform all the operations to compile the circuit. Section 3.1 presents an overview of the Virtex-6 FPGA and the reasons for using this particular device. Sections 3.2, 3.3, and 3.4 explains the modeling of configurable logic blocks, interconnect resources and Block RAMs using this language respectively. Subsequently, Section 3.5 concludes the chapter.

# 3.1 Virtex-6 FPGA Overview

The Virtex-6 architecture is the preferred choice for this work because it is the only architecture supported by the VTB tool as well as the newest architecture fully supported by the RapidSmith [24] CAD tools used within VTB tool. No other tool exists that can be used as an alternative to these tools for Xilinx devices. Closed proprietary device databases and unsupported interfaces are responsible for constraining the open source tools to use these architectures. Moreover, in recent times Xilinx has stopped the support for Xilinx design language (XDL) and Native circuit description (NCD proprietary netlist format while migrating to their new tool flow called Vivado, blocking the use of their new FPGA devices for architecture or CAD research. The XDL and NCD support related to the Xilinx FPGA devices are vital if we wish to use them in academic research. We can intuitively assume that the results will not change significantly within the Virtex family devices given the architecture remain the same concerning LUTs, Block RAMs or routing infrastructure. It is worth noting that, replicating the work for latest architectures using newer tools would involve exponential amount of work given closed-source nature of involved tools, architecture databases and no support related to them by their respective vendors.

The key enabling component is a detailed architecture description file that models as many features present on the physical device as possible, the VTR takes in this file and then performs synthesis, technology mapping, packing, placement and routing in correlation to it. It is important to understand the Virtex-6 architecture to describe it in (.xml) format using the architecture description language mentioned in section 2.3.1. VTR does not support all the features available on the physical device and hence constrains the functionality that can be derived from them. The sections below explain the design choices made for structure of different Virtex-6 tiles in conjunction with VTR constrains. It also highlights how various architectural parameters were determined.

Virtex-6 is an array or island style FPGA, consisting of an array of logic blocks and routing channels arranged in two dimensional grid of tiles. It is termed so because configurable logic blocks look like islands in a sea of routing interconnects. There are different types of tiles present on-chip such as CLB, BRAM or interconnect and tiles of the same type are typically identical. The tiles relevant to this work are presented below. Like other FPGAs, Virtex-6 devices are also configured by loading applicationspecific configuration data known as Bit-stream into internal memory and is generated by the BitGen [25] program, part of Xilinx ISE tool flow. Some important features supported by Virtex-6 that highlights the adaptability of this work are dynamic and partial reconfiguration and device read-back support. The reconfiguration features allows the designer to access and modify block specific configuration bits, status and control registers, even providing the flexibility to reconfigure a portion of FPGA while the rest of the logic is active, that is, live reconfiguration. Device read-back [34] enables the designer to extract and dump the configuration memory via SelectMAP, ICAP or JTAG interfaces of memory elements (LUTs, BRAMs, SRL16), internal CLB and IOB registers. There are two flavors of this feature: Readback Verify which only reads the memory elements and Readback Capture which behaves as superset of readback verify and captures internal CLB and IOB registers alongwith configuration memories. Both of the features can be used to adapt this work for live debugging.

# 3.2 CLB Tiles

Configurable logic blocks is the fundamental building block of a Xilinx FPGA, being the main logic resources for implementing combinational and sequential logic and consists of LUTs, flip-flops and multiplexers. Their internal structure varies with different vendors or product families. Virtex-6 CLB [35] spans over one tile and is divided into two entities called SLICEL and SLICEM (commonly referred as Slices). Each slice contains 4 LUTs, 8 flip-flops, 1 arithmetic and cary chain for SLICEL. For SLICEM - 256-bit DRAM and 128bit shift register in addition to SLICEL. Each slice implements a 6-input LUT with 1output, fracturable into two 5-input LUT with separate output but with common inputs. The storage elements can be used as D flip-flops or latches. The output of each flip-flop (4 in case of 6-input LUT or 8 in case of 5-input LUT when the first 4 storage elements are not used as latches) is directly connected to an output pin of the slice. Each CLB is connected to a switch matrix for routing to other FPGA resources and carry chains connects vertically in a column from one slice to the one above. The output and input pin of the slices connect to the adjacent interconnect tiles. For this work, only SLICEL is modeled, as distributed RAM option implemented by SLICEM is not supported by VTR.

The CLB model in this work is made up of two logic slices, each logic slice contain

four basic logic elements where each BLE contains a 6-input LUT (fracturable into 5input LUT), followed by two flip-flops. A bypass input (AX) used to reach either flip-flop, or to feed XADDER carry-in directly byspassing the LUT. A combinational output (A) as output O6, a sequential output (AQ) and output (AMUX) shared between secondary flip-flop, LUT outputs O6 and O5 and the COUT or sum from adder. Each slice contains one CIN and COUT connected as chain through all four BLEs. Logic slice clock enable, set/reset and wide multiplexers representing MUXF7/F8 hardened resources are not modeled because of being constrained by VTR which does not support them although architecture description language do support complex hierarchy and it is approximately possible to model the complete Virtex-6.

# **3.3** Interconnect Resources

The interconnect tiles such as switch or connection boxes are the primary location of the programmable routing resources that are spread throughout the FPGA. Each interconnect tile is paired with a non-interconnect tile such as CLB or IO blocks. The routing network consists of pre-fabricated wiring segments and programmable switches that are organized in horizontal and vertical routing channels and generally is a proprietary information from the FPGA vendors including other information like no. of physical tracks in routing channels, directionality of wires, type of switch and connection block etc. In Xilinx FPGAs, wire segments can be connected with each other in either channels via programmable interconnect points (PIPs). The interconnect wire segments span fixed distances known as Manhattan distances (L) ranging from L = 1,2,4 and 16(bi-dir) connecting logic blocks. The non-interconnect tiles uses the adjacent interconnect tiles to connect with resources of other tiles. For example, the output of a flip-flop can be routed to a CLB tile four blocks away using wire length of L=2 or 4 depending upon the requirement and congestion constraints. Since, VPR is not capable of modeling L-shaped or diagonal wires used by XilinX FPGAs, a pre-processed routing graph with this feature is directly imported into VPR stage.

| Architecture Parameters         | Value         |            |  |

|---------------------------------|---------------|------------|--|

| Logic Cluster Size              | Ν             | 8          |  |

| Lookup Table Size (Fracturable) | Κ             | 6          |  |

| Inputs Per Cluster              | Ι             | 56         |  |

| Channel segment Length          | $\mathbf{L}$  | 1,2,4 & 16 |  |

| Cluster Input flexibility       | $F_{c_{in}}$  | 1          |  |

| Cluster Output flexibility      | $F_{c_{out}}$ | 1          |  |

| BRAM data width (used)          |               | 32 bits    |  |

| BRAM address width (used)       |               | 11 bits    |  |

Table 3.1: Architecture parameters used as per Xilinx Virtex-6 FPGA

The architecture parameters based on the target device are presented in Table 3.1, where few parameters are experimentally determined. The internal structure of an

island style FPGA containing the configurable logic blocks, connection box, switch box and other routing resources is depicted in Figure 3.1. Figure 3.2 shows the internal of a connection box highlighting the cluster input/output flexibility.

Figure 3.1: Internal structure of FPGA showing CLBs, CB, SB and routing resources

Figure 3.2: Internal structure of a connection box

# 3.4 Block RAM

The Virtex-6 FPGA contains Block RAM tiles that can store upto 36K bits of data and can be configured as either two independently controlled 18Kb RAMs, or one 36Kb RAM [36]. The BRAMs support different aspect ratios ranging from 1bit X 32K - to - 72bit X 512, offering different combinations of data width and depth and can be cascaded to enable a deeper and wider implementation. A wider configuration (for example: 72bits X 512) will store just 512 entries while comparatively narrow configuration will have more entries. The BRAMs can operate with simple or true dual port requiring just one clock edge for read and write operations. Simple dual port means, one port is used for read-only operation and another for write-only while both port can be used simultaneously while true dual port means using both the ports for read and write operation. The BRAMs have built-in FIFO support, this dedicated logic can be used to track read and write address and status of FIFO. The FIFO has full, almost full, empty and almost empty status signals and can be configured for different widths.

| Xilinx Virtex-6 Resources          |           | Value        |

|------------------------------------|-----------|--------------|

| Input/Output Blocks                | I/O       | 600          |

| Configurable Logic Blocks (Slices) | SLICEL    | 37680        |

| Digital Signal Processing Slices   | DSP48E1   | 768          |

| Block RAMs (36 Kb)                 | BRAM      | 416          |

| Minimum Route Channel Width        | $W_{min}$ | 18           |

| FPGA Array Size                    |           | $102\ge 240$ |

Table 3.2: Based on Xilinx Virtex-6 LXT-FF1156 Device-Package Combination

Again, the BRAM modeled for this work via architecture description language contains both 36K or 18K configuration, simple and true dual port memory and complete aspect ratio. BRAMs as hardened FIFO is not modeled for this work, as VTR do not support this configuration. The logical and routing resources present on the Virtex-6 FPGA are listed in Table 3.2.

# 3.5 Conclusions

This chapter describes the modeling of Virtex-6 FPGA using architecture description language for use with the VTR CAD tool. Since, VTR itself is not capable of generating bit-stream for realistic architectures, it is extended with the VTB tool to generate bitstream for Xilinx Virtex devices. The VTB tool leverages the Rapidsmith tool that is based on XDL and provides a framework to use modern Xilinx Devices in academic research related to low-level FPGA CAD tools like the debug system presented in this thesis. The architecture description language is capable of describing any hypothetical or realistic architecture in XML format. Although, the architecture description language can describe most of the complex resources present on the Virtex-6 device, the VTR is not capable of using them. Hence, the debug system is constrained to use only those blocks on the FPGA that VTR can operate with. We experimentally determine the architectural parameters of Virtex-6 as this information is proprietary while modeling the Virtex-6 for this work. The next chapter describes the extension of overlay network for this architecture and implementation of the proposed debug system. This chapter describes the various intricacies of the implementation and design choices that lead to the realization of this work. It starts with Section 4.1 that describes how a BRAM can be used to implement both trigger and trace functionality. Afterward, Section 4.2 explains about the extension of the QuickTrace tool for the Virtex-6 architecture and VTR 7. Subsequently, in Section 4.3 we explain the proposed debug system that will facilitate the generation of bit-stream for Virtex-6 with debugging functionality. Finally, Section 4.4 concludes the chapter. In next paragraph, we will discuss the considerations and design choices made to proceed with the implementation.

As initial step towards realizing this work, we proposed few hardware designs that tries to address the topic of improving observability while overcoming the limitations of ELAs. These hardware designs had limitations such as additional cost of hardware components, area overhead of placing them over printed circuit board while also occupying the I/O resources of the FPGA that can be used for other important purposes. So, instead of hardware alternatives, we considered an approach that do not have these limitations. The requirements for such an approach are: No hardware components to eliminate area overhead and component cost, incrementally inserting the debug instrumentation for faster-debugging cycles, possibility to extract the content of trace buffers to off-chip memory for later analysis and to remove the instrumentation when not needed.