# A Fast and Accurate SystemC / SystemC-AMS Model for Super-Regenerative Radio

# THESIS

# CAS-MS-2011-02

# submitted in partial fulfillment of the requirements for the degree of

Master of Science

In

Microelectronics

by

Kezheng Ma Born in Beijing, China

This work was performed in:

Holst Centre / IMEC-NL Eindhoven, the Netherlands

Circuits and Systems Group Department of Microelectronics Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Delft University of Technology Department of Microelectronics

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis entitled "A fast and accurate SystemC / SystemC-AMS model for super-regenerative radio" by Kezheng Ma in partial fulfillment of the requirements for the degree of Master of Science.

Dated: 29/06/2011

Chairman:

prof.dr.ir. A.J. van der Veen

dr.ir. T.G.R.M. van Leuken

Advisor:

Committee Members:

dr.ir.W.A.Serdijn dr.L.Huang ing.H.W.Pflug

# Abstract

Nowadays, communication system has become a very important part of modern live. In order to dramatically reduce the cost and design time of a radio system, a unified design environment that can be used efficiently by system designers for modelling and simulation is very desirable. However, one of the main problems is that the simulation of a radio system is very time consuming or even impossible. Therefore, to examine the behaviour of a radio system, a fast and precise model is highly desirable. To address this problem, in this thesis, a new super-regenerative model based on the recently published SystemC/SystemC-AMS (BETA version) language is presented. The system is composed of both analog circuit model as well as the digital baseband which is impossible to model in the past. The simulation results are verified by both the simulation results of other model and the measurement results. The thesis shows the feasibility of a unified design environment for mixed signal modelling based on SystemC/SystemC-AMS in order to reduce the cost and design time of electrical systems.

# Contents

| 1 | Ir                       | ntroduc                                 | tion                                            | 1  |

|---|--------------------------|-----------------------------------------|-------------------------------------------------|----|

|   | 1.1                      | Mot                                     | ivation                                         | 1  |

|   | 1.2                      | The                                     | sis goals                                       | 2  |

|   | 1.3                      | Con                                     | tributions                                      | 2  |

|   | 1.4                      | The                                     | sis organization                                | 3  |

| 2 | В                        | Backgro                                 | bund                                            | 4  |

|   | 2.1                      | 2.1 Introduction to SystemC/SystemC-AMS |                                                 | 4  |

|   | 2                        | .1.1                                    | SystemC                                         | 4  |

|   | 2                        | .1.2                                    | SystemC-AMS                                     | 5  |

|   | 2.2                      | Intro                                   | oduction to super-regenerative radio            | 6  |

|   | 2.3                      | Intro                                   | oduction to PPM modulation                      | 9  |

| 3 | А                        | nalog                                   | parts modelling of the super regenerative radio | 10 |

|   | 3.1                      | The                                     | mixer block                                     | 10 |

|   | 3.2                      | The                                     | power amplifier                                 | 11 |

|   | 3.3                      | The                                     | super block                                     | 11 |

|   | 3.4                      | The                                     | quench block                                    | 12 |

|   | 3.5 The envelop detector |                                         | envelop detector                                | 14 |

|   | 3.6                      | Low                                     | /-pass filter                                   | 15 |

|   | 3.7 The VGA              |                                         | VGA                                             | 15 |

|   | 3.8                      | ADC                                     | S                                               | 15 |

| 4 | Ρ                        | hase L                                  | .ocked Loop (PLL) modelling                     | 17 |

|   | 4.1                      | Free                                    | quency analysis of the PLL                      | 17 |

|   | 4.2                      | The                                     | SystemC/SystemC-AMS model                       | 17 |

|   | 4                        | .2.1                                    | Reference clock block                           | 18 |

|   | 4                        | .2.2                                    | The PFD block                                   | 19 |

|   | 4                        | .2.3                                    | The rfdelay block                               | 20 |

|   | 4                        | .2.4                                    | Inverter                                        | 21 |

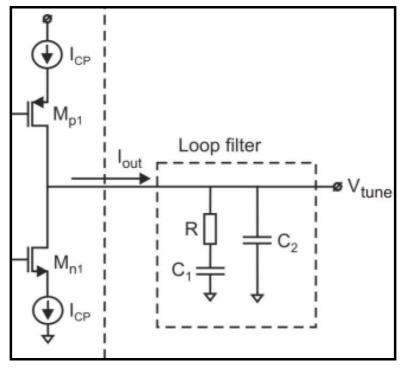

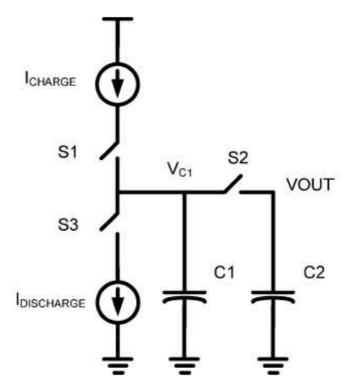

|   | 4                        | .2.5                                    | Charge pump and loop filter                     | 21 |

|   | 4                        | .2.6                                    | Control_m block                                 | 23 |

|   | 4                        | .2.7                                    | VCO                                             | 23 |

|   | 4                        | .2.8                                    | Converter                                       | 24 |

|   | 4                        | .2.9                                    | Divider                                         | 24 |

|   | 4                        | .2.10                                   | Sigma-Delta Modulator                           | 24 |

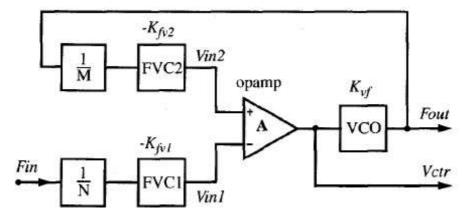

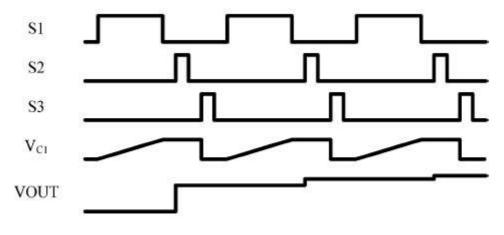

| 5 | F                        | •                                       | ncy Locked Loop (FLL) modelling                 |    |

|   | 5.1                      | Pha                                     | se-Aliened FLL (PA-FLL)                         | 27 |

|   | 5                        | .1.1                                    | Structure of PA-FLL                             | 27 |

| 1 | 5.2 Тур | pe-2 FLL                                                 |    |

|---|---------|----------------------------------------------------------|----|

|   | 5.2.1   | The structure of the FLL                                 |    |

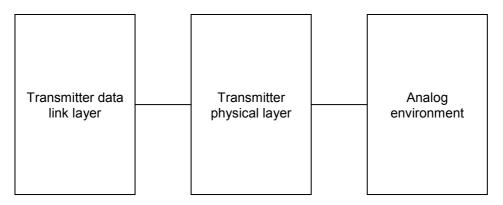

| 6 | The dig | gital baseband of the model                              |    |

|   | 6.1 The | e transmitter SystemC/SystemC-AMS model                  |    |

|   | 6.1.1   | Transmitter data link layer                              |    |

|   | 6.1.2   | Transmitter physical layer                               | 34 |

|   | 6.2 The | e receiver SystemC/SystemC-AMS model                     |    |

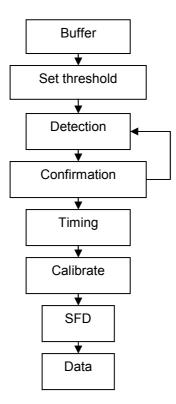

|   | 6.2.1   | The buffer                                               |    |

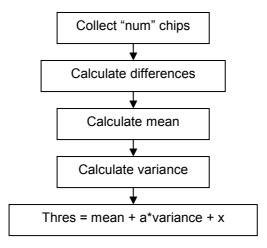

|   | 6.2.2   | The threshold estimation                                 |    |

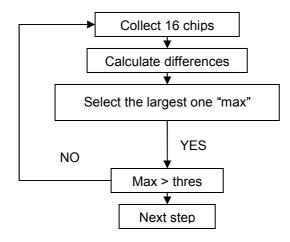

|   | 6.2.3   | The Detection                                            |    |

|   | 6.2.4   | The confirmation stage                                   |    |

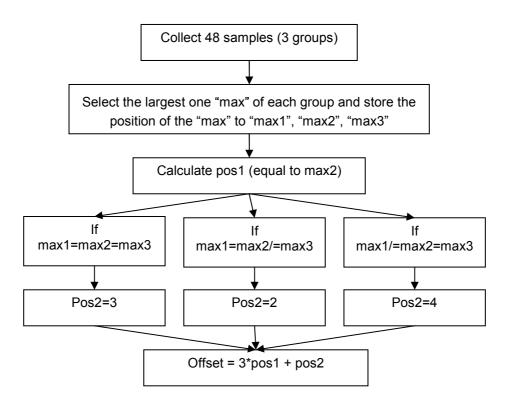

|   | 6.2.5   | The timing stage                                         |    |

|   | 6.2.6   | The SFD detection                                        | 40 |

|   | 6.2.7   | Data collection                                          | 41 |

| 7 | Simula  | tion results                                             | 42 |

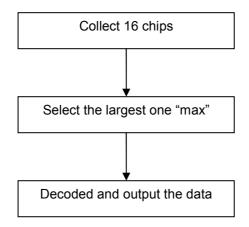

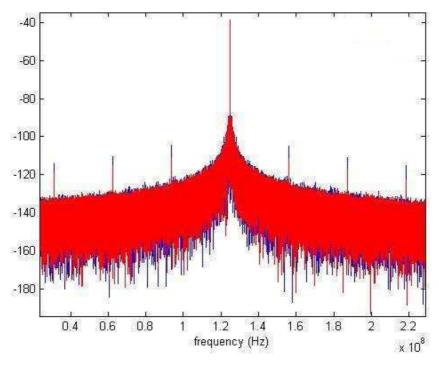

|   | 7.1 The | e simulation results of PLL and FLL                      | 42 |

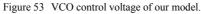

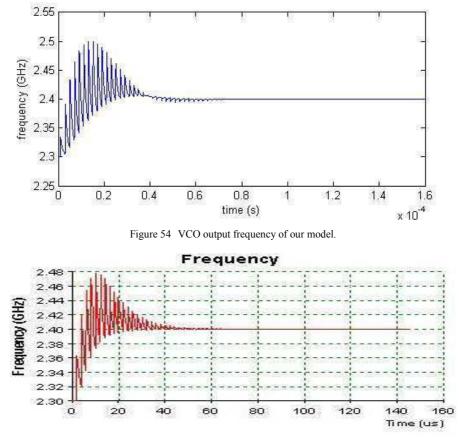

|   | 7.1.1   | Comparison with Matlab simulation results                | 42 |

|   | 7.1.2   | Comparison with ADI SimPLL simulation results            | 43 |

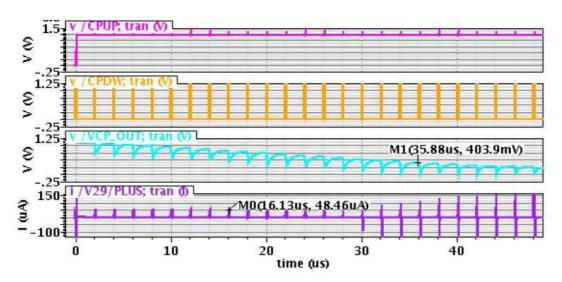

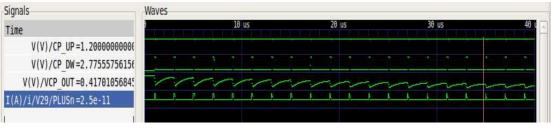

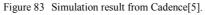

|   | 7.1.3   | Comparison with Cadence simulation results               | 44 |

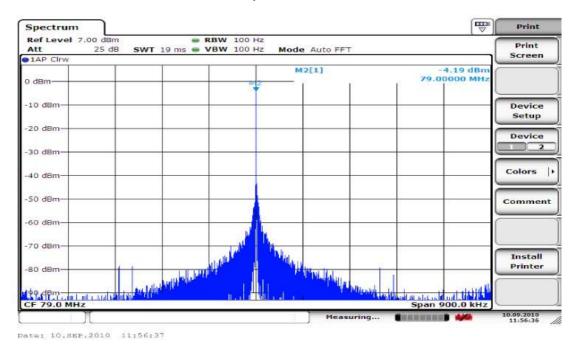

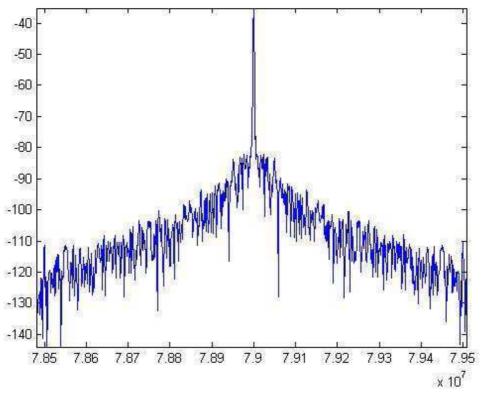

|   | 7.1.4   | Comparison with measurement results                      | 45 |

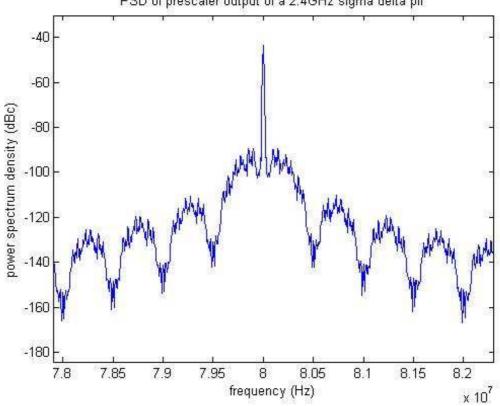

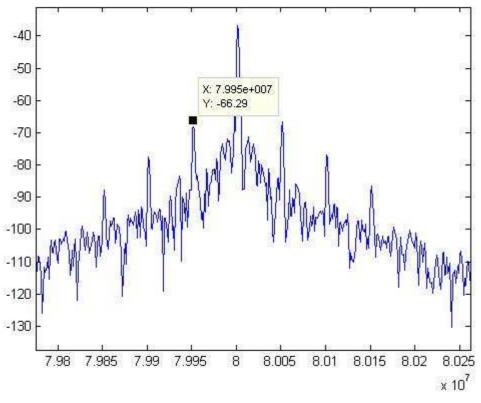

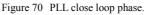

|   | 7.1.5   | Simulation results for sigma-delta modulator             | 46 |

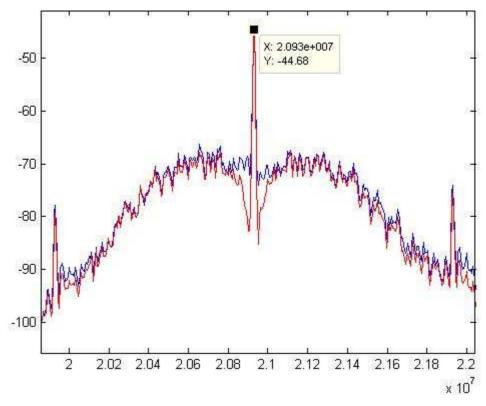

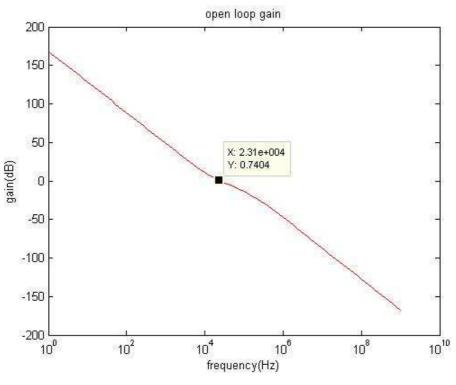

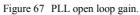

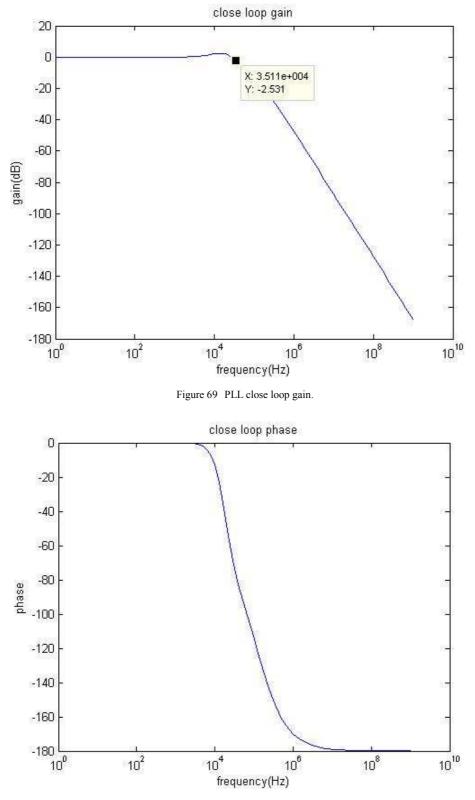

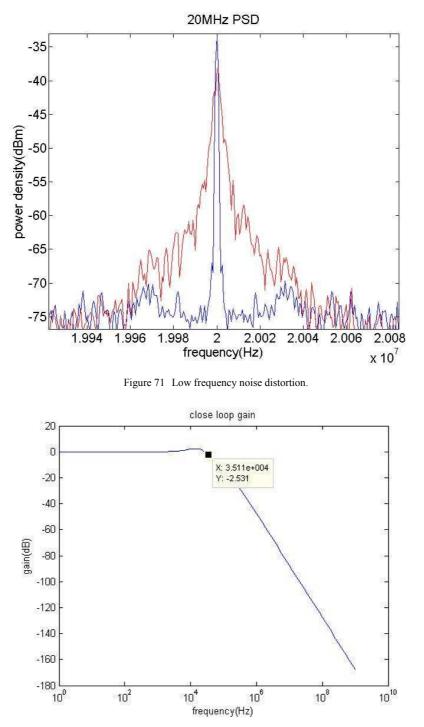

|   | 7.1.6   | Simulation results for the AC domain analysis of the PLL |    |

|   | 7.1.7   | Simulation results for PA-FLL                            | 53 |

|   | 7.1.8   | Simulation results for FLL type-2                        | 53 |

|   | 7.2 Sin | nulation results for the Analog System                   | 54 |

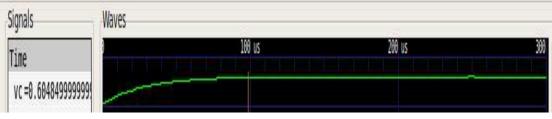

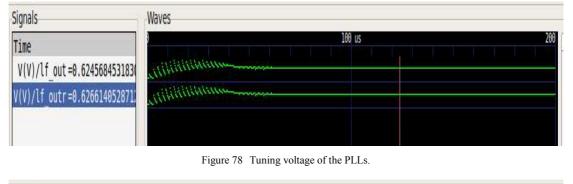

|   | 7.2.1   | The simulation results for PLLs                          | 55 |

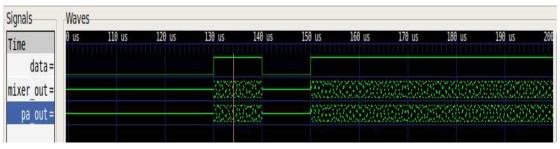

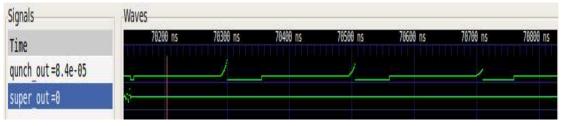

|   | 7.2.2   | The simulation results of the transmitter                | 55 |

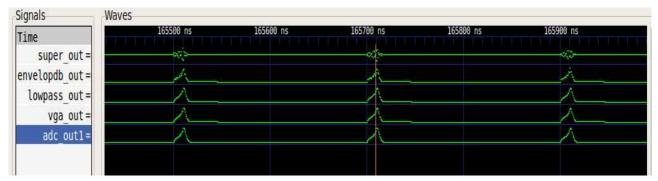

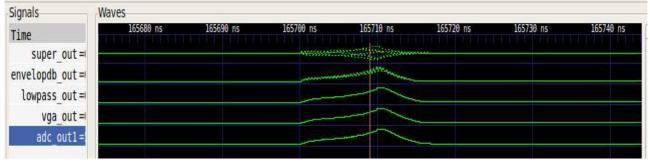

|   | 7.2.3   | The simulation results of the receiver                   | 55 |

|   | 7.2.4   | Simulation results for critical current searching        | 57 |

|   | 7.2.5   | Simulation results for optimal slope searching           | 57 |

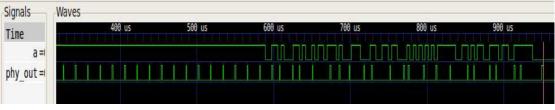

|   | 7.3 Sin | nulation results for digital baseband                    | 57 |

|   | 7.3.1   | The transmitter simulation results                       | 57 |

|   | 7.3.2   | Threshold estimation                                     | 57 |

|   | 7.3.3   | Simulation results for detection                         | 58 |

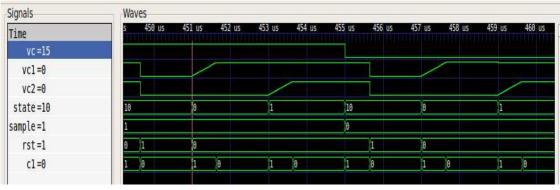

|   | 7.3.4   | Simulation results for confirmation                      | 58 |

|   | 7.3.5   | Simulation results for timing                            | 59 |

|   | 7.3.6   | Simulation results for SFD detection                     | 59 |

|   | 7.3.7   | Simulation results of data collection                    | 60 |

|   | 7.3.8        | Data verified                     | 61 |

|---|--------------|-----------------------------------|----|

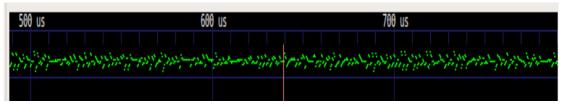

|   | 7.3.9        | Compare with measurement results  | 61 |

|   | 7.3.10       | Improvement of the PPM modulation | 63 |

| 8 | 3 Conclusion |                                   |    |

| 9 | Referen      | ces                               | 65 |

# List of abbreviation

| PLLPhase Locked LoopFLLFrequency Locked LoopRTLRegister Transfer LevelTDFTimed Data Flow modelLSFLinear Signal Flow ModelELNElectrical Linear Networks ModelRFRadio FrequencyLNALow Noise AmplifierPAPower AmplifierEDEnvelop DetectorLPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital ConverterVCOVoltage Control OscillatorPFDPhase/Frequency Locked LoopELDEarly Late DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description LanguageSNRSignal to Noise Ratio                                                                                                                                                                                                                                                                                                                     | [      |                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------|

| RTL       Register Transfer Level         TDF       Timed Data Flow model         LSF       Linear Signal Flow Model         ELN       Electrical Linear Networks Model         RF       Radio Frequency         LNA       Low Noise Amplifier         PA       Power Amplifier         ED       Envelop Detector         LPF       Low-pass Filter         VGA       Variance Gain Amplifier         ADC       Analog to Digital Converter         DAC       Digital to Analog Converter         VCO       Voltage Control Oscillator         PFD       Phase/Frequency Detector         LF       Loop Filter         CP       Charge Pump         PA-FLL       Phase-Aliened Frequency Locked Loop         ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language | PLL    | Phase Locked Loop                                                |

| TDFTimed Data Flow modelLSFLinear Signal Flow ModelELNElectrical Linear Networks ModelRFRadio FrequencyLNALow Noise AmplifierPAPower AmplifierEDEnvelop DetectorLPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                  | FLL    | Frequency Locked Loop                                            |

| LSFLinear Signal Flow ModelELNElectrical Linear Networks ModelRFRadio FrequencyLNALow Noise AmplifierPAPower AmplifierEDEnvelop DetectorLPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RTL    | Register Transfer Level                                          |

| ELNElectrical Linear Networks ModelRFRadio FrequencyLNALow Noise AmplifierPAPower AmplifierEDEnvelop DetectorLPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                      | TDF    | Timed Data Flow model                                            |

| RF       Radio Frequency         LNA       Low Noise Amplifier         PA       Power Amplifier         ED       Envelop Detector         LPF       Low-pass Filter         VGA       Variance Gain Amplifier         ADC       Analog to Digital Converter         DAC       Digital to Analog Converter         VCO       Voltage Control Oscillator         PFD       Phase/Frequency Detector         LF       Loop Filter         CP       Charge Pump         PA-FLL       Phase-Aliened Frequency Locked Loop         ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                 | LSF    | Linear Signal Flow Model                                         |

| LNA       Low Noise Amplifier         PA       Power Amplifier         ED       Envelop Detector         LPF       Low-pass Filter         VGA       Variance Gain Amplifier         ADC       Analog to Digital Converter         DAC       Digital to Analog Converter         VCO       Voltage Control Oscillator         PFD       Phase/Frequency Detector         LF       Loop Filter         CP       Charge Pump         PA-FLL       Phase-Aliened Frequency Locked Loop         ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                  | ELN    | Electrical Linear Networks Model                                 |

| PA       Power Amplifier         ED       Envelop Detector         LPF       Low-pass Filter         VGA       Variance Gain Amplifier         ADC       Analog to Digital Converter         DAC       Digital to Analog Converter         VCO       Voltage Control Oscillator         PFD       Phase/Frequency Detector         LF       Loop Filter         CP       Charge Pump         PA-FLL       Phase-Aliened Frequency Locked Loop         ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                        | RF     | Radio Frequency                                                  |

| EDEnvelop DetectorLPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LNA    | Low Noise Amplifier                                              |

| LPFLow-pass FilterVGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PA     | Power Amplifier                                                  |

| VGAVariance Gain AmplifierADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ED     | Envelop Detector                                                 |

| ADCAnalog to Digital ConverterDACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LPF    | Low-pass Filter                                                  |

| DACDigital to Analog ConverterVCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | VGA    | Variance Gain Amplifier                                          |

| VCOVoltage Control OscillatorPFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ADC    | Analog to Digital Converter                                      |

| PFDPhase/Frequency DetectorLFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAC    | Digital to Analog Converter                                      |

| LFLoop FilterCPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VCO    | Voltage Control Oscillator                                       |

| CPCharge PumpPA-FLLPhase-Aliened Frequency Locked LoopELDEarly Late DetectorDLDecision LogicDCODigital Control OscillatorFVCFrequency to Voltage ConverterPPMPulse Position ModulationOOKOn-Off-KeyedPSDPower Spectrum DensityVHDLVery High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PFD    | Phase/Frequency Detector                                         |

| PA-FLL       Phase-Aliened Frequency Locked Loop         ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LF     | Loop Filter                                                      |

| ELD       Early Late Detector         DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CP     | Charge Pump                                                      |

| DL       Decision Logic         DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PA-FLL | Phase-Aliened Frequency Locked Loop                              |

| DCO       Digital Control Oscillator         FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ELD    | Early Late Detector                                              |

| FVC       Frequency to Voltage Converter         PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DL     | Decision Logic                                                   |

| PPM       Pulse Position Modulation         OOK       On-Off-Keyed         PSD       Power Spectrum Density         VHDL       Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DCO    | Digital Control Oscillator                                       |

| OOK     On-Off-Keyed       PSD     Power Spectrum Density       VHDL     Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | FVC    | Frequency to Voltage Converter                                   |

| PSD     Power Spectrum Density       VHDL     Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PPM    | Pulse Position Modulation                                        |

| VHDL Very High Speed Integrated Circuit Hardware Description Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ООК    | On-Off-Keyed                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PSD    | Power Spectrum Density                                           |

| SNR Signal to Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VHDL   | Very High Speed Integrated Circuit Hardware Description Language |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SNR    | Signal to Noise Ratio                                            |

# **1** Introduction

# 1.1 Motivation

In recent years, the super regenerative circuit is re-examined due to its simplicity and power efficiency. It is widely used in short range communication system for robotics, sensor networks and home automation. However, a number of difficulties make the simulation for the radio system quite hard and to examine the behaviour of a super-regenerative radio system, a fast and precise model is highly desirable.

The first problem is the difficulty of including PLL into the analog system due to its high complexity. Therefore, the distortion caused by the frequency differences between the transmitter and receiver (which is important in many applications) cannot be simulated.

Another problem is the accurate and efficient whole radio system modelling, which includes both the analog circuits modelling as well as the digital baseband modelling. As a result, the designers can only evaluate the behaviour of the analog circuits but not the performance of the whole system.

SystemC/SystemC-AMS is a new published effective system-level simulation and modelling language, which offers many advantages which is able to solve the problems mentioned above. First of all, SystemC/SystemC-AMS is a C++ based language which ensures its calculation speed. With the help of fast simulation speed, the simulation time of the system is dramatically reduced. Therefore, the PLL is able to be included into the analog system to simulate the frequency difference between the transmitter and receiver which can be used to calculate the distortion caused by the difference. In addition, with the help of SystemC/SystemC-AMS, it is able to simulate the digital and analog circuits simultaneously. The analog parts use time driven methods while the digital parts use event driven methods. With this capability, it is very convenient to include the digital baseband to the radio system to evaluate the whole performance of the system (such as bit error rate).

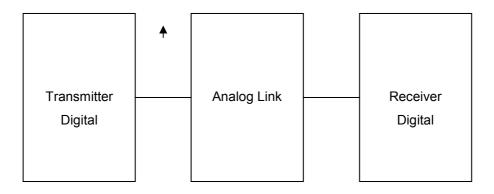

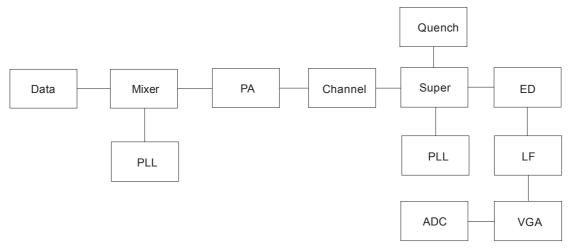

In this thesis, a new mixed signal super-regenerative radio model based on the recently published powerful language SystemC/SystemC-AMS (BETA version) is proposed. In this model, both the analog circuits and the digital circuits are included. The analog part include analog blocks such as Mixer, Power Amplifier, PLL, Envelop Detector, Low-pass Filter, VGA, ADC and so on. Also, many imperfections such as high order harmonies, VCO noise, Charge Pump current mismatch, leakage current, distortion caused by the frequency differences between the transmitter and receiver are included. In the digital system, both the digital baseband for transmitter and receiver are included. In the transmitter part, the data is first encoded according to the PPM algorithm and then transmitted to the analog environment. In the receiver part, the synchronization algorithm for PPM is implemented and the data is decoded and compare with the transmitted data to calculate the bit error rate. Figure 1 shows the structure of the considered whole system, which is divided into 3 parts: the transmitter digital part, the complete analog link and the receiver digital part. The transmitter digital part is used to generate the digital baseband signal to be transmitted. Then, the digital signal will be transferred through the analog part of the radio including the channel. Finally, the receiver digital part is used to recover the data from the output signal of the analog link.

Figure 1 The structure of the whole system.

As mentioned above, with the help of SystemC/SystemC-AMS, it is possible to simulate the whole radio system to evaluate the system performance which is not easy in the past. Also, by comparing its simulation results with the measurement results and the simulation results of the other models, the accuracy of the model and the functionality of the SystemC-AMS are validated.

# 1.2 Thesis goals

This thesis describes a super-regenerative radio model based on the recently published powerful language SystemC/SystemC-AMS (BETA version). In the model, the performance of the whole system is able to simulate. The primary objectives of this work are to:

- Make a fast and accurate PLL model

- Make a model for super-regenerative radio analog circuits

- Include the PLL model into the analog system of a super-regenerative radio

- Make a digital baseband model with SystemC

- Combine the analog system and digital system to simulate the whole performance of the radio system

- Verify the functionality of the model new published language SystemC-AMS

# **1.3 Contributions**

The main contributions of this thesis are shown below:

• Make fast and precise PLL and FLL models

- Make the model to describe the behaviour of the super-regenerative receiver

- Propose a new synchronization algorithm for the PPM modulation to improve system performance

- Implemented the digital baseband algorithms for PPM with SystemC

- Implemented the digital baseband algorithms for PPM with VHDL on FPGA

# **1.4 Thesis organization**

The thesis is organized into the following chapters:

In Chapter 2, there is a brief introduction to SystemC/SystemC-AMS and basic concepts of the super-regenerative radio system. The discussion of the advantages of the SystemC/SystemC-AMS is shown. Also the basic ideas of the PPM modulation are discussed.

Chapter 3 provides an overview of the SystemC/SystemC-AMS model for the analog system of the radio. The organization and key components of the radio system are shown.

Chapter 4 shows the modelling of the PLL used in the analog system. Except the basic functions of the PLL, many imperfections are included in the model proposed in this paper, e.g. VCO noise, PLL Dead Zone, Phase Frequency Detector (PFD) reset delay, Charge Pump (CP) current mismatch, CP leakage current, the reference jitter and Delay difference between the CP control signal.

Chapter 5 shows the FLL SystemC/SystemC-AMS model. Like PLL, many imperfections are included too.

Chapter 6 presents the digital baseband modelling. The digital baseband can be divided into 2 parts, the transmitter part and the receiver part. The transmitter part is used for the PPM modulation and the receiver part is used to realize a synchronization algorithm and verify the corrected data.

Chapter 7 provides the simulation results of the system. The results are verified by both the simulation results of other model and the measurement results.

Chapter 8 includes concluding remarks, and recommendations for future work.

# 2 Background

This chapter provides an overview of the basic concepts of this thesis. In the first part, SystemC/SystemC-AMS and its advantages are discussed and in the second part, the basic ideas about super-regenerative radio are shown. In the third part, a modulation technology called PPM modulation is presented.

# 2.1 Introduction to SystemC/SystemC-AMS

SystemC/SystemC-AMS is an effective system-level simulation and modelling language. SystemC-AMS is a new published language. As a result, not much work has been done to verify it. One purpose of this thesis is to verify the correctness of this language. SystemC/SystemC-AMS has many advantages. First of all, it is a C++ based language which ensures fast calculation speed. Moreover, it can take advantage of C++ power by using a large number of existing C++ functions and libraries. Secondly, SystemC/SystemC-AMS support hardware and software co-design which is very important to the design of a very complex system. Last but not least, SystemC/SystemC-AMS is an open source language, which requires no license fee for the usages.

# 2.1.1 SystemC

SystemC is a C++ based language. It adds a class library to C++ which enables it to describe hardware. SystemC is able to describe the concepts that are familiar with hardware designer, such as signals, modules and ports.

SystemC does not add any new syntax to C++. Instead, it only adds a library class to describe the concepts in hardware design. Thus, SystemC is essentially C++. For this reason, the designers can conveniently use the standard C++ developing tools to simulate, debug and execute all kinds of algorithms and structures. More importantly, with SystemC, we can make a hardware model in system level as well as RTL level. We can first make a system level model to simulate and optimize the design quickly. Then we can transfer the design to RTL level for synthesis.

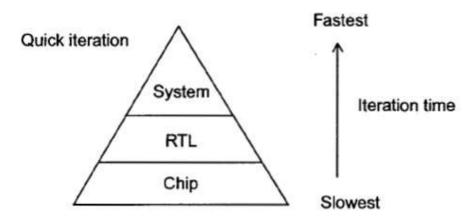

SystemC has many advantages. The first one is its fast simulation speed. Nowadays, system designs become more and more complex. As a result, a fast simulation speed is strongly preferred. As shown in Figure 2, we can see that the iteration time is the highest in chip level and fastest in system level. Thus, to make simulation faster, it is preferred to simulate design in system level. Besides, expressing the design in system level makes the exploration of algorithms and structures easy and quick.

Figure 2 Iteration time of design level [1].

The second advantage of SystemC is the capability of hardware/software co-design. Because of the growing complexity in both the hardware and software domains, partitioning of functions in which domain is desired. This partition could be easily implemented in SystemC since it is able to describe the function either in hardware domain or software domains.

Last but not least, SystemC is an open-source language. There is no license fee to use it.

As discussed above, SystemC is very suitable for modelling the digital circuits. Its main limitation is the disability of simulating analog or mixed signals. For this reason, SystemC-AMS is developed as a complement to deal with this inconvenience.

## 2.1.2 SystemC-AMS

In order to simulate the analog circuits, AMS extensions based on SystemC are introduced. The SystemC-AMS extensions are built on top of the SystemC language standard IEEE 1666-2005. They define additional language constructs, which introduce new execution semantics and system-level modelling methodologies to design and verify mixed-signal systems [2]. They can be further divided into 3 models -- Timed Data Flow model (TDF), Linear Signal Flow model (LSF), Electrical Linear Networks model (ELN).

## 2.1.2.1 TDF model

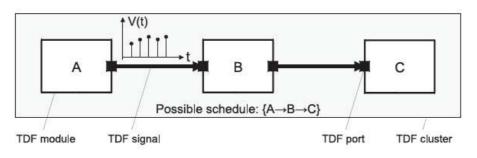

As shown in Figure 3, the TDF model is a discrete-time model. It considers the data as sampled signals in time. Each TDF model is composed of a number of TDF modules which are connected with TDF signals and TDF ports. In each module, C++ methods are used to describe a function that relates the inputs and outputs.

Figure 3 A TDF model with 3 TDF modules [2].

# 2.1.2.2 LSF model

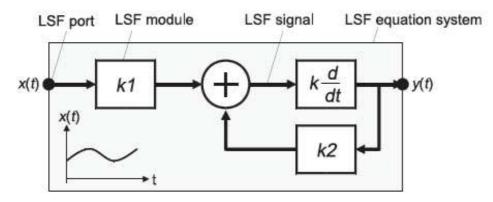

The LSF model is a continuous-time module. This model provides a finite number of LSF modules to implement calculation such as addition, subtraction and multiplication. The users are not allowed to define their own blocks. In other words, LSF model can only be composed with the provided modules. LSF signals are used to connect the modules. In this way, the equation system will be formed to relate the inputs and outputs. Figure 4 shows a basic LSF model.

Figure 4 A LSF model with 4 LSF modules [2].

# 2.1.2.3 ELN model

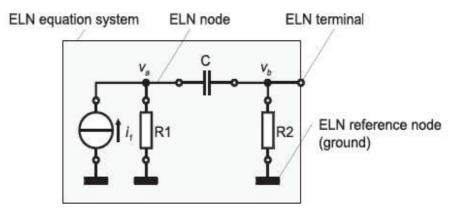

As shown in Figure 5, in ELN model, a set of electrical primitives such as sources (voltage or current), linear lumped elements (resistors, capacitors, inductors) are provided. Designers model the circuit by connecting these primitives with electrical nodes. The system will follow the Kirchhoff's current and voltage laws. ELN terminals are used to communicate with other models.

Figure 5 A basic ELN model [2].

# 2.2 Introduction to super-regenerative radio

The super-regenerative circuit is able to amplify an electrical signal many times by the same vacuum tube or other active component such as a field effect transistor. The circuit has 2 main parts, an amplifier and a feedback loop. The feedback loop connects the output and the input of the amplifier to provide a positive feedback. The idea of the super-regenerative circuit is proposed by Armstrong about 90 years ago. However, it did not attract the attention of engineer for a long period.

In recent years, the super regenerative circuit is re-examined due to its simplicity and power efficiency. It is widely used in short range communication system for robotics, sensor networks and home automation. These applications do not require high data rate but require longer lifetime. As a result, the receiver should be turned off as long as possible. The super-regenerative circuits are very suitable for these applications.

The basic idea of the super-regenerative radio is as follows. The oscillator starts to oscillate when the quenching signal is on and decay when the quenching signal is off. When the quenching signal is on, there are 2 cases. In the first case, there is no input, and the oscillator start to oscillate very slow. As a result, the peak value of the oscillation is small. In the second case, the input signal is not zero, in this case, the oscillator start to oscillate quicker than that with a 0 input and the peak value is big. This difference between the peak values can be used to determine if the data transmitted is 0 or 1. If the transmitter transmits '1', the output of the receiver oscillator will be large because it begins to oscillate earlier. On the contrary, if the data is '0', the output of the receiver oscillator is small.

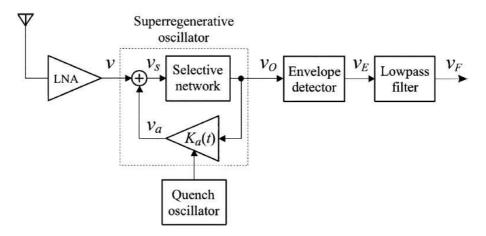

Figure 6 shows the structure of a super-regenerative receiver. The Quench Oscillator is used to generate the quenching signals to control the rise and die out of the RF oscillator. The RF oscillator can be modelled by a selective network and an amplifier. The amplifier provides a feedback from the output of the selective network to the input of the network. The gain of the amplifier is controlled by the quenching signals which make the system alternatively stable or unstable. The work modes of the receiver can be divided into 2 modes, the first is the linear mode and the second one is logarithmic mode. In the linear mode, the oscillation amplitude is not allowed to reach its maximum value. The peak value of the oscillation is proportional to the input signal. In the logarithmic mode, the peak value of the oscillation is the maximum value and the incremental area under the envelope is proportional to the logarithm of the amplitude of the input signal. The system in this thesis use linear mode.

Figure 6 structure of super-regenerative receiver [4].

The super-regenerative oscillator is modelled as a selective network with a feedback amplifier. We will assume that the selective network has two dominant poles providing a band-pass response centred on  $\omega_0$  [4]. The transfer function is shown below (in s-domain):

$$G(s) = K_0 \frac{2\zeta_0 \omega_0 s}{s^2 + 2\zeta_0 \omega_0 s + \omega^2}$$

Or, equivalently:

$$v_O(t) + 2\varsigma_0 \omega_0 v_O(t) + \omega^2 v_O(t) = K_0 2\varsigma_0 \omega_0 v_s(t)$$

Where  $\zeta_0$  is quiescent damping factor and  $K_0$  is the maximum amplification. From Figure 6, we can see that:

$$v_s(t) = v(t) + K_a(t)v_o(t)$$

As a result, the general form of the differential equation of the super-regenerative receiver is:

$$\ddot{v}_O(t) + 2\varsigma(t)\omega_0 \,\dot{v}_O(t) + \omega^2 v_O(t) = K_0 2\varsigma_0 \omega_0 \,\dot{v}(t)$$

Where  $\varsigma(t)$  is equal to  $\varsigma_0 - 2 \varsigma_0 K_a(t) K_0$ . By solving the above equation, we can get the expression of the output of the oscillator.

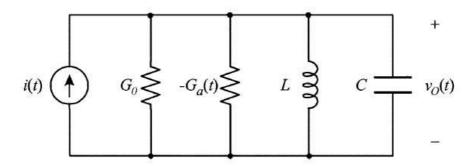

Another method is to model the LNA and oscillator as a parallel resonant circuit which is shown in Figure 7. In the figure, the L represents the load inductor and C represents the capacitor load, the G is the total conductance that is a sum of the parasitic losses of the resonant LC tank in the oscillator

(G0), and the negative conductance provided by the active devices (transistors) in the oscillator (-Ga(t)). The injected signal is the output current of the LNA. It is possible to obtain the equivalence between the parameters of the block diagram (Figure 6) and those of a particular circuit. The equivalence is shown in Figure 8 for parallel RLC circuits.

Figure 7 Parallel resonant circuit represented the LNA and oscillator [4].

| Block<br>diagram | v | $v_O$ | $K_0$          | $\zeta_0$                | ω <sub>0</sub>        | $K_a(t)$ |

|------------------|---|-------|----------------|--------------------------|-----------------------|----------|

| Circuit          | i | vo    | $rac{1}{G_0}$ | $\frac{G_0}{2C\omega_0}$ | $\frac{1}{\sqrt{LC}}$ | $G_a(t)$ |

Figure 8 The equivalence parameters for parallel RLC circuits [4].

# 2.3 Introduction to PPM modulation

In this thesis, the PPM modulation is used to modulate the data. Also a new synchronization algorithm for PPM modulation is presented and implemented with VHDL. In this section, a brief introduction to PPM modulation is shown.

The basic idea of PPM modulation is as follow. Every "x" bits data is translated into  $2^x$  chips, and there is only one "1" among these chips, the position of this chip is decided by the value of the "x" bits. Figure 9 shows a 2 to 4 PPM modulation. From the figure, we can see that the position of the "1" is decided by the value of the 2 bits of the source data. In this thesis, the 4 to 16 PPM modulation is used.

Figure 9 2 to 4 PPM modulation

# 3 Analog parts modelling of the super regenerative radio

In this section, the analog system modelling of the super-regenerative radio system is presented. The structure of the super-regenerative radio is shown in Figure 10. Because the PLL is very important as well as very complex, the discussion of it will be left to the next section, in this part, we will talk about the SystemC/SystemC-AMS model of all the other analog blocks.

As shown in Figure 10. The radio model is composed of twelve blocks, a data block, a mixer block, two PLL blocks, a Power Amplifier (PA) block, a channel block, a super block, a quench block, an Envelope Detector (ED) block, a Low-Pass Filter (LPF) block, a Variance Gain Amplifier (VGA) block and an Analog to Digital Converter (ADC) block. The data block is used to generate the data (replaced by digital baseband later). The mixer block is used to mix the data and the carrier that generate by the PLL in transmitter side. Then the mixed signal is sent to PA to amplify the power. The channel is used to model the transmission channel. The super block is a combination of Low Noise Amplifier (LNA) and receiver oscillator. The oscillator current is provided by Quench block and the oscillation frequency is tuned by the receiver PLL. The Envelop Detector and Low-Pass Filter is used to recover the low frequency baseband signal. The VGA is used to generate the signal that fit the ADC input and the ADC will generate the digital signals that can be processed by the digital baseband. The Quench block is modelled with SystemC and all other blocks (except PLLs) are modelled with SystemC-AMS. Most of them are modelled with TDF model because with TDF model, it is easier to model the non-ideal effect such as harmonies. Also, compare to ELN model, the TDF model is more flexible and can achieve all kinds of behaviour which is especially important for the modelling of some of the blocks such as Super block.

Figure 10 Structure of the super regenerative radio.

# 3.1 The mixer block

The mixer block is modelled as a multiplier and it is modelled with TDF model. It acts as follows: if the data is equal to 1, then the output of the mixer is equal to the PLL output; if the data is equal to 0, the output of the mixer is 0. Part of the source codes of mixers is shown in Figure 11.

```

SCA_TDF_MODULE(mixer) {

sca_tdf::sca_in<bool> in_bit;

sca_tdf::sca_in<double> in_wave;

sca_tdf::sca_out<double> out;

void processing() {

if (data==1)

{out=carrier;}

else

{out=0;}

}

SCA_CTOR(mixer) {}

};

```

Figure 11 Part of source code of mixer.

# 3.2 The power amplifier

The model of the PA includes the multiplier, and the high-order harmonies. It is modelled with TDF model. Part of the source code of PA is shown in Figure 12. In the code, the variable "in" is the input of the power amplifier and "out" is the output. The variable "a", "b", "c" are the gain for each harmonies.

```

out=a*in+b*in*in+c*in*in;

```

Figure 12 Part of the source code for PA

# 3.3 The super block

The super block is the main part to perform the function of super regenerative receiver and it is modelled with TDF model. It is the combination of the LNA and the receiver oscillator. The oscillator current is provided by quench block. By solving the equation mentioned in section 2.2, we can get the solution of the output signal which is equally to:

$$V_{o}(t) = \frac{A \omega_{r} e^{\left(-\frac{G \times t}{2 \times C_{L}}\right)}}{\beta \times |G|} \sin \left(\beta t\right) + \frac{A \sin \left(\omega_{r} t\right)}{|G|}$$

in which  $\beta = \sqrt{\frac{G^2}{4C_L^2} - \frac{1}{L_L C_L}}$ , and  $\omega_r = 2\pi f_r$  where "fr" is the resonant frequency [5], the "A" is

the amplitude of the input signal,  $L_L$  is load inductor,  $C_L$  is load capacitor and G is the total conductance.

The solution mentioned above does not take the frequency difference between the transmitter and the receiver into account. As a result, it is impossible to examine the PLL performance. To examine the PLL performance, the distortion caused by the different between the transmitter frequency and receiver frequency is modelled. The method is shown below:

$$s(t) = e^{\omega_0 \int_0^t \zeta(\lambda) d\lambda}$$

$$\psi(\omega) = \int_{-\infty}^\infty p_c(t) s(t) e^{j\omega t} dt$$

$$H(\omega) = \frac{\omega}{\omega_0} \frac{\psi(\omega - \omega_0)}{\psi(0)}$$

In the equation, the  $_{\varsigma(\lambda)}$  is the quenching signals,  $\omega$  is the transmitter frequency and  $\omega_0$  is the receiver centre frequency. " $p_c(t)$ " is the pulse shaping signal and here it is assume to be one. The distortion caused by the frequency difference between the transmitter and receiver is the absolute value of  $H(\omega)$  and the phase shift is equal to the phase of  $H(\omega)$ .

# 3.4 The quench block

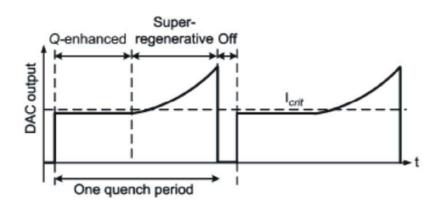

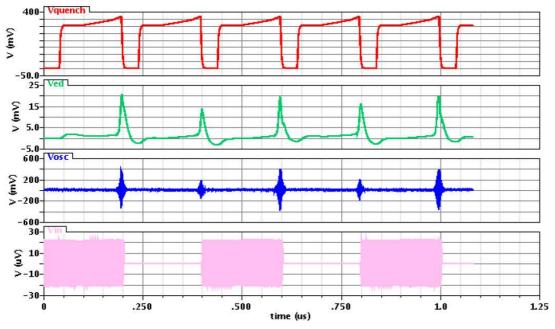

The quench block is used to generate the quenching current that is needed by the receiver oscillator and it is modelled with SystemC. The reason why I use SystemC rather than SystemC-AMS is that in the quenching block, it is needed to generate the period signal which is shown in Figure 13. This is convenience to generate with "wait" statement which is available in SystemC rather than SystemC-AMS. Figure 13 shows the quenching current that generated by this block, in the figure, the dashed line is the value of the critical current. In the Q-enhanced mode, the provided current is a little below the critical current, in the super-regenerative mode, the current will increase exponentially with time and during the off mode, the current will be 0. The code to generate the quenching current is shown in Figure 14. In the code, the 0.01ns is the resolution. The time for super-regenerative mode is equal to 0.01 ms \* 1000 = 10 ms.

Figure 13 Current provided by the quenching block[5].

```

SC MODULE (qunch) {

sc out<double> controls,c,slp;

sc out<bool> rpllc,adcen,qbegin;

sc_in<double> adco;

void prc qunch();

SC CTOR (qunch) {

SC_THREAD(prc_qunch);

}

void qunch::prc qunch() {

while(1){

controls=cr; // "cr" is the critical current searched by the system

wait(Q_time,SC_US); //Q-enhanced mode

for(int i=0;i<1000;i++)//super-regenerative mode</pre>

controls=cr*exp(slope*x);

wait(0.01,SC NS);

t=t+0.01e-9; //0.01e-9 is the resolution

}

t=0;

controls=0; // Off

wait(off time,SC US);

}

}

```

Figure 14 Code for quenching current generation.

Besides providing the quenching current, the quenching block also includes the critical current searching and optimum analog slope searching algorithms. In practical, the critical current is not known, as a result, before the operation start, the system needs to find the critical current autonomously. To address this issue, we consider a critical current searching algorithm, which will be described in detail here. In addition, to gain the best performance, the analog slope of the quenching signal need to be optimized. Thus, an analog slope searching algorithm will also be discussed here.

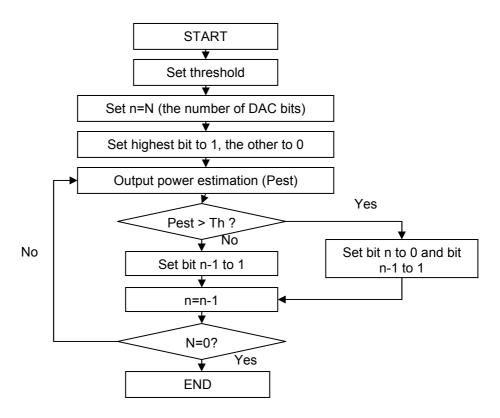

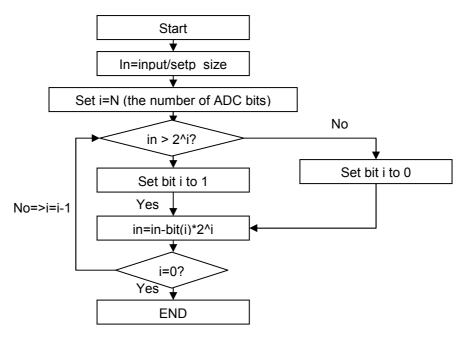

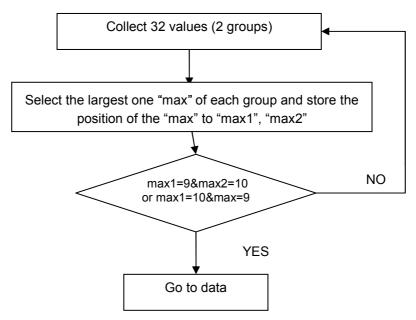

The basic idea of critical current searching algorithm is as follows. A DAC is used to control the quenching current of the VCO, the higher the DAC value, the higher the quenching current. The input of the receiver is set to 0. We change the DAC value, if the VCO oscillate, then decrease DAC value, if not, increase the DAC value. The critical current of the VCO will be found after several iterations (number of DAC bits). Figure 15 shows the steps of this algorithm. In the algorithm, the quench block will first set the highest bit of DAC to 1 and other bits to 0, then, it will estimate the output power of the VCO. If the power is larger than a threshold which means the VCO oscillated, it will set bit n to 0 and bit n-1 to 1. If the power is smaller than the threshold, bit n will remain to 1 and n-1 is set to 1 too. This will iterate for N times (N is the DAC bit number). Then the critical current will be found.

The optimum analog slope searching algorithm is nearly the same with critical current searching except that the DAC is used to control the analog slope rather than the quenching current.

Figure 15 Critical current searching.

# 3.5 The envelop detector

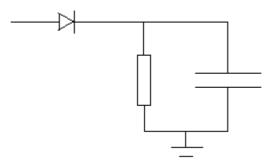

The structure of an envelope detector is shown in Figure 16. When the input wave's amplitude increases, the capacitor voltage is increased via the rectifying diode. When the input's amplitude falls, the capacitor voltage is reduced by being discharged by a resistor, R. In this way, the "envelope" of the input signal will be detected. The modelling of this block is composed of 2 parts. The first part is the diode which is modelled with TDF model and the second part is the parallel capacitor and resistor which is modelled with ELN model.

Figure 16 The structure of envelop detector.

# 3.6 Low-pass filter

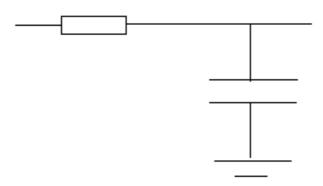

The low pass filter is modelled as a basic RC filter with the TDF model and the Laplace transfer function. It is also able to be modelled with ELN model. But the results are same. The structure of the low pass filter is shown in Figure 17. Part of the source code for low pass filter is shown in Figure 18. In the code, the ltf\_1 is the Laplace transfer function which is used to form the low pass characteristic of the filter. The "freq cut" is the cut off frequency.

Figure 17 Structure of low-pass filter

```

SCA_TDF_MODULE(lowpass) {

sca_tdf::sca_in<double> in;

sca_tdf::sca_out<double> out;

sca_tdf::sca_ltf_nd ltf_1;

double freq_cutoff;

sca_util::sca_vector<double> Nom, Denom;

void processing() {

out.write(ltf_1(Nom,Denom, in.read()));

}

lowpass(sc_module_name n, double freq_cut) {

Nom(0)= 1.0; Denom(0)=1.0;

Denom(1)= 1.0/(2.0*M_PI*freq_cut);

};

};

```

Figure 18 Part of the source code of the low pass filter.

# 3.7 The VGA

The VGA is modelled as a multiplier that used to adjust the signal amplitude to the ADC requirement. It is modelled with TDF model.

# 3.8 ADC

The ADC is used to transfer the analog signal to the digital signal that can be processed by the digital baseband. It is modelled with TDF model. The modelling method is shown in Figure 19, it acts as follows: first set the i to the number of ADC bits N, then compare the input value to  $2^i$ , if

the input is lager, bit i will be set to 1, else, it is set to zero. Then subtract  $bit(i) \times 2^i$  is subtracted from the input value and goes into the next iteration. The algorithm will iterate N times and then the output will be sampled by the digital baseband.

Figure 19 ADC modeling.

# 4 Phase Locked Loop (PLL) modelling

In the radio system, integer PLL is used to synthesize new frequencies which are integer or fractional times of a reference frequency, with the same stability as the reference frequency. Compare to other blocks of the super-regenerative radio, the PLL is the most complex block which composed of both analog parts and digital parts. In this section the frequency analysis and time model of the PLL are shown.

# 4.1 Frequency analysis of the PLL

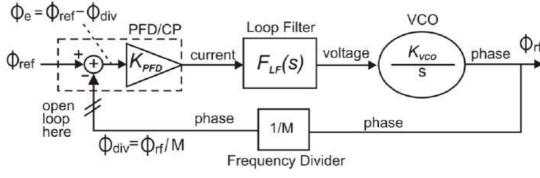

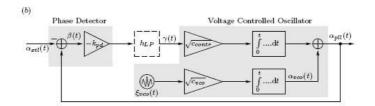

Transient response of phase-locked loops is a nonlinear phenomenon that cannot be formulated easily. However, a linear approximation can be used to gain intuition and understand trade-offs in PLL design. A liner-time continuous PLL model can be used to analyze the PLL in phase domain [6]. The linear model is shown in Figure 20. The output phase of the VCO is  $\Phi$ rf, then the divider will divide the phase by M and the phase become  $\Phi$ div =  $\Phi$ rf / M. The transfer function of the Loop Filter is  $F_{LF}$  (s) and the VCO gain is  $K_{VCO}$ . The VCO is modelled as an integrator and the transfer function of which is " $K_{VCO}$ /s", the K<sub>PFD</sub> is modelled as  $I_{CP}$ , where  $I_{CP}$  is charge pump current.

Figure 20 Linear model of the PLL[6].

The open loop transfer function is:

$$H_O(s) = \frac{K_{VCO}}{s} I_{CP} \frac{F_{LF}(s)}{M}$$

[6]

As a result, the close loop transfer function is:

$$H_{CL}(s) = \frac{H_O(s)}{1 + H_O(s)} = \frac{K_{VCO}I_{CP}F_{LF}}{sM + K_{VCO}I_{CP}F_{LF}}$$

<sup>[6]</sup>

# 4.2 The SystemC/SystemC-AMS model

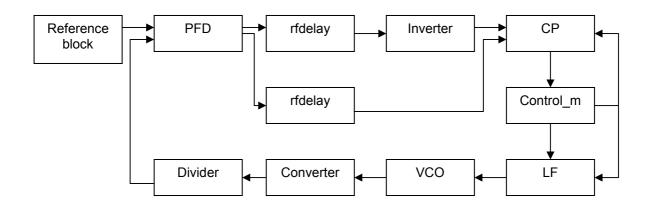

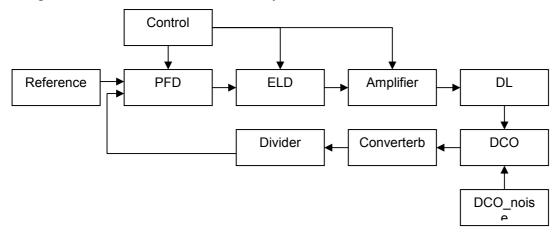

The structure of the integer PLL that modelled in this paper is shown in Figure 21.

Figure 21 Structure of the PLL.

As shown in Figure 21, the model is composed of eleven blocks, a reference clock block, a phase/frequency detector block, two rfdelay blocks, an inverter block, a charge pump block, a control\_m block, a loop filter (LF) block, a voltage control oscillator block, a converterb block and a divider block. The reference clock block is used to generate reference signal, the phase/frequency detector block is used to detect the phase/frequency difference between the reference signal and the divider output. After the PFD, The signal goes into rfdelay block and inverter to generate the signals that control the charge pump. Then CP will charge the loop filter to generate the VCO control voltage. The control\_m block is used to limit the output voltage of the loop filter. The converter block transfers the VCO analog output signal to a digital input signal that is suitable for the frequency divider.

#### 4.2.1 Reference clock block

The reference block is used to generate the reference clock of the PLL. Part of the code of reference block is shown in Figure 22. It works as follows: assume the period of the reference clock is T, then every T/2, the output will reverse its value. The function "gauss()" is used to generate a gauss random number with 0 mean and variance of 1.0e-9 which is used to model the reference jitter.

```

SC MODULE (reference) {

sc out<bool> a;

sc in<double> ref;

void prc reference();

SC CTOR (reference) {

SC_THREAD(prc_ reference);

}

};

void reference::prc reference() {

while(1)

{

a=!a;

wait(ref+gauss(1.0e-9),SC US);

a=!a;

wait(ref+gauss(1.0e-9),SC US);

}

}

```

Figure 22 Part of source codes of the reference clock block.

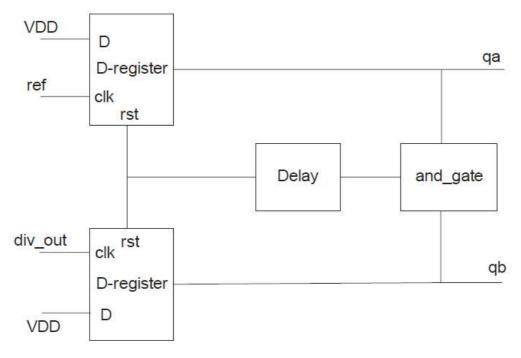

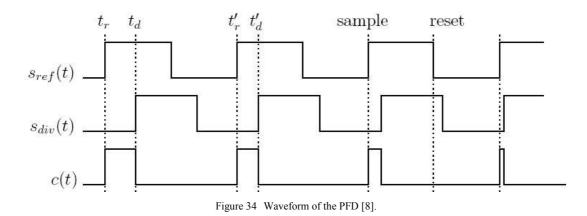

#### 4.2.2 The PFD block

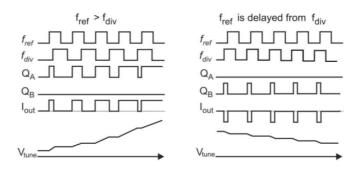

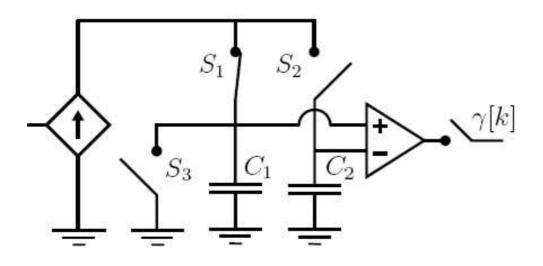

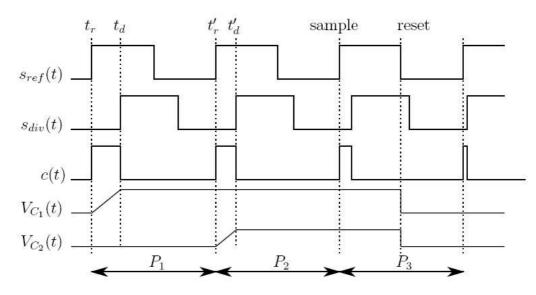

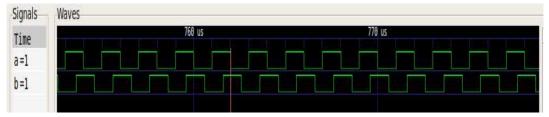

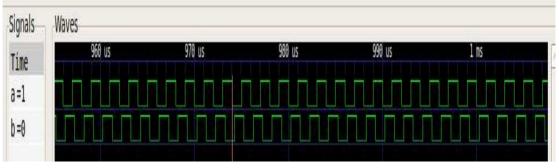

The structure of the PFD is shown in Figure 23, it is composed of two D-registers, a delay block and an and-gate. The signals of interest, reference clock and divider output, serve as the clock of the registers. The inputs (D) of the registers are connected to "1". The registers' outputs qa and qb will be the output of PFD. If qa and qb are both 0 and there is a rising edge in reference clock, qa will become 1. If this follows by a rising event in divider output the qb will become 1 and reset the registers. A delay block is introduced to model the reset-delay. Also it can be used to eliminate the dead zone. In this way, as shown in Figure 24, the phase and frequency difference will be detected. If the reference frequency is larger than that of divider output or reference phase leads to the divider output phase, there will be a pulse in qa and qb is equal to 0 (maybe with very small pulse because of the reset delay). On the contrary, if the reference frequency is smaller than that of divider output phase, there will be a pulse in quite reference frequency is equal to 0.

Figure 23 Structure of the PFD.

Figure 24 PFD waveform [6].

#### 4.2.3 The rfdelay block

In practice, both the rising edge and the falling edge of a digital signal are non ideal, i.e. there is some delay when the signal changing from "1" to "0" or from "0" to "1". This is the cause of PLL Dead Zone. The rfdelay block is used to model this behaviour. Part of the code of this block is shown 0. It acts as follows: when there is a positive or negative event in the input, the output will increase or decrease gradually until it is larger than "max" V or smaller than "min" V. During the rising or falling behaviour, if the input changes, the output will alter its changing direction.

```

SC MODULE (rfdelay) {

sc in<bool> clear in;

sc out<double> clear out;

void prc rfdelay();

SC CTOR(rfdelav) {

SC_THREAD(prc_rfdelay);

}

};

void rfdelay::prc_rfdelay() {

while(1) {

wait(clear in.value changed event());

if(clear in==1)

while(clear out<max){</pre>

b:

clear out=clear out+increase step; //input=1, increase the output

wait(0.1,SC_NS); //time step size

if(clear in==0){goto a;} //input changes to 0

}

}

else

{

while(clear_out>min) {

a:

clear out=clear out-decrease step; //input=0, decrease the output

wait(0.1,SC NS);

if(clear in==1){goto b;} //input changes to 1

}

}

}

}

```

Figure 25 Part of source codes of the rfdelay block.

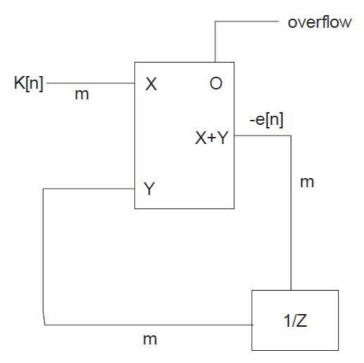

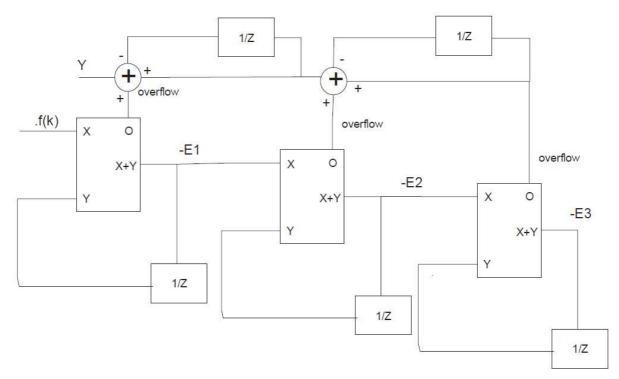

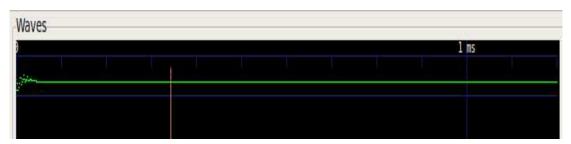

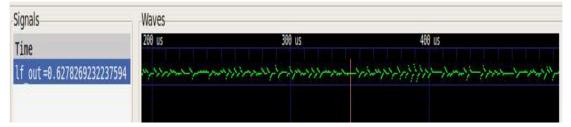

#### 4.2.4 Inverter