# A Mixed-Signal Multiplexing System for Cable-Count Reduction in Ultrasound Probes

# Qilong Liu

EEMCS

**Challenge the future**

# A Mixed-Signal Multiplexing System for Cable-Count Reduction in Ultrasound Probes

Ву

# Qilong Liu (student number: 4229568)

in partial fulfilment of the requirements for the degree of

Master of Science in Microelectronics

at the Delft University of Technology, to be defended publicly on Tuesday March 18, 2015 at 14:00.

This thesis is confidential and cannot be made public until March 18, 2016.

An electronic version of this thesis is available at <u>http://repository.tudelft.nl/</u>.

### DELFT UNIVERSITY OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING

The undersigned hereby certify that they have read and recommend to the Faculty of Electrical Engineering, Mathematics and Computer Science for acceptance a thesis

entitled

# A MIXED-SIGNAL MULTIPLEXING SYSTEM

### FOR CABLE-COUNT REDUCTION

# IN ULTRASOUND PROBES

by

# QILONG LIU

# in partial fulfilment of the requirements for the degree of MASTER OF SCIENCE MICROELECTRONICS

Dated: March 18, 2015

Dr.ir.Michiel Pertijs

Ir. Chao Chen

Dr.ir.Michiel Pertijs

Dr.Marco Spirito

Dr.ir. Martin Verweij

Ing .Christian Prins

Supervisor(s):

Reader(s):

# **Table of Contents**

| Chapter 1 Introduction                                                                                 | 1  |

|--------------------------------------------------------------------------------------------------------|----|

| 1.1 Background                                                                                         | 1  |

| 1.2 Design Considerations                                                                              | 3  |

| 1.2.1 Signal Properties                                                                                | 3  |

| 1.2.2 Cable Property                                                                                   | 3  |

| 1.2.3 Power and Area Restrictions                                                                      | 4  |

| 1.3 Solutions                                                                                          | 4  |

| 1.3.1 Possibilities and Limitations                                                                    | 4  |

| 1.3.2 Introduction to the Thesis Work                                                                  | 4  |

| 1.4 Summary                                                                                            | 5  |

| 1.5 References                                                                                         | 6  |

| Chapter 2 Multiplexing and Cable Modelling                                                             | 7  |

| 2.1 Comparison between Multiplexing Schemes                                                            | 7  |

| 2.2 Spectral Characteristics of Time-multiplexing                                                      | 10 |

| 2.3 Cable Modelling                                                                                    |    |

| 2.3.1 Cable Characterization                                                                           |    |

| 2.3.2 Transmission Line Effect of a Micro-Coaxial Cable                                                | 15 |

| 2.4 Summary                                                                                            |    |

| 2.5 References                                                                                         |    |

| Chapter 3 Equalization                                                                                 | 24 |

| 3.1 Basics of Equalization                                                                             | 24 |

| 3.1.1 Location of the Equalizer                                                                        | 24 |

| 3.1.2 Continuous-Time and Discrete-Time Equalization                                                   | 24 |

| 3.1.3 ADC-Based Equalization                                                                           | 27 |

| 3.2 Equalization Algorithms                                                                            |    |

| 3.2.1 Zero-Forcing Equalization (ZFE)                                                                  |    |

| 3.2.2 MMSE Equalization                                                                                |    |

| 3.3 Summary                                                                                            |    |

| 3.4 References                                                                                         |    |

| Chapter 4 System Design and Optimization                                                               |    |

| 4.1 Topology Selection of Driver                                                                       |    |

| 4.1.2 Current Mode or Voltage Mode                                                                     |    |

| 4.1.3 Single-Ended or Differential                                                                     |    |

| 4.2 Topology Selection of RX                                                                           |    |

| 4.3 System Modelling and Optimization                                                                  | 40 |

| 4.3.1 Noise Analysis                                                                                   | 40 |

|                                                                                                        |    |

| 4.3.2 Determination of Transconductance                                                                |    |

| <ul><li>4.3.2 Determination of Transconductance</li><li>4.3.3 Fine Model for SNR Calculation</li></ul> | 41 |

| 4.4 Summary                                                      |     |

|------------------------------------------------------------------|-----|

| 4.5 References                                                   |     |

| Chapter 5 Circuit Implementation                                 | 50  |

| 5.1 Multiplexing Configuration                                   |     |

| 5.1.2 Input Multiplexing                                         |     |

| 5.1.3 Output Multiplexing                                        |     |

| 5.2 Sampling Capacitor Array                                     |     |

| 5.3 Transconductor Design                                        | 53  |

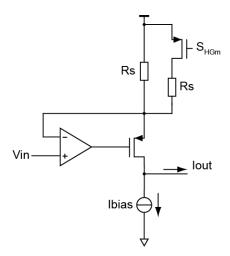

| 5.3.1 Source-Degeneration Topology                               | 53  |

| 5.3.2 Implementation of the Helper Amplifier                     | 55  |

| 5.3.3 Transconductor Implementation                              | 56  |

| 5.3.4 Biasing System                                             | 57  |

| 5.4 Auto-Zeroing                                                 |     |

| 5.5 Design of Multiplexing Switch                                | 60  |

| 5.5.1 Current-Steering Multiplexing Switch                       | 60  |

| 5.5.2 Timing of the Multiplexing Switch                          | 61  |

| 5.6 Active Biasing                                               | 64  |

| 5.7 Testability Design                                           | 64  |

| 5.7.1 MUX for Monitoring Node Selection                          | 64  |

| 5.7.2 High-Transconductance Mode                                 | 65  |

| 5.7.3 Test Transconductor                                        | 66  |

| 5.8 Layout Overview                                              | 66  |

| 5.9 Summary                                                      | 68  |

| 5.10 References                                                  | 69  |

| Chapter 6 Measurement                                            | 72  |

| 6.1 Measurement Setup                                            | 72  |

| 6.2 Measurement Results                                          |     |

| 6.2.1 Measurement without Equalization                           |     |

| 6.2.2 Measurements with Equalization                             |     |

| 6.3 References                                                   |     |

| Chapter 7 Conclusion                                             |     |

| 7.1 Thesis Contributions                                         |     |

| 7.2 Potential Improvements                                       |     |

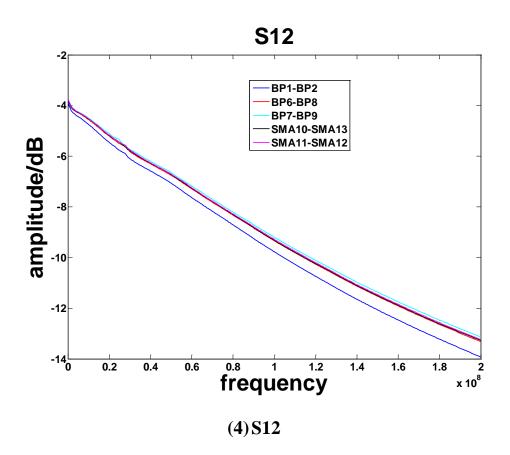

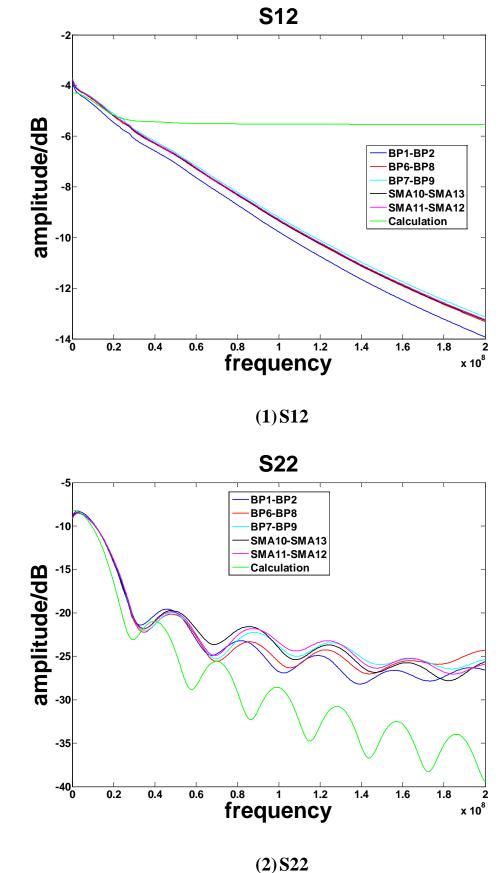

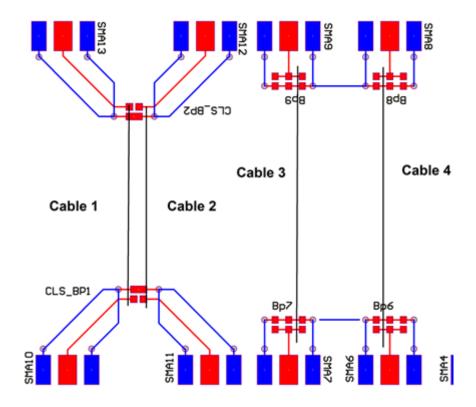

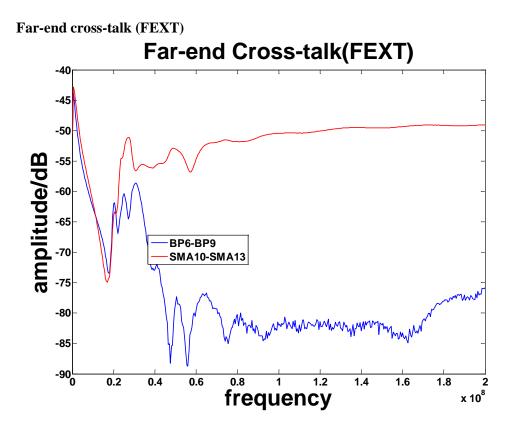

| Appendix A VNA Measurement                                       |     |

| Appendix B Multi-Input-Multi-Output (MIMO) Equalization          | 120 |

| Appendix C Current Mode or Voltage Mode                          | 125 |

| Appendix D Comparison between Several Trans-conductor Candidates | 126 |

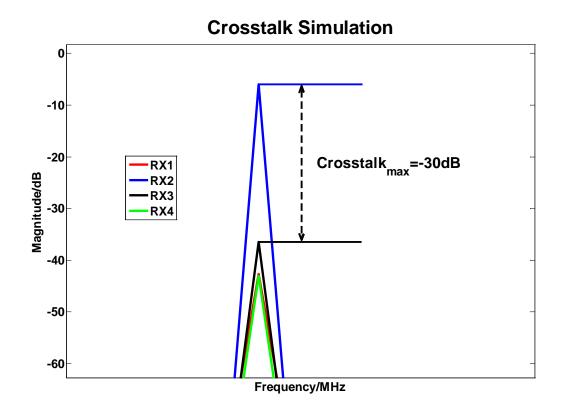

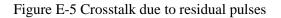

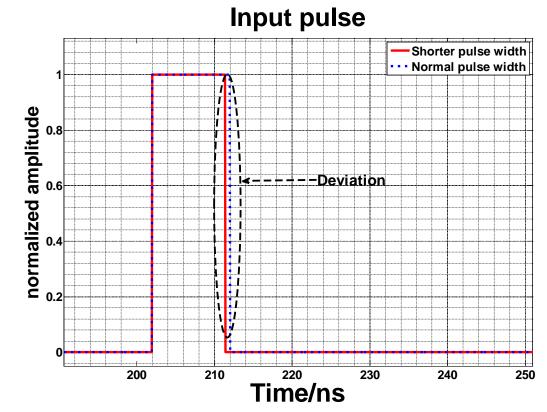

| Appendix E Possible Reasons for the Overlarge Crosstalk          | 130 |

| Appendix F Mismatch Analysis                                     |     |

# **List of Figures**

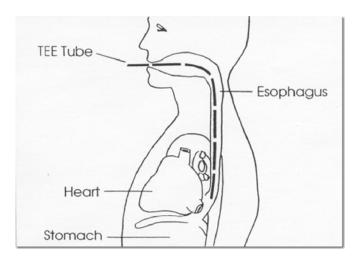

| Figure 1-1 TEE diagram                                                                      | 1  |

|---------------------------------------------------------------------------------------------|----|

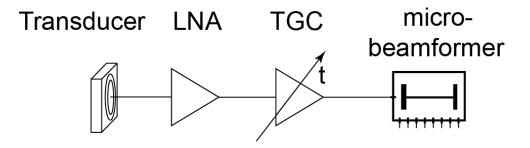

| Figure 1-2 Analog front end (AFE) with a transducer element                                 | 2  |

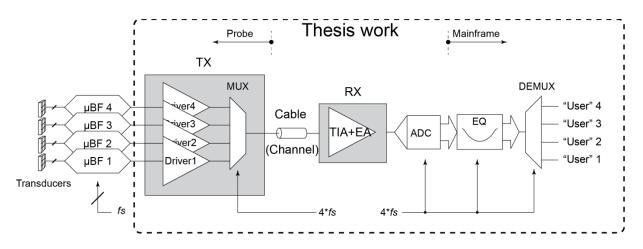

| Figure 1-3 Building blocks of the thesis project                                            |    |

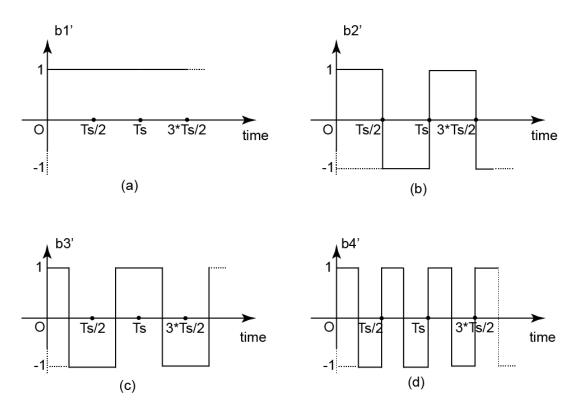

| Figure 2-1 Square-wave modulation carriers for different drivers in the modified FDM scheme | 8  |

| Figure 2-2 Spectrum spreading character of CDM                                              |    |

| Figure 2-3 TDM control                                                                      | 9  |

| Figure 2-4 Time and frequency domain of multiplexed signals                                 | 12 |

| Figure 2-5 Lumped model of a unity-length micro-coaxial cable                               | 13 |

| Figure 2-6 Extracted R, L, C, G from VNA measurement                                        | 13 |

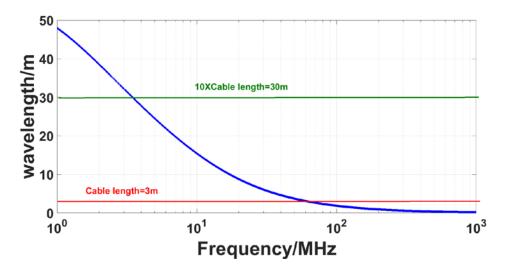

| Figure 2-7 Wavelength of EM wave in the micro-coaxial cable                                 | 14 |

| Figure 2-8 Configuration of voltage mode transmission                                       |    |

| Figure 2-9 Pulse response in a single-ended matching voltage mode transmission              | 15 |

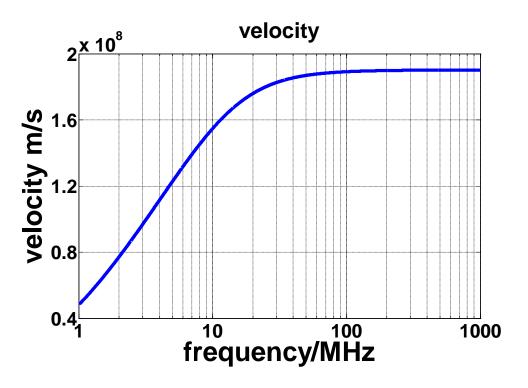

| Figure 2-10 Propagation velocity Vs. frequency                                              |    |

| Figure 2-11 Characteristic impedance of the micro-coaxial cable                             | 17 |

| Figure 2-12 Pulse response of a double-ended unmatched transmission line                    |    |

| Figure 2-13 Noise parameters in the 2-port network                                          | 18 |

| Figure 2-14 Decomposition of a 2-port network based on the noise source separation          |    |

| Figure 2-15 Noise contributors in <i>Gn</i>                                                 |    |

| Figure 2-16 Correlation coefficient, Ycor, obtained from VNA measurement                    |    |

| Figure 3-1 Continuous-time EQ                                                               |    |

| Figure 3-2 pulse response of current mode transmission                                      |    |

| Figure 3-3 Frequency response of current mode transmission with different loads             |    |

| Figure 3-4 One example of discrete-time equalization                                        |    |

| Figure 3-5 ADC-based equalization                                                           |    |

| Figure 3-6 Noise enhancement of ZFE                                                         |    |

| Figure 3-7 MMSE equalization                                                                |    |

| Figure 4-1 Input impedance seen from the output of a driver                                 |    |

| Figure 4-2 Input impedance versus frequency                                                 |    |

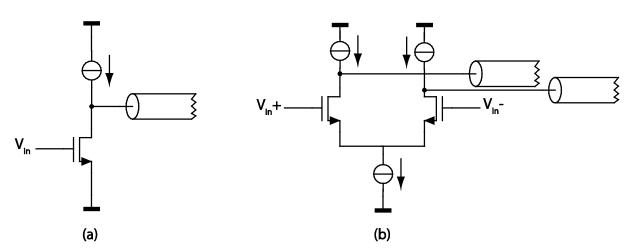

| Figure 4-3 Single-ended and differential current-mode transconductors                       |    |

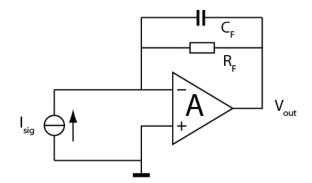

| Figure 4-4 TIA as the first stage on RX side                                                |    |

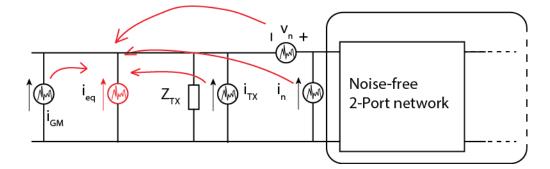

| Figure 4-5 Calculation of the equivalent noise current from a 2-port network                |    |

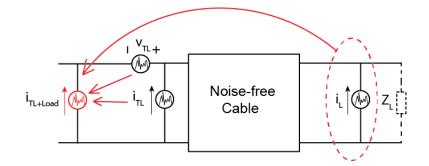

| Figure 4-6 Calculation of the equivalent noise current of a 2-port network with load        |    |

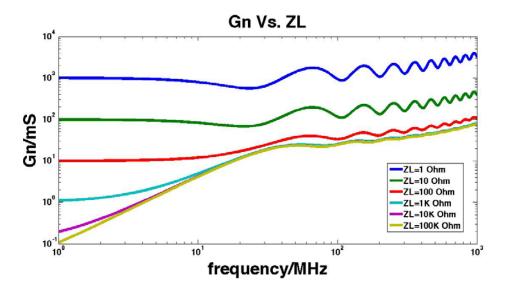

| Figure 4-7 Equivalent noise transconductance <i>Gn</i> for different resistive <i>ZL</i> 's |    |

| Figure 4-8 Signal chain used in the fine SNR model                                          |    |

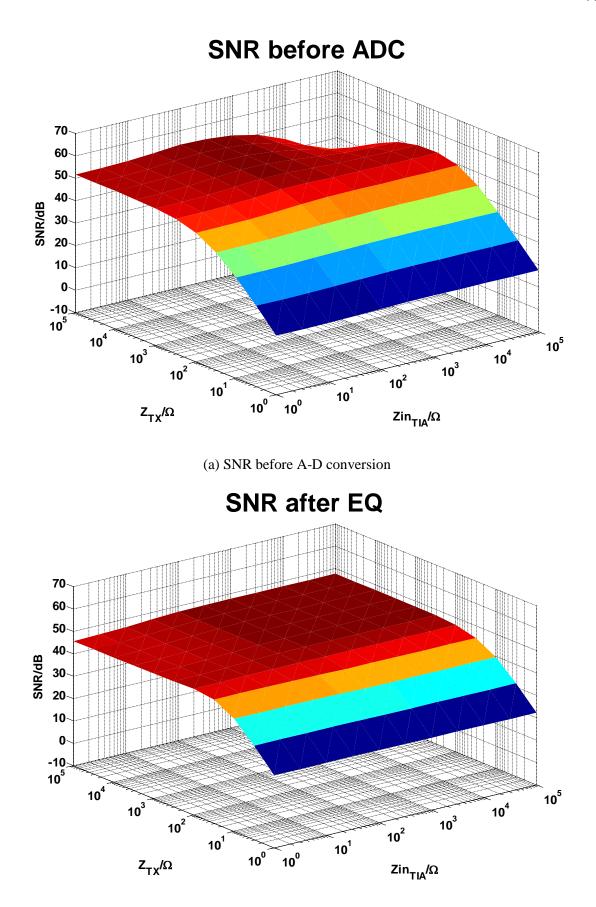

| Figure 4-9 SNR versus different ZTX's and Zin, TIA's                                        |    |

| Figure 4-10 Simple current mode transmission for equalization model                         |    |

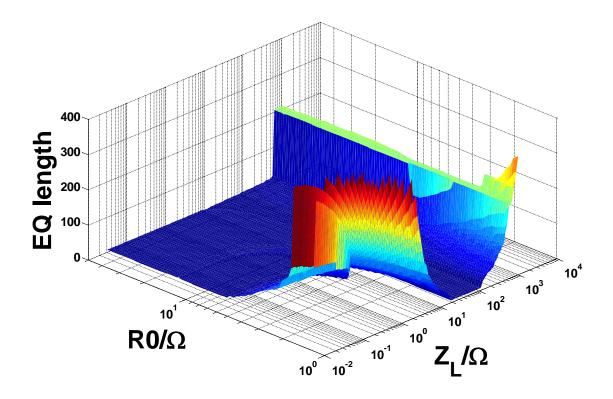

| Figure 4-11 Simulated shortest equalizer length needed to obtain -40dB PD,                  |    |

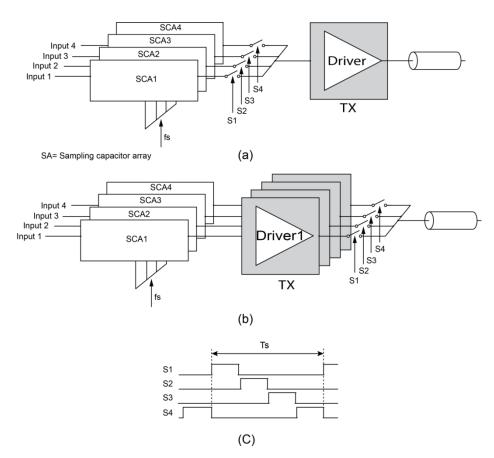

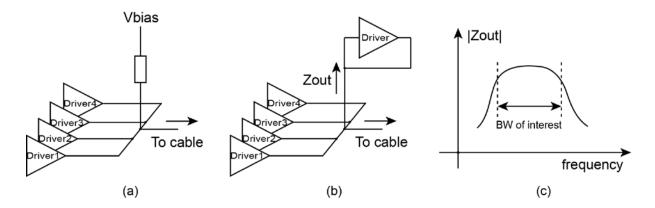

| Figure 5-1 Two configurations of a multiplexing system                                      |    |

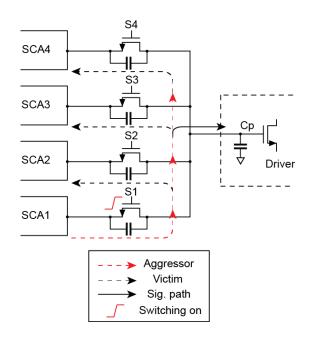

| Figure 5-2 Crosstalk in input multiplexing                                                  |    |

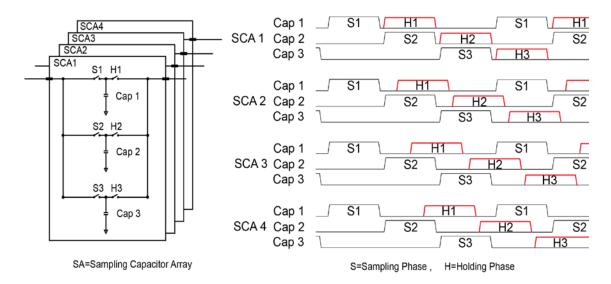

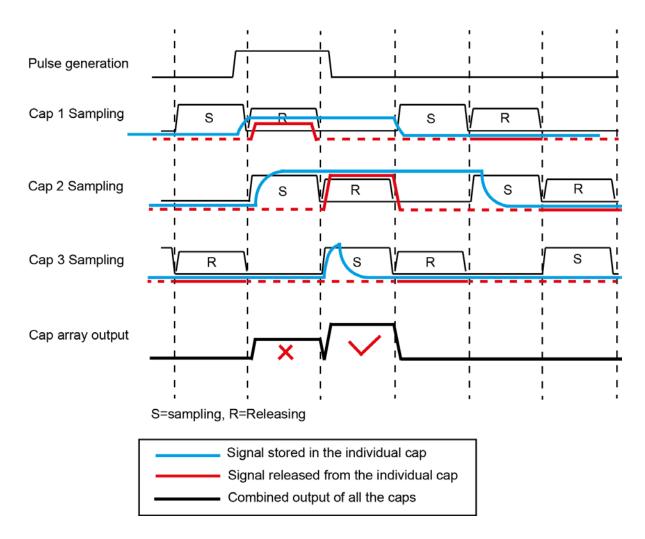

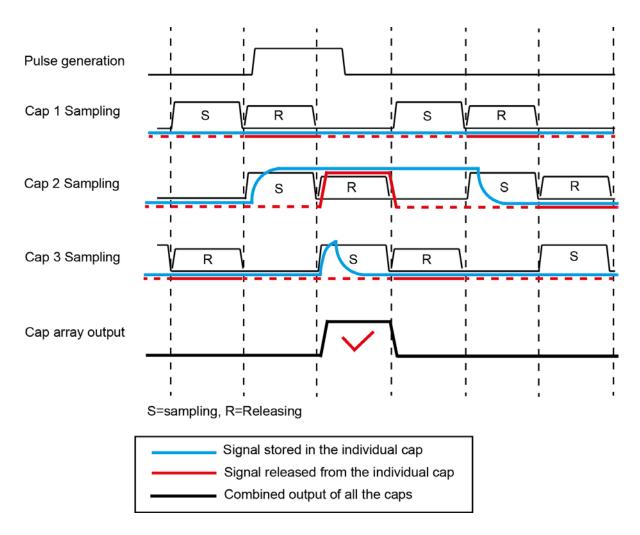

| Figure 5-3 Timing of 4-input sampling capacitor arrays                                      |    |

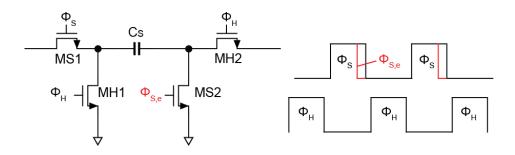

| Figure 5-4 Stray-insensitive bottom-plate sampling                                          |    |

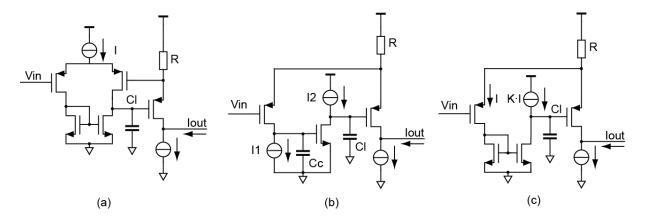

| Figure 5-5 Amplifier-assisted source-degenerated transconductor                             |    |

| Figure 5-6 Amplifier-assisted source-degenerated transconductor                             |    |

| Figure 5-7 Other amplifier-assisted source-degenerated transconductors [5.3][5.4]           |    |

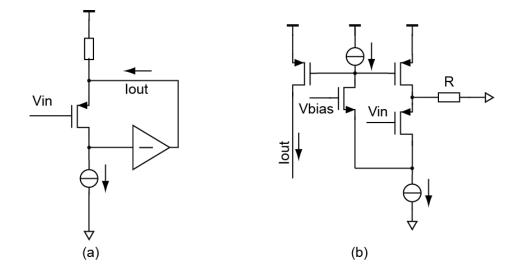

| - Pare - A and any mer assisted source defendation numberinderons [2:2][2:4]                |    |

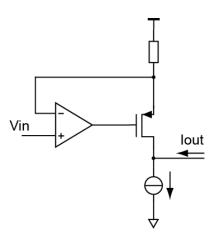

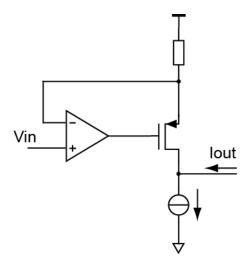

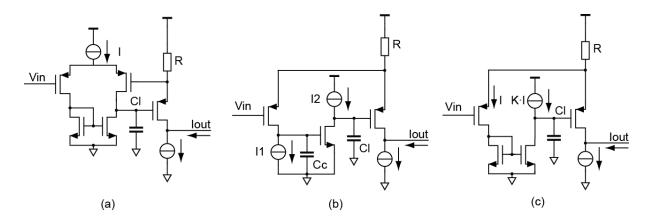

| Figure 5-8 Candidates for current-efficient helper amplifiers                   | 55  |

|---------------------------------------------------------------------------------|-----|

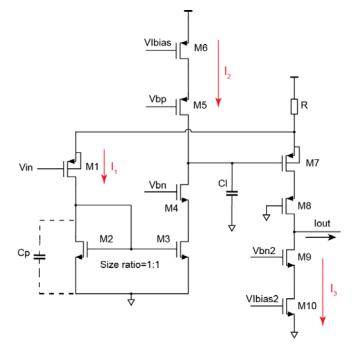

| Figure 5-9 Implementation of the proposed transconductor                        | 56  |

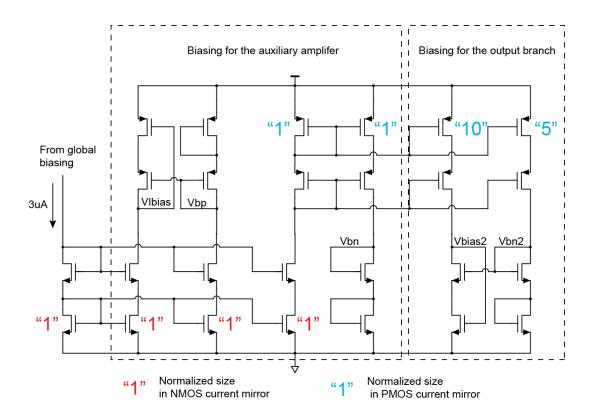

| Figure 5-10 Global biasing circuit                                              | 57  |

| Figure 5-11 Local biasing circuit                                               | 58  |

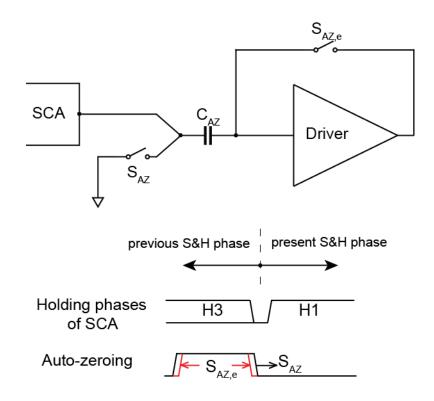

| Figure 5-12 Auto-zeroing circuit implemented in the project                     | 59  |

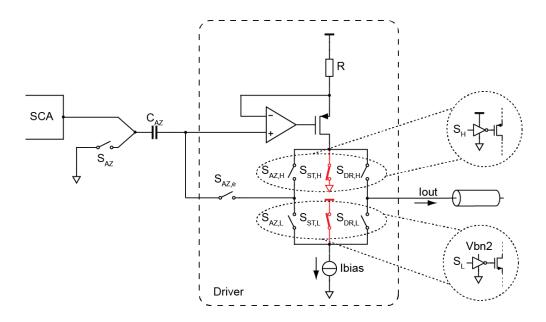

| Figure 5-13 Multi-phase operation of a transconductor                           | 61  |

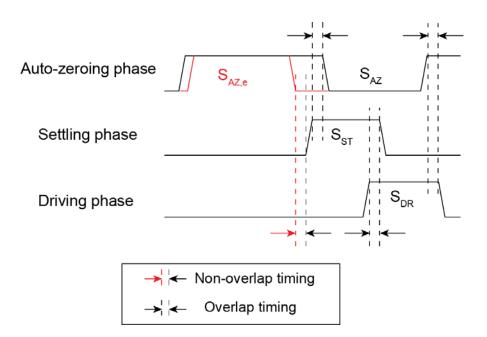

| Figure 5-14 Timing of the current steering in output multiplexing               | 62  |

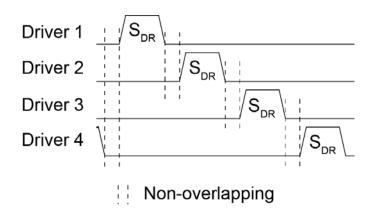

| Figure 5-15 Non-overlapping timing during driver switching                      | 62  |

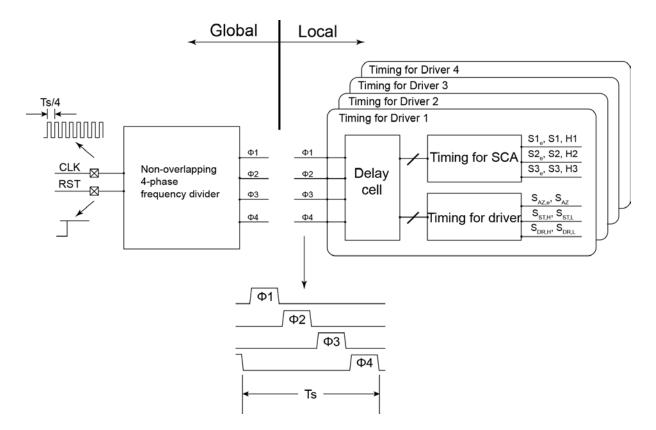

| Figure 5-16 Organization of the timing control                                  | 63  |

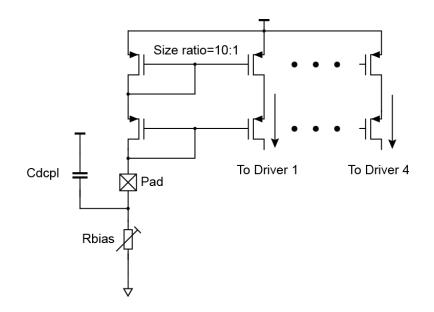

| Figure 5-17 Cable biasing                                                       | 64  |

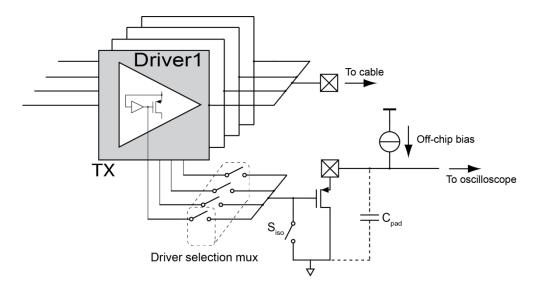

| Figure 5-18 Driver selection MUX                                                | 65  |

| Figure 5-19 High transconductance mode                                          | 65  |

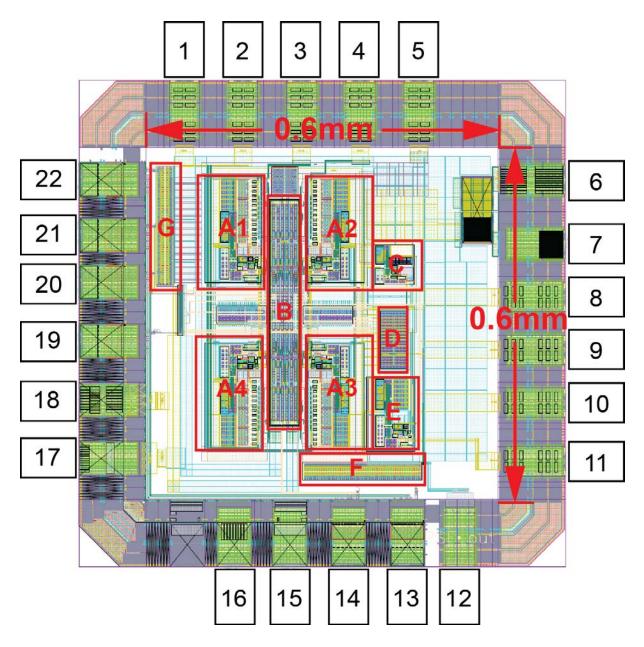

| Figure 5-20 Layout of the current mode analog multiplexer                       |     |

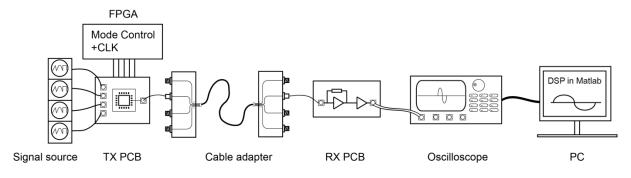

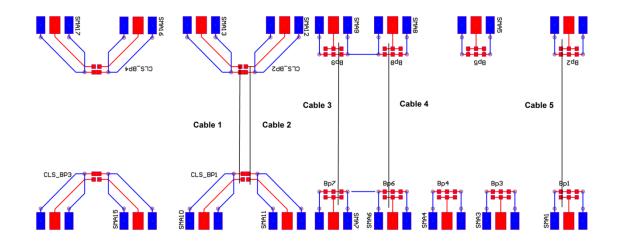

| Figure 6-1 Overview of the whole system                                         |     |

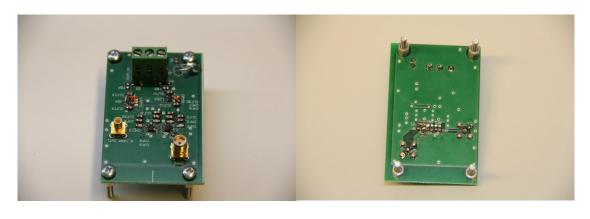

| Figure 6-2 Transmitter PCB                                                      |     |

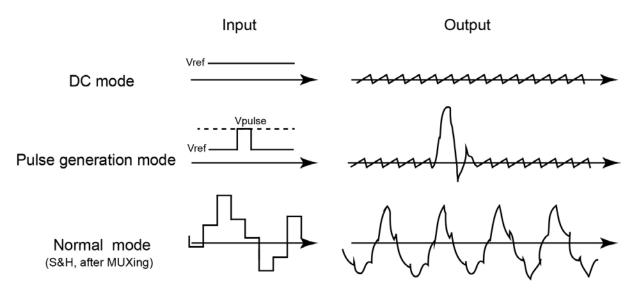

| Figure 6-3 Operation modes of the TX PCB                                        |     |

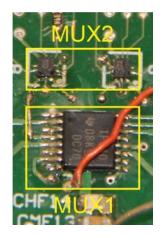

| Figure 6-4 Mode selection MUXes                                                 |     |

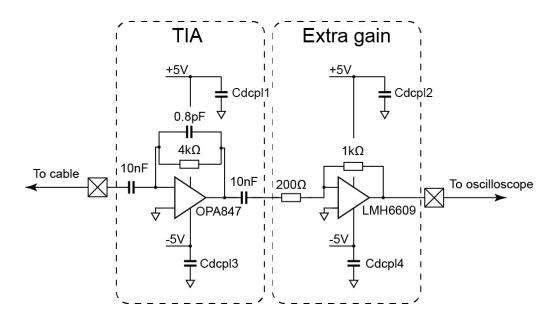

| Figure 6-5 Schematic of RX PCB                                                  |     |

| Figure 6-6 Receiver PCB                                                         |     |

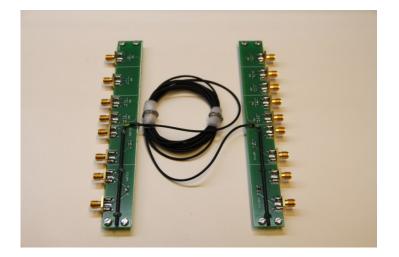

| Figure 6-7 Cable adapter                                                        |     |

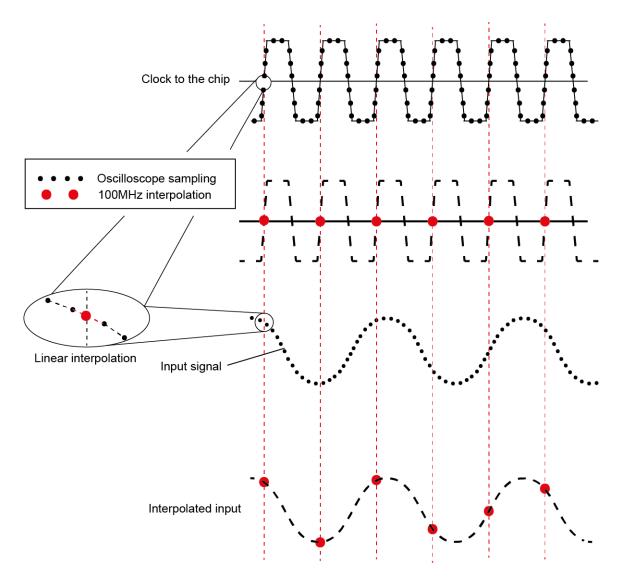

| Figure 6-8 Zero-crossing interpolation                                          |     |

| Figure 6-9 Wrong timing of pulse generation control without phase tuning        |     |

| Figure 6-10 Correct timing of pulse generation control obtained by phase tuning |     |

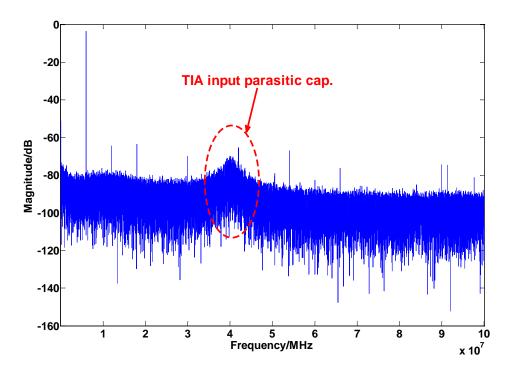

| Figure 6-11 Spectrum of the TIA's output in TX driver test                      |     |

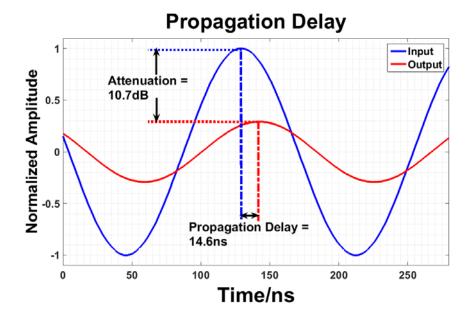

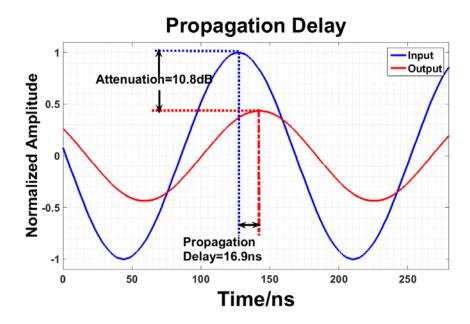

| Figure 6-12 Measured propagation delay and attenuation of the cable             |     |

| Figure 6-12 Calculated propagation delay and delay of the cable                 |     |

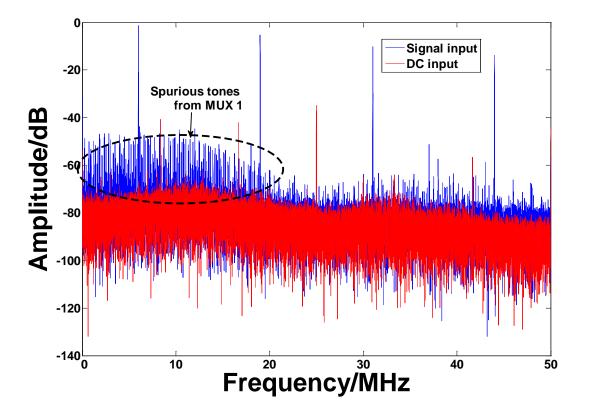

| Figure 6-14 Signal spectrum without equalization (one input case)               |     |

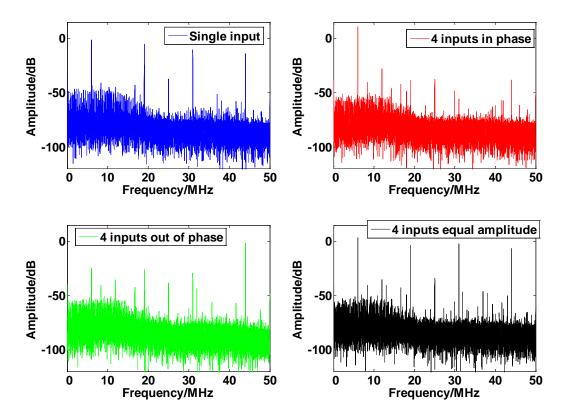

| Figure 6-15 Output spectrum with different phase combinations                   |     |

| Figure 6-16 TX distortion                                                       |     |

| Figure 6-17 RX distortion                                                       |     |

| 6                                                                               |     |

| Figure 6-18 Measurement flow with equalization                                  |     |

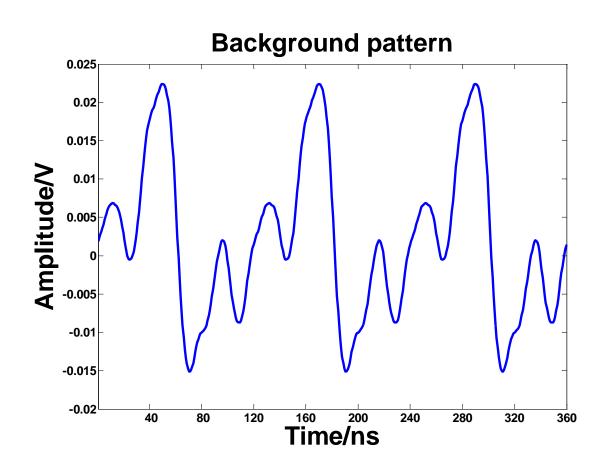

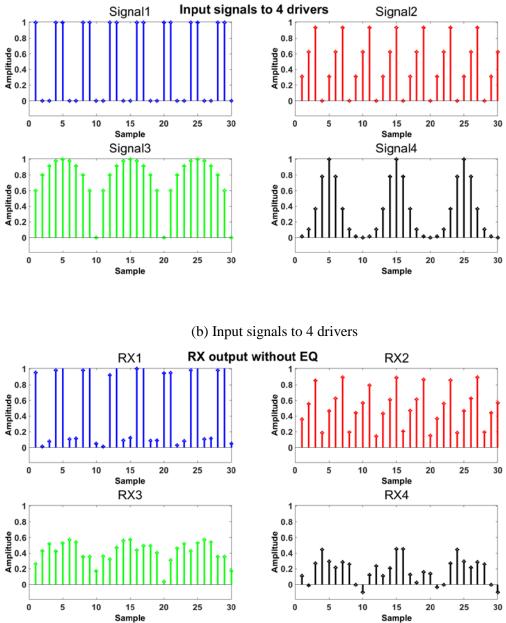

| Figure 6-19 Background pattern                                                  |     |

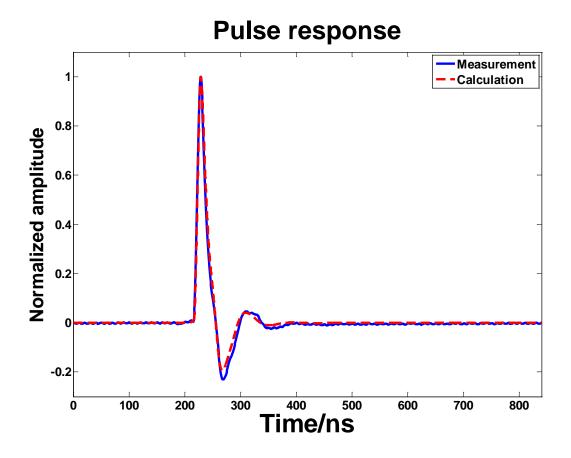

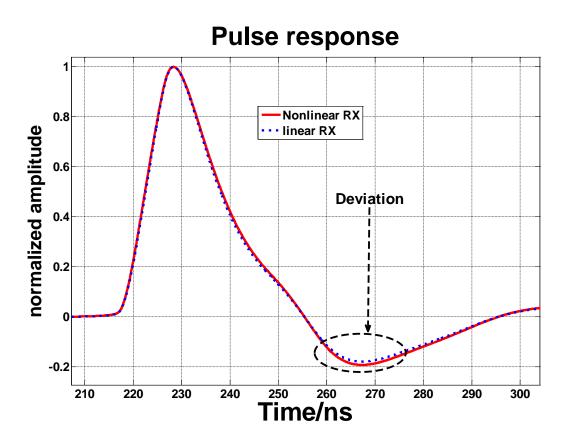

| Figure 6-20 Measured and calculated pulse response                              |     |

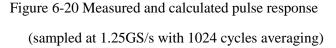

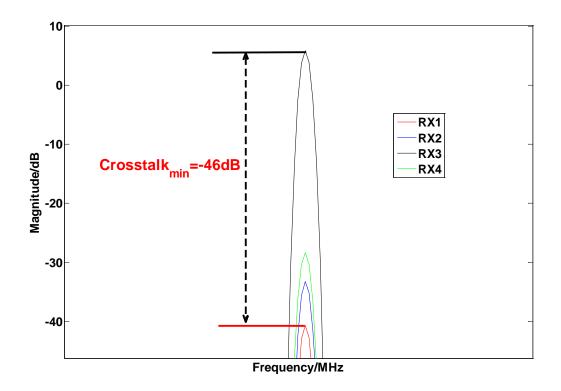

| Figure 6-21 Channel characterization in frequency domain                        |     |

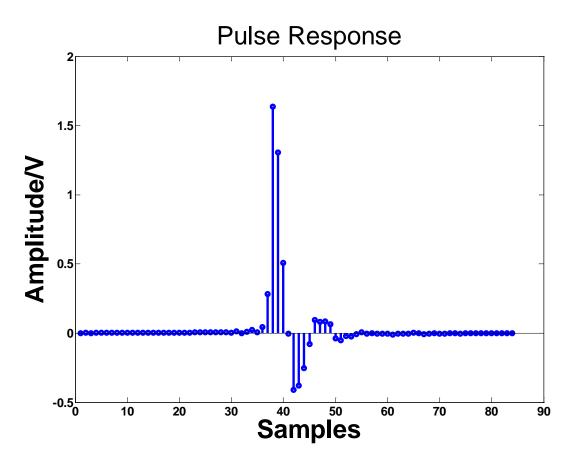

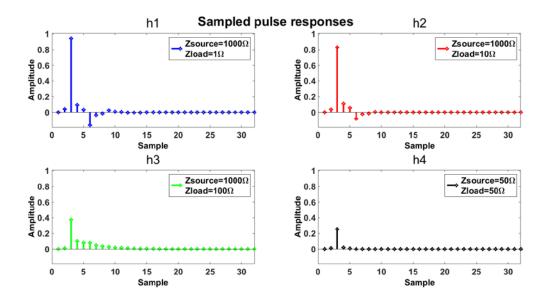

| Figure 6-22 Sampled pulse response                                              |     |

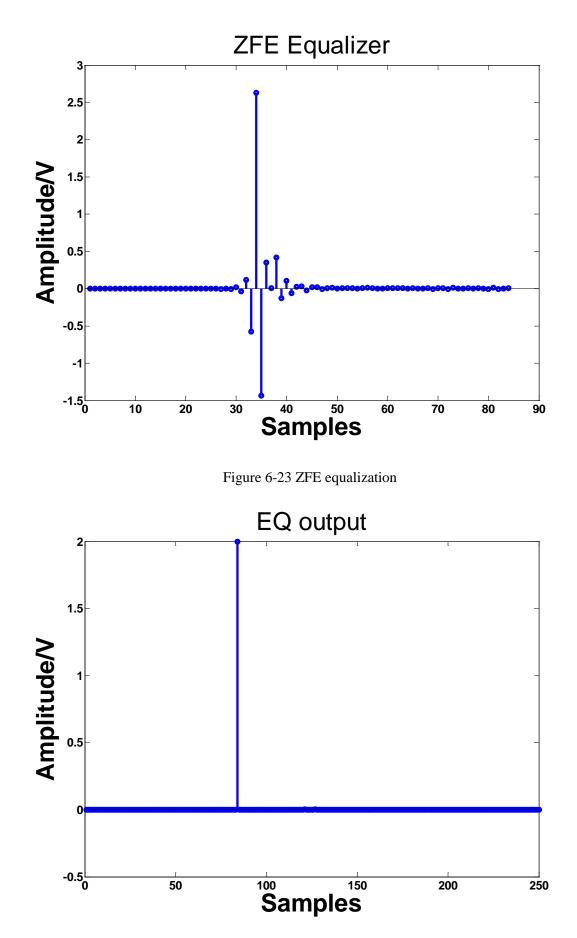

| Figure 6-23 ZFE equalization                                                    |     |

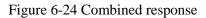

| Figure 6-24 Combined response                                                   |     |

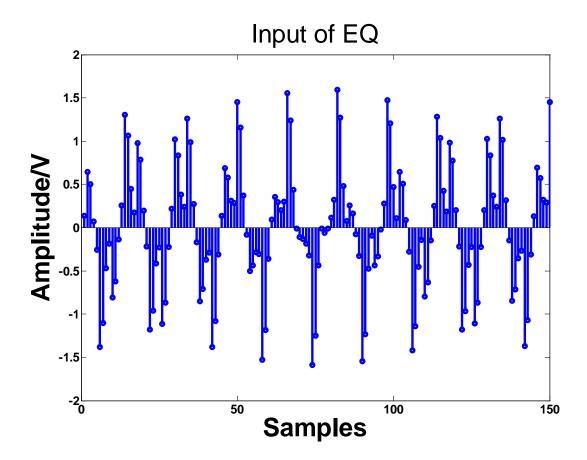

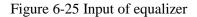

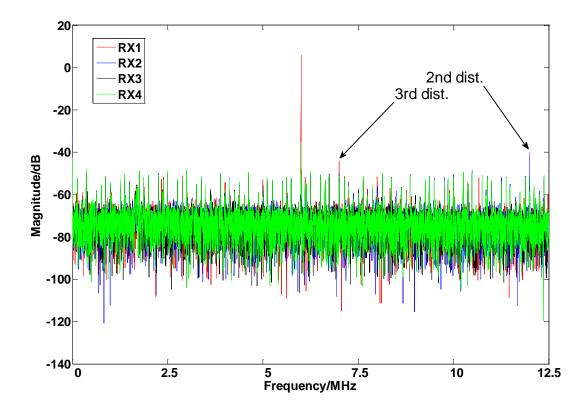

| Figure 6-25 Input of equalizer                                                  |     |

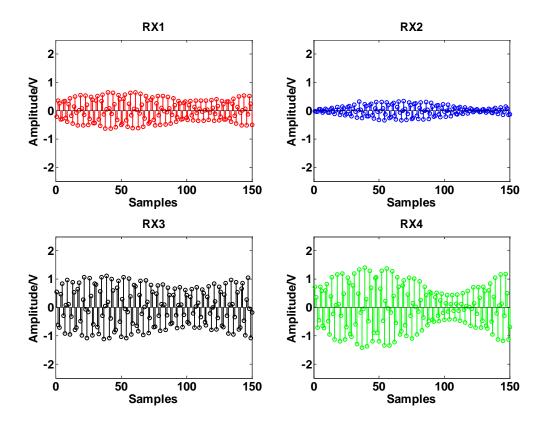

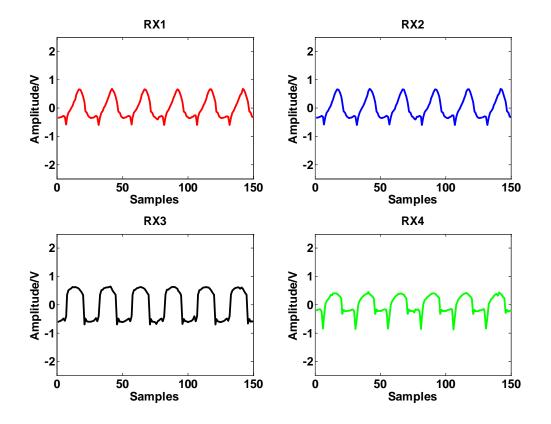

| Figure 6-26 Demultiplexed output without equalization                           |     |

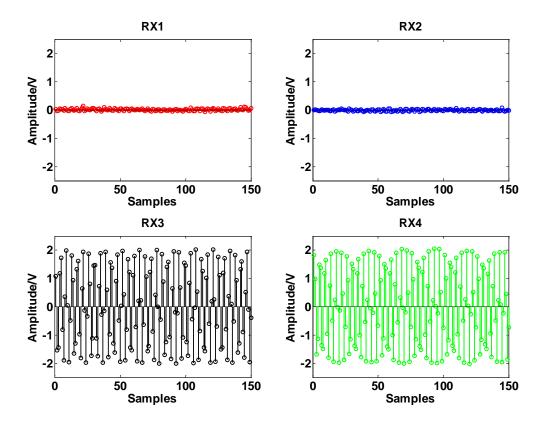

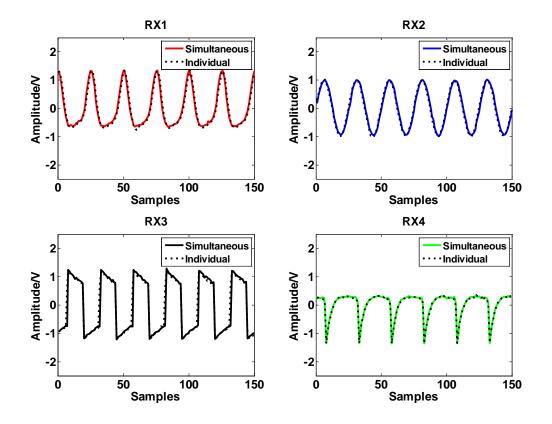

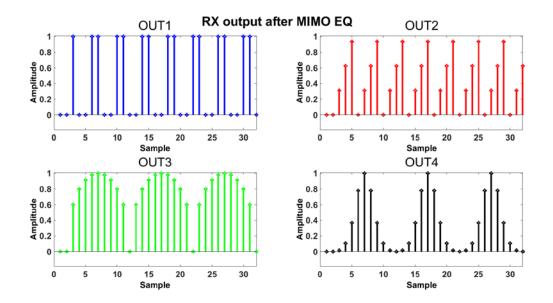

| Figure 6-27 Demultiplexing after equalization                                   |     |

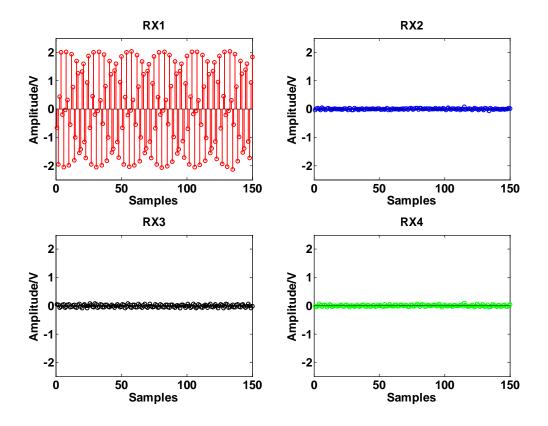

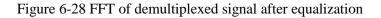

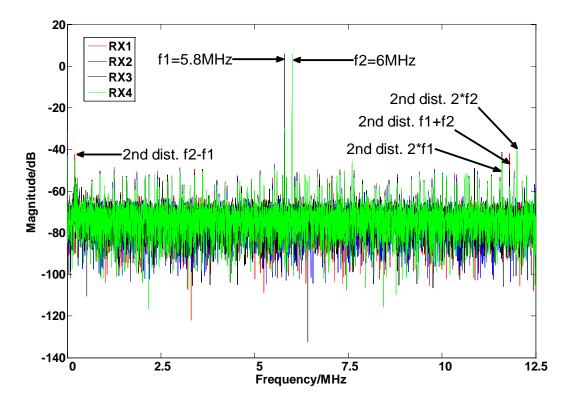

| Figure 6-28 FFT of demultiplexed signal after equalization                      |     |

| Figure 6-29 Zoom-in of Fig. 6-25 showing crosstalk at the signal frequency      |     |

| Figure 6-30 Demultiplexed output without equalization                           |     |

| Figure 6-31 Demultiplexing after equalization                                   |     |

| Figure 6-32 FFT of demultiplexed result after equalization1                     | 01  |

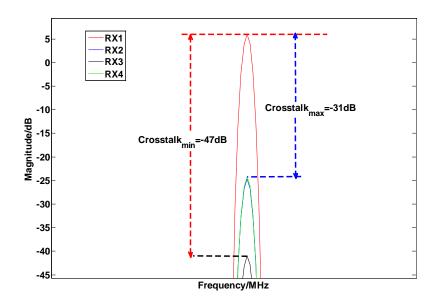

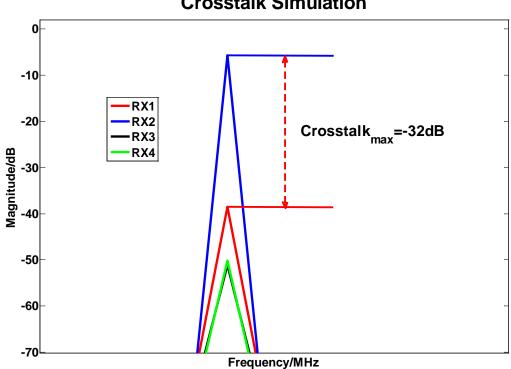

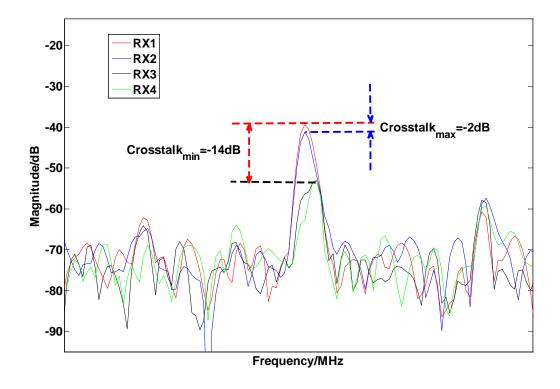

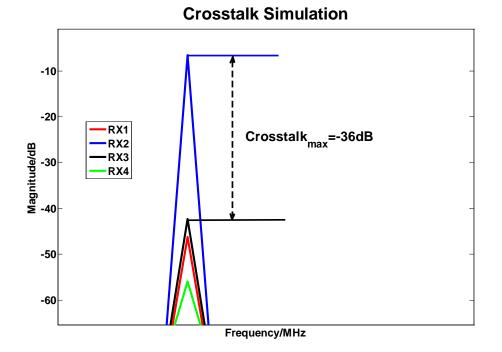

| Figure 6-33 Crosstalk measurement in two-driver test 1                          | 01  |

| Figure 6-34 Demultiplexed output without equalization1                          | 03  |

|                                                                                 | .05 |

# **List of Tables**

| Table 1-1 Signal property of µBF's output                           | 3  |

|---------------------------------------------------------------------|----|

| Table 1-2 Added requirements on the output stage's output           | 3  |

| Table 2-1 Cable specifications                                      | 13 |

| Table 4-1 Configuration details                                     |    |

| Table 4-2 Specifications of all the building blocks in the system   |    |

| Table 5-1 Pin assignments                                           | 68 |

| Table 6-1 Truth table of the mode selection control                 | 74 |

| Table 6-2 Signal property comparison                                |    |

| Table 6-3 SNR measurement                                           |    |

| Table 6-4 RX distortion look-up table                               |    |

| Table 6-5 Distortion measurement                                    |    |

| Table 6-6 Tones in the FFT of each receiver's output                | 97 |

| Table 6-7 SNR before and after equalization                         |    |

| Table 6-8 THD before and after equalization                         |    |

| Table 6-9 Different signals used in all-driver test                 |    |

| Table 6-10 SNR comparison in all-driver test with identical signals |    |

| Table 6-11 THD comparison in all-driver test with identical signals |    |

|                                                                     |    |

# **Chapter 1** Introduction

### 1.1 Background

The advance of modern society sees more need for health care. Among the causes of death, cardiovascular disease has been the number one killer according to a report from the World Health Organization (WHO) in 2013 [1.1]. In order to diagnose and heal it sufficiently, imaging technologies such as magnetic resonance imaging (MRI), positron emission tomography (PET) and echocardiography, have been developed. Among them, echocardiography shows its advantages of being low cost, body friendly and capable of providing good imaging quality. For imaging of the heart, transesophageal echocardiography (TEE) has been developed by using the esophagus as an acoustic imaging window. When applying this imaging technique, patients swallow a small probing tube that is positioned in the esophagus close to the heart, where it transmits ultrasonic pulses and receives the resulting reflections. After having been transmitted back to the mainframe and properly processed, the signals collected by the probe can be converted into an image of a heart. A TEE probe is shown in Fig. 1-1.

Figure 1-1 TEE diagram [1.2]

In the market there are already medical imaging instruments based on 2D or 3D TEE. For 2D imaging, an 1D transducer array is installed in the probe tip and in one imaging process only a cross-sectional image of the heart can be acquired. As such, the simplicity of the imaging process leads to the complexity of dependence on the physicians' experience. In order to address this issue and to provide better imaging quality, 3D TEE imaging probes are being developed.

In a 3D TEE probing system, a 2D transducer matrix is assembled in the probe tip. In the previous work [1.4], a 45\*45 2D TEE rectangular array was proposed, where an analog front end (AFE), as shown in Fig. 1-2 is attached to each transducer element. These AFEs are integrated in a chip that in mounted in the probe tip directly underneath the transducer array. In order to scan the tissue volume of interest, signals reflected arriving at a specific angle are strengthened by the AFE. This is done by delaying the signals arriving at each transducer element in order to emulate a simultaneous receiving from the target point to the whole 2D array. Then the received signals can be summed up in order to enhance SNR. This delay-and-sum technique is referred to as beamforming, which is widely used in a radar systems [1.3].

In the implementation of [1.4], the AFE is composed of a low noise amplifier (LNA), a time-gaincompensation (TGC) amplifier and an analog micro-beamformer ( $\mu$ BF), as shown in Fig. 1.4. After the received signal passes through the transducer for acoustic-electric conversion, it goes through an LNA to maintain the SNR deriving from the transducer in the following stages. Then the TGC compensates for the signal propagation attenuation via amplification with the programmable gains. After that a  $\mu$ BF, which combines signals from a 3\*3 subarray, implements the delay-and-sum function as mentioned above. Here the prefix "micro" means the beamformer here can only handle a partial delay-and-sum function which is applied only to a subarray. The complete beamforming of the whole 2D array it is carried out in the mainframe.

Figure 1-2 Analog front end (AFE) with a transducer element

One benefit that a  $\mu$ BF brings about is the reduction of cable count. Since the 9 transducer elements share one common  $\mu$ BF and generate one output, the overall 45\*45 chip-mainframe interconnections are reduced by 9 times, which results in only 225 cables needed for wiring.

However, the size of the interconnection bundle of 225 cables is still very challenging for an endoscope-based application. So a further output stage that can combine outputs from multiple  $\mu$ BFs is necessary, which forms the main goal of the thesis project. As the first trial, 4  $\mu$ BFs are combined and sent to one output stage so that the total cable count can be less than 60, which more comfortably satisfies the geometry constraint.

Qilong Liu

In order to accomplish this, we should start from the design requirements, which are illustrated in the next section.

## **1.2 Design Considerations**

### **1.2.1** Signal Properties

In order to adapt to the  $\mu$ BF of the previous project [1.4], the proposed output stage should be compatible with the signal properties of the  $\mu$ BF's output, which are listed in Table 1-1.

| Property           | Value               | Description                       |

|--------------------|---------------------|-----------------------------------|

| Signal frequency   | 6 MHz               | Gaussian wave, with 50% bandwidth |

| Signal amplitude   | 200 mV peak-to-peak | sampled-and-held output           |

| Sampling frequency | 25 MHz              | -                                 |

| Dynamic range      | 40 dB               | output of µBF                     |

Table 1-1 Signal property of µBF's output

Besides that, two more requirements are added to clarify the design boundary, as listed in Table 1-2.

Table 1-2 Added requirements on the output stage's output

| Requirements           | Value  | Description                |

|------------------------|--------|----------------------------|

| Distortion (THD)       | -40 dB | Derived from dynamic range |

| Crosstalk (µBF to µBF) | -40 dB | Derived from dynamic range |

Here both the distortion and crosstalk requirements are derived from the dynamic range at the  $\mu BF$ 's output. By doing this the above non-idealities can be of the same level as the noise.

Besides the requirements set by the conveyed signal, the cable as a loading gives another boundary to the design of output stage.

### **1.2.2 Cable Property**

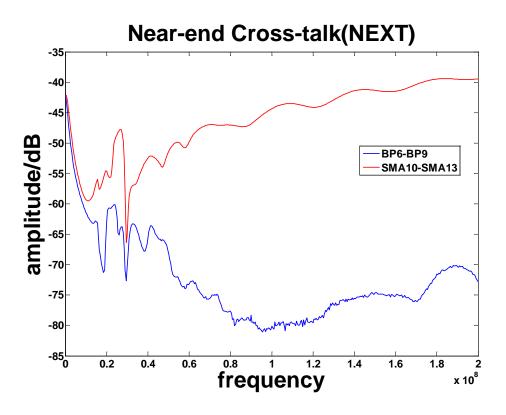

In order to carry the signal produced by the chip at the tip of the endoscopic probe to the mainframe, 3-meter-long micro-coaxial cables manufactured by SUMITOMO [1.5] are used. Being different from on-chip capacitive loading, the long cable exhibits a complicated impedance to the output stage. The accompanied noise, transmission line effects, crosstalk and the finite bandwidth together set new

requirements for the output stage and furthermore for the whole system. In Chapter 2 the details of the cable characterization is given.

#### **1.2.3** Power and Area Restrictions

Since the TEE probe is of endoscopic type, power and chip area are the critical limitations that should be designed with much emphasis. As a rough restriction, the power and the area of the proposed output stage should not exceed those consumed by the  $\mu$ BFs which share it. Based on the implementation in [1.4], one output driver should consume less than 9mW and occupy less than 2mm<sup>2</sup>, when the technology migration from 0.35  $\mu$ m to 0.18  $\mu$ m is taken into account.

### **1.3** Solutions

### **1.3.1** Possibilities and Limitations

In order to realize the challenges of the thesis project, first, the possible solutions and existing limitations are briefly discussed.

For the signal form to be transmitted, given the aforementioned required signal quality, it may seem more reasonable to convert the signals into digital domain for its robustness against distortion, noise and interference. However, analog to digital conversion using conventional design approaches would likely lead to a significant increase in complexity and power consumption. While with appropriate improvements in ADC design a digital solution might become realistic, it is considered outside the scope of this project. Here, instead, we will investigate the option of transmitting multiple analog signal through a single cable.

Nevertheless, there are also some techniques that we can leverage from digital wireline communication. In order to transmits signal from several  $\mu$ BFs via a shared cable, multiplexing schemes—such as time-division multiplexing (TDM) and frequency-division multiplexing (FDM), and code-division multiplexing (CDM), could be used in order to reduce the cable count.

Last but not least, power and area budgets assigned to the output stage lay the ultimate obstacle of the multiplexing and transmission system.

### **1.3.2** Introduction to the Thesis Work

In the thesis work, to tackle with the aforementioned challenges, an analog time-multiplexing system is proposed and implemented, as shown in Fig. 1-3.

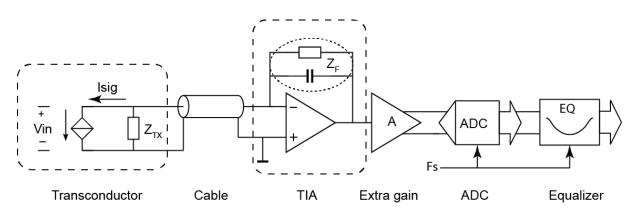

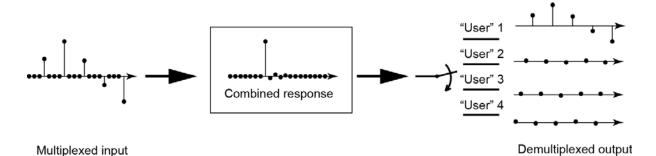

The whole system consists an low-power current-mode multiplexer as the output stage to transmit signals from multiple  $\mu$ BFs into one coaxial cable. At the other end of the cable, a transimpedance amplifier (TIA) followed by an extra gain stage (EA) is designed to boost the signal to a level suitable for digitization. And then an equalization algorithm takes over the digitized signals in order to repair the non-ideal effects from the cable and to resolve signals from different  $\mu$ BFs. In the end signals are de-multiplexed to their corresponding channels, and signal transmission ends.

To make terminology clear and consistent in the thesis (see labels in Fig. 1-3), term "driver" is used to refer to the individual driving unit with input sampling circuit, which is connected with an  $\mu$ BF (including 3\*3 LNAs and TGCs). "Transmitter" (TX) refers to the combination of four drivers and the current-mode multiplexer. "Channel" refers to the transmission media, which is the cable in our case. Sometimes it also refers to the whole signal chain from TX to RX when it does not cause ambiguity in the context. "Receiver" (RX) is used to specify the unit composed of the TIA and the EA in the other end of the cable. *fs* indicates the sampling clock for each  $\mu$ BF, which is 25 MHz in the project. "User" refers to the equalized and demultiplexed result corresponding to separate  $\mu$ BF.

Figure 1-3 Building blocks of the thesis project

### 1.4 Summary

In this chapter the background of the thesis work has been introduced. With an emphasis on the cable characteristics and the power/area budget, the basic design considerations are explained. In the last part, an overview of the thesis work has been given. In the following chapters, Chapter 2 is dedicated to the comparison of multiplexing schemes and the exhibition of transmission line effect after cable characterization. Chapter 3 mainly deals with equalization algorithms which are proposed to cancel

CONFIDENTIAL

the non-idealities associated with transmission line effect. A system-level design and optimization are given is Chapter 4, where the specifications of all the building blocks are determined and optimized in SNR and residual crosstalk points of view. In Chapter 5 the transistor-level TX design is given. Measurement results are given in Chapter 6, with a discussion about the discrepancies between modelling and measurement. In the last chapter of the thesis a summary of the project work is provided, including both contributions and potential improvements.

# **1.5 References**

[1.1] "Cardiovascular diseases." http://www.who.int/mediacentre/factsheets/fs317/en/, January 2015.

[1.2] "Transesophageal echo." <u>http://www.umanitoba.ca/medicine/units/cardiac\_sciences/teeinfo.htm</u>, January 2015.

[1.3] "Beamforming." http://en.wikipedia.org/wiki/Beamforming, February 2015.

[1.4] Z. Yu, *Low-Power Receive-Electronics for a Miniature 3D Ultrasound Probe*, Ph.D. Thesis, Delft University of Technology, Delft, the Netherlands, 2012.

[1.5] Micro flex coaxial cable (MFCX) datasheet: http://www.sei.co.jp/ewp/J/products/detail/pdf/6\_02.pdf

# **Chapter 2** Multiplexing and Cable Modelling

In this chapter, the question of how to squeeze signals from multiple micro-beamformers ( $\mu$ BF) into one cable will be answered. First, several multiplexing schemes are proposed and after comparison time-multiplexing is selected. Next, the cable characterization and modelling are carried out in order to well fit time-multiplexing into the project. During this process we find a distributed model of the cable – transmission-line modelling is inevitable to be used in the frequency of interest. In the last part of this chapter, the non-idealities of the cable are pointed out and explained in detail, as a preparation for the system solution proposed in the following chapters.

### 2.1 Comparison between Multiplexing Schemes

As mentioned in Chapter 1, cable count reduction is the main target of the project. As the first trial, the output signals from 4  $\mu$ BFs are designed to be transmitted via a shared cable in order to achieve the required reduction in cable count. To achieve this, a multiplexing scheme becomes necessary to be implemented with focus on minimizing the power consumption on the probe side of the cable. In the following discussion, several common schemes, such as frequency-division multiplexing (FDM), code-division multiplexing (CDM) and time-division multiplexing (TDM) are analysed.

### FDM

In FDM, signals from each  $\mu$ BF are modulated by a sinusoidal carrier into a separate frequency range [2.1][2.2]. In order to fit FDM into the frame of our application, the sinusoidal carrier should be modified by simpler implementation. Here, square-wave signals with different fundamentals are used as carriers, as shown in Fig. 2-1, enabling implementation using simple chopper switches. Furthermore, I/Q modulation can be also used to improve the frequency band utilization. On the receiver side, coherent demodulation can be applied as a replacement of sinusoidal demodulation and low-pass filtering.

### CDM

In CDM, signals from different drivers are coded by different series of pseudo random numbers [2.1][2.3]. Due to the orthogonality of those random series, at the receiver side signals from one driver will only be recognized by its corresponding receiver via the unique decoding series.

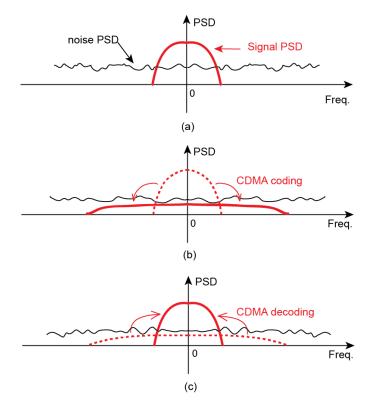

In the frequency domain, CDM is a spread-spectrum technique. It means that during transmission, signal power spectrum density (PSD) is wide spread and even hidden below the noise floor of the

physical channel, which is illustrated in Fig. 2-2. After being reconstructed at the corresponding receivers, the noise and interference during transmission are randomized and can be filtered out.

### TDM

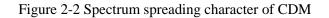

In TDM, or equivalently time-multiplexing, signals share one physical channel by time-interleaving [2.1][2.4]. In one multiplexing cycle, fs, the whole period is uniformly divided into several slots, and signals from drivers are assigned into the slots sequentially. The TDM control are plotted in Fig. 2-3, where "1" means the corresponding drivers are activated and "0" means being idle.

Figure 2-1 Square-wave modulation carriers for different drivers in the modified FDM scheme

(a) PSD at TX (b) PSD after CDM coding

(c) PSD after decoding at RX

As a summary, a comparison is made between different multiplexing schemes, which is tabulated in Tab. 2-1.

| Schemes | Implementation           | Characteristics                                              |  |

|---------|--------------------------|--------------------------------------------------------------|--|

| FDM     | Chopper, clocks with     | 1. All the drivers are on all the time, but their bandwidths |  |

|         | multiple frequencies and | can be lower than those in TDM for looser settling           |  |

|         | I/Q phases               | requirements.                                                |  |

|         |                          | 2. Different modulation frequencies indicate the             |  |

|         |                          | complexity of digital control, along with topology           |  |

|         |                          | asymmetry among the drivers.                                 |  |

|         |                          | 3. Phase misalignment between I/Q paths will cause           |  |

|         |                          | spectrum leakage to other signal bands.                      |  |

| CDM     | Chopper, random-         | 1. Drivers are on all the time.                              |  |

|         | number-generator, timing | 2. Orthogonal coding requires extra coder at TX side,        |  |

|         | control on both RX and   | which increase the complexity of TX design.                  |  |

|         | TX                       | 3. Better interference immunity during transmission          |  |

|         |                          | compared to FDM and CDM.                                     |  |

| TDM     | Multiplexing control,    | 1. Drivers can be off when they are idle.                    |  |

|         | clock with identical     |                                                              |  |

|         | frequency and multiple   | 3. Lighter design burden due to the uniform settling         |  |

|         | phases                   | requirement for all the drivers compared to FDM.             |  |

Table 2-1 Comparison between different multiplexing schemes

From the comparison in Tab. 2-1, we find TDM shows its advantage over the other two by simpler implementation in both digital control and driver design. More specifically, when the number of  $\mu$ BFs shared by one cable increases, the asymmetry between the different drivers and their controls becomes more obvious in the case of FDM, which lays heavier burden on the multiplexer design. Accordingly TDM, is chosen as the multiplexing scheme for the target of cable count reduction in our application. Next we start to analyse the spectral characteristics of time-multiplexed signals.

# 2.2 Spectral Characteristics of Time-multiplexing

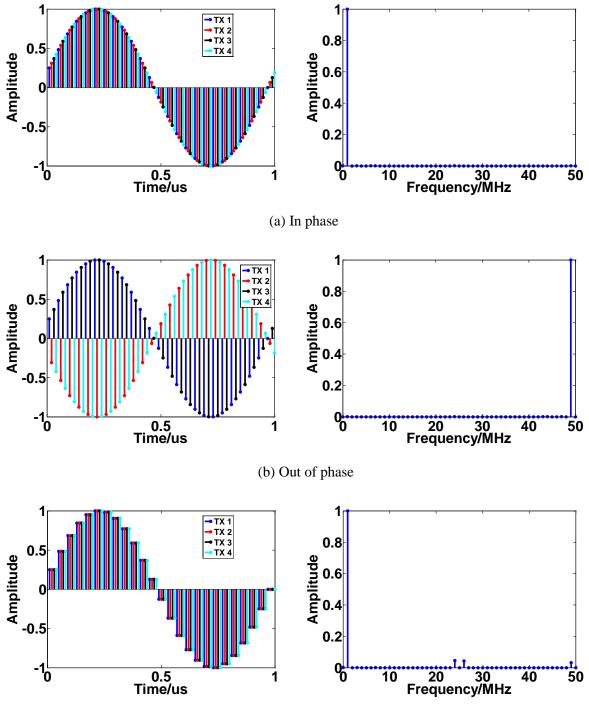

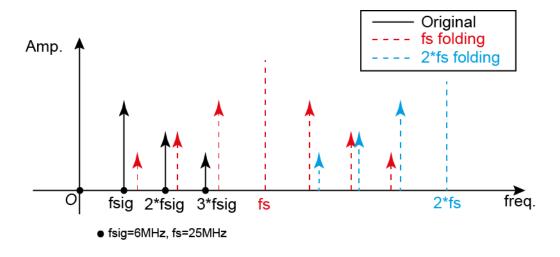

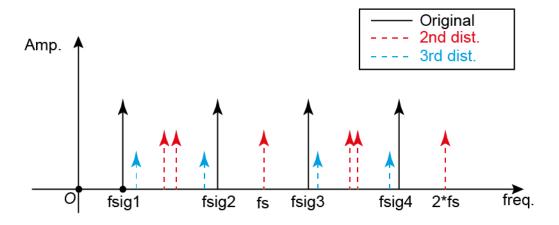

Even though time-multiplexing show its advantage from the implementation point of view, it does not provide better spectrum utilization than its competitors. To explain this, an example of TDM in both time and frequency domain is given in this section. In Fig 2-4 four 1 MHz signals with different phases are sampled at 25 MS/s and are then time-multiplexed. The FFTs of the resulting output signals are also shown in Figure 2-4.

(c) "Staircase"

(d) Random phase

Figure 2-4 Time and frequency domain of multiplexed signals

From Fig. 2-4 it can be found that:

- The global sampling frequency observed from the multiplexed signal is N times larger than the individual sampling frequency, where N is the number of drivers which share the cable.

- The spectrum of multiplexed signals are in the form of several tones within the Nyquist interval, and each tone contains partial information from all the drivers. It indicates that signal from an individual driver cannot be filtered out by a single band-pass filter.

- The amplitudes of the tones are associated with the relative phase shifts between the signals. However, later it will be shown that the whole signal chain (from TX to RX) shows a nonuniform frequency response in the Nyquist interval, which makes the SNR at the output of RX hard to be estimated. This will be shown in Chapter 6.

As explained above, the signal spectrum after multiplexing is expanded as compared to the case in an individual driver. This makes the cable's high-frequency behaviour critical to the system design. Allowing for this, in the next section, cable modelling will be given in detail.

# 2.3 Cable Modelling

## 2.3.1 Cable Characterization

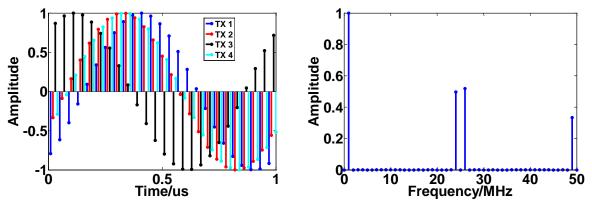

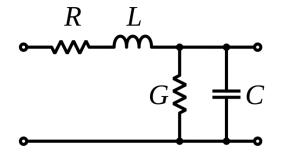

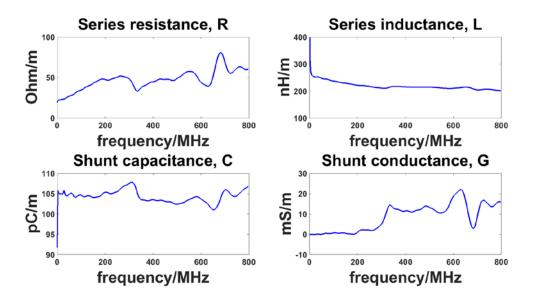

In order to efficiently apply the time-multiplexing in the project, the cable should be characterized to clarify its high-frequency behaviour. Normally, a cable is described using four basic electrical parameters: shunt conductance (G), shunt capacitance (C), series resistance (R) and series inductance (L), all of which are specified by unit length [2.5]. Fig. 2-5 gives a lumped model of a unity-length cable with these parameters. From the cable specifications provided by Oldelft [2.6], the values of R, L, C, G are tabulated in Tab. 2-2. They can be also be obtained by S-parameter measurement via a

12

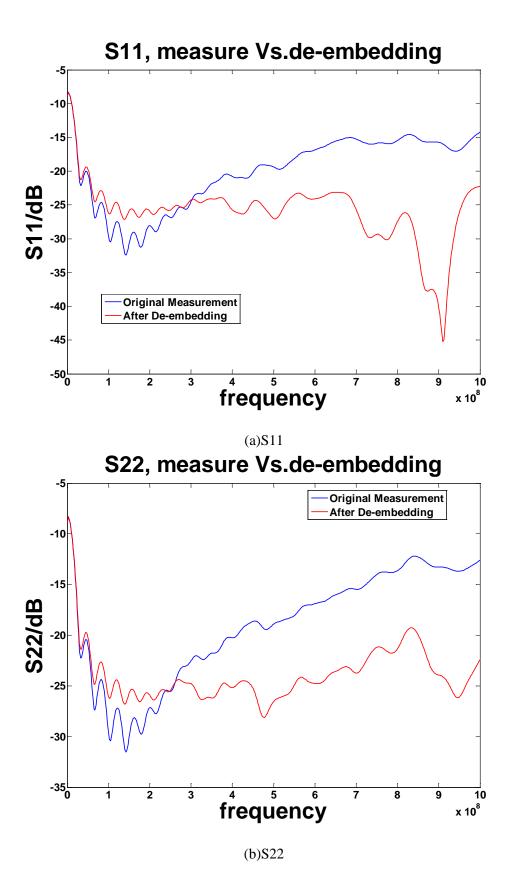

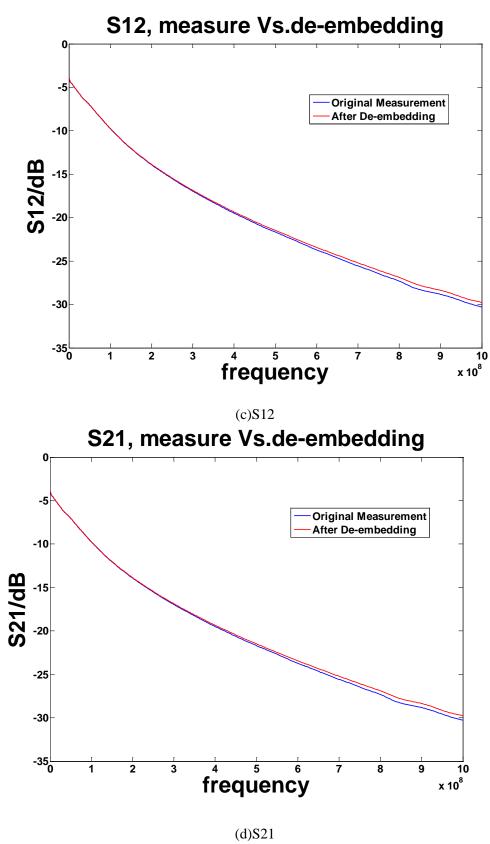

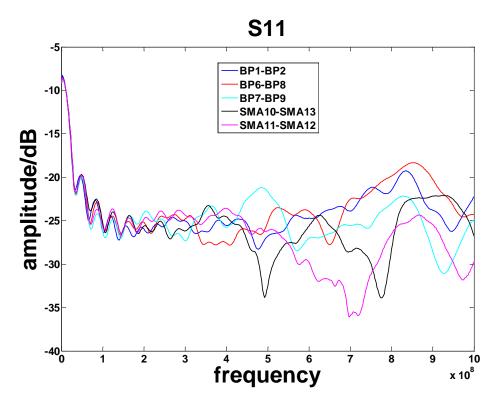

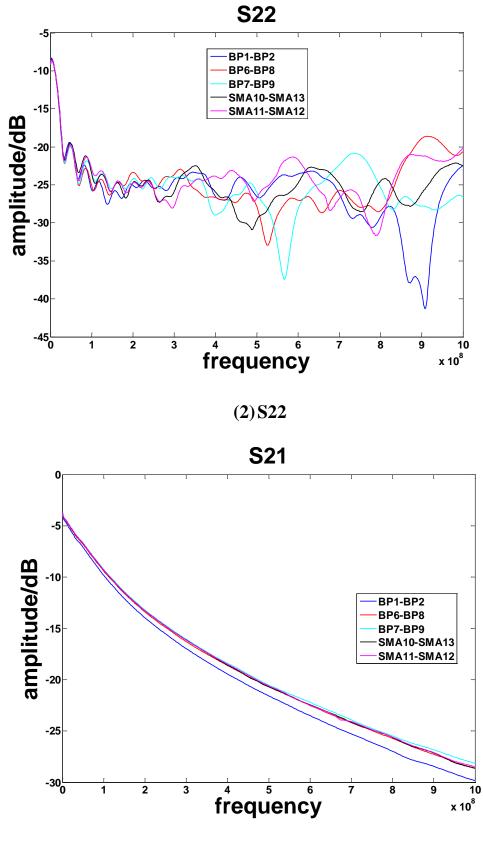

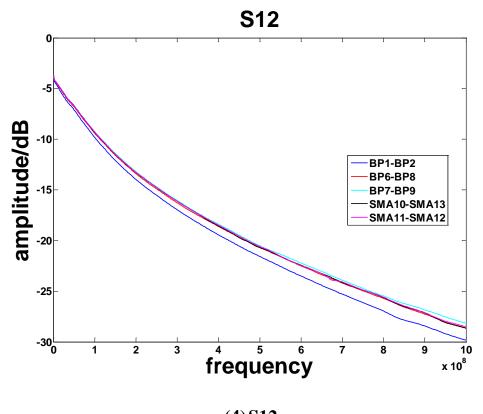

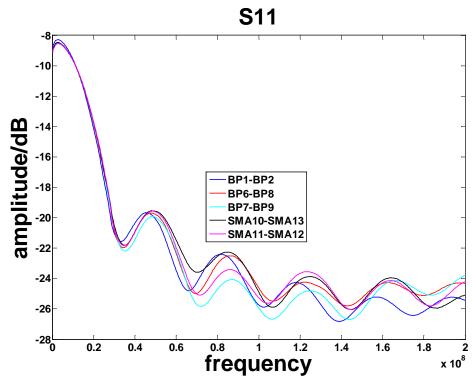

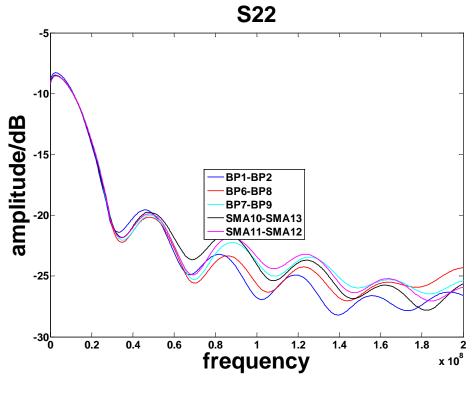

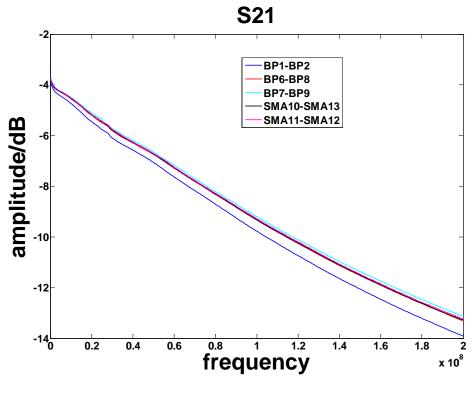

vector network analyzer (VNA) [2.7][2.8], of which the result is shown Fig. 2-6. As for the details of VNA measurement please refer to Appendix A.

| Parameter                      | Value         | Unit       |

|--------------------------------|---------------|------------|

| Series resistance ( <i>R</i> ) | Max. 22       | $\Omega/m$ |

| Shunt resistance $(G^{-1})$    | Min. 1524     | MΩ/km      |

| Shunt capacitance ( <i>C</i> ) | 120±10 (1KHz) | pF/m       |

| Series inductance ( <i>L</i> ) | 300 (10MHz)   | nH/m       |

Table 2-1 Cable specifications  $[2.6]^1$

Figure 2-5 Lumped model of a unity-length micro-coaxial cable<sup>2</sup>

Figure 2-6 Extracted R, L, C, G from VNA measurement

<sup>&</sup>lt;sup>1</sup> Here the shunt resistance is the value given in the specifications without any converting.

<sup>&</sup>lt;sup>2</sup> Here the series resistance (*R*) and the series inductance (*L*) includes the contribution from both the core and the shield.

Fig. 2-6 shows a good agreement in *L* and *C* between the cable specifications and measurement, while *R* and *G* exhibit frequency-dependent effect. The frequency-dependent *R* it is due to the skin-effect [2.5], and frequency-dependent *G* is caused by dielectric relaxation  $[2.9]^3$ .

In order to accurately model the cable with the above parameters, one thing that should be examined is the necessity to use a transmission line model in the thesis project. To verify this, we first check whether L or C is notable in the frequency of interest. By calculation we can get the critical frequency above which L becomes dominant to R:

$$f_{L,dom} = \frac{l \cdot R}{2\pi (l \cdot L)} = 10.6MHz \qquad (2-1)$$

where l is the cable length. And the critical frequency of C is

$$f_{C,dom} = \frac{1}{2\pi (l \cdot R)(l \cdot L)} = 6.7MHz$$

(2 - 2)

Since  $f_{L,dom}$  and  $f_{C,dom}$  are within the signal band (6MHz~44MHz), both *L* and *C* are indispensable in the cable model. Next we will check if the cable is a distributed model in the signal band. As a rule of thumb in radio-frequency IC design [2.10], a cable or trace is modelled as a distributed model when its physical length is shorter than 1/10 of the wavelength of signal-carrying electromagnetic (EM) wave. Judging from the calculated wavelength shown in Fig. 2-7, it suffices to claim that a distributed model, namely transmission line effect should be taken into account in the signal frequency of interest. From the next section we will elaborate it in our application.

Figure 2-7 Wavelength of EM wave in the micro-coaxial cable

<sup>&</sup>lt;sup>3</sup> For convenience in the following time domain simulation the parameters are interpolated linearly within the frequency of our interest (DC-200MHz) instead of using the extracted ones.

### 2.3.2 Transmission Line Effect of a Micro-Coaxial Cable

### **Pulse Response of Transmission Line**

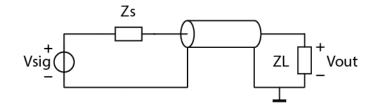

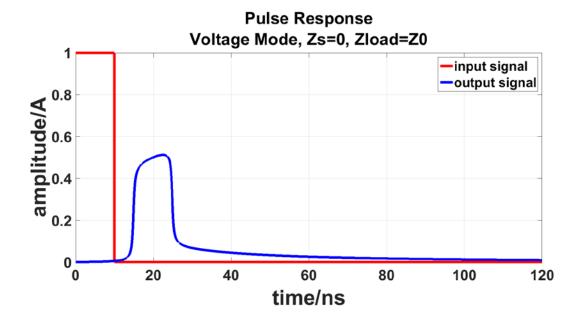

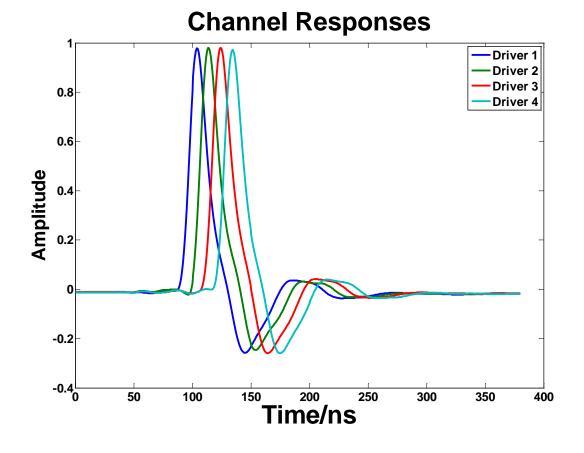

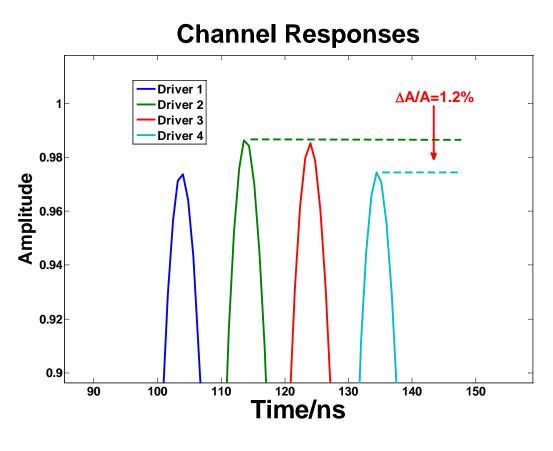

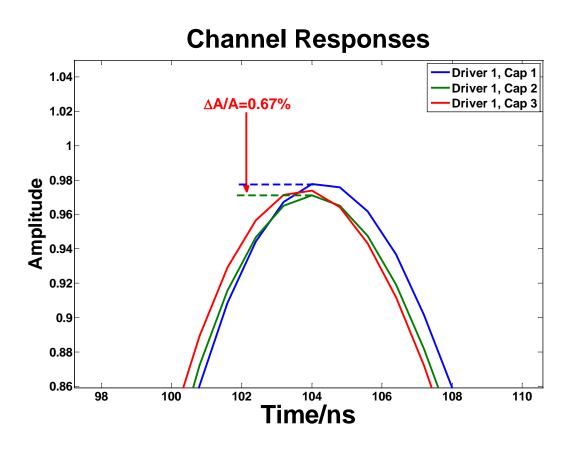

Due to the sampled-and-held nature of the input signal, the time-multiplexed signals on the cable will have the form of amplitude-modulated pulses. So it is important to interpret the cable's pulse response in the context of transmission line effects.<sup>4</sup> In the simulation configuration shown in Fig. 2-7, a pulse mode voltage source with certain output impedance  $Z_S$  is connected to the cable, and at the other end a load impedance  $Z_L$  is used to sense the output voltage. To make the simulation close to the real application, the pulse duration is chosen equal to the time slot used for single driver transmission (10ns). Fig. 2-8 gives the simulation result of the pulse response in the single-ended matching case, where the cable is loaded by its characteristic impedance. From Fig. 2-8 several key phenomena are observed, which will be explained in detail as follows.

Figure 2-8 Configuration of voltage mode transmission

Figure 2-9 Pulse response in a single-ended matching voltage mode transmission

<sup>&</sup>lt;sup>4</sup> In the following simulations the electrical parameters are interpolated from the measurement data. As for the details of time domain simulation, please refer to [2.11].

#### Attenuation

From Fig. 2-9 it can be observed that the peak of the output signal is around a half of the input, which shows obvious attenuation. This is due to the cable's intrinsic loss which dissipates the signal amplitude during propagation. As a result such an inevitable effect will lead to reduced output amplitude compared to that at the input port, which also gives the difficultly of SNR estimation at RX side. However, the cable-induced attenuation can be compensated by choosing an unmatched load which boosts the received amplitude via reflection. But extra penalty will paid as well, which will be explained later.

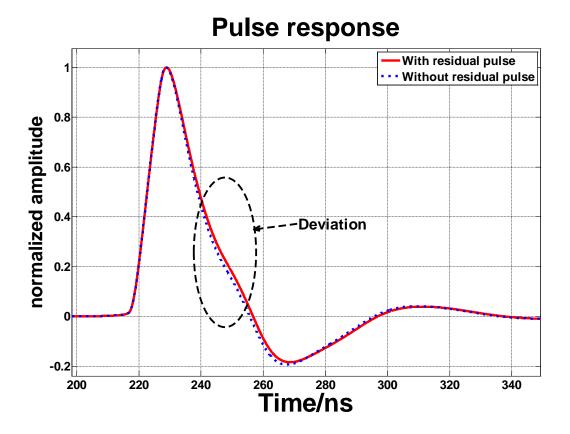

### Dispersion

Dispersion in a lossy transmission line can also be observed in Fig. 2-8. Compared with attenuation, dispersion is more serious because it can cause obvious crosstalk between signals from different drivers during multiplexing.

Essentially speaking, dispersion is due to the non-uniform propagation velocity across frequency which distorts the shape of the signals. As shown in Fig. 2-10, low frequency components propagate slower than those with high frequencies. Since a pulse spans a wide frequency range, the velocity difference appears in the form of a sharp rising edge for the high frequency components, and a long tail for the low frequency parts.

Figure 2-10 Propagation velocity Vs. frequency

#### Reflection

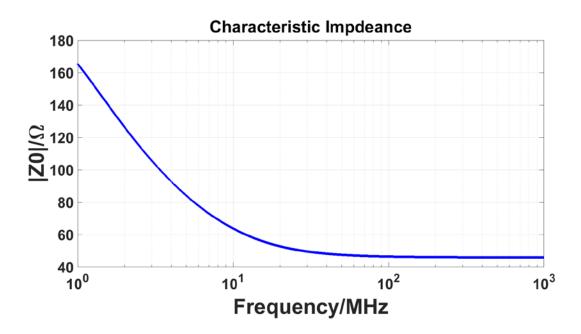

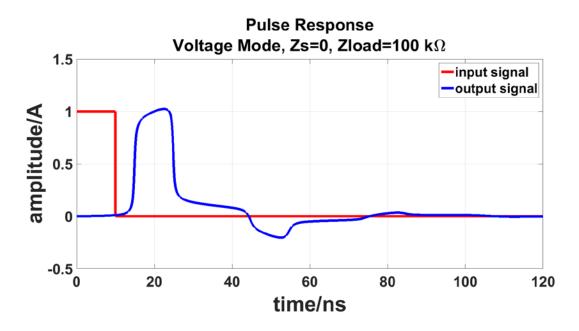

If  $Z_S$  or  $Z_L$  is not well matched with the characteristic impedance (plotted in Fig. 2-11), reflection will occur at the source or the load, which can change the received voltage amplitude and generate multiple reflections spaced by certain propagation delays. In the simulation result shown in Fig. 2-12, a loading condition of  $Z_S=0 \Omega$ ,  $Z_L=100 \text{ k}\Omega$  is chosen to illustrate such an issue. It can be observed in Fig. 2-12, that at the output there is a pulse with negative polarity arriving 30 ns later than the first received pulse. It is due to reflection caused be the unmatched terminations at both ends of the cable.

Figure 2-11 Characteristic impedance of the micro-coaxial cable

Figure 2-12 Pulse response of a double-ended unmatched transmission line

As mentioned in the above discussion, an unmatched loading can actually help to compensate the propagation attenuation, which can be observed by the comparison between Fig. 2-9 and Fig. 2-12. But the companied reflections present extra difficulty of cancelling the crosstalk between the multiplexed signals.

Allowing for the aforementioned phenomena presented by using pulse response, the conventional matching condition used in digital wireline system design might be abandoned [2.12][2.13]. From the comparison between Fig. 2-9 and Fig. 2-12 it can be found that in time domain the reflections are located in the long tail caused by the dispersion, which means from the crosstalk point of view, the loss of the cable might be the main concern compared with an unmatched termination. From the SNR point of view, an unmatched load can actually help to boost the received signal without any active components. Last but not least, the implementation will be more straightforward if we give up to realize an varying impedance across the signal frequency range (after multiplexing) in order to match the cable's characteristic impedance. In Chapter 4 a quantitative analysis of the above insight will be carried out.

### Noise Performance of the Micro-Coaxial Cable

Besides the transmission line effects shown in the time-domain simulation, the cable's distributed character also affects its noise performance. To illustrate this, we first introduce the concept of a 2-port network [2.5][2.14]. A 2-port network is composed of 4 terminals which forms two pairs. Each terminal pair is called as a port if the following condition is satisfied: the current entering one terminal should equal that coming out of the other one. From the above definition we identify that a cable is a 2-port network, since the above condition is automatically satisfied due to Kirchhoff's law.

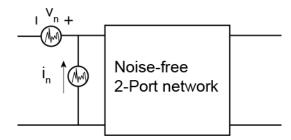

Noise in a 2-port network can be modelled using two equivalent noise sources: noise voltage  $v_n$  and noise current  $i_n$ , as labelled in Fig. 2-13.

Figure 2-13 Noise parameters in the 2-port network

Normally there is partial correlation between  $v_n$  and  $i_n$ . In time domain their correlation can be expressed as

$$i_n(t) = Y_{cor}(t) \cdot v_n(t) + i_u(t)$$

(2-3)

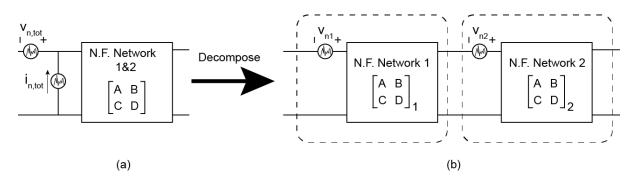

where  $i_n$  is the input-referred noise current and  $v_n$  is the input-referred noise voltage as labelled in Fig. 2-13.  $Y_{cor}$  denotes the correlation coefficient between  $i_n$  and  $v_n$ .  $i_u$  stands for the uncorrelated noise current, which is due to the different transfer functions that an independent voltage source in the network experiences when it is referred back to the input port. To illustrate this we decompose a 2-port network into two separate parts, in either of which there is only an independent voltage source, as shown in Fig. 2-14.

Figure 2-14 Decomposition of a 2-port network based on the noise source separation

By using  $v_{n1}$  and  $v_{n2}$ ,  $v_{n,tot}$  and  $i_{n,tot}$  can be expressed as follows,

$$v_{n,tot} = A_1 \cdot v_{n2} + v_{n1} \tag{2-4a}$$

$$i_{n,tot} = C_1 \cdot v_{n2} = \frac{C_1}{A_1} \cdot v_{n,tot} - \frac{C_1}{A_1} \cdot v_{n1}$$

(2-4b)

where  $A_1$ ,  $C_1$  are the hybrid parameters of Network 1, as labelled in Fig. 2-14(b). If we take  $v_{n,tot}$  and  $v_{n1}$  as two independent noise sources, then  $i_{n,tot}$  is found to be composed of two parts contributed by  $v_{n,tot}$  and  $v_{n1}$ , where the latter gives an uncorrelated noise current besides that from  $v_{n,tot}$ :

$$i_{n,tot} = \frac{C_1}{A_1} \cdot v_{n,tot} + i_{u,tot} \tag{2-5}$$

where

$$i_{u,tot} = -\frac{C_1}{A_1} \cdot v_{n1} \tag{2-6}$$

20

Now it has been found that an uncorrelated noise current does exist due to the different transfer functions of the independent noise sources.

In frequency domain, the power spectrum densities (PSD) of  $i_n$ ,  $v_n$  and  $i_u$  of a 2-port network can be expressed in the form of the noise equivalent transconductance and resistance expressed as follows,

$$S(i_n) = 4kT \cdot G_n \tag{2-7a}$$

$$S(v_n) = 4kT \cdot R_n \tag{2-7b}$$

$$S(i_u) = 4kT \cdot G_u \tag{2-7c}$$

where  $G_n$ ,  $R_n$  and  $G_u$  are the fictitious terms only used to specify the noise performance. For the cable used in the project,  $G_n$ ,  $R_n$  and  $G_u$  can be easily calculated based on the extracted electrical parameters shown in Fig. 2-6 [2.15]. In [2.15], the relation between them is also given,

$$G_n = |Y_{cor}|^2 \cdot R_n + G_u \tag{2-8}$$

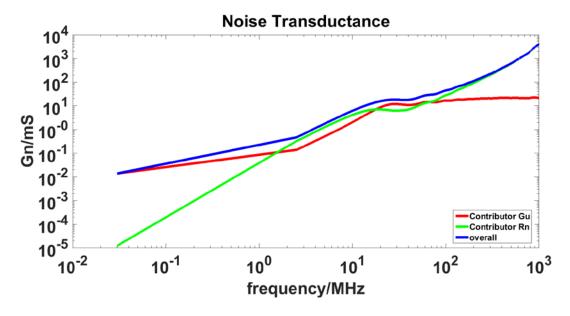

By expression (2 - 8) we can separately calculate the noise contributions in  $G_n$  due to  $R_n$  and  $G_u$ , which are plotted in Fig. 2-15.

Figure 2-15 Noise contributors in  $G_n$

From Fig. 2-15 we find:

1) Fig. 2-15 shows that  $G_n$  increases with frequency. To explained this, we can chop the cable into several identical segments, with each of them treated as lumped 2-port model at the specific frequency. For simplicity it is further assumed that in each segment noise only comes from the series

CONFIDENTIAL

resistance, R. Then we can refer the noise voltage in each segment back to the input port via different hybrid parameters as shown in Fig. 2-14. However, when frequency increases those parameters exhibit higher attenuation. As a result, the input-referred noise generally becomes larger.

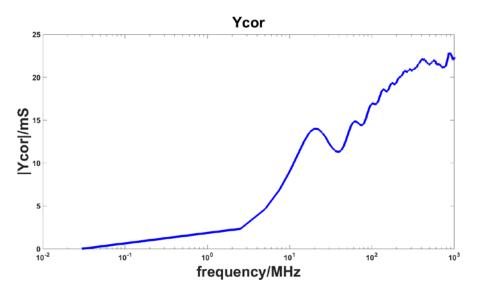

2) Among the two contributors of  $G_n$  shown in Fig. 2-15, it can be found that at low frequencies (DC-1MHz), the independent current noise,  $G_u$ , dominates the overall noise performance, and that at high frequencies (1MHz to 1GHz), the correlated voltage noise,  $R_n$ , plays an more important role. This behaviour can be also explained in a similar way as above. At low-frequencies, for a single noise voltage source in the aforementioned segment, the conversion ratio between the input-referred voltage and current differs obviously along the whole cable. However, at high-frequencies, the high attenuation of cable makes the aforementioned conversion ratio differs little among the segments at far end. And besides, the higher the frequency goes, the larger the number of those segments take up the cable. Allowing for this, the correlated noise originating from  $R_n$  starts to dominate the noise contribution over  $R_n$ . The insight can be verified by the calculated  $Y_{cor}$  shown in Fig. 2-16, where  $Y_{cor}$  shows increasing tendency as frequency goes up.

Figure 2-16 Correlation coefficient, Y<sub>cor</sub>, obtained from VNA measurement

3) When frequency goes higher than 50MHz, the contribution of  $R_n$  continues to increase. This is due to the skin-effect of the cable, which leads the series resistance R (and the resulted loss) to grow with frequency.

In this section it is found that the distributed model of the micro-coaxial indeed brings out the problems when time-multiplexing is chosen as the multiplexing scheme. To tackle with those problems, equalization, for time domain non-idealities, and a dedicated SNR model, for the complicated noise performance, are proposed and discussed in detail in the following two chapters.

### 2.4 Summary

In this chapter we have first investigated several multiplexing schemes in order to investigate their feasibility in our application. After a comparison, time-multiplexing has been chosen for its implementation simplicity and the potential of low power consumption. After that, the spectral characteristics of time-multiplexing have been investigated, from which we conclude that the time-multiplexing actually expands the signal bandwidth and calls for accurate modelling of the behaviour of the cable at higher frequencies. Verified by the time domain simulations and an analysis of the cable's noise performance, the transmission line model has shown to be needed in the cable modelling and does present difficulties in the system level solution that will be addressed in the following chapters.

## 2.5 References

[2.1] B. Razavi, *RF Microelectronics*, second edition. Upper Saddle River, NJ, USA: Prentice-Hall, 2011.

[2.2] "Frequency-division multiplexing."

http://en.wikipedia.org/wiki/Frequency-division\_multiplexing, January 2015.

[2.3] "Code division multiple access." <u>http://en.wikipedia.org/wiki/Code\_division\_multiple\_access</u>, March 2015.

[2.4] "Time-division multiplexing." <u>http://en.wikipedia.org/wiki/Time-division\_multiplexing</u>, March 2015.

[2.5] D. M. Pozar, *Microwave engineering*, 4<sup>th</sup> edition. New York: Wiley, 2011.

[2.6] Cable Specifications, provided by Oldelft via personal e-mail.

[2.7] "Network Analyzer Basics." <u>http://cp.literature.agilent.com/litweb/pdf/5965-7917E.pdf</u>, August 2004.

[2.8] User's Guide HP 8753E Network Analyzer:

http://literature.cdn.keysight.com/litweb/pdf/08753-90367.pdf

[2.9] S. H. Hall and H. L. Heck, *Advanced Signal Integrity for High-Speed Digital Designs*. Wiley-IEEE Press, 2009.

[2.10] W. J. Dally and J. W. Poulton, *Digital Systems Engineering*. Cambridge University Press, April 2008.

[2.11] S. Palermo, ECEN 720, High-Speed Links Circuits and Systems lecture notes, Texas A&M University, 2014.

[2.12] J. Plusquellic, CMPE 650 Digital Systems Design lecture notes, University of Maryland, 2008.

[2.13] E. Mensink, D. Schinkel, E. Klumperink, E. van Tuijl and B.Nauta, "Power Efficient Gigabit Communication Over Capacitively Driven RC-Limited On-Chip Interconnects," *IEEE J. Solid-State Cir-cuits*, vol.45, pp. 447-457, February 2010.

[2.14] L. de Vreede, ET 4294, Microwave Circuit lecture notes, Delft University of Technology, 2012.

[2.15] R. Shimon. and M. Feng, "Exact noise parameters of lossy transmission lines," *Microwave Symposium Digest, 1999 IEEE MTT-S International*, vol.1, pp. 47 – 50, June 1999.

[2.16] A. M. Niknejad, *Electromagnetics for High Speed Analog and Digital Communications Circuits*, Cambridge Press, 2007.

[2.17] "Coaxial cable." http://en.wikipedia.org/wiki/Coaxial\_cable, February 2015

[2.18] H. Nyquist, "Thermal Agitation of Electric Charge in Conductors", Phys. Rev. 32, 110 (1928)

[2.19] J. C. Bellamy, *digital telephony*, 3<sup>rd</sup> edition. New York: John Wiley & Sons, 2000.

[2.20] B. Razavi, *Design of Integrated Circuits for Optical Communications*. New York: McGraw-Hill, 2002.

[2.21] J. G. Proakis, *Digital Communications*, 4th edition. Boston, MA, USA: McGraw-Hill, 2001.

[2.22] J. G. Proakis and D. K. Manolakis, *Digital Signal Processing: Principles, Algorithms and Applications*, 3<sup>rd</sup> edition. New York: McGraw-Hill, 1995.

# **Chapter 3 Equalization**

As shown in Chapter 2, the loss of the transmission line will introduce crosstalk between signals from different drivers. In order to resolve signals clearly, the finite bandwidth of the channel should be repaired before de-multiplexing. This process is called equalization (EQ). In this chapter several common equalization schemes will be introduced. After comparison the conclusion will be drawn that ADC-based equalization is more suitable in our application. In the last part of this chapter the detailed algorithms of ADC-based equalization will be covered.

## **3.1 Basics of Equalization**

### 3.1.1 Location of the Equalizer

There are two options for the location of an equalizer: TX or RX. In the case of TX EQ, the high-frequency components of the signal will be pre-emphasized before transmission. This approach potentially leads to SNR reduction, since the low-frequency components will be partly suppressed to allow emphasizing the high-frequency components within the swing limitation set by the power supply. Another disadvantage of TX EQ is that the EQ coefficient adjustment calls for an extra feedback loop from RX to TX, which is against the target of cable and power reduction in the project. Moreover, TX EQ increases complexity on the TX side, which is also not desirable.

In RX EQ, the non-ideal channel response is repaired on the RX side. Due to the more relaxed power and complexity requirements on the RX side, the EQ effort spent on this side is relatively more tolerable. Therefore, equalization at RX is chosen in the project.

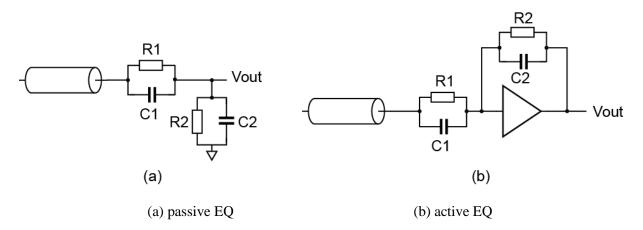

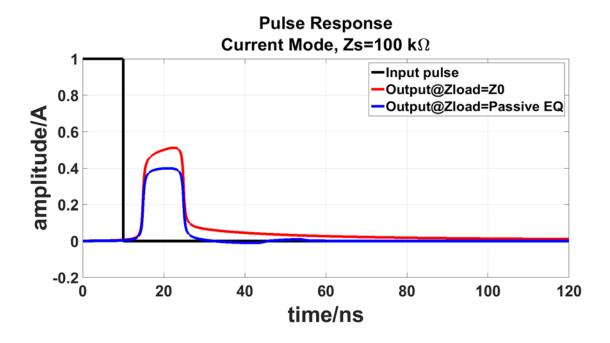

#### 3.1.2 Continuous-Time and Discrete-Time Equalization

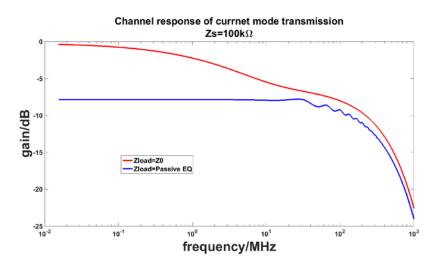

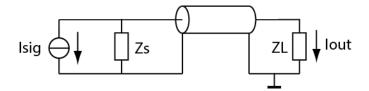

From a signal-processing point of view, channel equalization can be categorized as continuous-time EQ and discrete-time EQ. In continuous-time EQ, a passive or active network is connected to the cable in order to boost the overall channel bandwidth, as shown in Fig. 3-1. For a passive network, EQ is realized by attenuating the low-frequency components and retaining the high-frequency ones. Fig. 3-2 shows the simulated output signal for the case of current-mode transmission, with and without passive continuous-time EQ [3.1][3.2][3.3]. With EQ, the load current has a sharper falling edge compared with the characteristic impedance load. However, it can also be observed that the peak of the pulse response is degraded due to the low-frequency suppression. This can be understood with more ease in the frequency response, as is shown in Fig. 3-3.

As a consequence of that, the passive equalization scheme is more sensitive to the noise of the following stages since no gain is provided due to the nature of the passive network. This issue can be

addressed by active EQ [3.4][3.5], where not only the gain can be designed, but also the readout mode can be altered. These advantages come at the cost of additional power consumption of active devices.

Besides these differences between passive EQ and active EQ, a common disadvantage of continuoustime EQ lies in that only a limited number of poles and zeros can be flattened, complicating the implementation of a high-order equalizer .This implies that it is may not be sufficient to implement only continuous-time EQ in applications requiring high accuracy, such as this thesis project. In such applications, it may be combined with discrete-time EQ to yield better performance.

Figure 3-1 Continuous-time EQ

Figure 3-2 pulse response of current mode transmission<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Figure can be obtained using the derivation described in [3.1]

Figure 3-3 Frequency response of current mode transmission with different loads

Usually continuous-time EQ is installed as the first stage of a receiver, which relaxes the requirements on the following discrete-time EQ [3.5].

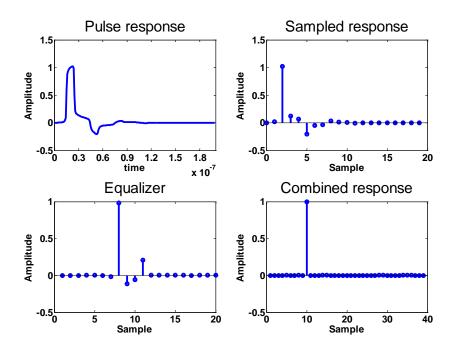

In a discrete-time EQ, the pulse response of the channel is sampled and then equalized in the discretetime domain. By employing criteria to reduce the residual error between the equalized response and the ideal one, a set of equalization coefficients can be obtained. This can be either a finite impulse response (FIR) or an infinite impulse response (IIR) description of the EQ impulse response. After convolution of the channel output with this EQ impulse response, the input pulse can be reconstructed as one impulse with other elements approximately being zero, as shown in Fig. 3-4 [3.4].

Figure 3-4 One example of discrete-time equalization

In the sampled response as shown in Fig. 3-4, there are usually a main impulse of which the amplitude is larger than that of other samples. Usually the main impulse is called main cursor, and the nonzero samples appearing before the main cursor are called precursors and those after the main cursor are called postcursors.

In high-speed digital links, FIR/IIR EQ is usually implemented in the analog domain, which makes the whole EQ loop compact and fast [3.6]. However, if higher precision with lower transmission speed is required in the application, more stress should be put on the accuracy than the speed, and such an analog-intensive way of equalization should be modified accordingly.

#### 3.1.3 ADC-Based Equalization

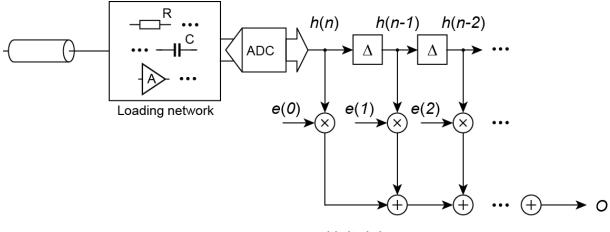

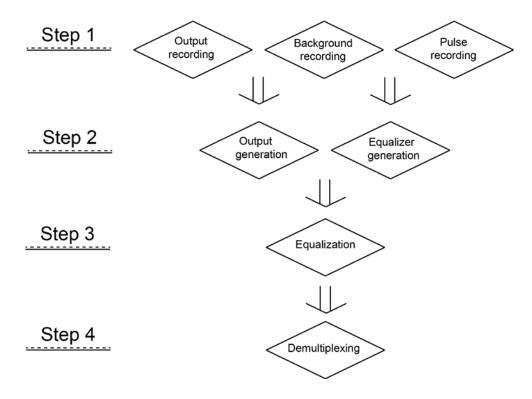

Besides the EQs discussed above, one promising solution to our application is ADC-based EQ. As shown in Fig. 3-5, in such a scheme the output signal at RX is sampled and digitized first, and then it is sent to the digital signal processing (DSP) unit where EQ is done in the digital domain. Moreover, an ADC and DSP are typically already present in ultrasound systems, and equalization is expected to be a relatively simple task compared to the signal processing already taking place. Since the power and complexity at RX are less critical in our application, such a scheme is finally chosen and applied in the project.

$\Delta$ =Unit delay

Figure 3-5 ADC-based equalization

Compared with the aforementioned analog-intensive implementations, another advantage of ADCbased EQ is that both the algorithm and the coefficients can be adjusted with more flexibly. This property will benefit the case where the channel response varies with the cable length, layout and wiring situation. However, due to the good shielding of the micro-coaxial cable used in our application, the cable's electrical character is found to be quite stable with cable bending and twisting. Therefore, the one-time calculated EQ coefficients can be stored in hardware and used for a long time, which saves the effort of adjustment.

In this section, different aspects of equalization have been introduced, with the proposal of ADCbased EQ in our application. The details of the EQ algorithm will be discussed in the next section.

# **3.2 Equalization Algorithms**

Based on the information of the channel response, an equalizer should be designed in order to cancel all the pre-/post cursors. Mathematically, the algorithm can be expressed as

$$E * H * C = C \tag{3-1}$$

where *H* is the pulse (not impulse!) response of the whole channel, *E* are the coefficients of the equalizer, and *C* denotes the input signal series. Here the symbol "\*" represents convolution instead of simple dot multiplication. Since *C* stays on both sides of the equal sign, after simplification *C* can be removed and *E*, H can be combined as an overall operator applying on the input signal:

$$E * H = U \tag{3-2}$$

where U is the sampled pulse response of an ideal channel, which contains one impulse and other samples being zero. This implies that E should be the inverse of H. However, due to the finite storage space, the recorded H is of finite length. In consequence, an error between the combined response and the ideal one has to be tolerated. Based on the understanding of this error, two main algorithms for finding E, zero-forcing (ZF) and minimum-mean-square-error (MMSE) are studied and employed in the project [3.7].

## **3.2.1** Zero-Forcing Equalization (ZFE)

In zero-forcing equalization, the channel response is assumed to be accessible and noise-free. Based on this assumption, ZFE is designed to suppress residual pre-/postcursors after equalization to the largest extent. Mathematically, a quantity to measure the effect of the residual cursors is defined as peak distortion (PD) [3.7], which is the ratio between the summations of all the remaining pre-/postcursors and the main cursor,

$$PD(0) = \frac{\sum_{k=1,k\neq k_0}^{N+L-1} |O(k)|}{|O(k_0)|}$$

(3-3)

CONFIDENTIAL

where O is the combined response of the finite-length E and H,

$$0 = E * H \tag{3-4}$$

and  $k_0$  is the location of the main cursor. L is the length of H and N is the length of E.

However, there is no guarantee that PD(O) can always be minimized. In the special case that the PD of the pulse response itself is less than unity, there will be solution towards goal of the PD minimization [3.7]. This statement can be expressed as

$$PD(H) = \frac{\sum_{k=1, k \neq k_1}^{L} |h(k)|}{|h(k_1)|} < 1$$

(3-5)

where h(k) is the element of H and  $h(k_1)$  is the main cursor. Then the E towards the minimum PD(0) can be calculated by solving the following matrix equation<sup>2</sup>:

$$H_{ZFE} \cdot E = U = => E = H_{N \times N}^{-1} \cdot U$$

(3-6)

where  $H_{ZFE}$  a matrix composed of sampled pulse responses with different time delays,

$$H_{ZFE} = \left[ H_{k_1}, H_{k_1-1}, H_{k_1-2}, \dots, H_{k_1-N+1} \right]$$

(3-7)

where  $H_k$  is denoted by

$$H_k = [h(k), h(k+1), h(k+2), \dots, h(k+N-1)]^T$$

(3-8)

If some elements in  $H_k$  are not recorded in the implementation, they should be replaced by zero. U is the desired ideal response, which means there should be only one impulse in it.

$$U = [0,0,0,\dots,0,0,1,0,0,\dots,0,0,0]^T$$

(3-9)

Even though ZFE can effectively flatten the channel response, there are some drawbacks of this algorithm. First, the assumption of a noise-free channel response is not justified. In order to capture the channel response cleanly, the noisy channel response should be sampled repeatedly and averaged. In some time-varying or always-on channels where averaging is not possible, such an algorithm exhibits limited functionality in equalization. In our application, the signal is transmitted and processed in real time, and therefore on-line averaging may not be preferred.

Another drawback is that noise is enhanced. Since ZFE is aimed at completely flattening the low-pass channel response, any high-frequency noise added before the equalizer will be boosted due to the

<sup>&</sup>lt;sup>2</sup> From Expression (3-6) we may find the first and the last several terms of O might be still nonzero and cause the crosstalk to the signal from other AFEs. But as has been proved [3.7], by using such a set of coefficients as a N-element equalizer, PD(O) is minimized.

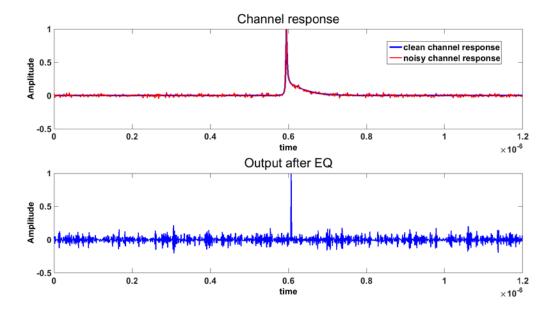

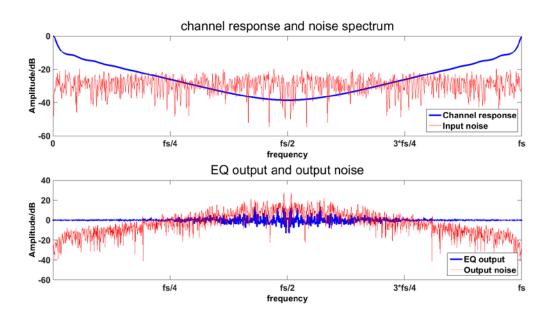

inverse response of the equalization. To verify this, a simulation has been carried out, in which the cable is modelled with a severer skin effect than that in our application, a pulse current is fed into the cable and read out from a 100  $\Omega$  load resistor. White Gaussian noise is plugged into the channel response to emulate the added noise through signal transmission. In Fig. 3.6 the channel response and the ZFE output are shown, where the equalizer's length is chosen to be long enough to avoid the noticeable truncation error due to the FIR limitation. In equalization a low-noise channel response is obtained by averaging several noisy responses. By comparison of the noise level in both time domain (Fig. 3.6 (a)) and frequency domain (Fig. 3.6 (b)), it can be found that the high-frequency noise is actually boosted. On the other hand, in Fig. 3.6 (a) it can be also found the long tail in the channel response is effectively cut out during ZFE, with a single pulse at the equalizer's output. Together with the frequency domain result shown in Fig. 3.6 (b), it verifies the property of complete channel flattening in ZFE.

(a) Noise enhancement of ZFE in time domain

(b) Noise enhancement of ZFE in frequency domain

Figure 3-6 Noise enhancement of ZFE

In ADC-based equalization, quantization noise is one of the noise sources that is enhanced. So in order to achieve the target resolution after equalization, the resolution of the ADC should be carefully considered. This will be discussed in the next chapter.

In order to avoided the drawbacks of ZF equalization, another equalization called minimum-meansquared-error (MMSE) equalization can be employed.

## **3.2.2 MMSE Equalization**

In MMSE equalization, the channel is equalized in the presence of noise in the channel response[3.7]. The optimization criteria of MMSE EQ is to get the best trade-off between the preventing noise enhancement and reducing pre-/postcursors after equalization. Suppose H' is the sampled channel pulse response with additive noise, n, then we have

$$H' = H + n \tag{3-10}$$

After equalization and comparison with the ideal combined response, U, there will be an error that consists of both residual pre-/postcursors and noise, which is

$$err = H' * E - U = (H * E - U) + n * E$$

(3 - 11)

CONFIDENTIAL

Reducing the term in brackets is the optimization goal for ZFE. For MMSE, the optimization goal is minimizing (3-11) as a whole,

$$||err||^{2} = \sum_{k=1}^{\overline{N+L-1}} |err(k)|^{2}$$

(3 - 12)

where *N*, *L* are the same as defined in ZFE. Operator """ means taking average of the several batches of errs. Minimization of  $||err||^2$  can be achieved by setting the partial derivative with respect to e(k) to zero,

$$\frac{\partial ||err||^2}{\partial e(k)} = 0, k = 1, 2, \dots, N$$

(3 - 13)

where e(k) are the coefficients of the equalizer:

$$E = \begin{bmatrix} e(1) \\ e(2) \\ \vdots \\ e(N) \end{bmatrix}, \qquad (3-14)$$

The solution of E can be expressed in the matrix form, which is

$$E_{MMSE} = \overline{(H_{MMSE}^{T} \cdot H_{MMSE})^{-1}} \cdot \overline{H_{MMSE}^{T} U}$$

(3 - 15)

of which  $H_{MMSE}$  is the matrix composed of sampled pulse response with different time delays,

$$H_{MMSE} = \left[ H'_{l_0}, H'_{l_0-1}, H'_{l_0-2}, \dots, H'_{l_0-N+1} \right]$$

(3 - 16)

where  $l_0$  is the starting position of H' used in MMSE.  $H'_k$  is denoted by

$$H'_{k} = [h(k), h(k+1), h(k+2), \dots, h(k+N+L-2)]^{T} + [n(k), n(k+1), n(k+2), \dots, n(k+N+L-2)]^{T}$$

(3-17)

Then the error can be expressed as

$$||err_{MMSE}||^{2} = \overline{(H_{MMSE} \cdot E_{MMSE} - U)^{T} \cdot (H_{MMSE} \cdot E_{MMSE} - U)}$$

(3-18)

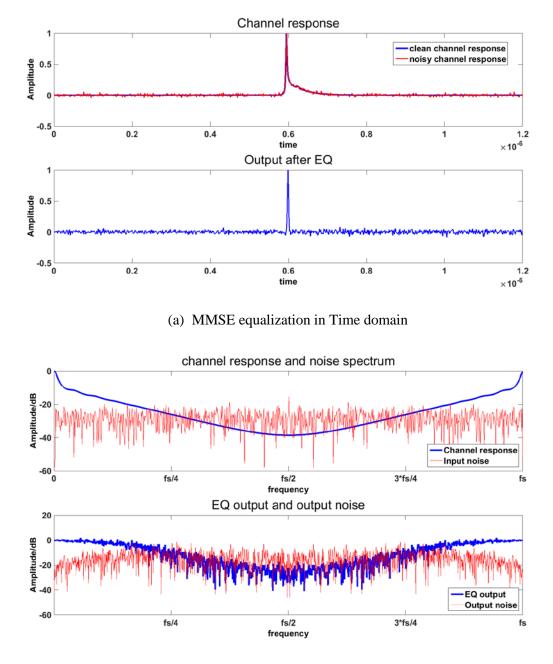

Compared with ZFE, MMSE equalization takes the overall error with noise as the optimization goal, and thus the noise enhancement effect becomes less obvious compared with ZFE, but at a cost of less complete channel equalization. To verify this, a simulation with the same configuration as that in ZFE has been run. The results in both time and frequency domain are plotted in Fig. 3.7. In comparison with the ZFE results shown in Fig. 3.6, the noise is less heavily levelled up in MMSE. However, the pulse is partially recovered, with several remaining pre-/postcursors compared with the result in ZFE,

as the penalty explained above. These effects can also be observed in the frequency domain shown in Fig. 3.7(b), where the EQ output spectrum (blue curve) is still of the low-pass form and the output noise spectrum is less enhanced.

In comparison with ZFE, it can be found that averaging is also carried out for obtaining the meansquare error. So from the point of view of real-time operation point of view, both algorithms are equally feasible.

(b) MMSE equalization in frequency domain

Figure 3-7 MMSE equalization

The aforementioned property of partial channel recovery in MMSE makes it suitable for highly noisy applications. However, if the SNR at the input of equalizer is high enough, the difference between ZFE and MMSE is small since in both cases the main effort will be paid on reducing the residual pre-/postcursors other than noise [3.8]. In this project, both algorithms have been implemented for comparison.

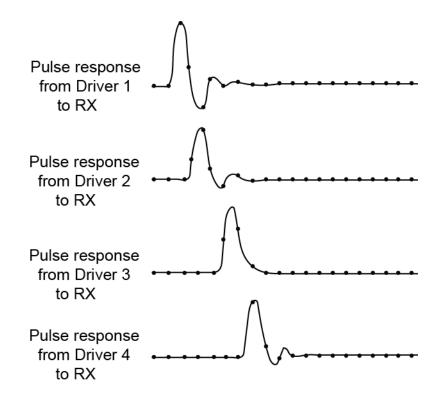

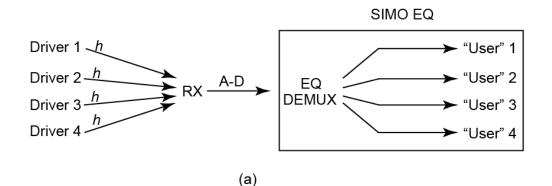

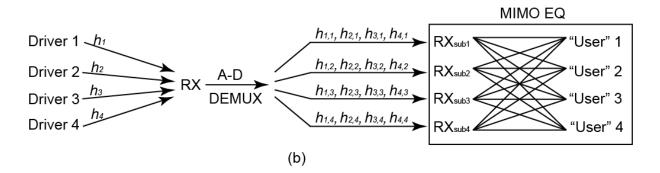

So far, the basics of equalization have been introduced. The application details in our project, such as the dependency of the equalizer's length on the loading condition and cable length, and the optimization of the equalizer's length, are explained in detail in Chapter 4. Besides that, in order to apply the algorithms to the time-multiplexing system, the difference between drivers should be taken into account, which turns the system, that has so far been assumed to be a single-input-single-output system, into a multiple-input-multiple-output (MIMO) system [3.9][3.10]. In consequence, one set of equalizer coefficients can only correspond to one driver. An equalization algorithm for the MIMO system is elaborated in Appendix B.

# 3.3 Summary

In this chapter, channel equalization has been introduced. By comparing with common equalization algorithms used in digital links, we propose an ADC-based scheme which is well matched to the requirements of our ultrasound system. Several equalization algorithms have been discussed, with an emphasis of pros and cons in our application.

# **3.4 References**

[3.1] E. Mensink, D. Schinkel, E. Klumperink, E. van Tuijl and B.Nauta, "Power Efficient Gigabit Co-mmunication Over Capacitively Driven RC-Limited On-Chip Interconnects," *IEEE J. Solid-State Circuits*, vol.45, pp. 447-457, February 2010.

[3.2] D. Schinkel, "On-chip data communication : analysis, optimization and circuit design" Ph.D. dissertation, University of Twente, Enschede, The Netherlands, 2011 [Online]. Available: http://doc.utwente.nl/77529/1/thesis\_D\_Schinkel.pdf

[3.3] E. Mensink, "High-speed global on-chip interconnects and transceivers" Ph.D. dissertation, University of Twente, Enschede, The Netherlands, 2007 [Online]. Available: http://doc.utwente.nl/57868/1/thesis\_Mensink.pdf

[3.4] S. H. Hall and H. L. Heck, Advanced Signal Integrity for High-Speed Digital Designs. Wiley-IEEE Press, 2009.

[3.5] S. Palermo, ECEN 720, High-Speed Links Circuits and Systems lecture notes, Texas A&M University, 2014.

[3.6] E. Alon, EE290C, High-Speed Electrical Interface Circuit Design lecture notes, UC Berkeley, 2011.

[3.7] V. Bhargava, EECE564, Detection and Estimation of Signals in Noise Lecture notes, the University of British Columbia, 2010.

[3.8] T. Deepa, "Linear equalizers and nonlinear equalizers." [Online]. http://www.srmuniv.ac.in/sites/default/files/files/Linear&nonlinearequalizers.pdf

[3.9] D. Tse and P. Viswanath, *Fundamentals of Wireless Communication*, Cambridge University Press, 2005.

[3.10] A. Maleki-Tehrani, B. Hassibi and J.M. Cioffi, "Adaptive Equalization of Multiple-Input Multiple-Output frequency selective channels," *Signals, Systems, and Computers, 1999. Conference Record of the Thirty-Third Asilomar Conference on*, pp. 547-551, October 1999.

[3.11] G.J.T. Leus and A.J. van der Veen, ET4235, Statistical digital signal processing lecture notes, 2014.

# **Chapter 4** System Design and Optimization

In this chapter the system design and optimization is carried out. The discussion starts from the determination of the signal transmission mode, which affects the design of the on-chip TX circuit. Next, the topology of the bulling blocks on the RX side, including a trans-impedance amplifier (TIA), extra gain stage and ADC, are introduced. Next the system-level modelling and optimization are made in order to provide accurate specifications for these building blocks. Finally, a summary of the whole system is given, as a starting point for circuit design and PCB design in the following chapters.

# 4.1 **Topology Selection of Driver**

#### 4.1.2 Current Mode or Voltage Mode

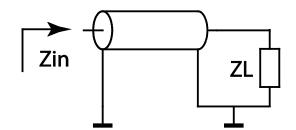

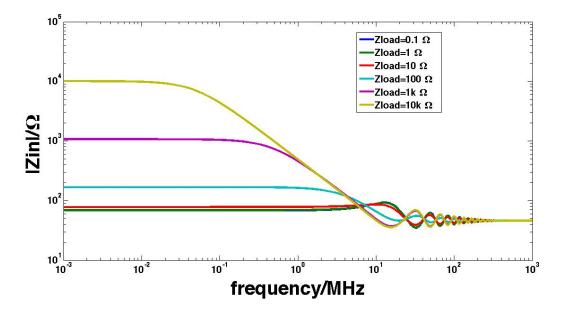

For the driver, in the circuit topology point of view, there are two alternatives, current mode and voltage mode regardless the termination conditions [4.1]. Due to transmission line effect, the input impedance as shown in Fig. 4-1 is [4.2]

$$Z_{in} = Z_0 \frac{Z_L + Z_0 \tanh \gamma l}{Z_0 + Z_L \tanh \gamma l}$$

$$(4-1)$$

where  $Z_L$  is the load impedance at the output port of the cable. Other parameters in expression (4-1) have been described in Chapter 2.

Figure 4-1 Input impedance seen from the output of a driver

From the input impedance vs. load impedance plot shown Fig. 4-2,  $Z_{in}$  is below 100  $\Omega$  in the frequency range of interest with different loads ranging from 0.1  $\Omega$  to 10 k $\Omega$ . This is because the loss in the cable screens the load and only the impedance close to  $Z_0$  can be seen at the input port. Such a low  $Z_{in}$  gives us the preference to using current-mode transmission, since a high  $Z_L$  does not help to build a high  $Z_{in}$  in order to utilize the advantage of light loading in voltage-mode transmission. A detailed analysis on the driving power in Appendix C shows that if the transconductance of a current-