Delft University of Technology Faculty of Electrical Engineering, Mathematics and Computer Sciences Laboratory of Electronic Components, Technology and Materials DIMES Technology Centre

### Foldable 3D Wafer Level SSL Package Using Flexible Interconnect

#### MASTER THESIS ELECTRICAL ENGINEERING

AUTHOR: Robert Sokolovskij robert.sokolovskij@gmail.com SUPERVISOR: Prof. G.Q. Zhang G.Q.Zhang@tudelft.nl

Delft, The Netherlands December 9, 2013

#### Abstract

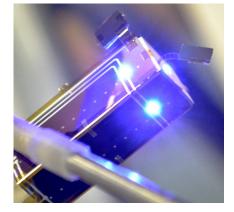

Solid State Lighting (SSL) is on track to replace conventional incandescent and fluorescent sources for general lighting. Even though it offers many benefits, the high initial device costs are still a major hindrance for many consumers. Packaging can account for up to half of the total device price, offering high potential for cost reduction. In this thesis, novel silicon wafer level packaging (WLP) concept and development platform are presented. The proposed packaging platform consists of silicon chips connected with neutral bending plane based flexible interconnect. Each chip contains an etched reflector cavity with wire bonded LED. The polyimide encapsulated flexible interconnects offer the benefit of folding the package into a 3D geometric shape. The space around the reflector cavity could be used to integrate active components and the backside - for passive components of the SSL driver circuit. The design, fabrication and characterization of the package is presented. A novel method to interconnect the front and backside of the chips is also incorporated into the process flow. After fabrication, packages are completed by adding LEDs, applying phosphor color conversion and release from substrate, followed by characterization of electrical, mechanical, thermal and optical performance. The developed packaging platform offers potential for future functional expansion by means of heterogeneous integration, possibly leading to a smart WLP package for SSL.

# **Table of Contents**

| $\mathbf{Li}$ | List of Abbreviations v           |                                                                                            |    |  |  |

|---------------|-----------------------------------|--------------------------------------------------------------------------------------------|----|--|--|

| 1             | Intr                              | roduction                                                                                  | 1  |  |  |

|               | 1.1                               | Integration and Packaging                                                                  | 2  |  |  |

|               | 1.2                               | LEDs for General Lighting                                                                  | 5  |  |  |

|               | 1.3                               | Functions of LED Packaging                                                                 | 8  |  |  |

|               | 1.4                               | LED Wafer Level Packaging                                                                  | 9  |  |  |

|               | 1.5                               | Proposed 3D WLP Design and Motivation                                                      | 15 |  |  |

| <b>2</b>      | Flex                              | xible Interconnect Integration                                                             | 17 |  |  |

|               | 2.1                               | Introduction                                                                               | 17 |  |  |

|               | 2.2                               | Current State of the Art                                                                   | 17 |  |  |

|               | 2.3                               | Flexible Interconnect Design                                                               | 21 |  |  |

|               | 2.4                               | Flexible Interconnect Fabrication                                                          | 26 |  |  |

|               | 2.5                               | Chapter Summary                                                                            | 32 |  |  |

| 3             | Embedded Capacitor Integration 33 |                                                                                            |    |  |  |

|               | 3.1                               | Introduction                                                                               | 33 |  |  |

|               | 3.2                               | Current State of the Art                                                                   | 33 |  |  |

|               | 3.3                               | Embedded Capacitor Design                                                                  | 38 |  |  |

|               | 3.4                               | Embedded Capacitor Fabrication                                                             | 39 |  |  |

|               | 3.5                               | Theoretical Estimations for High $C'$ MIM Integration $\ldots \ldots \ldots \ldots \ldots$ | 40 |  |  |

|               | 3.6                               | Chapter Summary                                                                            | 47 |  |  |

| 4             | Pac                               | kage Fabrication and Assembly                                                              | 49 |  |  |

|               | 4.1                               | Introduction                                                                               | 49 |  |  |

|               | 4.2                               | Integrated Process Flow                                                                    | 49 |  |  |

|               | 4.3                               | Post-Fabrication Assembly                                                                  | 53 |  |  |

|               | 4.4                               | Chapter Summary                                                                            | 57 |  |  |

| <b>5</b>      | Pac                               | kaging Characterization                                                                    | 59 |  |  |

|               | 5.1                               | Introduction                                                                               | 59 |  |  |

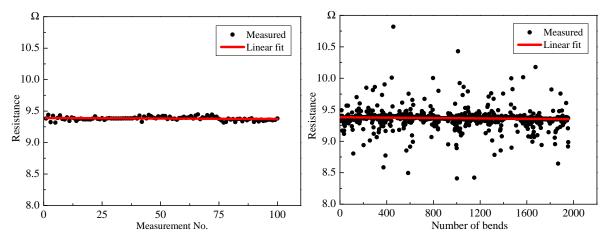

|               | 5.2                               | Interconnect Bending Tests                                                                 | 59 |  |  |

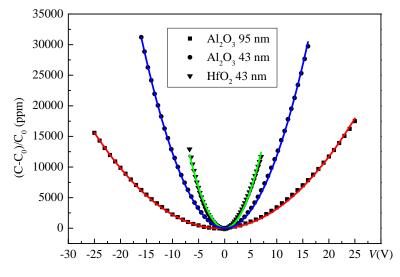

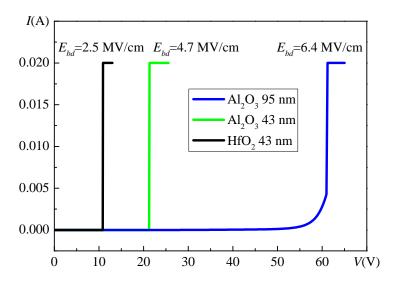

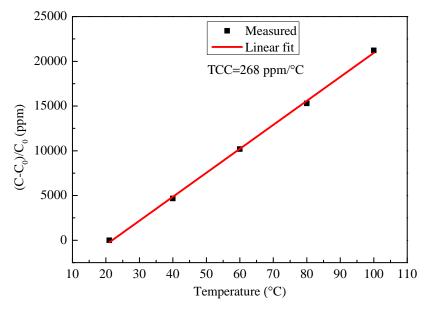

|               | 5.3                               | Embedded Capacitor Characterization                                                        | 62 |  |  |

|               | 5.4                               | Package Thermal Performance                                                                | 65 |  |  |

|                      | 5.5 Device Optical Performance                          | . 66 |

|----------------------|---------------------------------------------------------|------|

|                      | 5.6 Chapter Summary                                     | . 68 |

| 6                    | Conclusions and Future Outlook                          | 69   |

|                      | 6.1 Results and Conclusions                             | . 69 |

|                      | 6.2 Recommendations for Future Work                     | . 71 |

| A                    | ppendix A Complementary Technologies for 3D integration | 73   |

| A                    | ppendix B Heat Dissipation in LED Packages              | 77   |

| A                    | ppendix C Phosphor Coating Methods for SSL              | 81   |

| A                    | ppendix D Dielectric Constants                          | 83   |

| List of Publications |                                                         | 85   |

| A                    | cknowledgments                                          | 87   |

| R                    | References                                              | 90   |

# List of Abbreviations

| 3D                     | 3 dimensional                           |

|------------------------|-----------------------------------------|

| ALD                    | Atomic layer deposition                 |

| $\mathbf{AR}$          | Aspect ratio                            |

| ARDE                   | Aspect ratio dependent etching          |

| BCB                    | Benzocyclobutene                        |

| BEOL                   | Back-end-of-line                        |

| BHF                    | Buffered hydrofluoric acid              |

| BOE                    | Buffered oxide etch                     |

| CAD                    | Computer-aided design                   |

| $\mathbf{CC}$          | Correlation coefficient                 |

| CCT                    | Correlated color temperature            |

| CMOS                   | Complementary metal-oxide-semiconductor |

| $\mathbf{CMP}$         | Chemical-mechanical polishing           |

| CoB                    | Chip-on-board                           |

| CRI                    | Color rendering index                   |

| CTE                    | Coefficient of thermal expansion        |

| DBC                    | Direct-bond-copper                      |

| $\mathbf{DC}$          | Direct current                          |

| $\mathbf{DF}$          | Dissipation factor                      |

| DI                     | Deionized water                         |

| DRIE                   | Deep reactive-ion etching               |

| DSP                    | Double-side polished                    |

| $\mathbf{DUT}$         | Device under test                       |

| $\mathbf{EBR}$         | Edge bead removal                       |

| $\mathbf{E}\mathbf{M}$ | Electromigration                        |

| EPD                    | Electrophoretic deposition              |

| $\mathbf{ESD}$         | Electrostatic discharge                 |

| $\mathbf{EUV}$         | Extreme ultraviolet                     |

| F2R                    | Flex-to-Rigid                           |

| $\mathbf{FEM}$         | Finite element modeling                 |

| FEOL                   | Front-end-of-line                       |

| $\mathbf{FM}$          | Failure modes                           |

| FPP                    | Four point probe                        |

| GaAs                   | Gallium arsenide                        |

| $\operatorname{GaN}$ | Gallium nitride                                                |

|----------------------|----------------------------------------------------------------|

| HB-LED               | High brightness light emitting diode                           |

| HF                   | Hydrofluoric acid                                              |

| HNA                  | Isotropic Si etchant (HF:HNO <sub>3</sub> :AcOH)               |

| $HNO_3$              | Nitric acid                                                    |

| I/O                  | Input/output                                                   |

| IC                   | Integrated circuit                                             |

| ICP                  | Inductively coupled plasma                                     |

| IPA                  | Isopropyl alcohol                                              |

| IR                   | Infrared                                                       |

| KOH                  | Potassium hydroxide                                            |

| LED                  | Light emitting diode                                           |

| LPCVD                | Low pressure chemical vapor deposition                         |

| LTO                  | Low temperature oxide                                          |

| MEMS                 | Micro-electro-mechanical systems                               |

| MIM                  | Metal-insulator-metal                                          |

| MMC                  | Metal matrix composite                                         |

| MOCVD                | Metalorganic chemical vapor deposition                         |

| $\mathbf{MSM}$       | Metal-semiconductor-metal                                      |

| $\mathbf{MtM}$       | More-than-Moore                                                |

| MTTF                 | Mean-time-to-failure                                           |

| NMP                  | N-Methyl-2-pyrrolidone                                         |

| NP                   | Neural plane                                                   |

| $\mathbf{PA}$        | Polyamide                                                      |

| PCB                  | Printed circuit board                                          |

| PDMS                 | Polydimethylsiloxane                                           |

| PE ALD               | Plasma enhanced atomic layer deposition                        |

| PECVD                | Plasma enhanced chemical vapor deposition                      |

| PES                  | Aluminum etchant (phosphoric acid - acetic acid - nitric acid) |

| PI                   | Polyimide                                                      |

| PIP                  | Polysilicon-insulator-polysilicon                              |

| $\operatorname{RDL}$ | Redistribution layer                                           |

| $\mathbf{RF}$        | Radio frequency                                                |

| RPM                  | Revolutions per minute                                         |

| RTA                  | Rapid thermal anneal                                           |

| $\mathbf{SAM}$       | Scanning acoustic microscopy                                   |

| $\mathbf{SiC}$       | Silicon carbide                                                |

| SiP                  | System-in-package                                              |

| $\mathbf{SMD}$       | Surface-mount device                                           |

| $\mathbf{SMT}$       | Surface-mount technology                                       |

| $\mathbf{SMU}$       | Source/monitor unit                                            |

| $\mathbf{SoC}$       | System-on-chip                                                 |

|                      |                                                                |

| SOI            | Silicon on insulator                   |

|----------------|----------------------------------------|

| SPD            | Spectral power distribution            |

| SSL            | Solid state lighting                   |

| TCC            | Temperature coefficient of capacitance |

| TE             | Thermoelectric                         |

| $\mathbf{TFT}$ | Thin film transistor                   |

| $\mathbf{TMA}$ | Trimethylaluminum                      |

| TMAH           | Tetramethylammonium hydroxide          |

| $\mathbf{TSV}$ | Through silicon (strata) via           |

| UV             | Ultraviolet                            |

| VCC            | Voltage coefficient of capacitance     |

| WL-CSP         | Wafer level chip scale packaging       |

| WLP            | Wafer level packaging                  |

| YAG            | Yttrium aluminum garnet                |

### Chapter 1

## Introduction

Since its invention, the light emitting diode (LED) has gradually established itself as the main light source for a broad range of applications. It is extensively used in many consumer electronics devices for indicator lights, portable light sources (flashlights), switches, information displays and automotive applications. First reports of electroluminescence date back to 1907, when H. J. Round published his observations that silicon carbide (SiC) crystals emitted light with voltage applied. Unfortunately his explanation of the observed phenomenon was inaccurate. The invention of the first visible LED is mostly credited to Nick Holonyak, Jr. in 1962 [1], though Oleg Losev reported electroluminescence of silicon carbide diodes 35 years earlier [2]. Despite the arguable origins, LED indicators of various sizes, colors and brightness levels can nowadays be found in virtually every electronics device.

Solid state lighting (SSL) is the application of LEDs for various illumination purposes. It introduces many benefits over conventional incandescent and fluorescent light sources, such as low power consumption, higher efficiency, absence of hazardous materials (mercury vapour, lead), exceptionally long lifetimes [3] and novel applications of lighting, however LED chips can only emit a narrow band of wavelengths, that is, monochromatic light of a single color. The color of emitted light is related to the band-gap of the semiconductor device, which in turn is dependent on material composite (e.g. GaN, GaAs, AlGaIn etc.). Therefore, certain wavelengths of the visible spectrum need to be combined so as to stimulate the perception of white light in the human eye.

High quality white light generation is only one of the main challenges associated with the design of SSL bulbs or luminaires. Other aspects include the design of power supply (driver) circuitry, optics, heat dissipation, demand for increasing light output and extremely long lifetime of the entire product. So the LED die is only a small part of the entire system. The costs of manufacturing SSL light sources are substantially higher than conventional light bulbs. According to a recent report [4], packaging of LEDs accounts for up to 50% of the total device cost. On the other hand, it suggests high potential for overall price reduction if novel approaches are further developed.

A promising approach to reduce the costs associated with LED packaging is to integrate them in functional silicon based packages during processing compatible with back-end-of-line (BEOL) fabrication steps. This method is known as wafer level packaging or WLP. The purpose of this research is to design and fabricate a novel SSL package prototype on a silicon wafer with integrated additional functionality that includes utilization of flexible interconnects to form 3D substrates, light reflector cavities with integrated LEDs and passive IC components, thereby demonstrating a heterogeneous integration approach for SSL applications.

This introductory chapter will first briefly cover the known device packaging and integration approaches for the IC (integrated circuit) industry. Then the issues with LED adaptation for SSL applications are presented as well as an overview of conventional packaging technologies for LEDs. Finally, a review of WLP is given followed by the motivation for the proposed 3D design.

#### 1.1 Integration and Packaging

For almost 5 decades, Moore's law [5] has been the main guideline for the continued increase of functionality per unit silicon chip area. Ongoing feature size reduction approximately every two years (22 nm at time of writing), allows for the increase in transistor count per silicon area and therefore increases device performance and functionality with lower power consumption and heat generation. Reduction of the chip size on a Si wafer also yielded continuous decrease in manufacturing costs, since more devices could be fabricated on the same wafer. With every new node, lithographic scaling had to handle a growing amount of challenges to keep up with Moore's law. It has been recently reported [6] that sub 32 nm technologies will no longer possess the benefit of cost reduction due to increasing processing and extreme ultraviolet (EUV) equipment complexity. To continue the trend for more functionality per Si area new integration concepts known as More than Moore (MtM) [7] are gaining R&D momentum.

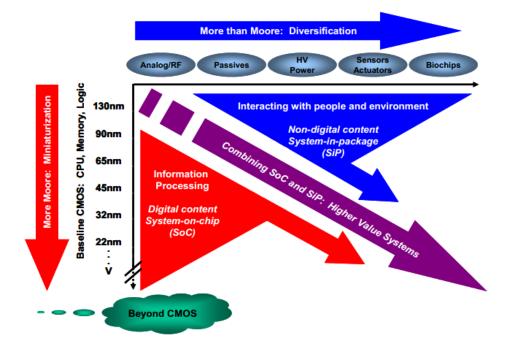

The MtM approach aims at combining several semiconductor technologies on a single chip, as depicted in fig. 1.1. Two directions are shown: digital circuitry will continue to follow

Figure 1.1: Combining Moore's law and More than Moore integration [7].

the lithographic scaling trends but additional functionally will be added to the same system by adding analog, RF or passive components. Integrated MEMS sensors would allow the to interact with the environment and the user. Such multifunctional systems on a chip (SoC) or in package (SiP) are applied in high end (consumer and industrial) applications.

Incorporation of additional functionality without increasing the floor plan area of the chip is a challenging task. Integrated circuits are usually considered as 2D, planar devices. Adding analog, sensing and other functions as well as passive components to a digital chip will significantly increase the 2D area of the die. Such an approach to heterogeneous integration could have an inverse effect on MtM, since the functionality per chip area would actually reduce as well as result in serious final device yield issues. An alternative and highly promising path towards MtM is by implementing 3D heterogeneous integration.

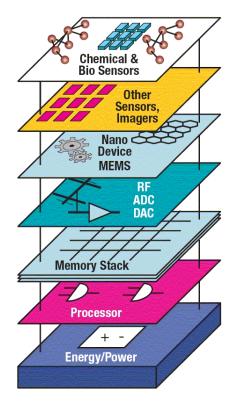

3D integration is based on utilizing the vertical dimension of the chip, without altering the planar area, by stacking multiple technologies on top of each other, forming a single SiP. Such ultimate design concept incorporating not only different functions but also new materials is presented in fig. 1.2. [8]. The enabling technologies driving 3D stacking and packaging

Figure 1.2: Functionality stacking for 3D integarion [8].

research are [9]:

- Through silicon (or strata) via TSV interconnections

- Wafer thinning

- Wafer alignment and bonding

These technologies can be further diversified in terms of various integration approaches, compatibility with other fabrication processes, intended applications and manufacturing costs.

A brief overview of the aforementioned technologies for 3D integration is given in appendix A.

Wafer level packaging (WLP) is essential for heterogeneous SiP integration. It enables the advancement of 3D heterogeneous integration for SIPs based on MtM. The term WLP defines technologies and design options to perform as many packaging steps of processed dies directly on the wafer as possible, prior to chip dicing and separation. WLP offers benefits in package miniaturization, increased processing throughput by packaging high numbers of devices in parallel, integration of additional functionally and overall cost reduction. It has been successfully applied for analog and digital IC chips, power IC, MEMS devices and passive components packaging.

Miniaturization of integrated circuit packages is possible by employing wafer level chip scale packaging (WL-CSP) technology. As the name suggests, these packages have dimensions that must not exceed  $1.2 \times (\text{chip size})$  and preferably should be 1:1 with the chip. With the continuation of Moore's law, it has been observed that cost per transistor is decreasing with process node downscaling and increased wafer size, since more functionality is added per Si area or chip size is reduced, while the fabrication costs remain the same. At the same time, the price of single chip packaging was increasing with every node, since more chips with higher I/O counts had to be packaged and tested. Contrarily, WL-CSP package costs go down with smaller nodes, as more chips can be packaged in parallel with shrinking die sizes [27]. In addition to increased throughput, WLP of IC chips allows to perform testing and burn-in procedures before die separation which leads to manufacturing cost reduction. IC chips are designed with bondpads on the edges of the die. The bondpad pitch is continuously decreasing as the die size is reduced and number of I/O goes up. To accommodate all required connections from chip to PCB, redistribution layers (RDL) are incorporated into the WL-CSP. Redistribution process starts with chip surface passivation using photosensitive polymers like benzocyclobutene (BCB) or polyimide (PI). Then metalization is performed by sputtering or evaporation. The metal layer is patterned to form an array layout of metal pads from the peripheral chip pads, allowing to substantially increase the pitch. Lastly, solder bumps are formed on the redistributed array by electro or electro-less plating or other methods [28] and A wafer level flip-chip package is complete.

WLP for micro-electro-mechanical systems (MEMS) differs from IC chip scale packaging. The main purpose of MEMS WLP is to provide encapsulation and electrical connection for micro-machined devices before wafer dicing. MEMS devices need to be packaged without molding materials because they have moving parts. Glass wafers with cavities for electrical interconnections are bonded to device wafers by anodic bonding (appendix A), to secure the chips from mechanical damage during further processing. CTE mismatch between Si and glass can damage certain sensitive devices. To avoid CTE mismatch Si wafers can be used for device sealing. Direct Si-Si bonding would damage the fabricated devices due to high process temperatures (appendix A), therefore bonding by intermediate layers, such as frit glass, solder, metal or polymer is employed. MEMS resonators, vacuum or IR sensors require vacuum packaging. For such applications, sealing with anodic bonding is done in vacuum and special getter films are deposited inside the device cavity to adsorb oxygen generated at the Si-glass interface. WLP by wafer bonding provides an inexpensive and robust packaging solution for MEMS devices before chip dicing to prevent contamination with Si particles. Since MEMS can only be tested after chip separation, cost reduction and yield improvements are achievable with the WLP approach [29].

#### **1.2** LEDs for General Lighting

LEDs are essentially p-n junction diodes. Under forward bias voltage, light is generated by emitting photons during radiative recombination of electrons and holes in direct band-gap semiconductor materials e.g. III-V compounds. The band-gap of a semiconductor is related to the wavelength of emitted light through the well-known Planck's relation [10]:

$$E_g = h\nu = h\frac{c}{\lambda} \tag{1.1}$$

where  $E_g$  is the semiconductor band-gap,  $h=6.62617 \times 10^{-34}$  J·s – Planck's constant, c – speed of light,  $\nu$  and  $\lambda$  – frequency and wavelength of a photon. Even though the operation principal of LED is similar to a diode for electronics applications, there are numerous additional parameters that define the performance of LEDs in terms of optical and electrical performance.

An important quantitative parameter of a white light source is the color rendering index (CRI). Color rendering is an effect that a light source has on the appearance of objects, when compared to a reference source. Poor color rendering leads to objects appearing discolored and unnatural [11]. CRI is determined by comparing the colors of 14 Munsell samples illuminated by the source under test and the reference illuminant. A CRI value  $R_i$  for each sample is then calculated by:

$$R_i = 100 - 4.6\Delta E_i \tag{1.2}$$

where  $\Delta E$  – color difference between test and reference source. From eq. (1.2) it is evident that  $R_i$  can even have a negative value if color differences are very high. The average value of the first 8 samples is then calculated and gives the general color rendering index  $R_a$  which is usually quoted by the manufacturers of SSL. In general CRI < 80 is suitable for outdoor lighting, CRI > 80 used for indoor lighting and CRI > 90 is considered as sufficient for demanding applications, such as lighting for hospital operating rooms or art exhibitions. Unfortunately, there is an inherent trade-off between CRI and efficiency of SSL sources that needs to be taken into account when designing luminaires for various applications.

Because of wavelength dependence on the material band-gap, LEDs can only emit light of a single color. White light is a mixture of wavelengths of the whole visible electromagnetic spectrum and therefore it is not possible to produce white light with just a bare LED chip without employing color conversion techniques to stimulate the perception of white light in a human eye. Two approaches are used to produce white LED light for SSL applications: multi-chip combination and wavelength conversion [3, 12].

Our eyes see white light if three types of cones, located in the retina, are stimulated with similar intensity [13]. It is possible to mimic such stimulation by mixing two complementary, yellow and blue, color LEDs with appropriate power ratios. This dichromatic approach yields the highest luminous efficacy, but the CRI is lower than 20, unsuitable for lighting applications. Adding a red LED to the first two (trichromatic source) significantly improves the CRI > 80

at the expense of efficacy, but is suitable for general lighting. Reports on tetrachromatic multi-chip white light sources claim CRI of 95, at 6500 K CCT by selecting LED chips with appropriate peak emission wavelengths [14].

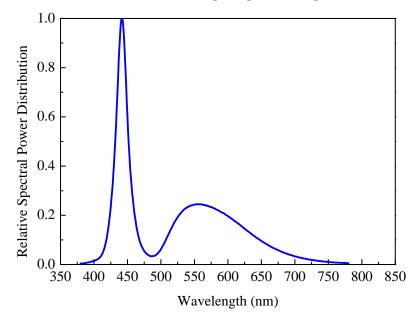

Wavelength converters are special materials that use high energy blue or UV photons (corresponding to the shortest wavelength) and down-convert part of these photons into lower energy (longer wavelength) photons. Most commonly used converter materials are phosphors, others include semiconductor converters and dyes [13]. When a blue photon excites (often called "optical pumping") yellow phosphor a photon, with wavelength in the wide middle range of the visible spectrum, is emitted. Extensively used yellow phosphors are based on yttrium aluminum garnets (YAG), doped with rare earth elements, YAG:Ce – used for SSL. By tuning the percentage of absorbed and transmitted light it is possible to obtain white light with correlated color temperature (CCT) in a range of 4000 K–8000 K, well suited for portable or outdoor lighting applications [15]. To improve the quantum efficiency and CRI of the source, various combinations of LED and phosphors have been investigated. Similarly to multi-chip designs, these are classified as dichromatic, using one LED and 1–2 phosphors [16], trichromatic and tetrachromatic, combining 1–2 LEDs with 1–4 phosphors [13].

Figures of merit for optical and electrical characterization of LEDs are summarized according to LED related literature [13] in table 1.1.

| Figure of merit                                   | Explanation                                                | Measure unit |

|---------------------------------------------------|------------------------------------------------------------|--------------|

| Luminous flux                                     | Light power of source as perceived by<br>the human eye     | lm           |

| Luminous efficacy                                 | Luminous flux per optical unit power                       | lm/W         |

| Luminous efficiency<br>(Source luminous efficacy) | Luminous flux per input electrical unit<br>power           | $\rm lm/W$   |

| Luminous intensity efficiency                     | Luminous flux per sr per input<br>electrical unit power    | $\rm cd/W$   |

| Luminance                                         | Luminous flux per sr per chip unit area                    | $\rm cd/m^2$ |

| Power efficiency                                  | Optical output power per input<br>electrical unit power    | %            |

| Internal quantum efficiency                       | Photons emitted in active region per<br>electrons injected | %            |

| External quantum efficiency                       | Photons emitted from LED per<br>electrons injected         | %            |

| Extraction efficiency                             | Escape probability of photons emitted<br>in active region  | %            |

Table 1.1: Photometric, radiometric and quantum performance measures for LEDs [13].

So far, only issues regarding the LED chip were discussed. A complete solid state lighting system is segmented into 6 levels of the value chain, LED chip being level 0 [17]. A summary of functions at each level is presented below [18]:

- 0. LED die. Semiconductor diode, emitting light by electroluminescence.

- 1. *LED packaging.* Providing electrical connection, encapsulation, mechanical support and heat dissipation. Phosphor layer formation for white light generation.

- 2. *Multi LED assembly.* Smaller LED packages are placed and interconnected on PCBs enabling higher luminous output and improved thermal management. Also used for white light generation with phosphors and multicolor chips.

- 3. *LED module*. Interconnection and housing of driver circuitry to convert grid AC power to DC power for LED assembly. Additional functionally is often added: dimming, smart control.

- 4. Luminaire. Complete and sealed housing of final product. Two distinct approaches exist: 1. Retrofit bulbs compatible with existing sockets and fixtures. 2. Beyond retrofit whole systems integrated in custom housings with extremely long lifetime without need for replacement bulbs.

- 5. *Lighting system*. Complex system of many luminaires with control, monitoring, programming and sensing functions, as well as power consumption profiling and failure detection. Applied for large scale projects: street, building or city lighting.

Because of system complexity, designing and manufacturing SSL luminaires demands close attention at every value chain level in order meet the reliability and lifetime requirements exceeding 50000 hours. More than 30 failure modes (FM) have been identified for SSL, with the list still expanding [19]. For comparison, compact fluorescent bulbs only have 7 identified failure modes. For a brief overview, FMs can be categorized into optical, mechanical, thermal and electrical domains. Optical reliability deals with the light quality degradation, lumen depreciation, phosphor cracking and yellowing over the operational period of the device.

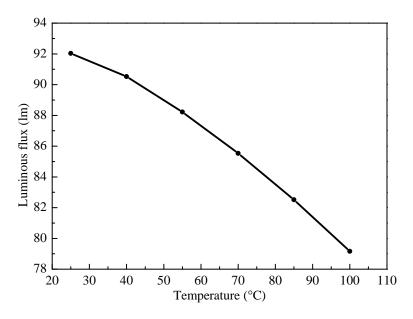

Mechanical reliability deals with defects in assembly, thermal stress, corrosion, delamination, cracks etc. of packages, modules and luminaries. Thermal stability is crucial for longevity of SSL systems. Increasing forward current is a way to increase luminous output, however this results in an increased junction temperature, that negatively affects lifetime as well causes shifts in emission spectrum peak. Ambient temperature inside the luminaire also plays an important role on reliability and is related to mechanical device stability mentioned earlier as well as electrical performance of power converters.

Power converters are the link between the input power source and the optical part of the luminaire. Typical driver circuit consists of three parts: control, switching and energy storage [20]. Studies have shown that the low power control circuitry that manages the switching frequency and determines the duty cycle of the converter is least prone to malfunction. Switching transistors and ceramic or electrolytic capacitors are regarded as the weak points of the circuit. These devices are more sensitive to thermal cycling and fail prematurely if are operated at elevated temperatures [20].

In addition to SSL specific failure modes, the electronics and interconnects also need to be validated in terms of electronics reliability. Failures due to electromigration, Joule heating, current crowding, and solder failure have to be considered.

Adapting the LED technology for general purpose lighting bulbs or luminaires, introduces a wide range of design, manufacturing, integration and reliability challenges, requiring multidisciplinary knowledge from various fields of research and engineering. Since SSL sources are required to meet stringent lifetime specifications, simulations and accelerated test methods are used to predict time to failure. Studies aimed at testing time reductions are of great interest for SSL industry [21]. Components need to be tested individually first, then as a complete device. Tests involving multiple stress scenarios at once are carried out [17] and only after complete validation a product can be put on the market.

#### 1.3 Functions of LED Packaging

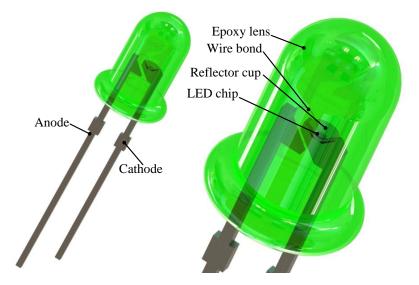

The main functions of any electronics package are chip protection and insulation, input/output signal interconnection, power distribution and heat dissipation. Packages for SSL applications also contain phosphors for color conversion and optics to provide high color quality and light extraction efficiency.

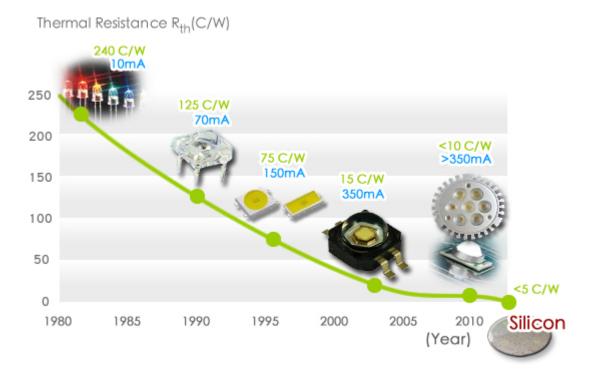

The requirements for LED packaging arise from the targeted application. With increasing power of the device, more advanced packaging solutions are required to effectively dissipate heat generated by the LED chip. Heat dissipation performance is commonly characterized by thermal resistance of a package. Thermal resistance  $R\theta$  is a property that defines how a material or body resists the flow of heat. In LED packaging applications thermal resistance is commonly measured between the semiconductor junction and the thermal pad, used for attachment to a heat dissipation structure (e.g. heatsink):

$$R\theta = \frac{T_J - T_C}{P} \tag{1.3}$$

Where  $T_J$  and  $T_C$  are junction and thermal pad temperatures respectively, P – thermal power dissipation of the chip. The development of LED packages in terms of thermal resistance reduction is presented in appendix B.

Light extraction, CCT control and light pattern formation are equality important aspects of packaging design for lighting applications. Low power LEDs are typically encapsulated using epoxy resins. Input power higher than 1W causes photo-thermal degradation of epoxy encapsulant due to increased junction temperatures and higher voltages. Degradation of encapsulant results in lifetime reduction caused by yellowing discoloration and cracking of the lens [22]. Silicones are more suitable for high power SSL applications, because they exhibit improved thermal stability, low shrinkage, low moisture absorption, variable Young's modulus, high optical transmittance for UV and visible spectrum and tunable refractive index [22, 23]. According to Snell's law (as described in appendix B), tuning of refractive index allows to maximize light extraction by reducing internal reflections between chip-encapsulant and encapsulant-air interfaces.

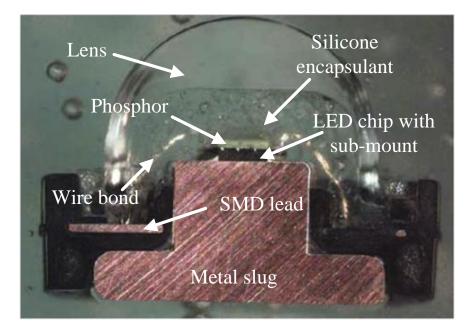

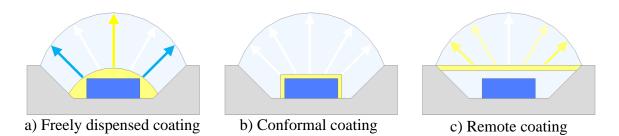

Silicone and phosphor mixtures are used to cover the surface of LED chips for down-

conversion based white light generation. Chips are first attached inside reflective cups and the phosphor-silicone compound is dispensed. There are 3 main methods to form phosphor layers:

- Freely dispensed coating

- Conformal coating

- Remote coating

A summarized description of these techniques is given in appendix C.

Designers of LED packages also have to take into account light beam collection and shaping. Materials used to form lenses need to have high transmittance in the visible spectrum range as well as be able to withstand thermal cycling and UV exposure. Glass has excellent properties for optical applications, but because of high cost and limited integration possibilities, is not commonly used. Various plastics with adequate optical properties are instead utilized for miniaturized LED optics molding.

LED optical system is often divided into primary and secondary optics. Primary optical elements are placed inside the package, in close proximity to the chip. An example of primary optics component is the reflector cup. Varying the depth and sidewall angle allows radiative pattern shaping. The reflector cup is coated with highly reflective material, like aluminum or silver. In addition to reflectivity, surface roughness of the reflector influences light extraction efficiency. Textured or diffusive reflectors extract more light as it is effectively scattered at varying angles, thereby reducing the number of total internal reflections and light trapping between the sidewalls [3]. The encapsulant material is also part of primary optics system. By shaping the top surface, where it interfaces with air, radiative patterns are formed as well as light extraction efficiency is enhanced.

Secondary optics are typically included for light pattern formation and additional mechanical support. Extra lenses and reflectors can be added and in certain cases phosphor coatings are placed on secondary lenses for maximizing light extraction with scattered photon extraction (SPE) method as described by [26].

#### 1.4 LED Wafer Level Packaging

Silicon based wafer level packaging is the next tier in component integration for power LEDs, succeeding CoB technology. Solid state lighting industry is still trailing behind in terms of WLP adaptation, but substantial research efforts are aimed at this technology for next generation lighting solutions. Because this work focuses on a novel WLP design for SSL applications, existing state-of-the-art designs will be reviewed.

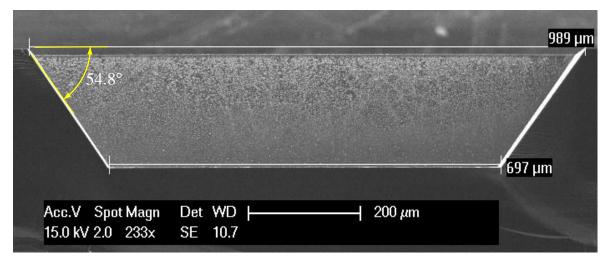

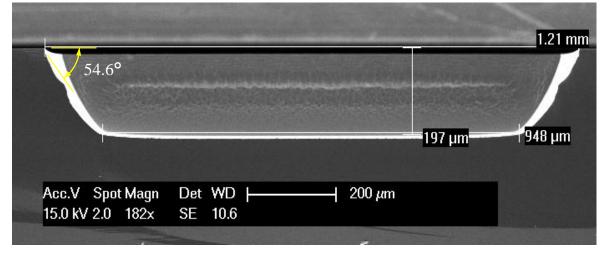

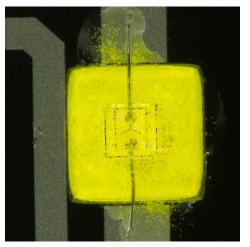

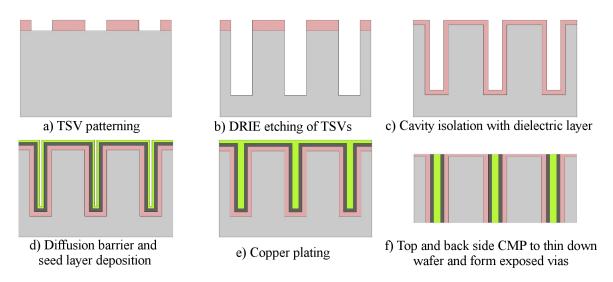

Application of silicon microfabrication processing enables multiple package formation on the entire wafer followed my LED chip placement and attachment using exiting pick-and-place and die attach technologies with increased precision leading to overall yield improvements. A basic WLP package consists of a single chip attached to the Si wafer surface and encapsulated with silicone. Metal interconnects are formed and routed for wire bonding to the PCB. An improved approach is to route the interconnects to the backside of the substrate for flip-chip mounting with solder. Deep reactive-ion etching DRIE and copper TSVs are used for vertical connections [30]. These designs have no light reflectors hence the emission field is only defined by the LED chip, which results in a wide angle pattern. Integrated micro-reflectors are fabricated by etching cavities in the substrate by DRIE or wet etching. Wet KOH or TMAH etch forms tapered cavities with 54.74° angle with respect to the top surface. These cavities are then lined with a thin reflective layer of metal for efficient light extraction. Simulations carried out for cavity optimization show that the taper angle as well as depth influence the light extraction efficiency of the package. It has been reported by Tsou and Huang [31] that for  $1.8 \text{ mm} \times 1.8 \text{ mm}$  surface area and 525 µm deep cavity optimum taper angle is  $53^{\circ}$  – close to the wet etch angle. Modifying the sidewall angle is possible with DRIE etching by tuning the process conditions. Angle variation is achievable by altering the O<sub>2</sub> percentage of the SF<sub>6</sub> + O<sub>2</sub> gas mixture inside the plasma chamber, the chamber pressure, DC bias of the electrodes and substrate temperature [32, 33]. DRIE demands higher equipment costs but permits more processing flexibility, especially for designs incompatible with wet etching.

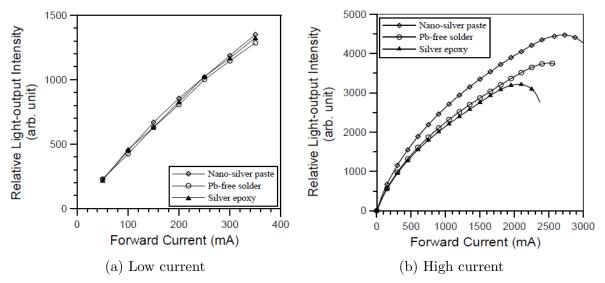

Most of LED WLP designs utilize the etched reflector cavities. Chips, placed inside these cavities by pick-and-place techniques, require reliable attachment and electrical interconnections. Proper attachment is done using adhesives like silicone or epoxy, re-flow soldering or sintering. The most suitable methods depend on the kind of chip used. Polymer based non-conductive adhesives provide reliable chip-attach for wire bond, flip-chip or vertical structure (one contact on top and one on bottom) LEDs, but suffer from low thermal conductivity. Electrically conductive die-attach materials have higher thermal conductivities and can be directly used for wire bond type chips. Wang et al. [34] investigated how different conductive die-attach materials influence the performance of high power GaN blue LEDs mounted on direct-bond-copper (DBC) alumina PCBs. The studied materials were silver epoxy ( $10 \text{ W/m}\cdot\text{K}$ ), lead-free solder ( $50 \text{ W/m}\cdot\text{K}$ ) and nano-silver paste ( $200 \text{ W/m}\cdot\text{K}$ ). Experimental results have shown that for low supplied current levels there was no significant difference in light output, which means that the heat generated by the LEDs could be efficiently transfered through the tested mounting interfaces to the DBC board (fig. 1.3(a)). Increasing the current

Figure 1.3: Relative light intensity of LEDs attached using three different materials at (a) low and (b) high supplied current values [34].

to higher levels resulted in greater temperature differences between the LED and substrate which indicates that heat transfer was insufficient. Best results were obtained using nano-silver, while chips mounted with silver epoxy burned at 2.5 A fig. 1.3(b).

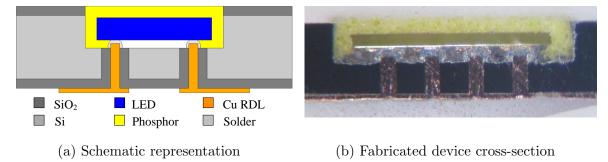

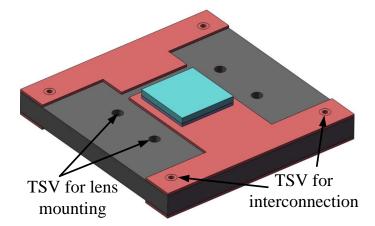

Flip-chip LEDs require the mounting interface to be patterned to expose the solder pads and avoid short circuits. Precisely patterning the bottom of a cavity is challenging, because of the need for lithographic exposure with proximity. A method to pattern the chip attachment and interconnection from the wafer backside was demonstrated in a WLP design by Zhang et al. [35]. The presented design fabrication starts with blind via etching at the backside and LED cavity etching at the from side using DRIE. The vias are then filled using same approach as for TSVs – electroplating. The front cavity is further etched with KOH until the copper pillars are exposed followed by BOE (buffered oxide etch) to remove the cavity passivation from the pillar tips. At this point the backside is still covered with a layer of copper, which is then covered in photoresist and electrodes are attached for solder platting. Solder is plated on the Cu pillar tips without any masking as there are no other conductive layers on the front-side. Solder is re-flown followed by the RDL formation using backside copper layer. LEDs are mounted and re-flow attached to the Cu pillars. Small amount of epoxy is dispensed inside the cavity and pre-cured with UV light, followed by phosphor powder printing with a squeegee blade and final curring to bind the epoxy and powder. The schematic of the finalized package as well as a cross-section image are presented in fig. 1.4. Such a design approach effectively combines the LED attachment and interconnection, but does not include a tapered cavity with reflective sidewalls, resulting in reduced light extraction efficiency.

Figure 1.4: Flip-chip WLP with Cu pillars and RDL [35].

Alternative approaches for flip-chip mounting and RDL formation were proposed by [31, 36]. Solder was chosen instead of Cu to fill the through holes and form the RDL patterns. Wet etching was used by [31] to form both the reflector and backside via cavities, followed by thermal oxide isolation and nickel evaporation in the vias. Solder balls or paste were placed inside the cavities with micro-gripper or squeegee respectively, followed by re-flow to fill the vias with solder and form protruding bumps for LED mounting and RDL formation. The resistance of resulting vias was less than  $5\Omega$ . Reflector cavity was not metalized by Tsou and Huang [31], whereas Chen et al. reports [36] on a wafer level package designed with metal reflectors, TSVs and cavity sealing by glass wafer bonding. The bottom of the reflective cavity was patterned to avoid shorts and the chip was mounted with adhesive prior to TSV etching. Glass wafer was bonded to seal the cavities and provide support to the Si wafer. The backside of the Si wafer was then thinned and TSVs, aligned to the LED contacts, were etched by DRIE. Polymer cavity passivation was carried out and laser drilling method was used to open the cavities and LED pads for metal sputtering and solder platting. Some of the glass sealant

wafers were coated with phosphor before bonding, forming a remote phosphor based WLP package directly applicable for SSL [36].

After mounting and interconnection, LED chips are encapsulated to complete a wafer level package. Various approaches are being developed to fill the reflector cavities with silicone and phosphor mixtures and form micro lenses for every package on the wafer with high throughput.

A method for conformal phosphor coating, based on injection molding, was developed and incorporated into a WLP process flow [37]. The package includes copper TSVs that are partially filled to reduce thermal stress. After vertical structure LEDs are attached and wire bonded, a mold is fixed and phosphor mixture is injected from one side. The phosphor is evenly coated on the chip due to capillary effect, followed by currying and mold removal. Unlike screen printing, this technique does not damage the wire bond leads during phosphor application and is suitable for all types of LED dyes. A separate wafer is etched with hemispherical cavities, which are filled with silicone, and is used as a mold to form an array of micro-lenses. The device wafer is flipped face-down and placed on the mold wafer. Once the silicone is partially cured the mold is removed. The polymer continues to cure and flows into additional TSV trenches (fig. 1.5), added to improve the shear strength of the lenses, due to poor adhesion of silicone to Si.

Figure 1.5: Wafer level package with TSVs for electrical connections and micro-lens attachment.

A moldless encapsulation method for LED arrays on a Si wafer was developed by Zhang and Lee [38]. UV curable epoxy was used as the encapsulation and lens material. Analysis of how the epoxy spreads on the wafer coated with low temperature oxide (LTO) was carried out. A syringe with precisely controlled injection volume was used to dispense the epoxy using the glob-top method, i.e. conformal dispense of viscous encapsulant at pre-defined areas for mechanical protection of devices. The obtained results indicated that freely dispensed epoxy, even when accelerated UV curing was applied, spreads too rapidly and a hemispherical lens, which, according to ray-tracing simulations [37], would result in maximum light extraction efficiency, cannot be formed. The maximum contact angle between the polymer and Si substrate with UV curring was  $56.5^{\circ}$  (fig. 1.6), where as angle of more than  $80^{\circ}$  is needed to form a hemisphere. Free flow constraining structures were designed around the encapsulation area to limit the spread of epoxy and increase the height to length ratio (H/L) of dome shaped

Figure 1.6: Highest achieved contact angle of freely dispensed epoxy after UV curing  $\theta$ =56.5° [38].

lens. Two variants of constraining structures were evaluated, namely squares of varying area outlined with single and double line trenches, as shown in fig. 1.7. The best results obtained were H/L=0.42 for single line and H/L=0.52 for double line, which indicates that an hemisperical lens (H/L=0.5) can be obtained with moldless glob-top dispense method employing flow-constrain structures.

(b) Double line constrain

Figure 1.7: Epoxy flow constraining structures: (a) single line, (b) double line [38].

An advantage of silicon based packaging is that additional functionality or devices can be directly integrated using standard silicon processing technology. Liu et al. demonstrated a thermoelectric (TE) device based on the Peltier effect, integrated into a Si LED package [39]. The heat removing structure was sandwiched between two Si wafers. The LED chip was placed on the cold side of the TE device and the hot side attached to a heatsink. Measurement results demonstrated that such active cooling method allowed to maintain the LED junction temperature at levels close to ambient temperature. In the proposed package the device and LED were connected in series to have the same driving current. Even though the TE cooling consumes additional power, it was determined that, compared to a package without TE device, the luminous efficacy of the device was 70% and 11% higher at 100 mA and 350 mA respectively.

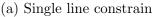

Sensor integration into the SSL module would allow to monitor the performance of the LED chip. In case, the chip starts to overheat brightness reduces and a shift in peak color occurs, that can be detected using a photo-sensor. Kim and Lee [40] designed a metal-semiconductor-metal (MSM) photo-sensor integrated on a thin polysilicon membrane. The sensor was placed on the top corner of the integrated micro-reflector cavity with the polysilicon membrane overhanging above the cavity. A portion of light emitted from the LED would

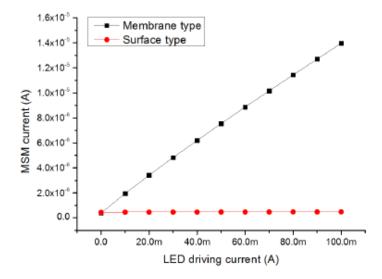

then be absorbed by the sensor and generate a photo-current. A design with sensors on the membrane and on the surface of the Si wafer was made to compare the amount of generated photo-current in the MSM sensor (fig. 1.8). The amount of light falling on the membrane sensor was substantially higher, leading to an increasing amount of photo-current generation with increase in LED driving current. The surface mounted photo-sensor absorbs only a small portion of emitted light and a change in photo-current is difficult to detect. Measurement results for both sensors are presented in fig. 1.9. By integrating sensors and a feedback network to the driving circuitry accurate monitoring and control of chip performance is possible by altering the supplied current.

Figure 1.8: Top view of MSM sensors on Poly-Si membrane and Si surface.

Figure 1.9: Photo-current generated by MSM sensors fabricated on poly-Si membrane and Si surface with increasing LED driving current.

To sum up the overview of current WLP technologies for SSL, a conclusion is made that silicon based packaging is a viable replacement of current LED packaging methods. Combining the reviewed technologies will allow to develop completely functional and compact form factor SSL modules with integrated circuitry, sensors and optical components. Such devices will follow the More-than-Moore heterogeneous integration concepts and evolve to low cost smart packages for high reliability lighting modules.

#### 1.5 Proposed 3D WLP Design and Motivation

Generally the term 3D WLP is used to describe packages that utilize vertical (TSV) interconnections, redistribution and interposer layers. These packages are still only as thick as the substrate wafer, essentially flat. In lighting applications, wafer level packaged LED chips would be singulated and individually placed on multi-led assembles. LED assemblies are designed to meet specific luminaire applications, some of them having all the LED chips facing one direction for unidirectional lighting, while others form omni-directional designs for uniform light distribution without complex secondary optics, as shown in fig. 1.10. In this

(a) Unidirectional

(b) Omni-directional

Figure 1.10: LED luminaires with (a) unidirectional [41] and (b) omni-directional [42] assemblies.

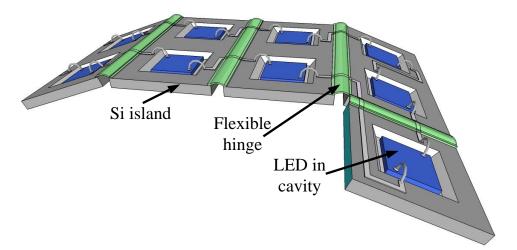

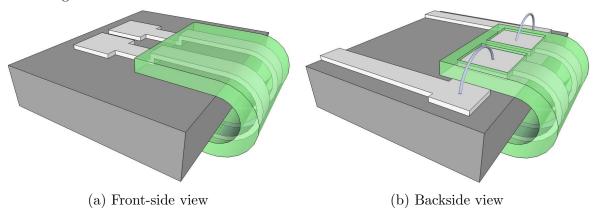

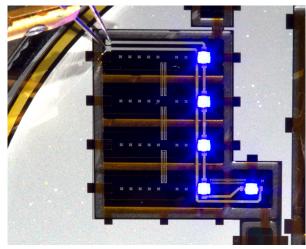

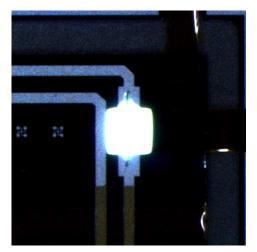

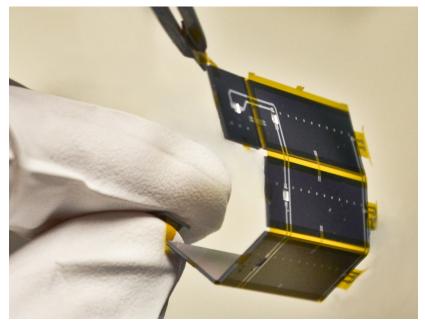

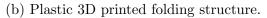

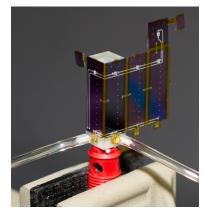

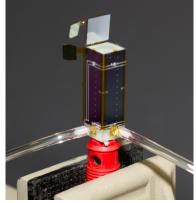

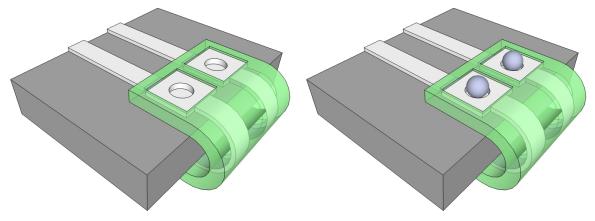

work, novel multi-chip WLP concept is introduced, which allows to form packages with 3D geometry and shape them into assemblies with omni-directional light emission. Si is used as substrate material to from packages with reflector cavities. Aluminum lines and bonding pads are added to interconnect packages together to form assembles. Geometrical shaping is achieved by adding flexible hinges with embedded interconnects followed by release of the formed packages by backside DRIE etching, forming rigid silicon islands with flexible joints (fig. 1.11).

Figure 1.11: Silicon based flexible WLP package concept.

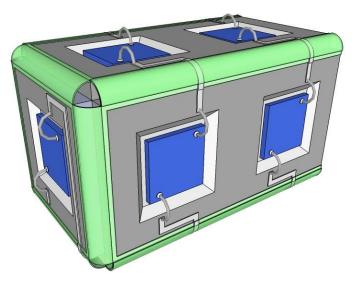

Figure 1.12: Flexible WLP design folded to form a cuboid.

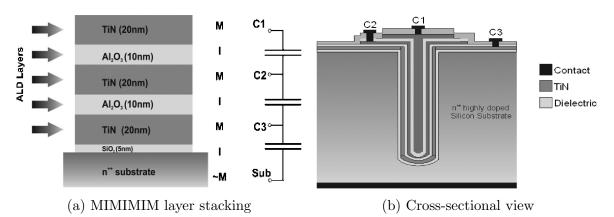

To demonstrate the compatibility of the proposed design with standard microfabrication technology, metal-insulator-metal (MIM) capacitors are integrated on the backside of the formed islands. Embedded capacitors can be used to replace their discrete counterparts in the LED driver circuitry. A method to interconnect the front-to-back side of the Si package through the chip periphery, based on foldable interconnect is also added to the package design. The finalized device is released from the substrate wafer and folded around a heatsink to form the desired shape. A design with 5 islands, forming a cuboid with the bottom sidewall left open, as shown in fig. 1.12, was chosen. Dimensions of the package were based on the current version of the G4 1W LED Capsule from Philips Lighting [43]. The proposed WLP design effectively merges the 1st and 2nd levels of the SSL value chain (ref. to page 7), thereby offering potential manufacturing cost reductions. A detailed description of the flexible WLP design and fabrication process will follow in subsequent chapters of this work. Each design aspect and integrated components will be presented separately followed by the complete process flow and final device characterization. The last chapter will summarize the work and achieved results and present suggestions for further development of the proposed concept.

### Chapter 2

## **Flexible Interconnect Integration**

#### 2.1 Introduction

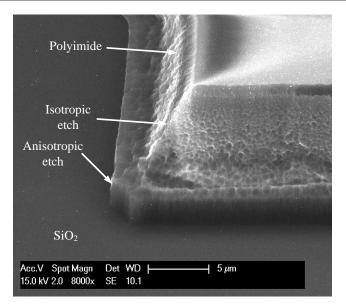

The proposed WLP requires flexible hinges with embedded interconnect for folding into the 3D geometry and providing power to every LED chip. In this chapter, the latest existing methods to form flexible/stretchable chips are reviewed. Then the design of the package is presented, that incorporates neutral bending plane based flexible interconnects encapsulated in polyimide. A method to connect the front-side to the backside of the chips is incorporated into the processing flow. The complete flow is discussed in detail, introducing the associated challenges and chosen solutions.

#### 2.2 Current State of the Art

Development of electronic components and devices that can withstand cyclic stress, strain and deformation without functionality degradation has gained increasing research interest in the last decade. These devices fall under a broad category of flexible and stretchable electronics engineering. A growing number of applications for such circuits has been demonstrated, ranging from flexible displays and sensors to miniaturized medical instruments and energy storage systems [44]. These devices require reliable interconnects that would withstand repeated mechanical deformation to comply with various form factors and while operating within required specifications.

Organic semiconductor materials are widely applied for large area flexible electronics. The benefit arises from the ability to deposit these materials on low cost substrates such as glass, plastic or metal foil using high throughput methods like ink-jet and roll-to-roll printing. Typical applications are in manufacturing of organic LEDs, flat and curved displays, flexible thin-film solar cells and thin film transistors (TFT). The main disadvantage of organic semiconductors is their inferior electrical properties (carrier mobility, resistivity), in comparison to inorganic semiconductors [45].

High performance chips are fabricated on rigid Si wafers. Integration of these devices for use in flexible electronics presents a challenging task with various approaches being developed. Silicon wafers are extremely rigid, hard and brittle with Young's modulus values from 130 GPa to 170 GPa for the  $\langle 100 \rangle$  and  $\langle 110 \rangle$  crystal orientations respectively [46]. Thin Si films (<300 nm) are known to exhibit size effect, which causes the Young's modulus to monotonically reduce with decreasing layer thickness [47]. This property as well as the reduced strain in thin layers has been utilized for flexible, thin Si based circuits, that can be transfered onto flexible substrates or curved surfaces. A transfer method for such silicon micro-structures, using a polydimethylsiloxane (PDMS) elastomer stamp, was presented in [48]. Thin structures, fabricated on silicon-on-insulator (SOI) wafers, are partially released by etching the buried oxide layer with HF. The soft stamp is pressed against the substrate and forms a conformal contact with the structures. The adhesion between an elastomer and a solid is peel rate dependent, thus, with sufficient peel velocity, the structures are transfered onto the stamp. To transfer the pattern onto another substrate the stamp is brought in contact and peeled slowly. In this case the adhesion is higher between the structures and the substrate resulting in efficient pattern transfer. Figure 2.1 shows arrays of thin Si bars transfered onto a spherical surface with radius of 1 cm, without delamination or cracking. A comprehensive study on

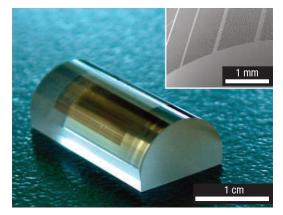

Figure 2.1: Thin silicon structures on spherical surface, applied by transfer printing [48]

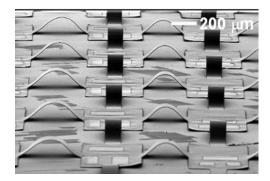

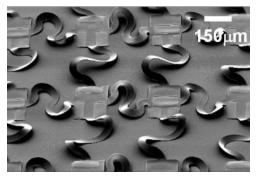

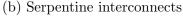

the thin silicon deformation that demonstrates the relations between thickness and bending radius as well as observed failure mechanisms has been conducted by Park et al. [49]. Transfer printing of thin silicon islands, joined with out-of-plane flexible interconnects onto pre-strained stretchable PDMS substrates, yields the formation of flexible and stretchable inorganic circuits, as demonstrated in [50]. After releasing the strained substrate arc-shaped non-planar ribbons are formed, as shown in fig. 2.2(a). The arrays could stretch and twist in multiple directions

(a) Arc-shaped interconnects

and strain of 11%, (with prestrain of 17%) was reported for the entire mesh. Replacing the arc with a serpentine layout (fig. 2.2(b)) with high substrate prestrain of 90% resulted in 100% elongation (system strain). Simulation and experimental results indicated that higher prestrain improves the system stretchability and increases the active component density due to shorter interconnect lengths. Thin Si and substrate transfer procedures pose a number of processing challenges. For many applications it is sufficient to employ flexibility and stretchability only at the interconnect, keeping the active devices on rigid Si. A common attribute of such designs is wafer segmentation by etching through the entire substrate, to form rigid islands with integrated components. The islands are held together by flexible or stretchable joints with embedded interconnects. High levels of flexibility have been demonstrated by placing the metal lines in between two layers of encapsulation material of equal thickness. Observing from the cross-section of the formed structure, the metal is located at the center. When bending is applied, one surface experiences tensile strain while the opposite side – compressive strain. It is known from mechanical beam bending theory, that at the center the tensile and compressive strains compensate each other therefore the stress at the center of the beam is approaching zero. This is known as the neural plane (NP). Flexible micro-cables have been successfully implemented, by placing the metal layer in the NP, for an implantable neural probe array [51]. Polyimide (Pyralin PI 2611) was chosen as the flexible substrate. A 5 µm thick layer was spin-coated and cured at 350 °C on a Si wafer covered with a thin Ti layer without using an adhesion promoter to enable easy release of the cable from the substrate wafer after processing is complete. Interconnects were formed by evaporating a 1 µm Cr/Au/Cr stack and lift-off patterning. The second PI layer of equal thickness was then applied and cured. The cables were patterned using RIE etching and then manually released by pealing with tweezers. The completed cable consisted of 30 interconnects with dimensions  $20000 \times 100 \times 1 \,\mu\text{m}$  (L  $\times$  W  $\times$ H) and 150 µm pitch, which demonstrates the possibility to fabricate high densitity flexible interconnects. The cable was then subjected to electrical and mechanical characterization and demonstrated high data transmission rates with proper isolation between the signal lines. Fatigue testing showed that the wire can withstand cyclic deformation which is necessary for implantation of neural probes in the human brain.

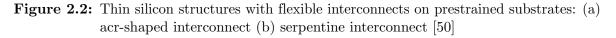

Stretchable interconnects have also been demonstrated by utilizing the NP. In this case PDMS is used as encapsulation material due to it's elastic properties. To accommodate the applied strains, interconnects with meandering shapes were designed. Gonzalez et al. [52] presented a study relating the shape of copper interconnects to strain distribution and the possible elongation that the interconnects can withstand. Three meander shapes were investigated: elliptical, "U" shape and horseshoe. Finite element modeling (FEM) results have shown that when deformation of 20% was applied, the horseshoe meander exhibited the smallest amount of stress, 40% less in comparison to the elliptical. A scale factor was defined that shows that with a constant meander radius to interconnect width ratio (R/W) (fig. 2.3) the equivalent plastic strain of the interconnects remains unchanged. With increasing scale factor plastic strain reduces, so it was concluded than wide meandering lines should be split into equally spaced parallel tracks with minimized widths to achieve maximum stretchability. An improvement from 20% to 100% elongation was observed when a wide line was split into

Figure 2.3: Horseshoe meander shape: R – inner diameter, W – line width,  $\theta$  – joining angle [48]

four lines of reduced width (from  $60 \,\mu\text{m}$  to  $15 \,\mu\text{m}$ ). Finally, higher elongation was obtained for horseshoe designs with higher joining angles  $\theta$ .

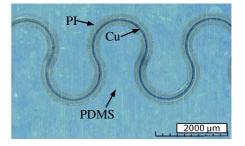

The horseshoe type meandering interconnects possess high single-stretch strain. During cyclic stretching, these interconnects failed after only 85 stretch cycles of 30% elongation [53]. In addition, delamination was observed between the metal lines and PDMS encapsulation [54], that presents a risk of premature failure. To increase the overall reliability of meandering interconnects a double encapsulation approach was investigated by [55]. In this case, horseshoe Cu tracks were first encapsulated in polyimide, before molding with PDMS, as shown in fig. 2.4. The experimental results revealed that the maximum elongation increased to 250%.

Figure 2.4: PI-enhanced stretchable interconnects [55]

A substantial improvement in the number of stretching to failure cycles (from 85 to 40000 at 30% elongation) was achieved. Delamination between PDMS and PI was observed at 65% stretching, however no interfacial delamination was observed between PI and metal, indicating that interconnects are reliably insulated by PI.

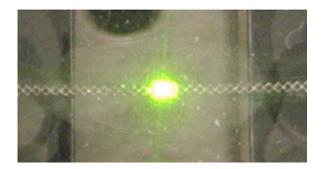

Liquid alloy materials have also been investigated for applications in flexible/stretchable interconnects. Alloys of eutectic gallium indium (EGaIn), injected into elastic hollow fibers or molds can achieve elongation levels exceeding 700% [56]. A common characteristic of this type of interconnects is the increase in resistance with stretching as the length of the conductor increases while the cross-sectional area reduces. The resistance variation can be minimized by using a diamond-shaped rather than a straight-line conductor design, because the channel length variation is reduced [57]. A functioning LED, connected to liquid-alloy diamond-shaped interconnects, encapsulated in PDMS, is shown in fig. 2.5. The device was subjected to stretching, bending and torsional twisting and still maintained proper operation.

Figure 2.5: PDMS encapsulated LED with EGaIn diamond-shaped interconnects [57].

#### 2.3 Flexible Interconnect Design

The main focus of this work was to design and fabricate a flexible Si based wafer level package for SSL applications. Various approaches were reviewed as evident from section 2.2. The package would consist of rigid Si islands with LEDs integrated inside reflector cavities. The LEDs should be connected in series to form wafer level LED assembles. The fabricated devices would be released form the substrate and folded into a 3D geometry. The design choices were weighed with regard to the following considerations:

- Current-carrying capability

- Mechanical bendability

- Compatibility with standard CMOS processing

- Compatibility with MEMS processing

- Reduction of overall process complexity

Current carrying capability of a conductor is largely determined by the electrical resistance of the chosen metal and physical dimensions. Resistance of a uniform conductor can be calculated as:

$$R = \rho \frac{l}{A} \tag{2.1}$$

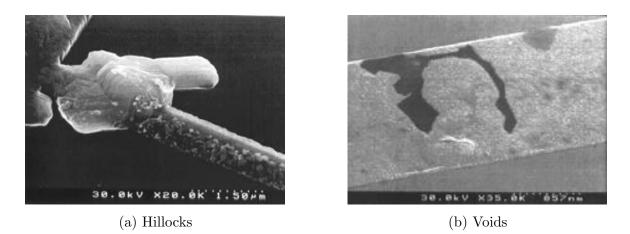

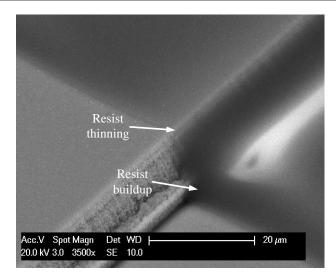

where  $\rho$  – electrical resistivity, l and A – length and cross-sectional area. Pure aluminum was used for the interconnects, because of package cost considerations, compatibility with the processing sequence and low electrical resistivity (2.7 µΩ·cm). Interconnects were designed to withstand possible failures due to electromigration (EM) during the entire operational lifetime of the LEDs. Electromigration is the effect of material transfer caused by electric field. When DC current flows through the conductor some of the free electron momentum is transfered to the metal ions, causing transfer of material in the direction of current flow. This effect causes buildup of metal atoms that form hillocks as well as voids at the grain boundaries of the metals [58]. Hillocks can result in short circuits between densely spaced lines, where as voids cause local resistance increases leading to complete line failure. An example showing aluminum film degradation caused by EM is shown in fig. 2.6. To estimate the mean time to failure (MTTF) of metal interconnects in integrated circuits, an empirical model, that takes electromigration into account, was developed by J. R. Black [59]:

$$MTTF = \frac{A}{J^n} \exp\left(\frac{E_a}{kT}\right) \tag{2.2}$$

Figure 2.6: Interconnect defects caused by electromigration [58]

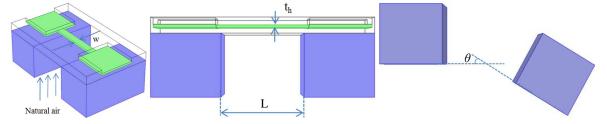

where A – constant related to the cross-sectional area of the interconnect, J – electric current density, n – scaling factor,  $E_a$  – activation energy (0.7 eV for Al), k – Boltzmann's constant (1.38 × 10<sup>-23</sup> J/K), T – absolute temperature. Interconnects integrated on Si can withstand higher current densities without melting than electrical wires, since the thermal conductivity of Si is high. To increase the lifetime of interconnects current densities must be kept below critical values. Elevated operating temperature of the device will also lead to reduced MTTF. Since LED junction temperatures can reach above 100 °C and generated heat is dissipated across the whole silicon island, the interconnect temperature will raise accordingly. At areas were the flexible hinges are formed, the metal lines are encapsulated between two layers of polyimide and the underlying silicon is etched away. FEM simulations were carried out to investigate how encapsulation of Al interconnects between layers of polyimide will influence the temperature of the interconnects [60]. The simulated geometry is shown in figure fig. 2.7. Joule heating, generated by current flowing through the Al interconnects was considered as

Figure 2.7: Geometry for FEM simulations of flexible interconnect[60].

the only heat source and natural convection and thermal radiation were used as heat transfer mechanics. To meet the lifetime requirements, MTTF of 25000 h was chosen as a minimum value. The maximum temperature difference between the package and ambient could not exceed 65 °C. The width of the hinge (L) and cross-sectional area ( $S=t_hW$ ) were chosen as variables for the encapsulated metal lines. The influence of bending angle on the package temperature was also evaluated. With all the mentioned constraints in mind, simulations were performed and a design rule was derived indicating that in order to meet the current requirement of 700 mA for high power LEDs at a 90° hinge bending angle the ratio L/S should be less than 2. In the fabricated package, the L/S=1.5 was chosen for the interconnects, with dimensions of  $900 \times 300 \times 2 \,\mu\text{m}$  (L × W × t<sub>h</sub>).

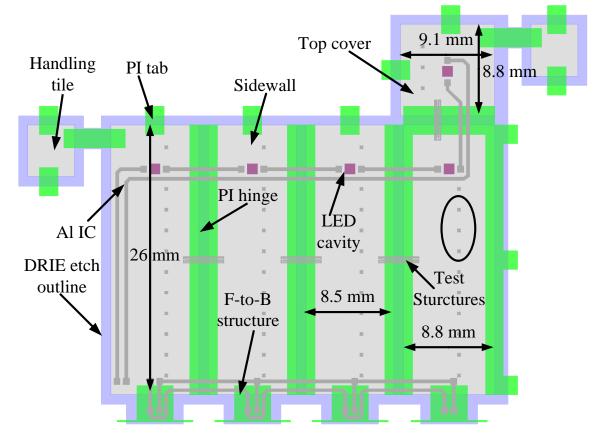

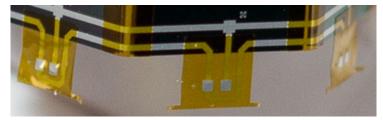

In the proposed package design, flexible interconnects are implemented to connect the LED chips in series and to form a flexible front-to-backside connections for components that are integrated on the backside of the chips. The front-side layout of the package is presented in fig. 2.8 with labels indicating each of the design components. The purpose of these components

Figure 2.8: Front-side layout of proposed WLP design.

will now be discussed:

- *Handling tile.* An dummy piece of Si used to ease handling of fabricated devices using tweezers. It can be pealed off or cut with a blade after final device mounting.

- *Polyimide tab.* After processing is complete these tabs prevent the devices from falling out of the wafer. They are cut with a fine blade in subsequent post-processing steps when the structures need to be released.

- *DRIE etch outline*. Outline of area were the Si is etched from the backside for device release form the wafer.

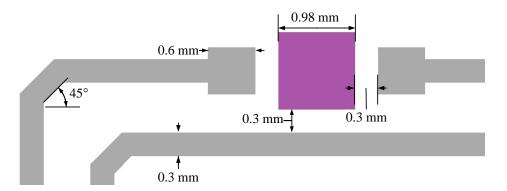

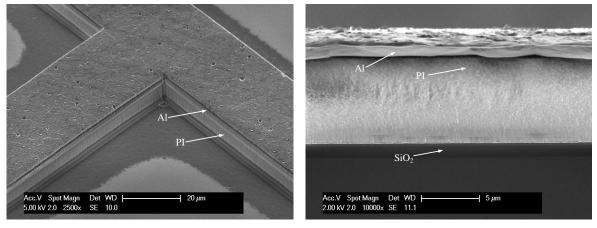

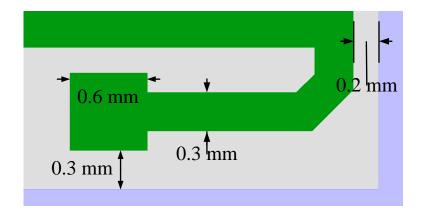

- Al interconnect. Provides power for series connected LEDs on every sidewall of the package. The dimensions of interconnects and bonding pads are shown in fig. 2.9. Multiple combinations of line width and thickness were considered to have the required cross-sectional area. The thickness of 2 µm was chosen to minimize the stress of encapsulated line, due to offset form the neutral plane. A 45° angle bend design was implemented to minimize the effect of current crowding [58].

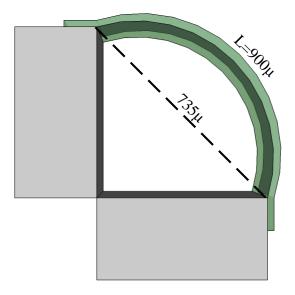

- *Polyimide hinge*. The flexible part between the rigid Si sidewalls. The minimum width of the hinge (hypotenuse) to form a right angle between two Si islands with wafer

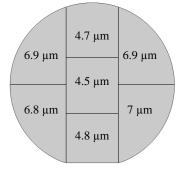

Figure 2.9: Dimensions of package interconnects and LED cavities.

thickness of  $520 \,\mu\text{m}$  is  $\sqrt{520^2 + 520^2} \approx 735 \,\mu\text{m}$ . The width of  $900 \,\mu\text{m}$  was designed to avoid stretching and form an arc-shaped bend, as shown schematically in fig. 2.10.

Figure 2.10: Schematic representation of right angle bend with arc-shaped polyimide hinge.

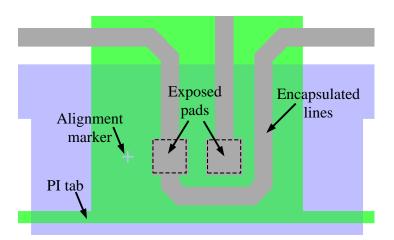

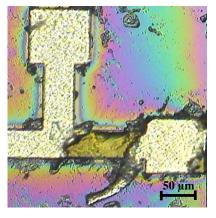

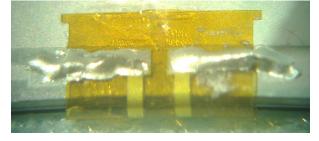

• Front-to-back interconnect structure. Al lines designed to overhang over the edge of the chip and encapsulated in polyimide with exposed contact pads fig. 2.11. The end of the structure is released from the wafer during through wafer backside etching. The

Figure 2.11: Polyimide based front-to-back interconnect structure.

released structure can now be folded to the backside of the chip using a precision micro-manipulator. An alignment marker is added to aid with the placement of this PI strip on the backside. After folding, the bottom of PI layer is glued to the Si and the exposed contact pads are wire bonded to designated pads on the backside, as demonstrated in fig. 2.12. Such an interconnect desing proves a alternative to TSV based interconnect which requires additional complex processing steps. The proposed structure does not require additional lithographic steps and is integrated during flexible hinge and interconnect fabrication.

Figure 2.12: Schematic representation of front-to-back interconnection

- *LED cavity*. A tapered sidewall cavity etched in the Si substrate, used for housing the LED chips. The cavity is coated with a thin layer of Al and is used as a reflector to improve light extraction efficiency and directionality. The design aspects and integration process of LED cavities are discussed in chapter 4.

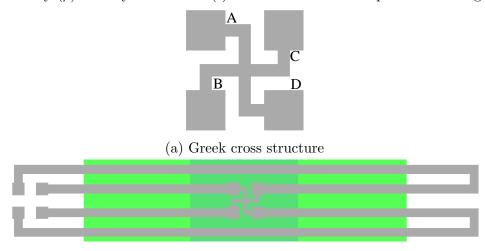

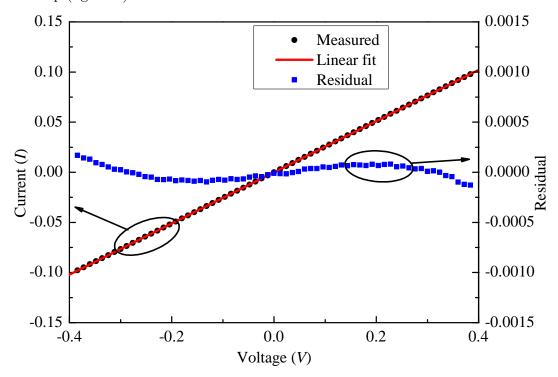

- Electrical test structures. Sheet resistance structures were added to the interconnect mask design (fig. 2.13). Sheet resistance  $(R_s = \rho/t)$  is the ratio between material resistivity  $(\rho)$  and layer thickness (t). The measurement is performed using the four

(b) Greek cross structure encapsulated in PI hinge

Figure 2.13: Greek cross structures for sheet resistance measurements.

point probe (FPP) method. The layout of these structures is often referred to as the Greek cross structure [61]. A design with elongated traces was used for measurements

of resistance in the flexible bend (fig. 2.13(b)). The measurement is performed by forcing a current (I) between points A-B and measuring the voltage drop (V) across points C-D. Sheet resistance is calculated using the van der Pauw formula:

$$R_s = \left(\frac{V}{I}\right) \frac{\pi}{\ln 2} \tag{2.3}$$

By measuring  $R_s$ , the thickness of the deposited layer can be extracted since electrical resistivities of commonly used metals are known. The metal sputtering uniformity can therefore be evaluated by measuring sheet resistance at various points across the wafer.

• Sidewalls and top cover. The sidewall dimensions were chosen to be slightly smaller than the current G4 1W LED Capsule form Philips Lighting [43]. The last sidewall and top cover dimensions are larger to form an overlap with the edges of the other sidewalls for preventing adhesive leakage due to limited alignment precision during package folding.

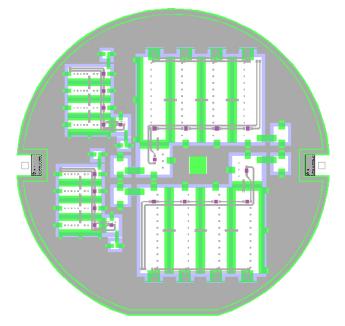

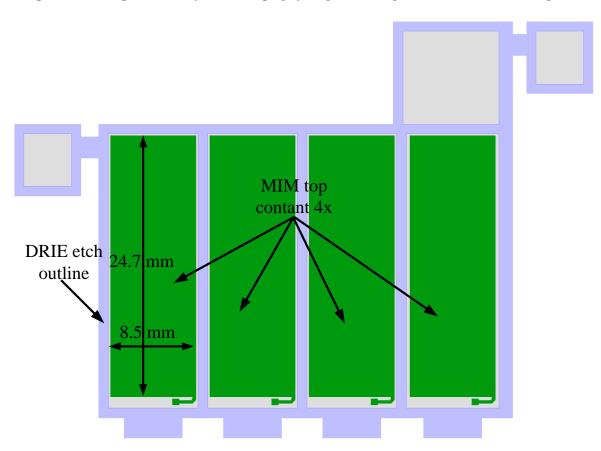

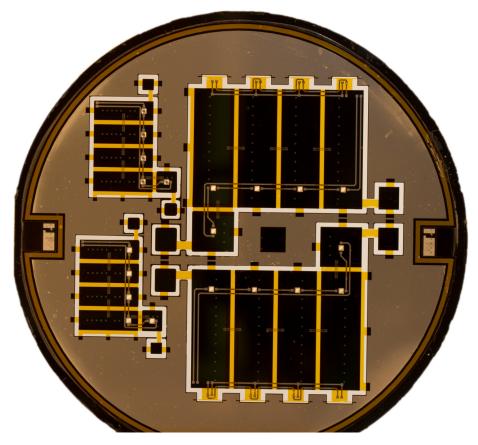

A package design with 50% smaller physical dimensions was also added for demonstration purposes. This package does not include backside components nor front-to-back interconnections, but retains the same cross-sectional area of the interconnects as the full size design. A complete 4 inch wafer front-side layout is shown in fig. 2.14, which contains 2 full size and 2 half size packages. Package design and layout were realized using L-Edit v15.15 physical

Figure 2.14: Full wafer front-side design layout.

layout editor, by Tanner EDA. Mask fabrication was done in Dimes Technology Centre (DTC) of Delft University of Technology.

#### 2.4 Flexible Interconnect Fabrication

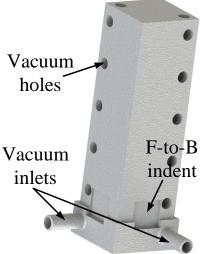

Package fabrication was based on the Flex-to-Rigid (F2R) platform, designed for ultra-flexible medical sensor processing [62]. F2R was developed in collaboration between TU Delft and Philips Research. In this process polyimide is used to encapsulate aluminum interconnect

in the neutral bending plane. Some modifications were made to the processing sequence to incorporate additional features in the design.

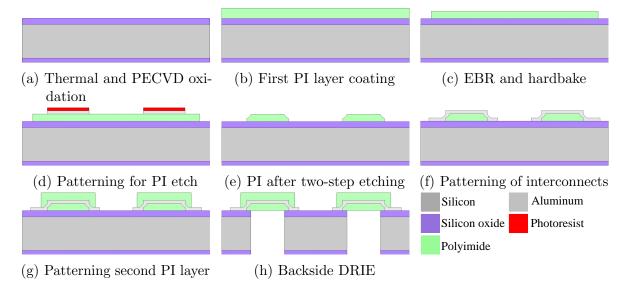

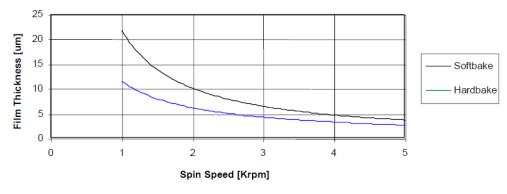

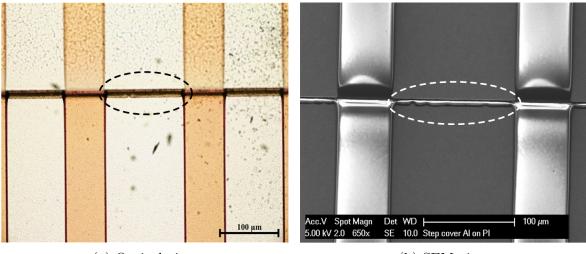

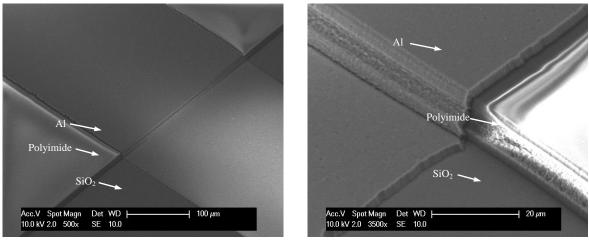

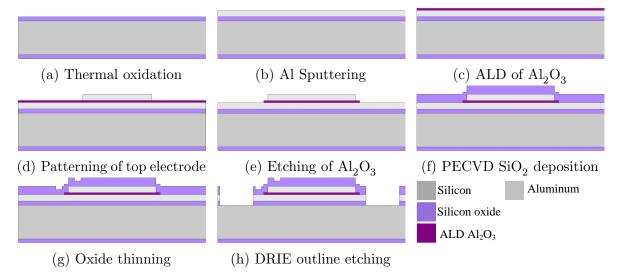

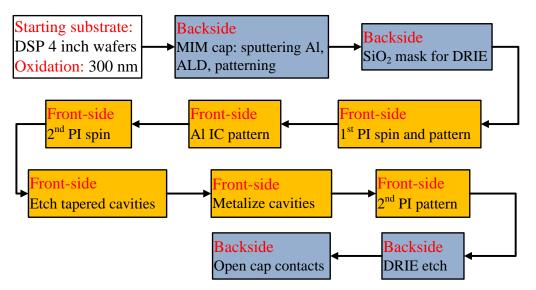

Fabrication was carried out at the DTC class 100 cleanroom. 4 inch double-side polished (DSP) p-type Si wafers of 520 µm thickness were used as the substrate material. The process started with growing 300 nm of wet thermal silicon oxide (SiO<sub>2</sub>) at 1000 °C on both sides of the wafer. This layer was used as an isolation layer for the backside integrated capacitors and part of the etch stopping layer for through wafer DRIE etching. An additional 1 µm of oxide was deposited at 400 °C by plasma enhanced chemical vapor deposition (PECVD) on the front-side to finalize the etch stop layer as shown in fig. 2.15(a). Then a layer of polyimide

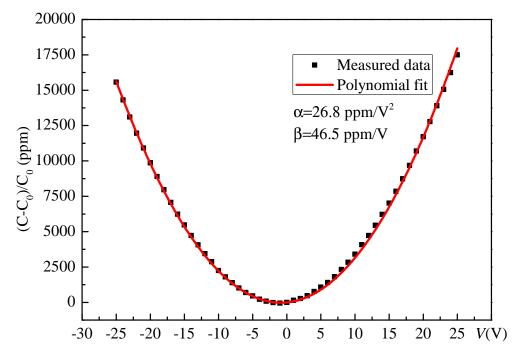

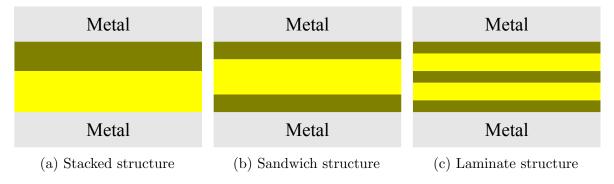

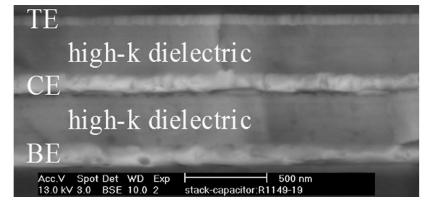

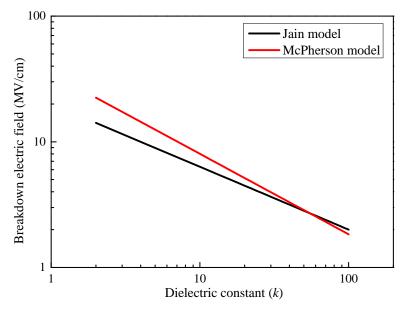

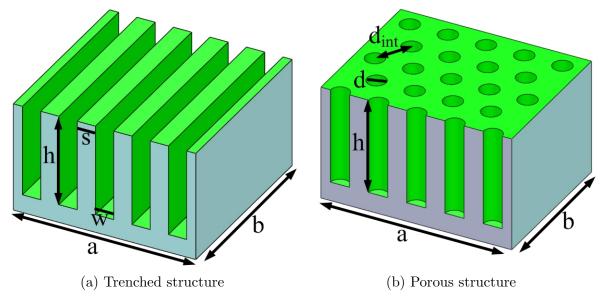

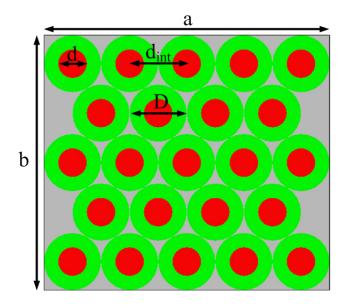

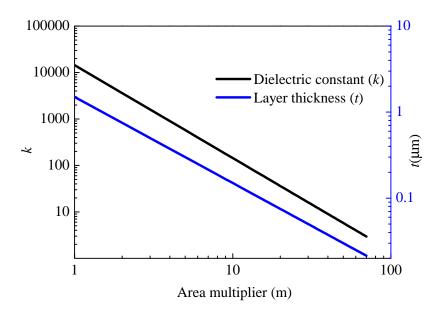

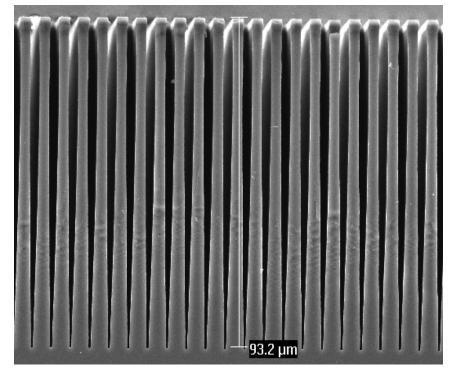

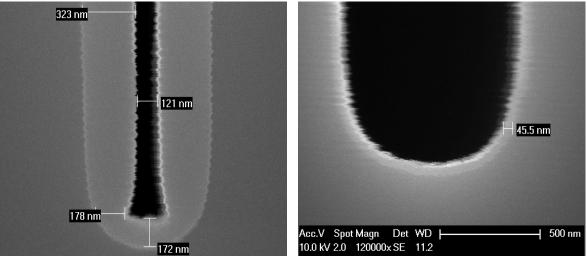

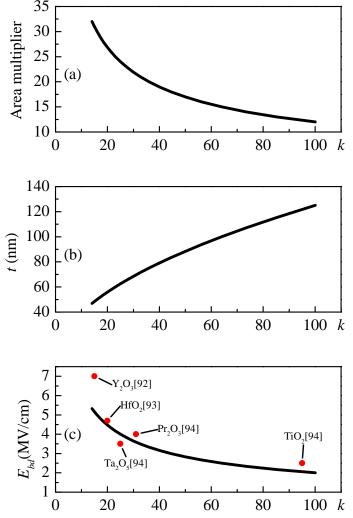

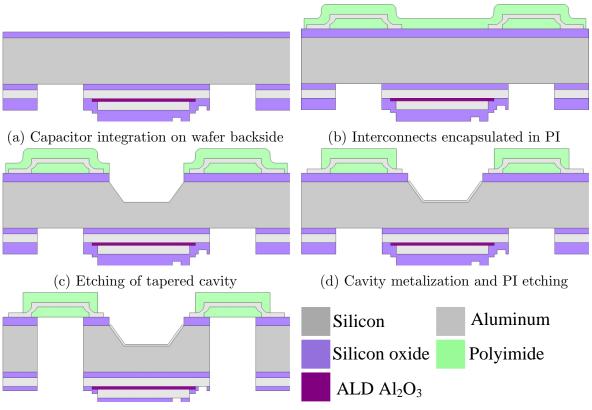

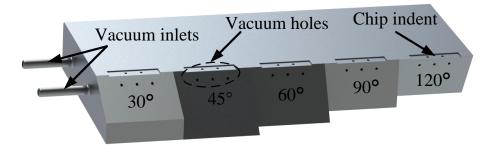

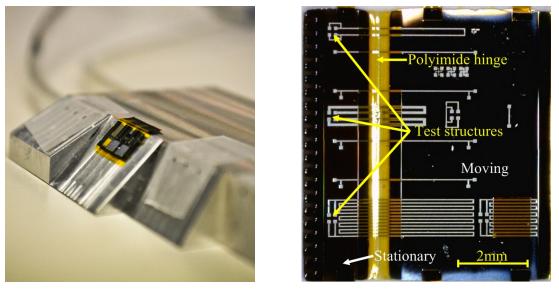

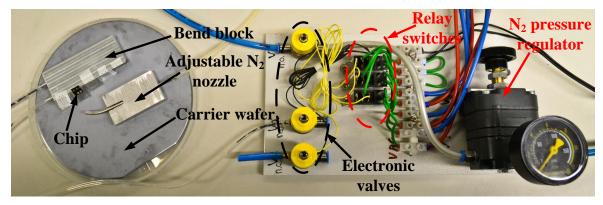

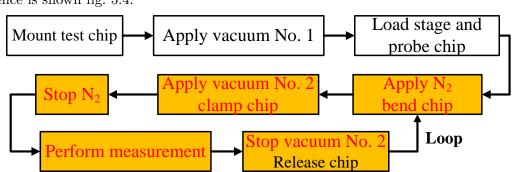

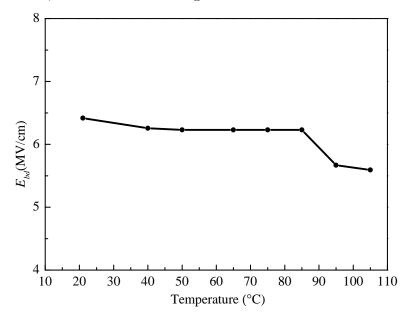

Figure 2.15: Flexible interconnect fabrication process.